Abstract

The step-up DC–DC converter is widely used for applications such as IoT sensor nodes, energy harvesting, and photovoltaic (PV) systems. In this article, a new topological quasi-Z-source (QZ) high step-up DC–DC converter for the PV system is proposed. The topology of this converter is based on the voltage-doubler circuits. Compared with a conventional quasi-Z-source DC–DC converter, the proposed converter features low voltage ripple at the output, the use of a common ground switch, and low stress on circuit components. The new topology, named a low-side-drive quasi-Z-source boost converter (LQZC), consists of a flying capacitor (CF), the QZ network, two diodes, and a N-channel MOS switch. A 60 W laboratory prototype DC–DC converter achieved 94.9% power efficiency.

1. Introduction

Step-up DC–DC converters are widely used for applications that require high voltage converted from low input voltage, such as energy harvesting systems [1,2], IoT node operating systems on low-voltage battery cells [3], and photovoltaic (PV) systems for grid connection [4,5,6]. Although the necessary power and voltage for application is different, the same dc–dc converter topology is applicable and effective to these applications. The basic boost converter (BBC) is an established technique with a long history by which CR is determined by CR = 1/(1–D), where D is duty cycle. However, it has difficulty of control at high duty cycle when the duty ratio increases because of its nonlinear characteristics and narrow pulse width [7]. In addition, it suffers from the voltage stress on the semiconductor switches and conduction loss that is due to the long ON status of the switches during period D to hold the high CR status. Of course, the high CR can be simply obtained by the series connection of BBC, but it increases loss, cost, and volume; therefore, it is not smart option. To overcome these obstacles, alternative types of high step-up dc–dc converters have been proposed [8,9,10]. There are two approaches to achieve the high CR; one is the isolated type and the other is the non-isolated type. The isolated type obtained the high voltage by changing the secondary and primary turn ratios of the transformers. However, it produces inductor leakage and the necessity for the custom-made transformer, which additionally often requires measurements of unknown key electric and magnetic parameters. In addition, the bulky equipment is not suitable for the harvesting system and IoT node operation system. On the other hand, non-isolated converters are suitable for these applications because of both volume and cost. In this category, there are some promising converters introduced. R-J. Wai et al. [11], S-M. Chen et al. [12], and H-C. Liu et al. [13] proposed a coupled inductor type. However, it required the snubber circuits to suppress the leakage of inductors. In addition, the coupled inductors are not off-the-shelf components—the same as the transformer. Recently, a quasi-Z-source network has been installed in DC–DC converters [14,15,16,17,18,19,20,21,22,23,24]. Z-source networks typically consist of two inductors, two capacitors, and a diode that are connected to each other. Originally, Z-source networks were used for inverters to suppress shoot-through problems. L. Yang. et al. [14,15] applied the quasi-Z-source networks to the DC–DC converters. After that, several Z-source-type DC–DC converters were introduced. However, there are some drawbacks in previously introduced QZ DC–DC converters, such as low CR [14,15,16], an uncommon GND between input and output voltage [19,20,23], and complex implementation [18,21,22]. M. Veerachary et al. proposed the QZ boost converter [17], called a sixth-order quasi-Z-source DC–DC converter (SOQZCS). The achieved CR of the converter was (2–2D)/(1–2D). The operating duty cycle D is less than 0.5 to avoid narrow pulse-width control in the common GND configuration by simple implementation. However, it suffers from a large output ripple, requiring level shift circuits for the high-side switch, and high-voltage stress on circuit components. To eliminate these drawbacks, we reported a new QZ DC–DC converter [24].

Generally, a PV system has two approaches to connect the grid called DC-module type and AC-module type [25,26]. Since the output voltage of the one PV panel is small, that is from 15 V to 40 V [12], the DC-module type connects PV panels in series to build up the DC voltages for ensuring the grid voltage. However, the DC-module type has a drawback in principle for a partial shadow problem. When one PV panel is shadowed by obstacles such as clouds, leaves, and birds, the PV current becomes weak and the other series-connected PV-string currents are also weakened because they connect in series with each other. So, some avoiding methods are required [26]. On the other hand, the AC-module type connects the PV panels in parallel, and the partial shadow problem does not occur. However, instead, the AC-module type requires the high step-up DC–DC converter to ensure grid-connect voltage from the low output voltage of the one PV panel. The conventional AC-module installed BBC, so the aforementioned problems exist. A DC–DC converter for a PV system requires the following characteristics: the low input current for maximum point tracking (MPPT) control, low voltage stress at high step-up status, high efficiency, low cost, and reliability.

In general, to connect to the AC grid from the PV panels, an inverter circuit is inserted between the PV output and the grid to convert voltage from DC to AC. To the input terminal of the inverter, an electrolytic capacitor is connected to suppress the voltage ripple. The electrolytic capacitors are the most-aging components in the electric instruments, and they inflate the aging speed by their input voltage ripple. Of course, the electrolytic capacitor is a possible replacement of the film-type capacitor; however, the capacitance value of film-type capacitance is smaller and more expensive than the electrolytic capacitor. Therefore, the input voltage of the ripple is a significant parameter for the inverter from the viewpoint of cost and reliability. The proposed converter features high CR, low output voltage ripple, and low voltage stress for both semiconductor devices and flying capacitor, and is free from the high-side level shifter. A previously submitted paper [24] introduced the fundamental idea, the theoretical consideration, and the simulation results using a simulator. However, all elements used in the simulator are ideal elements. For example, the on resistance of transistor M, the parasitic resistance of inductor L, and the equivalent series resistance (ESR) of capacitor C are ignored. In addition, input voltage Vg and the output resistance Ro are ideal. So, the efficiency of the DC–DC converter was not evaluated. In this paper, we developed an actual 60 W laboratory prototype of the proposed DC–DC converter.

The operational principle is summarized in Section 2 and the topology comparison between [17] and LQZC are discussed in Section 3. Shown in the components selection, Section 4, are the measurement results of the conversion rate (CR), the measurement waveforms, and the measurement results of the efficiency. The measurement set-up and experimental results are shown in Section 4, and how the parasitic resistance of inductor RDC affects the CR is considered theoretically and verified by a simulator in Section 5, and, finally, this work concludes in Section 6.

2. Circuits of the Proposed High Step-Up Converter

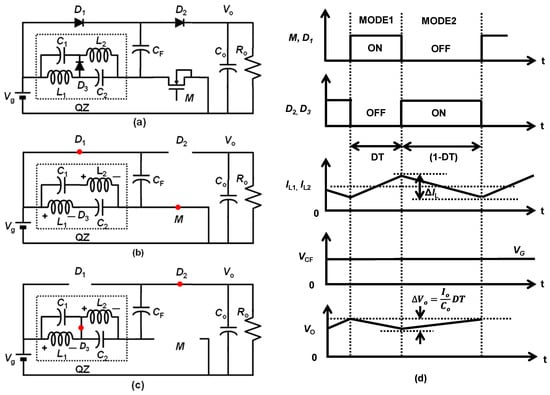

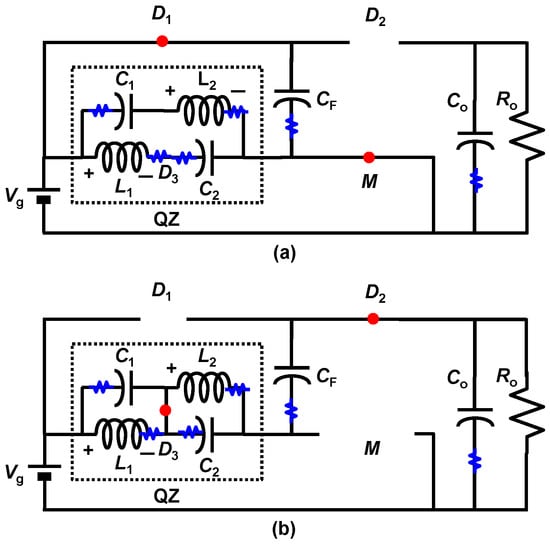

Figure 1a shows the proposed converter. The surrounded dot-line is a QZ network. It operates in two modes, Mode1 and Mode2.

Figure 1.

(a) Proposed high step-up DC–DC converter (LQZC). (b) Mode1 operation. (c) Mode2 operation [24]. (d) Key waveforms. Reprinted/adapted with permission from Ref. [24]. Copyright 2022, IEICE.

Mode1: The equivalent circuit for this mode of operation is depicted in Figure 1b. The diode D1 and transistor M are turned ON and the diode D2 and D3 are turned OFF during this operation. The red circles denote the ON state of the switch transistor and diodes. Applying KVL to the closed loops, the following equations are obtained:

Vg − VL1 + VC2 = 0

Vg + VC2 − VL2 = 0

VCF = Vg

Mode2: The equivalent circuit for this mode of operation is depicted in Figure 1c. The D2 and D3 are turned ON and diode D1 and transistor M are turned OFF during this operation. Applying KVL to the closed loops, the following equations are obtained:

VL1 = −VC1

VL2 = −VC2

Vg + VC1 + VC2 + VCF = Vo

Applying the volt-second balance to inductor L1 using Equations (1) and (4), assume C1 = C2:

By substituting Equation (9) for Equation (6), and using Equation (3), Vo/Vg was obtained as follows:

Equation (10) shows the same CR (=Vo/Vg) as obtained by [17].

Figure 1d shows the key waveforms.

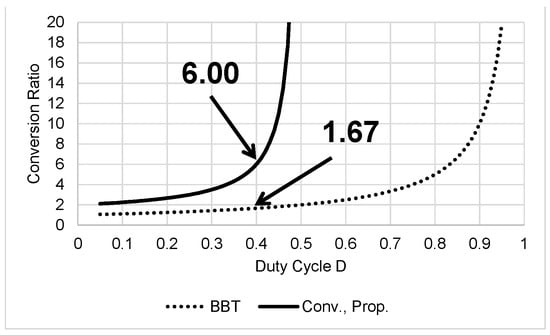

Figure 2 shows the CR of the BBC and the proposed converter. To eliminate narrow pulse-width control difficulty, the conventional converter [17] and the proposed converter [24] are designed to operate in a range from 0 to 0.5 of D, unlike BBT. The CR of Conv. [17] and Prop. [24] is obtained as 6.00 but that of BBT [7] becomes only 1.67 at D = 0.4.

Figure 2.

CR of BBC [7] and Conv. [17], Prop. [24] converters.

3. Topology Comparison of Converters

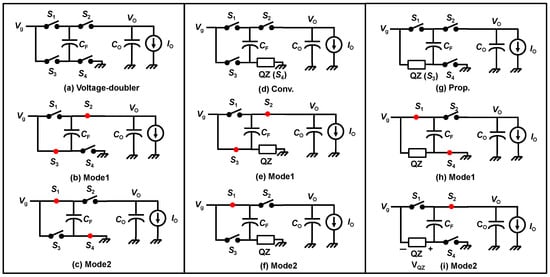

In this section, the topology difference between the conventional converter and proposed converter is described. Figure 3 shows the three converters. Figure 3a shows the voltage-doubler [27]. Figure 3b,c are the Mode1 and Mode2 operations of it, respectively. Figure 3d shows a conventional converter [17]. Figure 3e,f are the Mode1 and Mode2 operations of it, respectively. Figure 3g shows the proposed converter [24]. Figure 3h,i are the Mode1 and Mode2 operations of it, respectively. The conventional converter topology can be regarded as the QZ replaced from the S4 in the voltage doubler. Considering other variations, we found the new topology, as shown Figure 3g. The proposed converter can be regarded as the QZ replaced from the S3 in the voltage doubler. By this modification, the proposed converter improved the output ripple, power loss, and voltage stress.

Figure 3.

Comparison of converters: (a) voltage doubler, (b) Mode1 of voltage doubler, (c) Mode2 of voltage doubler, (d) Conv., (e) Mode1 of Conv., (f) Mode2 of Conv., (g) Prop., (h) Mode1 of Prop., and (i) Mode2 of the Prop. Reprinted/adapted with permission from Ref. [24]. Copyright 2022, IEICE.

3.1. Output Voltage Ripple

The output voltage of the proposed converter is significantly reduced compared to the converter. The droop voltage of the output comes up when the output capacitor Co disconnects the source voltage Vg. This situation occurs in Mode2 in the conventional converter that is shown in Figure 3f. Since the output capacitor Co connects to only the load current Io, the output voltage Vo droops at the rate determined by Vo = (Co/Io) t. As the high step-up DC–DC converter operates generally less than D = 0.5, the period of the operation time of Mode2 shown Figure 3f is longer than that of Mode1 shown Figure 3d. On the other hand, in the proposed converter, the period of time disconnected from source voltage Vg occurs in Mode1, as shown Figure 3h. This advantage results in that low EMI and the available small-output capacitor.

3.2. High Side Driver and Level Shifter

The switch S3 in Figure 3d is given by the N-channel MOS transistor [17], where the drain terminal of the N-channel MOS transistor is connected to Vg and the source terminal is connected to QZ. It means that this is necessary for the high-side driver and the level shift circuits for S3. The level shift circuits consume operating power, and some additional circuits are required for proper start-up of the DC–DC converter. In contrast, The LQZC is high-side driver-free because the source terminal of S4 is terminated to GND, as shown in Figure 3g. It can improve the efficiency and reduce the cost and complex design of the converter.

3.3. Voltage Stress

The proposed converter provides the reduction in voltage stress for the flying capacitor CF. The voltage stress of elements is shown in Table 1. In a conventional converter, the terminals of CF are applied by Vo and Vg as shown in Figure 3e. Using Equation (10), the terminal voltage across CF becomes:

Table 1.

Voltage stress of components.

In contrast, the voltage stress of the CF applied only Vg. The voltage across CF is determined as follows:

This is obvious from Figure 3h and Equation (3). Consequently, the proposed converter can mitigate the voltage stress of CF. The stress voltages of other elements, D1, D2, M, C1, and C2, are same as those of a conventional converter [17].

4. Measurement Setup and Results

4.1. Measurement Setup

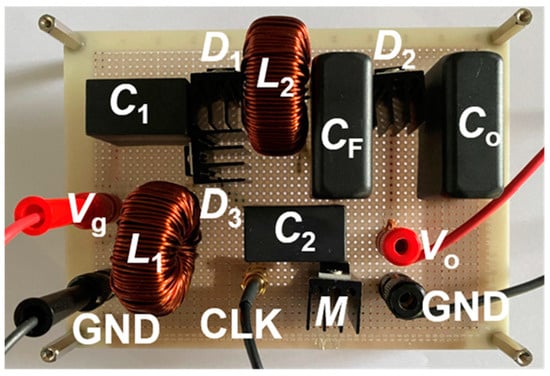

Figure 4 shows a photograph of the prototype. The values of the components and the part numbers are listed in Table 2. Here all capacitors are film type.

Figure 4.

Photograph of prototype.

Table 2.

Components specification.

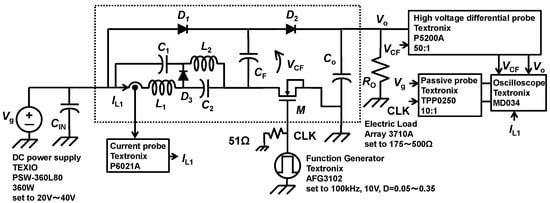

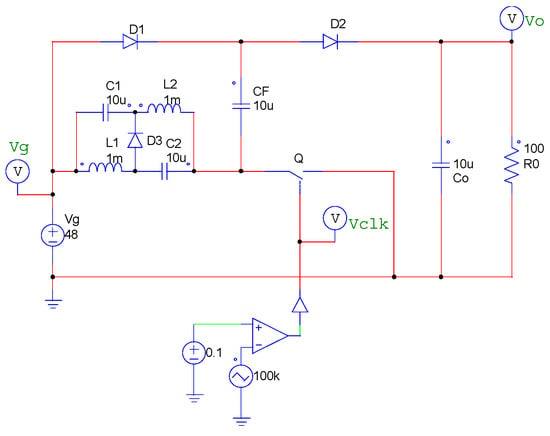

Figure 5 shows the block diagram of the measurement set-up. The clock frequency fCLK is set to 100 kHz for all measurements. The duty cycle D is changed from 0.05 to 0.35 by function generator Textronix AFG3120. The drive voltage amplitude for the transistor M is set to 10 V. The input voltage Vg is set to 20 V, 30 V, and 40 V. The output voltage Vo connected the electric current load Array 3710 A, of which the output resistance Ro is set from 175 Ω to 500 Ω. The electrolytic capacitor CIN, 470 uF (200 V), is connected between the Vg and GND as an input filter. The waveform of the output voltage Vo and the flying capacitor CF are measured by a high-voltage differential probe, Textronix P5200A, on 50:1 attenuation, and the inductor current IL1 is measured by the current probe Textronix P6021A. The input voltage Vg and clock signal CLK are measured by the passive probe Textronix TPP0250 on 10:1 attenuation.

Figure 5.

Measurement set-up.

4.2. Measurement Results

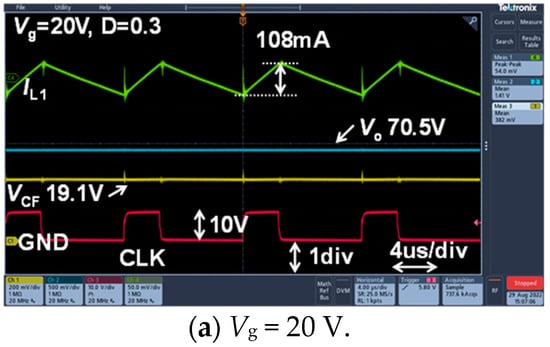

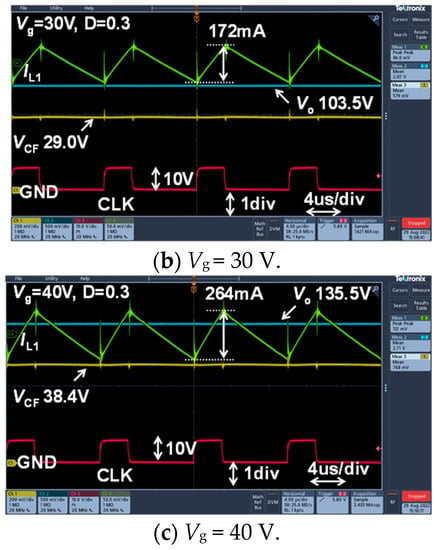

Figure 6 shows the steady-state measurement waveforms of IL1, Vo, VCF, and CLK when D = 0.3 and Ro = 500 Ω, and set to Vg = 20 V, 30 V, and 40 V, respectively.

Figure 6.

Experimental waveforms. Green line: IL1. Blue line: Vo. Yellow line: VCF. Red line: CLK.

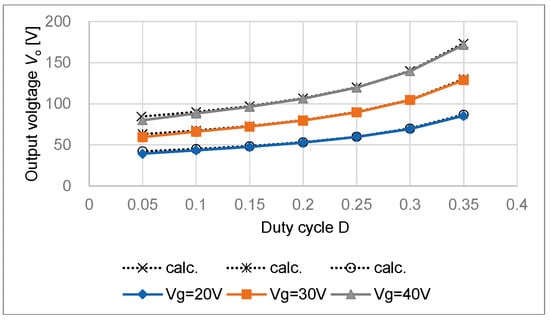

Figure 7 shows the relationship between the measured output voltage Vo and duty cycle D drawn together with the calculated gain by the dotted lines. The duty cycle D changed from 0.05 to 0.35 for input voltage Vg = 20 V, 30 V, and 40 V, respectively, on Ro = 500 Ω. The measurement results agree well with the calculated results. When the duty cycle D is small, the output voltage Vo is slightly low because of the forward voltage VF of D1.

Figure 7.

Output voltage Vo and duty cycle D.

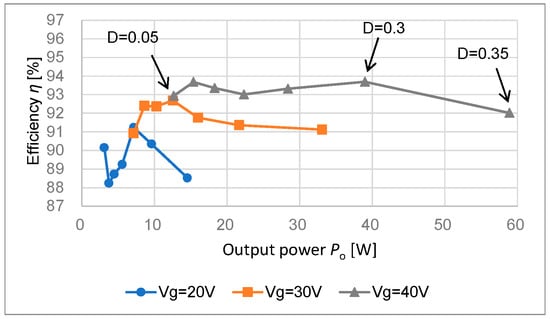

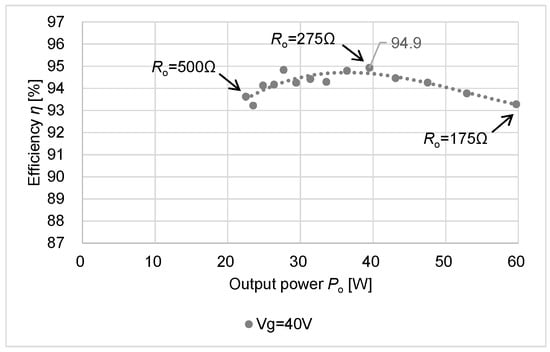

Figure 8 depicts the relationship between the output power Po and the efficiency η using the data of Figure 7. Figure 9 shows the efficiency versus the output power Po at Vg = 40 V and D = 0.2 when Ro varies from 500 Ω to 175 Ω by 25 Ω steps. The peak efficiency 94.9 % is obtained. Table 3 summarizes the performance comparison of Conv. [17] and this work.

Figure 8.

Efficiency η using data of Figure 7.

Figure 9.

Peak efficiency η.

Table 3.

Performance summaries.

5. Discussion

In this section, the effect of the parasitic element of the proposed converter is discussed. Generally, the equivalent series resistance (ESR) of the capacitors is relatively smaller than the DC resistance (RDC) of the inductor [28,29,30]. So, we focus on the parasitic element of the inductors. Figure 10 shows the proposed converter, which includes the parasitic resistance depicted by the blue resistor symbol.

Figure 10.

Proposed high step-up DC–DC converter (LQZC) with parasitic resistances. (a) Mode1. (b) Mode2.

Considering the steady-state condition, the average current through a capacitor operating in a periodic steady state is zero and the average current through an inductor operating in a periodic steady state is zero [7]; therefore, the average inductor current IL1 can be written as follows.

By substituting Equation (10) with Equation (13) and using VgIg = VoIo, the following equation is obtained.

Equation (14) indicates that the inductor current IL1 is larger than the output current Io. For example, IL1 = 5Io when D = 0.4 and IL1 = 1.67Io when D = 0.2. This means that the equivalent series resistance (RDC) of inductors affects the efficiency of the converter and CR, too. Here, we focus on how much the CR is affected by the RDC of L1 and L2.

In Mode1, the voltage expressions obtained using KVL are:

where Vr = RDC × IL.

In Mode2, the voltage expressions obtained using KVL are:

Applying the volt–second balance to inductor L:

Compared to Equation (9), Equation (18) indicates that when the voltage of capacitor Vc is reduced by Vr, it results in reducing Vo. This is attributed to the voltage across inductors VL being reduced in Mode1 by RDC.

By substituting Equation (18) for Equation (6), VCF = Vg, Vo/Vg is obtained as follows:

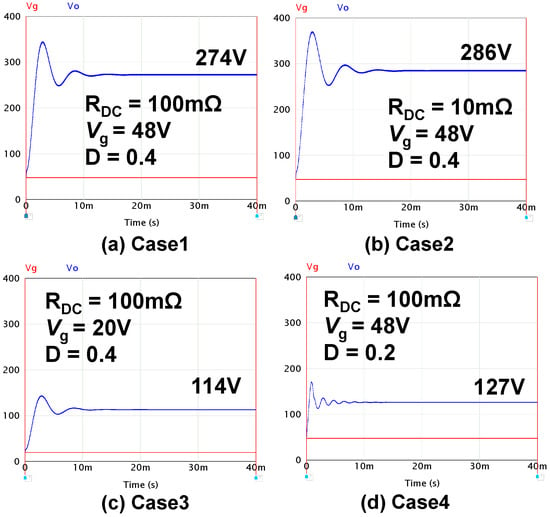

To verify Equation (19), the output voltage Vo was checked by the PSIM [30] simulator when conditions changed. In the simulator circuit, the output resistance Ro is set to 100Ω, and RDC are added to L1 and L2, respectively, in Figure 11. In this situation, four cases are tested. Figure 12 shows the simulation results of output voltage Vo in four cases. The blue line is output voltage Vo, and the red line is input voltage Vg. Table 4 shows the results of calculations and the simulation results.

Figure 11.

Simulation circuits.

Figure 12.

VO and Vg. (a) Case1. (b) Case2. (c) Case3. (d) Case4.

Table 4.

Comparison of calculation and simulation results in four cases.

Calculated numerical equations in Case4 are shown as follows by Equations (19) and (14); IL1 = Io/(1–D) = 1.67Io, Io = 127 V/Ro = 127 V/100 Ω, and Vo becomes:

Table 4 shows that the calculation results correspond well to the simulation results.

6. Conclusions

This article has introduced a new high step-up DC–DC converter. The LQZC realizes a low output ripple, is free from the use of a level shifter and a high-side switch, and is plus the low stress on a flying capacitor CF. The proposed converter makes the following contributions: (i) by the low output ripple, a reliability and cost reduction for the DC–DC converter itself and the inverter circuit for the PV system because the low ripple voltage reduces the size of the capacitors and its aging. (ii) By omitting the level shifter circuit, the consuming loss is definitely reduced because the level shifter circuits and their accompanied circuits are not necessary. (iii) By reducing the voltage stress of the components, the equipment volume becomes small and reduces cost. The achieved efficiency of the converter was more than 94.9% in this prototype. Although the prototype design focuses on a PV application, the proposed architecture can be applied to applications that require the high step-up DC–DC converter, such as energy harvesting and low voltage battery systems for IoT sensor nodes, by power scaling down.

Author Contributions

Conceptualization, formal analysis, investigation, writing—original draft, T.S.; writing—review and editing, Y.M.; writing—review and editing, Y.S. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Sungjun, Y.; Salvador, C.-B.; Edgar, S.-S. An Area Efficient Thermal Energy Harvester with Reconfigurable Capacitor Charge Pump for IoT Applications. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1974–1978. [Google Scholar]

- Kishore, K.P.C.; Gabriel, C.; Harikrishnan, R.; Mohd, Y.A.; Jagadheswaran, R. Low-Voltage Capacitive-Based Step-Up DC-DC Converters for RF Energy Harvesting System: A Review. IEEE Access 2020, 8, 186393–186407. [Google Scholar]

- Min-Woo, K.; Hyunki, H.; Hyun-Sik, K. 17.8 A 90.5%-Efficiency 28.7μVRMS-Noise Bipolar-Output High- Step-Up SC DC-DC Converter with Energy-Recycled Regulation and Post-Filtering for ±15 V TFT-Based LAE Sensors. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021. [Google Scholar]

- Chen, Y.-M.; Huang, A.; Yu, X. A High Step-Up Three-Port DC–DC Converter for Stand-Alone PV/Battery Power Systems. IEEE Trans. Power Electron. 2013, 28, 5049–5062. [Google Scholar] [CrossRef]

- Wai, R.-J.; Wang, W.-H. Grid-Connected Photovoltaic Generation System. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 953–964. [Google Scholar]

- Tseng, K.-C.; Huang, C.-C. High Step-Up High-Efficiency Interleaved Converter with Voltage Multiplier Module for Renewable Energy System. IEEE Trans. Ind. Electron. 2014, 61, 1311–1319. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 3rd ed.; Springer: Cham, Switzerland, 2020; pp. 24–29. [Google Scholar]

- Li, W.; He, X. Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications. IEEE Trans. Ind. Electron. 2011, 58, 1239–1250. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Schmitz, L.; Martins, D.C.; Coelho, R.F. Generalized High Step-Up DC-DC Boost-Based Converter with Gain Cell. IEEE Tran. Circuits Syst. I: Regul. Pap. 2017, 64, 480–493. [Google Scholar] [CrossRef]

- Wai, R.-J.; Duan, R.-Y. High step-up converter with coupled-inductor. IEEE Trans. Power Electron. 2005, 20, 1025–1035. [Google Scholar] [CrossRef]

- Chen, S.-M.; Liang, T.-J.; Yang, L.-S.; Chen, J.-F. A Boost Converter with Capacitor Multiplier and Coupled Inductor for AC Module Applications. IEEE Trans. Ind. Electron. 2013, 60, 1503–1511. [Google Scholar] [CrossRef]

- Liu, H.-C.; Li., F. Novel High Step-Up DC–DC Converter with an Active Coupled-Inductor Network for a Sustainable Energy System. IEEE Trans. Power Electron. 2015, 30, 6474–6482. [Google Scholar] [CrossRef]

- Yang, L.; Qui, D.; Zhang, B.; Zhang, G.; Xiao, W. A modified Z-source DC-DC converter. In Proceedings of the 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014. [Google Scholar]

- Yang, L.; Qiu, D.; Zhang, B.; Zhang, G.; Xiao, W. A quasi-Z-source DC-DC converter. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014. [Google Scholar]

- Veerachary, M.; Kumar, P. Analysis and Design of Fourth-order Quasi-Z-Source Equivalent DC-DC Boost Converter. In Proceedings of the 2019 IEEE Transportation Electrification Conference (ITEC-India), Bengaluru, India, 17–19 December 2019. [Google Scholar]

- Veerachary, M.; Kumar, P. Analysis and Design of Sixth Order Quasi-Z-Source DC-DC Boost Converter. In Proceedings of the 2019 IEEE International Conference on Sustainable Energy Technologies and Systems (ICSETS), Bhubaneswar, India, 26 February–1 March 2019. [Google Scholar]

- Kumar, P.; Veerachary, M. Z-Network Plus Switched-Capacitor Boost DC–DC Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 791–803. [Google Scholar] [CrossRef]

- Andrade, J.M.d.; Coelho, R.F.; Lazzarin, T.B. New High Step-up dc-dc Converter with Quasi-Z-Source Network and Switched-Capacitor Cell. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020. [Google Scholar]

- Rahimi, R.; Habibi, S.; Shamsi, P.; Ferdowsi, M. A High Step-Up Z-Source DC-DC Converter for Integration of Photovoltaic Panels into DC Microgrid. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021. [Google Scholar]

- Singh, A.; Siva, V.; Singh, S.K.; Kumar, A. Quasi-Z-Source based Step-up Converter for Fuel Cell Vehicle. In Proceedings of the IEEE 2nd International Conference on Sustainable Energy and Future Electric Transportation (SeFeT), Hyderabad, India, 4–6 August 2022. [Google Scholar]

- Rahimi, R.; Habibi, S.; Shamsi, P.; Ferdowsi, M. A Three-Winding Coupled-Inductor-Based Dual-Switch High Step-Up DC–DC Converter for Photovoltaic Systems. IEEE J. Emerg. Sel. Top. Ind. Electron. 2022, 3, 1106–1117. [Google Scholar] [CrossRef]

- Rahimi, R.; Habibi, S.; Ferdowsi, M.; Shamsi, P. Z-Source-Based High Step-Up DC–DC Converters for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 4738–4796. [Google Scholar] [CrossRef]

- Toru, S.; Moon, Y.; Sugimoto, Y. New high step-up DC-DC converter with quasi Z-source network. IEICE Electron. Express 2022, 19, 20220356. [Google Scholar]

- Scholten, D.M.; Ertugrul, N.; Soong, W.L. Micro-inverters in small scale PV systems: A review and future directions. In Proceedings of the 2013 Australasian Universities Power Engineering Conference (AUPEC), Hobart, TAS, Australia, 29 September–3 October 2013. [Google Scholar]

- Toru, S.; Kitamura, A.; Sun, X.-D.; Matsui, M. Distributed MPPT PV system with current source inverter. In Proceedings of the IECON 2015—41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015. [Google Scholar]

- Palumbo, G.; Pappalardo, D. Charge Pump Circuits: An Overview on Design Strategies and Topologies. IEEE Circuits Syst. Mag. 2010, 10, 31–45. [Google Scholar] [CrossRef]

- Analog Devices Inc. Engineeri: Linear Circuit Design Handbook; Zumbahlen, H., Ed.; Elsevier Science: Amsterdam, The Netherlands, 2011; p. 758. [Google Scholar]

- Alioto, M. Enabling the Internet of Things from Integrated Circuits to Integrated Systems; Springer International Publishing: Cham, Switzerland, 2017; p. 312. [Google Scholar]

- Powersim Inc. Available online: https://powersimtech.com/ (accessed on 8 December 2022).

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).