A High Power-Conversion-Efficiency Voltage Boost Converter with MPPT for Wireless Sensor Nodes

Abstract

:1. Introduction

2. System Design and Analysis

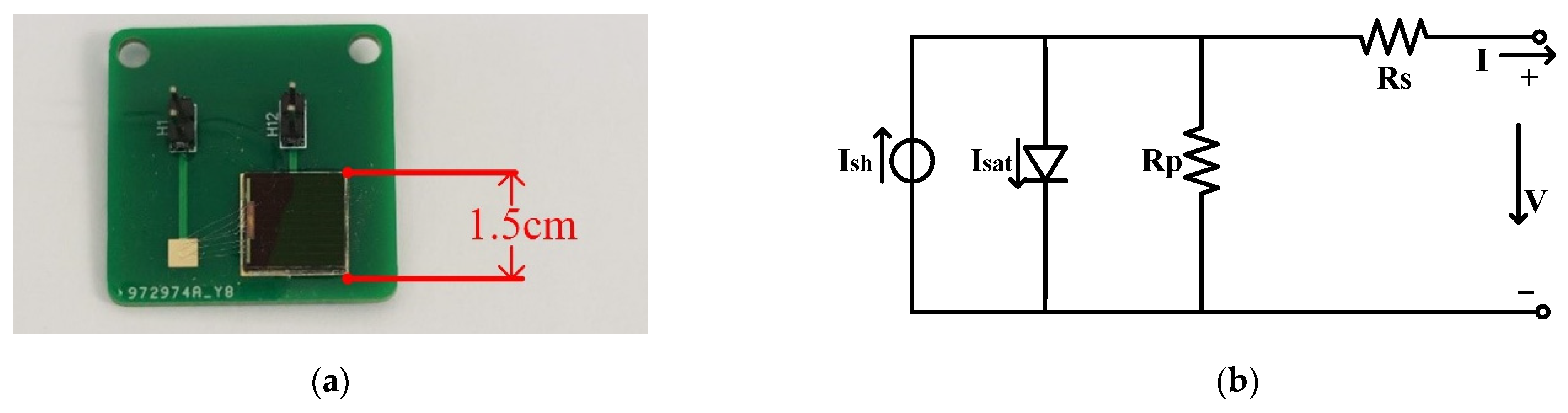

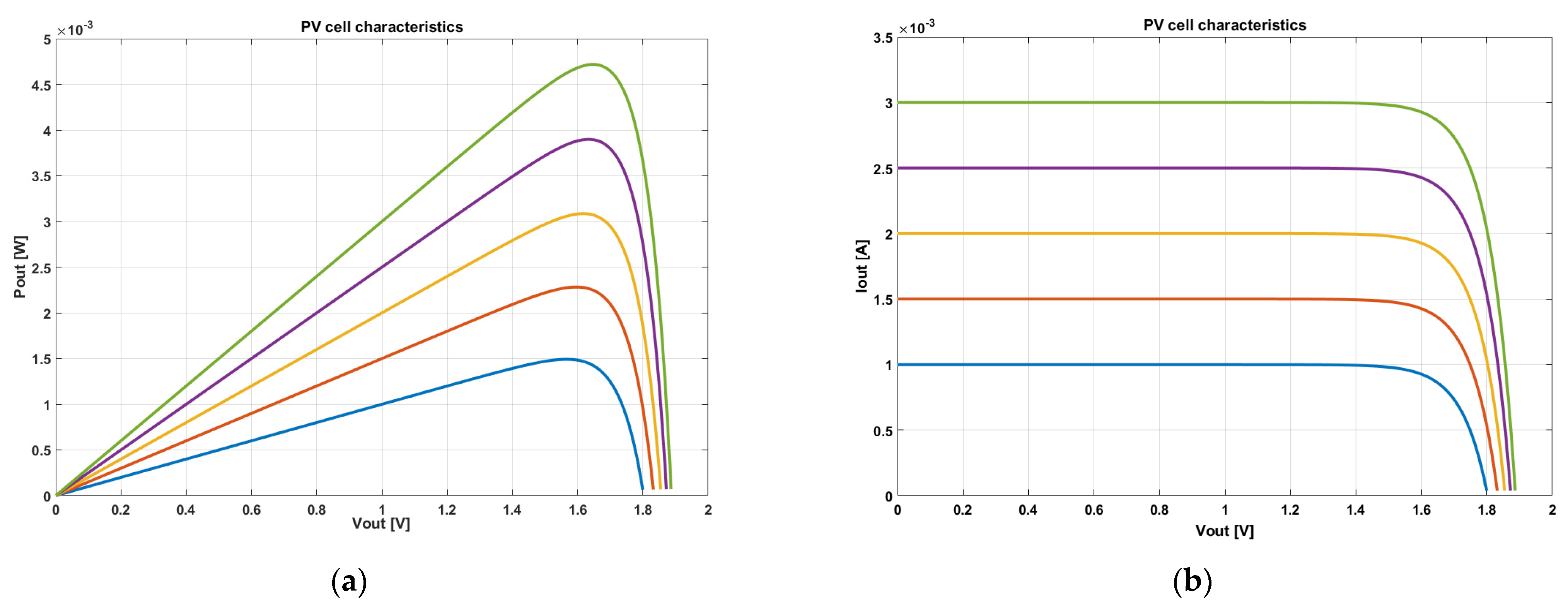

2.1. Modeling of the Photovoltaic Cell

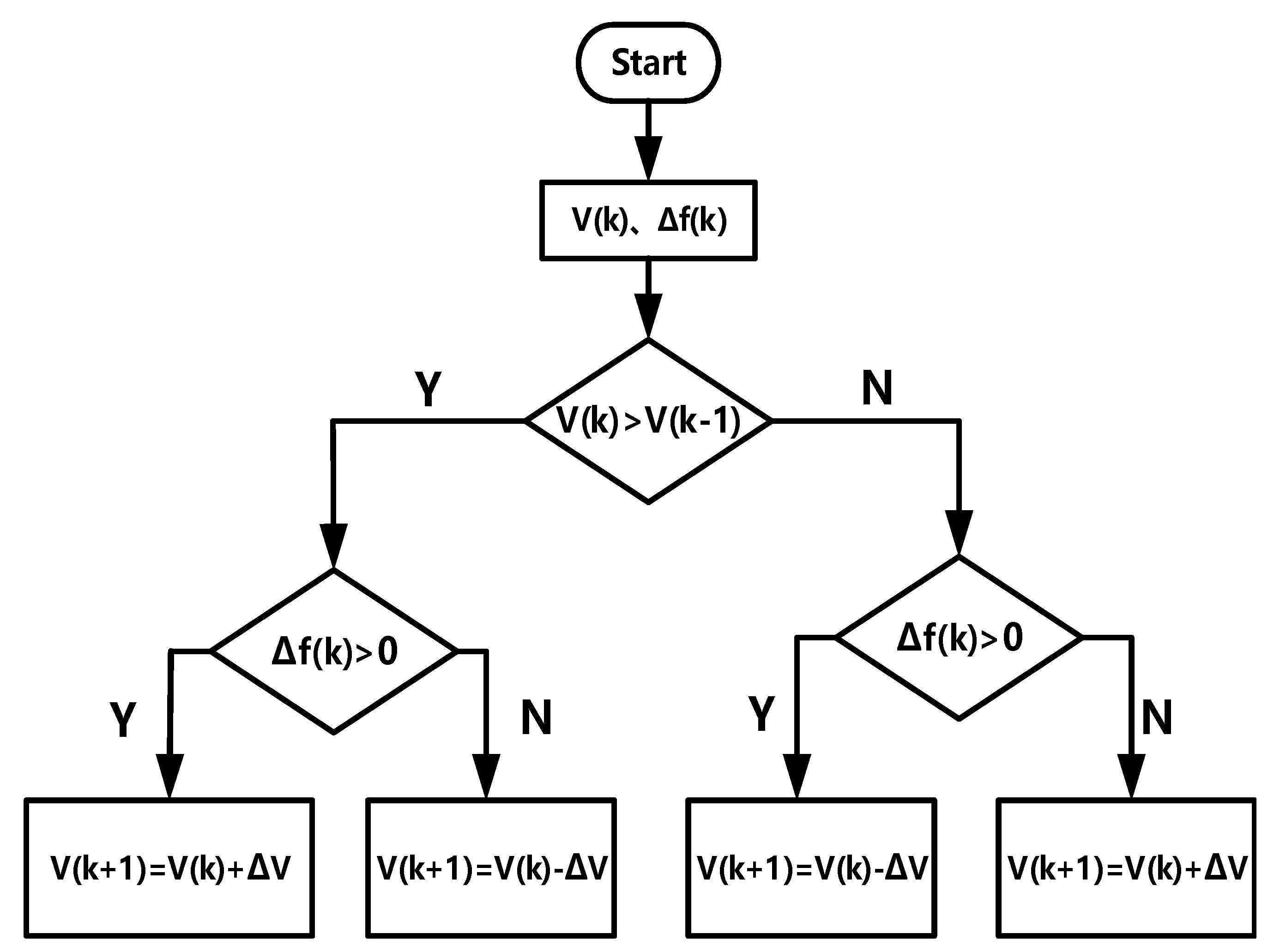

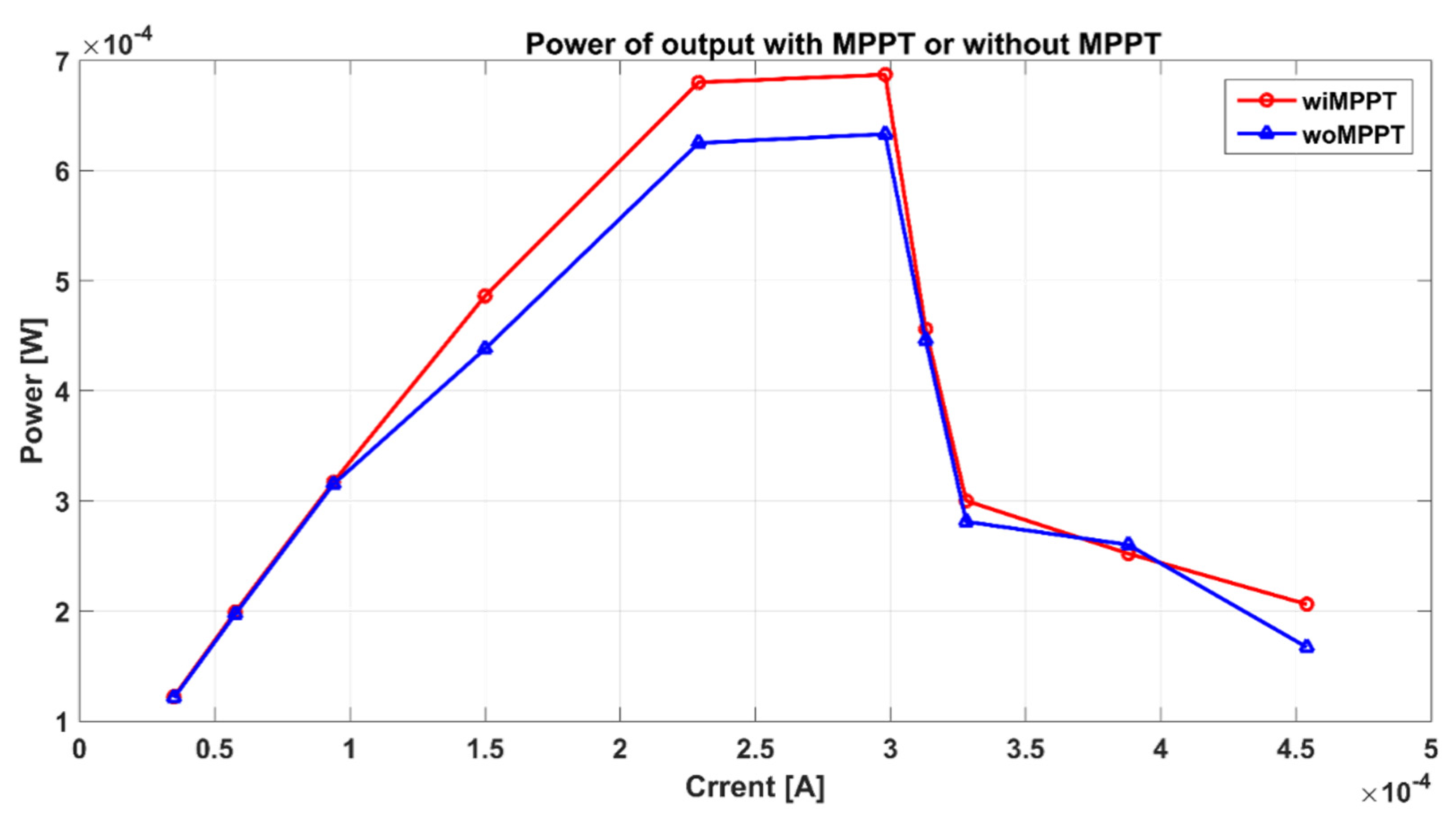

2.2. Analyze of MPPT Algorithm

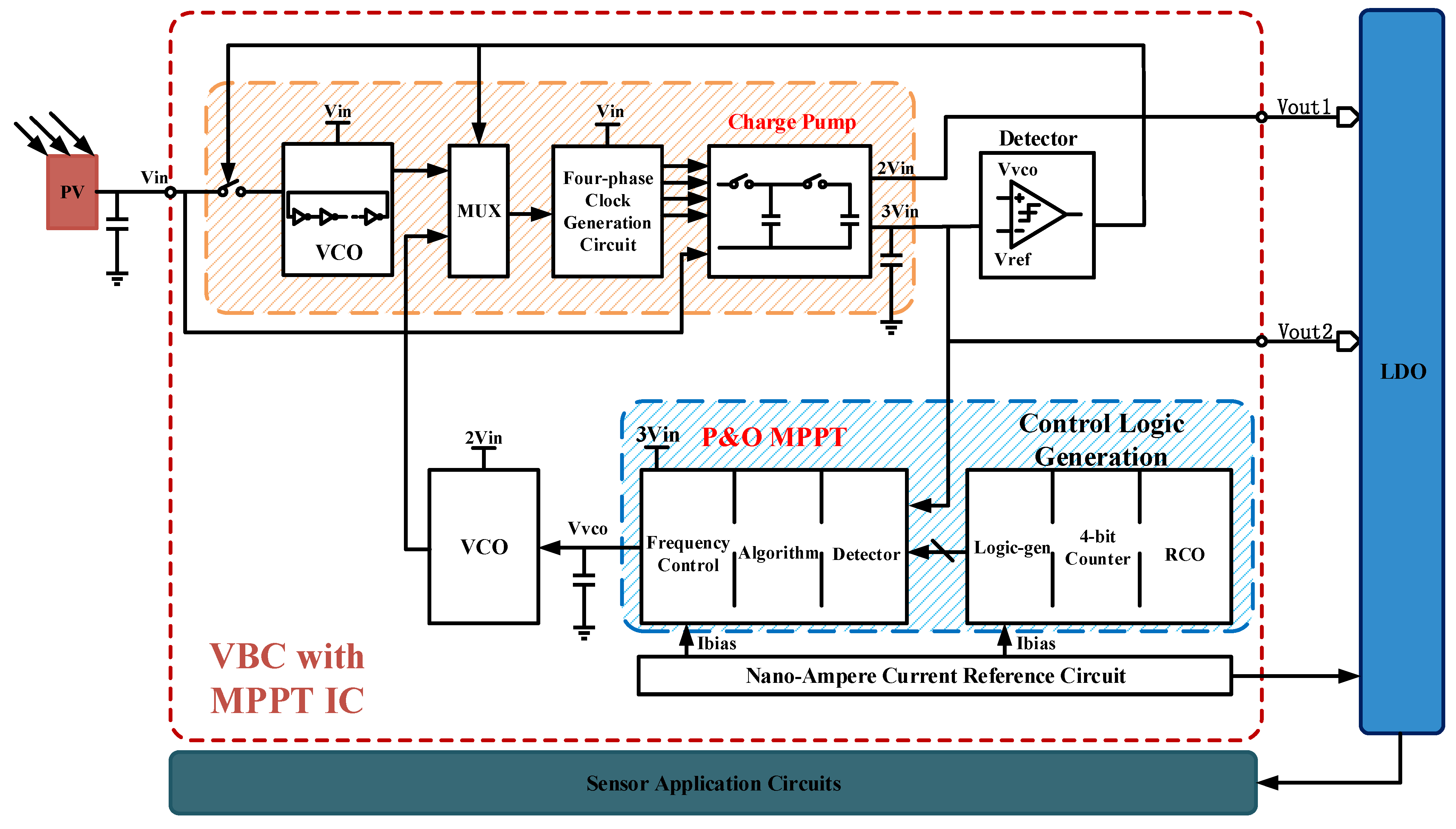

2.3. Design of the VBC System with MPPT

3. Circuit Block Implementation Details

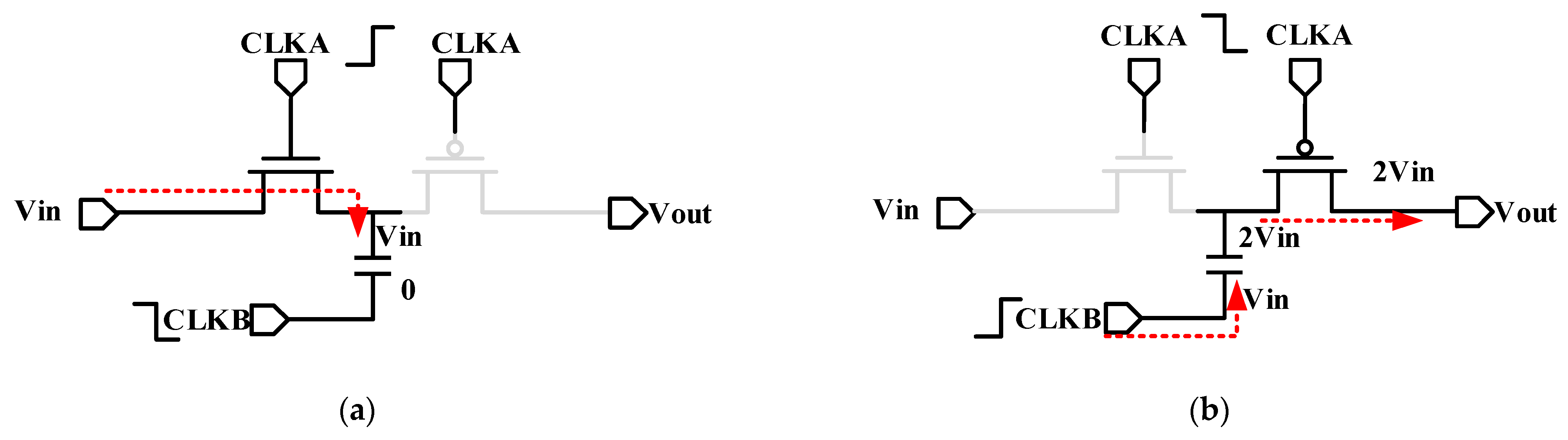

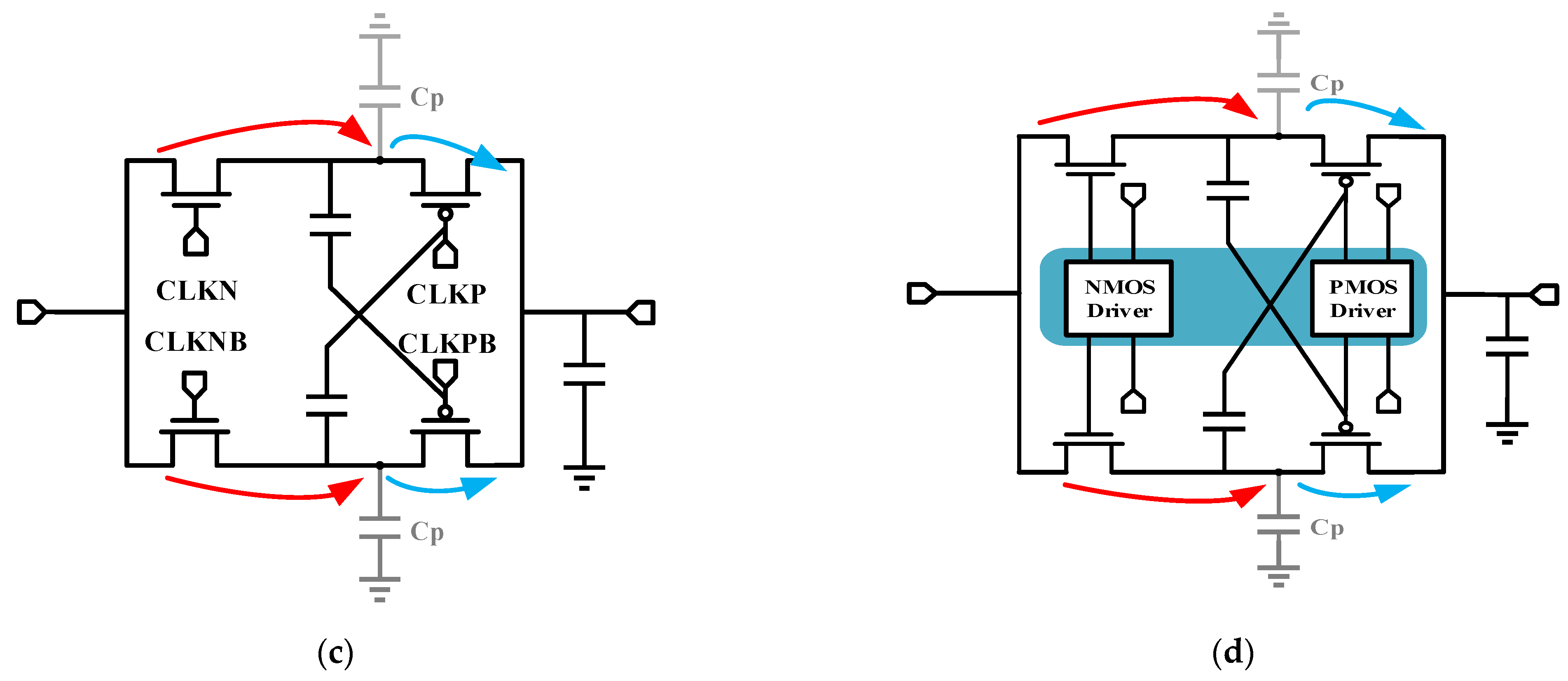

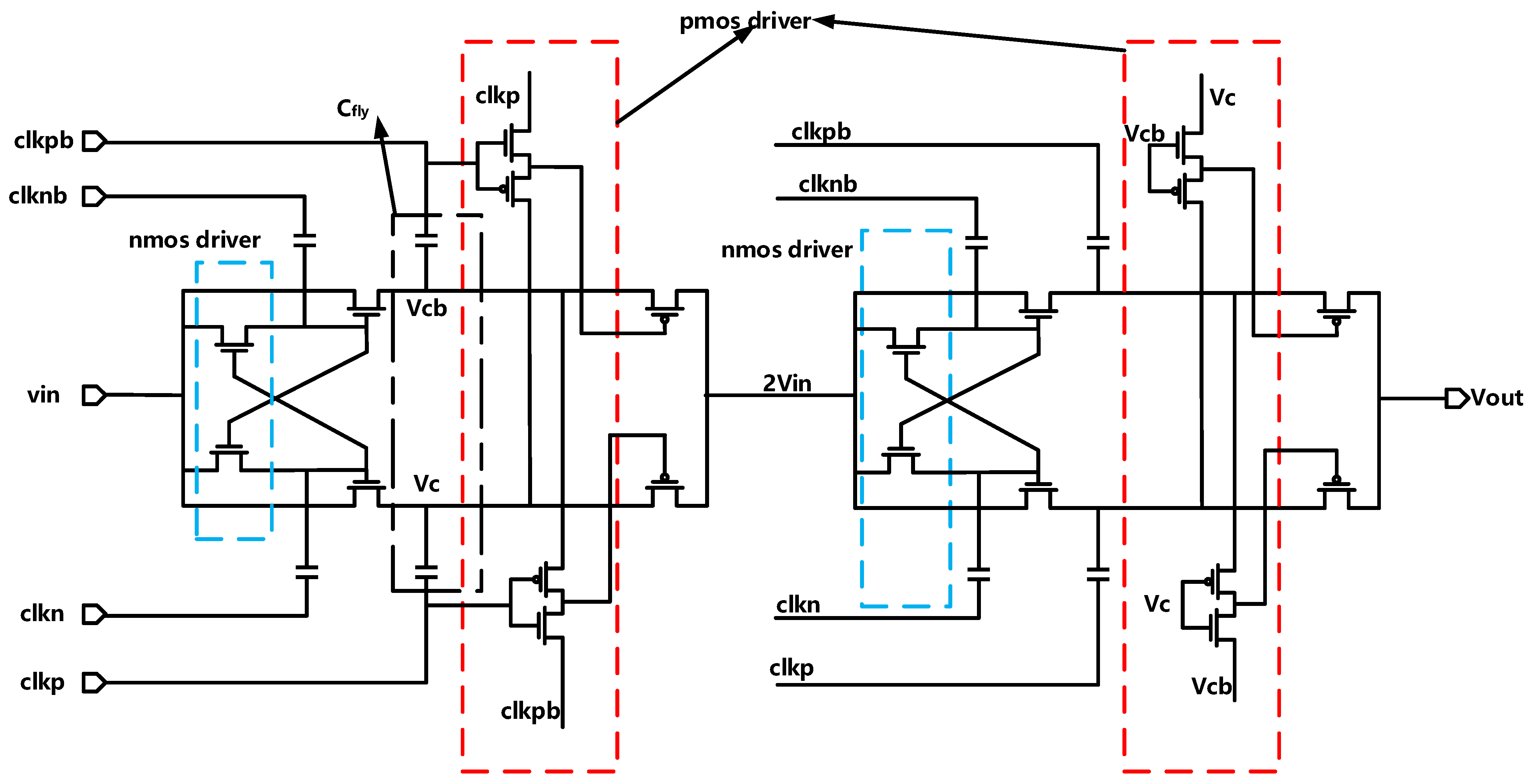

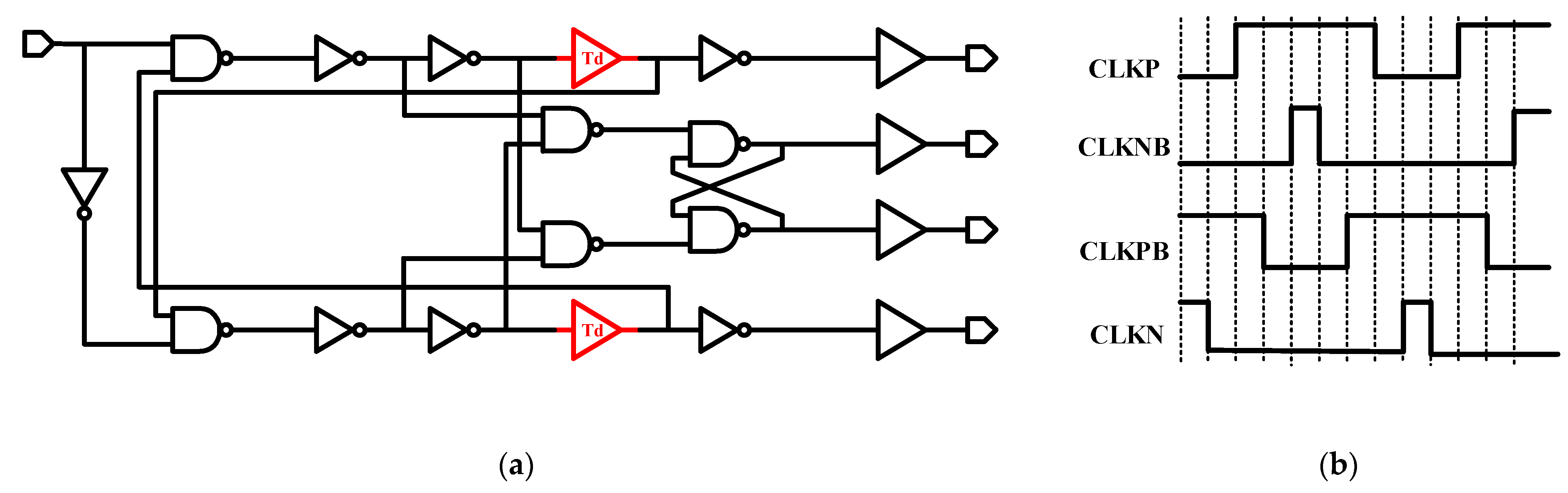

3.1. High PCE Charge Pump

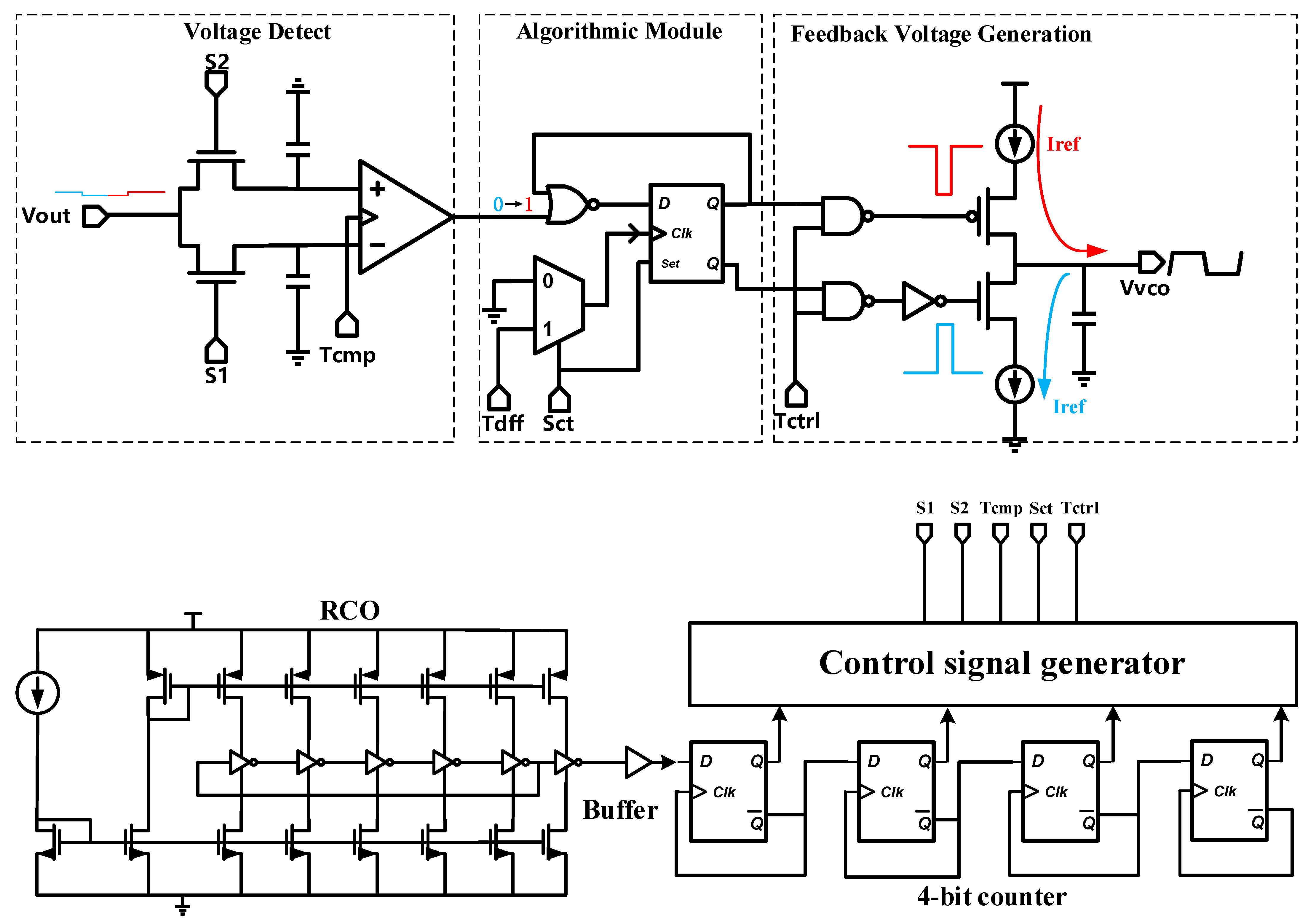

3.2. Ultra-Low-Power P&O MPPT Algorithm and Control Block

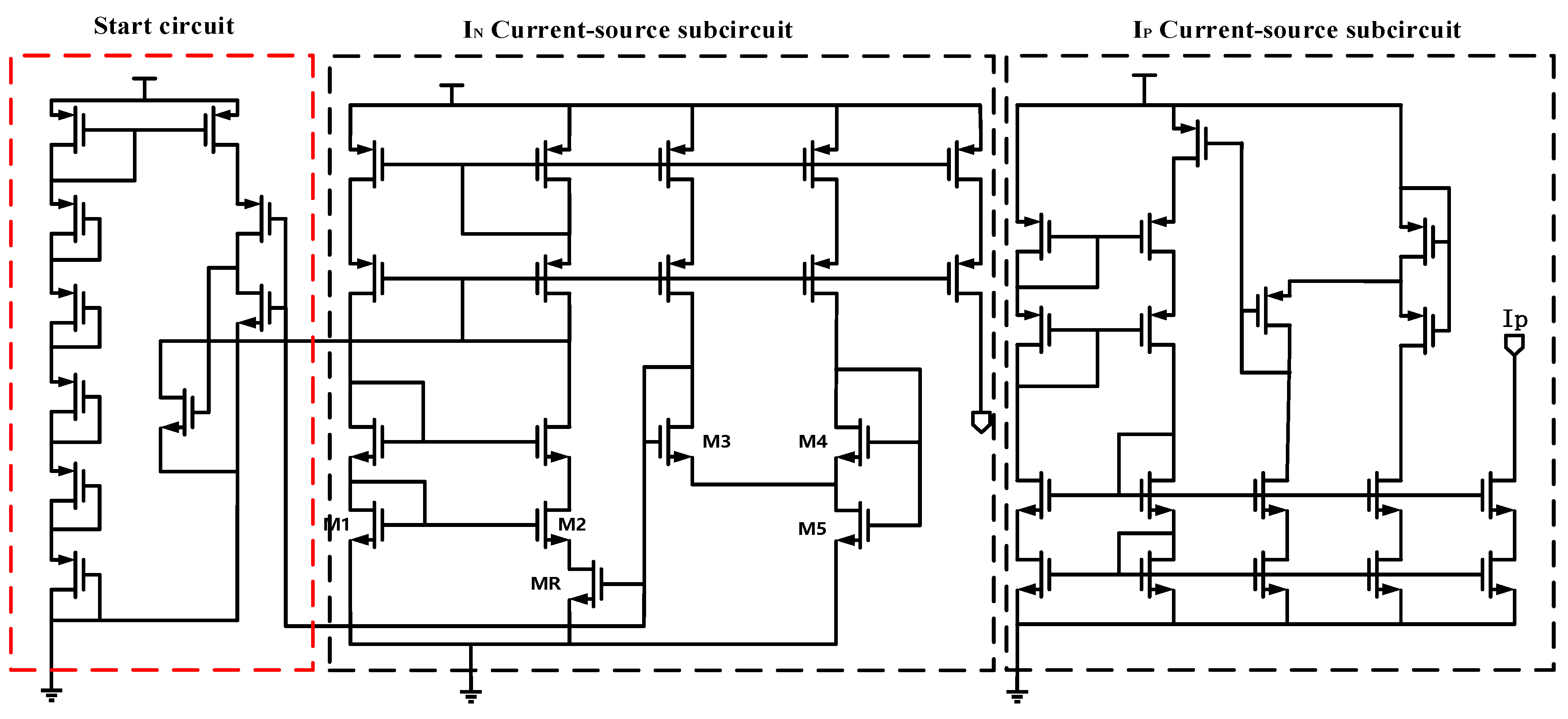

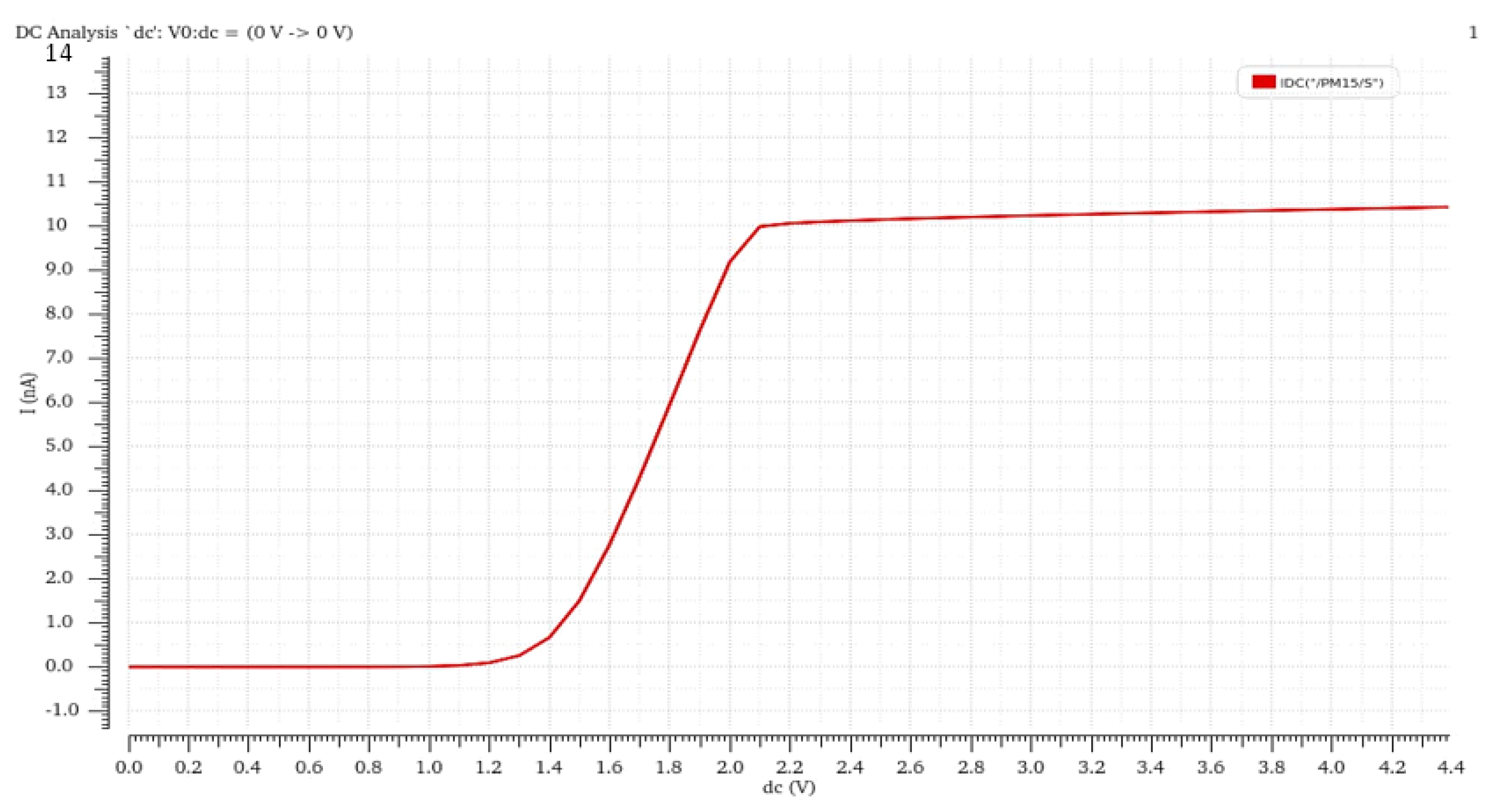

3.3. Nano-Ampere Current Reference and Current Starvation VCO

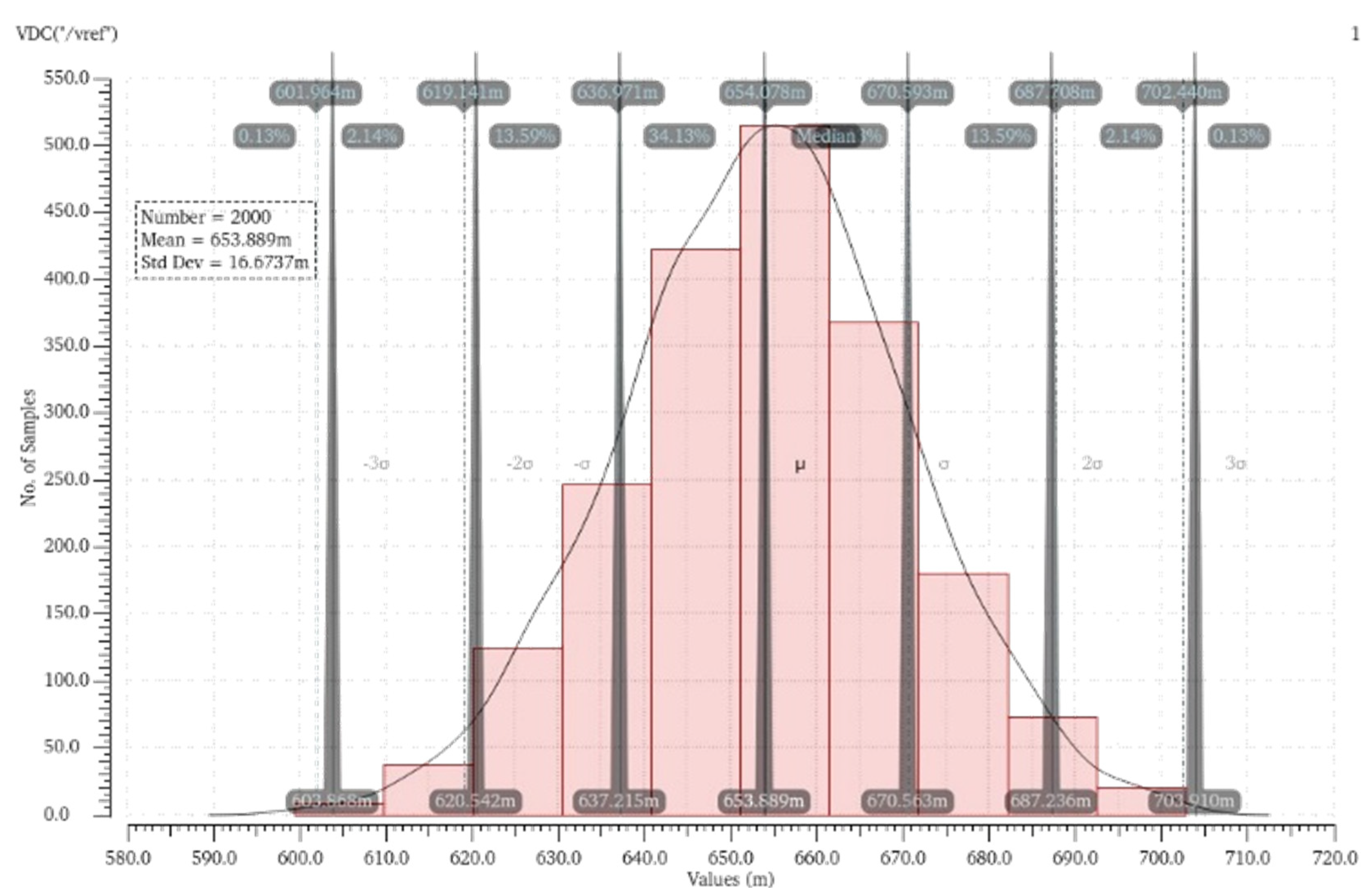

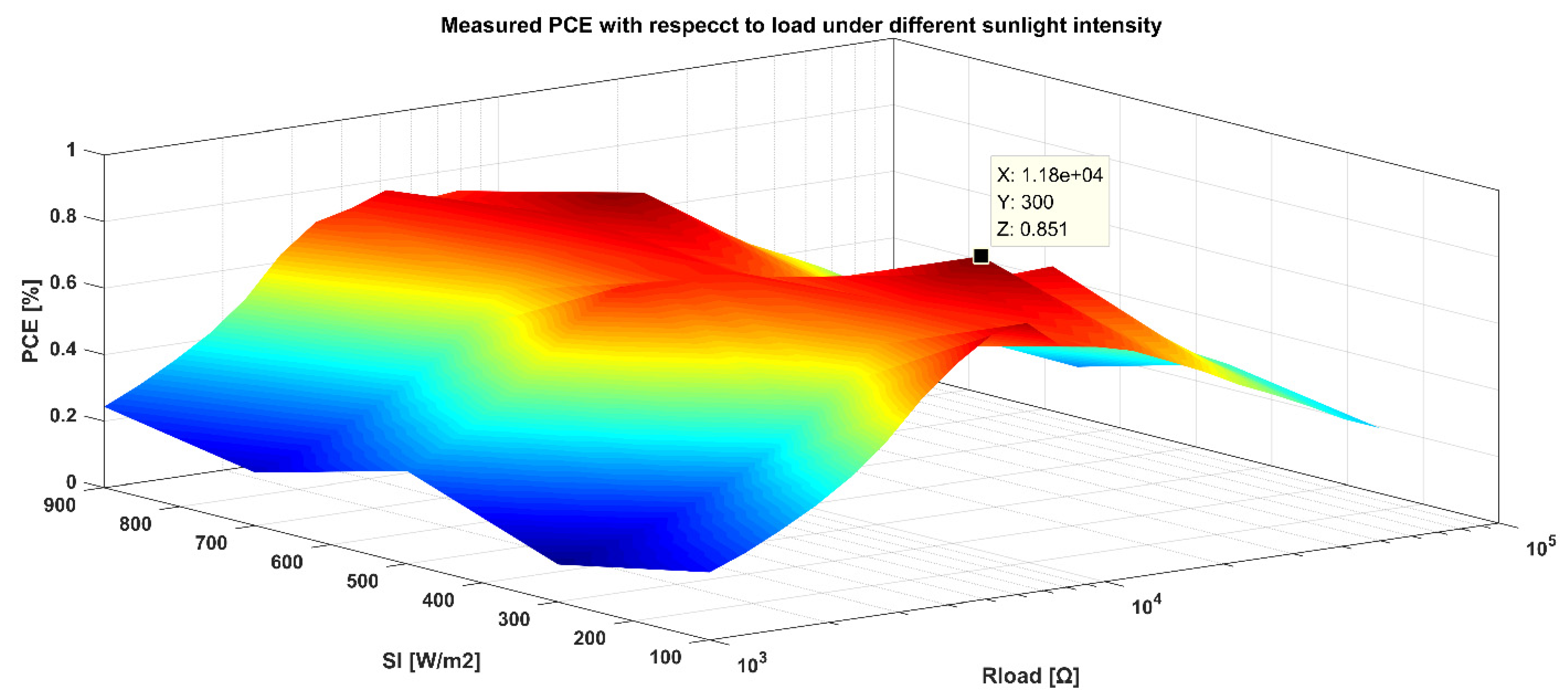

4. Experimental Results and Discussion

5. Discussion and Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Pottie, G.J.; Clare, L.P. Wireless Integrated Network Sensors: Towards Low Cost and Robust Self-Organizing Security Networks. In Sensors, C3I, Information, and Training Technologies for Law Enforcement; International Society for Optics and Photonics: Bellingham, WA, USA, 1999. [Google Scholar]

- Warneke, B.A.; Pister, K.S.J. An ultra-low energy microcontroller for Smart Dust wireless sensor networks. In Proceedings of the 2004 IEEE International Solid-State Circuits Conference (IEEE Cat. No.04CH37519), San Francisco, CA, USA, 15–19 February 2004; Volume 311, pp. 316–317. [Google Scholar]

- Doms, I.; Merken, P.; Mertens, R.; Hoof, C.V. Integrated capacitive power-management circuit for thermal harvesters with output power 10 to 1000 µW. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 300–301. [Google Scholar]

- Wang, W.S.; Donnell, T.O.; Ribetto, L.; Flynn, B.O.; Hayes, M.; Mathuna, C.O. Energy harvesting embedded wireless sensor system for building environment applications. In Proceedings of the 2009 1st International Conference on Wireless Communication, Vehicular Technology, Information Theory and Aerospace & Electronic Systems Technology, Aalborg, Denmark, 17–20 May 2009; pp. 36–41. [Google Scholar]

- Seeman, M.D.; Sanders, S.R.; Rabaey, J.M. An Ultra-Low-Power Power Management IC for Wireless Sensor Nodes. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 567–570. [Google Scholar]

- Ozaki, T.; Hirose, T.; Nagai, T.; Tsubaki, K.; Kuroki, N.; Numa, M. A 0.21-V minimum input, 73.6% maximum efficiency, fully integrated voltage boost converter with MPPT for low-voltage energy harvesters. In Proceedings of the ESSCIRC 2014—40th European Solid State Circuits Conference (ESSCIRC), Venice Lido, Italy, 22–26 September 2014; pp. 255–258. [Google Scholar]

- Ozaki, T.; Hirose, T.; Asano, H.; Kuroki, N.; Numa, M.J.I. A fully-integrated, high-conversion-ratio and dual-output voltage boost converter with MPPT for low-voltage energy harvesting. IEEE J. Solid-State Circuits 2016, 51, 2398–2407. [Google Scholar] [CrossRef]

- Kim, J.; Mok, P.K.T.; Kim, C. A 0.15 V Input Energy Harvesting Charge Pump with Dynamic Body Biasing and Adaptive Dead-Time for Efficiency Improvement. IEEE J. Solid-State Circuits 2015, 50, 414–425. [Google Scholar] [CrossRef]

- Yu, G.; Chew, K.W.R.; Sun, Z.C.; Tang, H.; Siek, L. A 400 nW Single-Inductor Dual-Input–Tri-Output DC–DC Buck–Boost Converter with Maximum Power Point Tracking for Indoor Photovoltaic Energy Harvesting. IEEE J. Solid-State Circuits 2015, 50, 2758–2772. [Google Scholar] [CrossRef]

- Uprety, S.; Lee, H. 22.5 A 93%-power-efficiency photovoltaic energy harvester with irradiance-aware auto-reconfigurable MPPT scheme achieving >95% MPPT efficiency across 650 µW to 1 W and 2.9 ms FOCV MPPT transient time. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 378–379. [Google Scholar]

- Huang, P.; Kuo, T. A Reconfigurable and Extendable Single-Inductor Single-Path Three-Switch Converter for Indoor Photovoltaic Energy Harvesting. IEEE J. Solid-State Circuits 2020, 55, 1998–2008. [Google Scholar] [CrossRef]

- Qiu, Y.; Liempd, C.V.; Veld, B.O.h.; Blanken, P.G.; Hoof, C.V. 5 μW-to-10 mW input power range inductive boost converter for indoor photovoltaic energy harvesting with integrated maximum power point tracking algorithm. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 118–120. [Google Scholar]

- Wu, X.; Shi, Y.; Jeloka, S.; Yang, K.; Lee, I.; Lee, Y.; Sylvester, D.; Blaauw, D. A 20-pW Discontinuous Switched-Capacitor Energy Harvester for Smart Sensor Applications. IEEE J. Solid-State Circuits 2017, 52, 972–984. [Google Scholar] [CrossRef]

- Brito, M.A.G.d.; Galotto, L.; Sampaio, L.P.; e Melo, G.D.A.; Canesin, C.A. Evaluation of the Main MPPT Techniques for Photovoltaic Applications. IEEE Trans. Ind. Electron. 2013, 60, 1156–1167. [Google Scholar] [CrossRef]

- Sher, H.A.; Murtaza, A.F.; Noman, A.; Addoweesh, K.E.; Al-Haddad, K.; Chiaberge, M. A New Sensorless Hybrid MPPT Algorithm Based on Fractional Short-Circuit Current Measurement and P&O MPPT. IEEE Trans. Sustain. Energy 2015, 6, 1426–1434. [Google Scholar] [CrossRef] [Green Version]

- Li, S. A variable-weather-parameter MPPT control strategy based on MPPT constraint conditions of PV system with inverter. Energy Convers. Manag. 2019, 197, 111873. [Google Scholar] [CrossRef]

- Liu, H.-D.; Lin, C.-H.; Pai, K.-J.; Lin, Y.-L. A novel photovoltaic system control strategies for improving hill climbing algorithm efficiencies in consideration of radian and load effect. Energy Convers. Manag. 2018, 165, 815–826. [Google Scholar] [CrossRef]

- Hui, S.; Tsui, C.Y.; Ki, W.H. The Design of a Micro Power Management System for Applications Using Photovoltaic Cells with the Maximum Output Power Control. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2009, 17, 1138–1142. [Google Scholar]

- Kabalci, E.; Boyar, A. Design and Comparison of MPPT Controllers with Fuzzy Logic and Particle Swarm Optimization for PV Power Conversion. In Proceedings of the 2020 2nd International Conference on Control Systems, Mathematical Modeling, Automation and Energy Efficiency (SUMMA), Lipetsk, Russia, 11–13 November 2020. [Google Scholar]

- Chen, P.; Wu, C.; Lin, K. 20.10 A 50 nW-to-10 mW output power tri-mode digital buck converter with self-tracking zero current detection for photovoltaic energy harvesting. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Priyadarshi, N.; Padmanaban, S.; Maroti, P.K.; Sharma, A. An Extensive Practical Investigation of FPSO-Based MPPT for Grid Integrated PV System under Variable Operating Conditions with Anti-Islanding Protection. IEEE Syst. J. 2019, 13, 1861–1871. [Google Scholar] [CrossRef] [Green Version]

- Liu, X.; Ravichandran, K.; Sánchez-Sinencio, E. A Switched Capacitor Energy Harvester Based on a Single-Cycle Criterion for MPPT to Eliminate Storage Capacitor. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 793–803. [Google Scholar] [CrossRef]

- Jung, J.H.; Hong, S.K.; Kwon, O.K. A Highly Reliable SIMO Converter Using Hybrid Starter and Overcharging Protector for Energy Harvesting Systems. IEEE Access 2020, 8, 162172–162179. [Google Scholar] [CrossRef]

- Talkhooncheh, A.H.; Yu, Y.; Agarwal, A.; Kuo, W.; Emami, A. A Fully-Integrated Biofuel-Cell-Based Energy Harvester with 86% Peak Efficiency and 0.25 V Minimum Input Voltage Using Source-Adaptive MPPT. In Proceedings of the 2020 IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 22–25 March 2020. [Google Scholar]

- Aloulou, R.; Lucas De Peslouan, P.O.; Mnif, H.; Alicalapa, F.; Lan Sun Luk, J.D.; Loulou, M. A power management system for energy harvesting and wireless sensor networks application based on a novel charge pump circuit. Int. J. Electron. 2016, 103, 841–852. [Google Scholar] [CrossRef]

- Favrat, P.; Deval, P.; Declercq, M.J. A high-efficiency CMOS voltage doubler. IEEE J. Solid-State Circuits 1998, 33, 410–416. [Google Scholar] [CrossRef]

- Osaki, Y.; Hirose, T.; Kuroki, N.; Numa, M. Temperature-Compensated NanoAmpere Current Reference Circuit with Subthreshold MetalOxideSemiconductor Field-Effect Transistor Resistor Ladder. Jpn. J. Appl. Phys. 2011, 50, 584–587. [Google Scholar] [CrossRef]

- Duan, Q.; Wang, X.; Huang, S.; Ding, Y.; Meng, Z.; Shi, K.J. 0.55–1.8 V, 7.5 nW, 225.5 mV, CMOS-only subthreshold voltage reference. Electron. Lett. 2019, 55, 306–308. [Google Scholar] [CrossRef]

- Osaki, Y.; Hirose, T.; Kuroki, N.; Numa, M. Nano-ampere CMOS current reference with little temperature dependence using small offset voltage. In Proceedings of the IEEE International Midwest Symposium on Circuits & Systems, Seattle, WA, USA, 1–4 August 2010. [Google Scholar]

- Ueno, K.; Hirose, T.; Asai, T.; Amemiya, Y. A 300 nW, 15 ppm/°C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. IEEE J. Solid-State Circuits 2009, 44, 2047–2054. [Google Scholar] [CrossRef]

- Lacorte, W.B.; Manalo, R.M. A Sub-1-V, High PSRR, Subthreshold MOSFET-only Voltage Reference for Wireless Sensor Networks. In Proceedings of the TENCON 2019—2019 IEEE Region 10 Conference (TENCON), Kochi, India, 17–20 October 2019. [Google Scholar]

| Device | Parameter |

|---|---|

| MN1/MN2 | 80/0.5 |

| MP1/MP2 | 100/0.5 |

| C1 | 5 pF |

| Cfly | 200 pF |

| Properties | [7] | [8] | [12] | [13] | This Work |

|---|---|---|---|---|---|

| CMOS process | 0.18 um | 0.13 um | 0.25 um | 0.18 um | 0.35 um |

| Chip area | 1.6 × 1.1 | 0.066 | 3.4 × 3.4 | 1.6 × 1.7 | 3.15 × 2.43 |

| Input voltage | 0.5–0.6 V | 0.15 | 0.5~2 V | <0.6 V | 0.5–1.8 V |

| Output voltage | 1.8/4.2 V | 0.619 | 0~5 V | 1.8/3 V | 1.5–5.4 V |

| PCE | 75.8%/49.1% | 72.5% | 87% | 50% | 85.1% |

| MPPT | yes | no | yes | yes | yes |

| Fully integrated | yes | yes | no | no | yes |

| Boost device | cap | cap | ind | - | cap |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, X.; Fu, Q.; Yang, R.; Zhang, Y. A High Power-Conversion-Efficiency Voltage Boost Converter with MPPT for Wireless Sensor Nodes. Sensors 2021, 21, 5447. https://doi.org/10.3390/s21165447

Zhu X, Fu Q, Yang R, Zhang Y. A High Power-Conversion-Efficiency Voltage Boost Converter with MPPT for Wireless Sensor Nodes. Sensors. 2021; 21(16):5447. https://doi.org/10.3390/s21165447

Chicago/Turabian StyleZhu, Xiwen, Qiang Fu, Ruimo Yang, and Yufeng Zhang. 2021. "A High Power-Conversion-Efficiency Voltage Boost Converter with MPPT for Wireless Sensor Nodes" Sensors 21, no. 16: 5447. https://doi.org/10.3390/s21165447

APA StyleZhu, X., Fu, Q., Yang, R., & Zhang, Y. (2021). A High Power-Conversion-Efficiency Voltage Boost Converter with MPPT for Wireless Sensor Nodes. Sensors, 21(16), 5447. https://doi.org/10.3390/s21165447