Voltage-Frequency Domain Optimization for Energy-Neutral Wearable Health Devices

Abstract

:1. Introduction

- A technique that finds the energy-optimal voltage and frequency levels for a given design and VF domain partition;

- An exact algorithm and an efficient heuristic to find the optimum VF domain configuration; and,

- Experimental evaluation on three applications: two activity monitoring applications implemented using TSMC 65 nm LP technology and a low-power ECG application from the literature.

2. Related Work

3. Overview and Problem Formulation

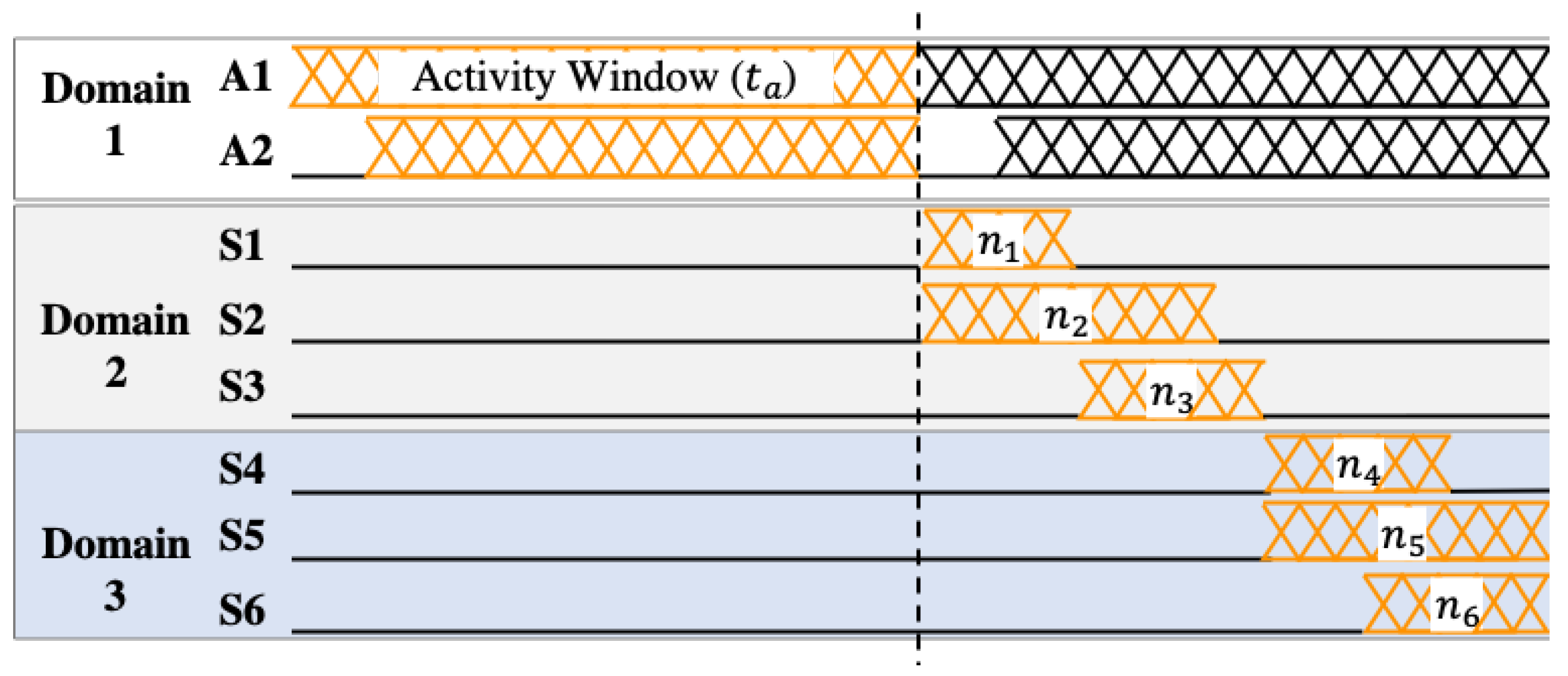

3.1. Application Model

3.2. Problem Formulation

- Given: A design with and ,

- Find:

- (1)

- The number (N) and set of voltage-frequency domains ;

- (2)

- The mapping of the modules to domains;

- (3)

- The voltage and frequency of each module

- Such that:

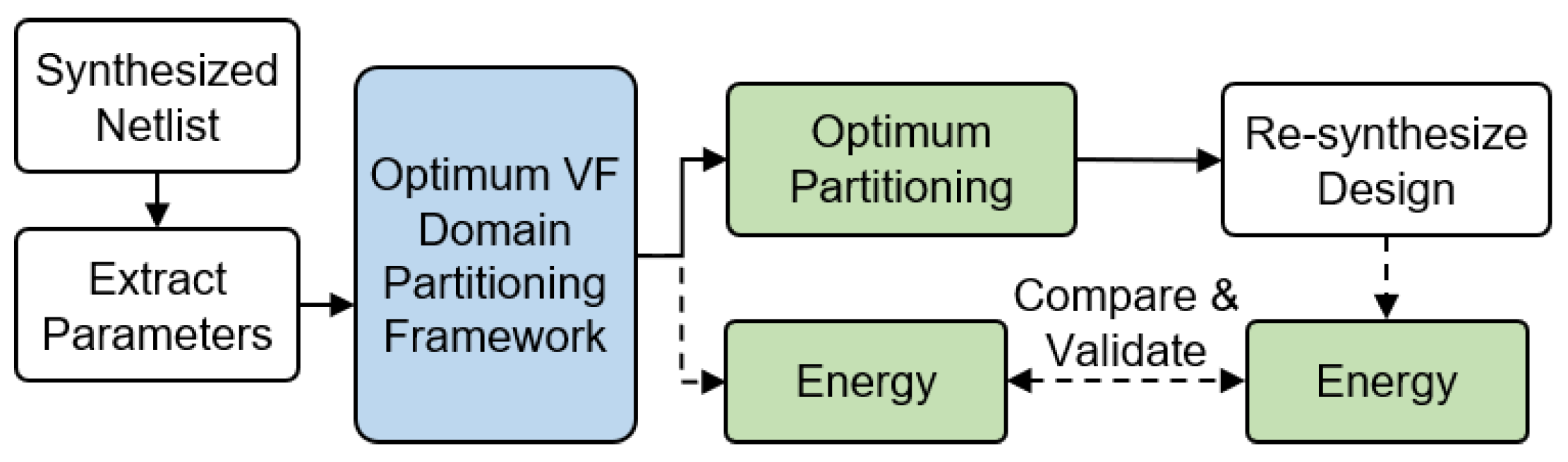

4. Optimal VF Domain Design

4.1. Optimal Voltage and Frequency in a Domain

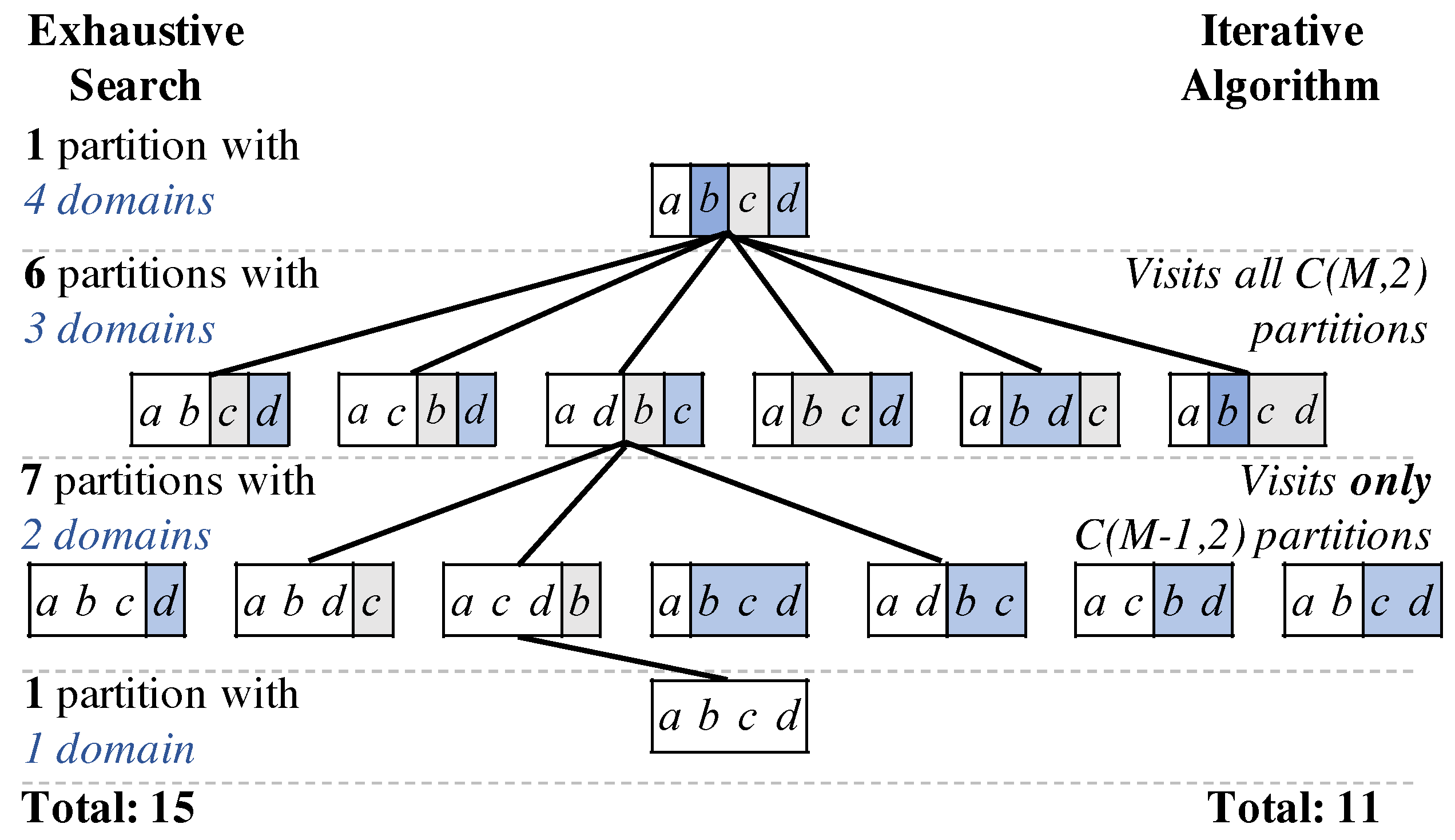

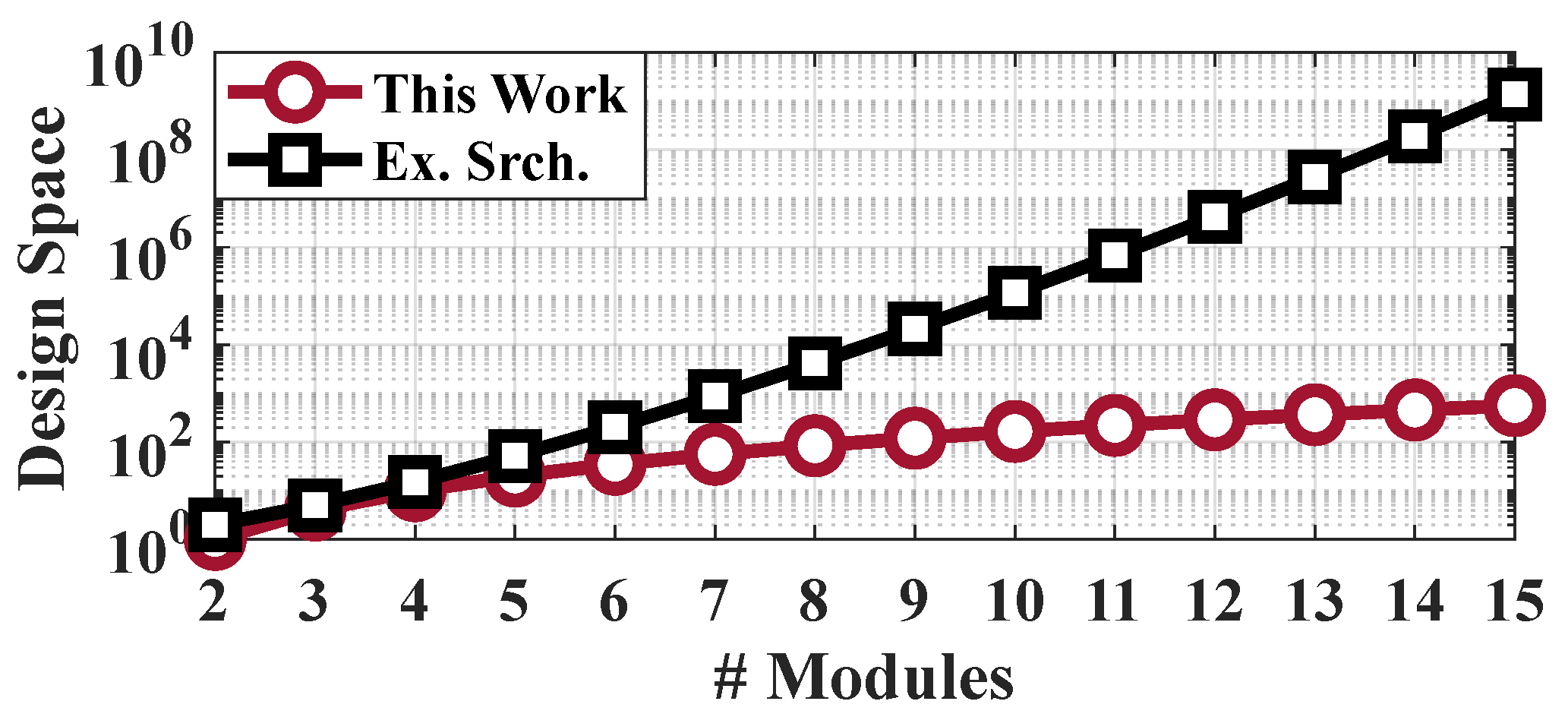

4.2. Optimum VF Domain Partitioning

5. Experimental Results

5.1. Experimental Setup

5.1.1. Driver Applications

5.1.2. Experimental Methodology

5.2. Activity Monitoring Application

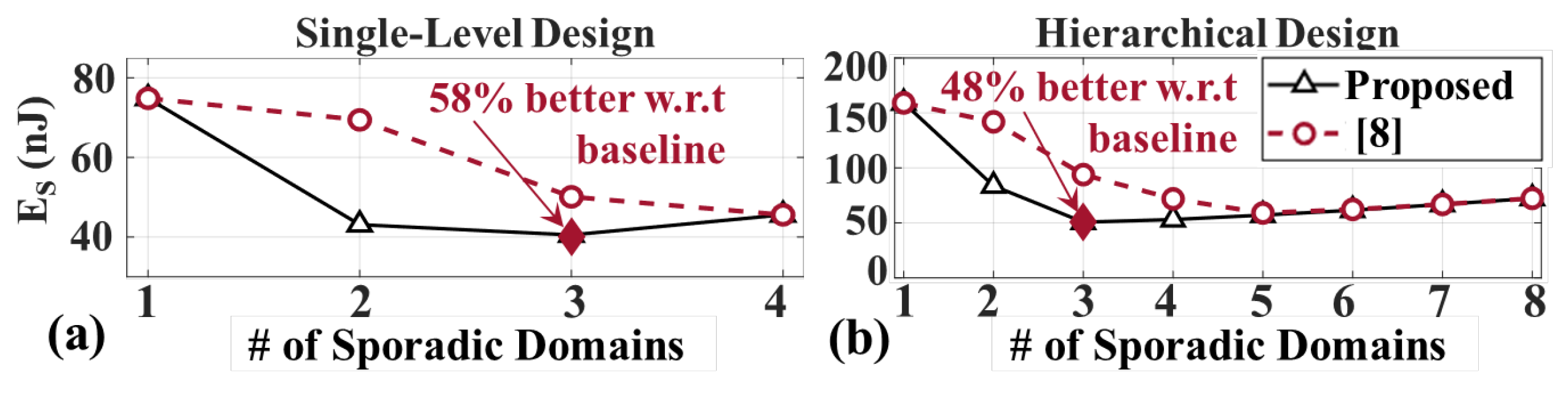

5.2.1. Single-Level Activity Monitoring Design

5.2.2. Hierarchical Activity Monitoring Design

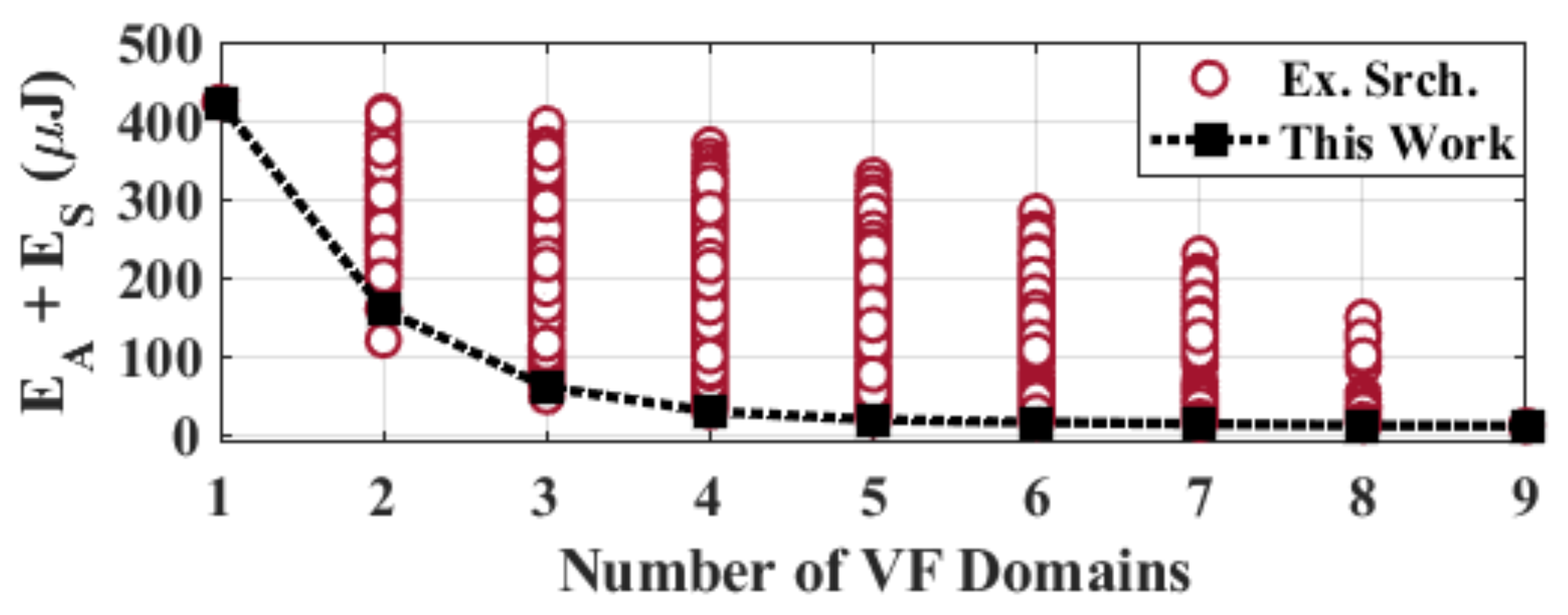

5.3. Optimization Results

5.3.1. Energy Overhead of VF Domains

5.3.2. Single-Level Activity Monitoring Design

5.3.3. Hierarchical Activity Monitoring Design

5.3.4. ECG Application Validation

5.4. Validation of the Framework

5.5. Discussion of the Results

5.5.1. Wider Applicability of the Proposed Framework

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Yazicioglu, R.F.; Kim, S.; Torfs, T.; Kim, H.; Van Hoof, C. A 30 μW Analog Signal Processor ASIC for Portable Biopotential Signal Monitoring. IEEE J. Solid-State Circuits 2010, 46, 209–223. [Google Scholar] [CrossRef]

- Tricoli, A.; Nasiri, N.; De, S. Wearable and Miniaturized Sensor Technologies for Personalized and Preventive Medicine. Adv. Funct. Mater. 2017, 27, 1605271. [Google Scholar] [CrossRef]

- Ozanne, A.; Johansson, D.; Graneheim, U.H.; Malmgren, K.; Bergquist, F.; Murphy, M.A. Wearables in Epilepsy and Parkinson’s disease—A Focus Group Study. Acta Neurol. Scand. 2018, 137, 188–194. [Google Scholar] [CrossRef] [PubMed]

- De Lima, A.L.S.; Hahn, T.; Evers, L.J.; De Vries, N.M.; Cohen, E.; Afek, M.; Bataille, L.; Daeschler, M.; Claes, K.; Boroojerdi, B.; et al. Feasibility of Large-Scale Deployment of Multiple Wearable Sensors in Parkinson’s Disease. PLoS ONE 2017, 12, e0189161. [Google Scholar]

- Wang, A.; Chen, G.; Yang, J.; Zhao, S.; Chang, C.-Y. A Comparative Study on Human Activity Recognition Using Inertial Sensors in a Smartphone. IEEE Sens. J. 2016, 16, 4566–4578. [Google Scholar] [CrossRef]

- Bhat, G.; Deb, R.; Chaurasia, V.V.; Shill, H.; Ogras, U.Y. Online human activity recognition using low-power wearable devices. In Proceedings of the 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Diego, CA, USA, 5–8 November 2018; pp. 1–8. [Google Scholar]

- Bhat, G.; Tuncel, Y.; An, S.; Lee, H.G.; Ogras, U.Y. An Ultra-Low Energy Human Activity Recognition Accelerator for Wearable Health Applications. ACM Trans. Embed. Comput. Syst. (TECS) 2019, 18, 1–22. [Google Scholar] [CrossRef]

- Ogras, U.Y.; Marculescu, R.; Choudhary, P.; Marculescu, D. Voltage-Frequency Island Partitioning for GALS-Based Networks-on-chip. In Proceedings of the 44th ACM/IEEE Design Automation Conference, San Diego, CA, USA, 4–8 June 2007; pp. 110–115. [Google Scholar]

- Valenzuela, A. Energy Harvesting for No-Power Embedded Systems. 2008. Available online: http://focus.ti.com/graphics/mcu/ulp/energy_harvesting_embedded_systems_using_msp430.pdf (accessed on 31 July 2019).

- Geisler, M.; Boisseau, S.; Perez, M.; Gasnier, P.; Willemin, J.; Ait-Ali, I.; Perraud, S. Human-Motion Energy Harvester for Autonomous Body Area Sensors. Smart Mater. Struct. 2017, 557, 012024. [Google Scholar] [CrossRef]

- Tuncel, Y.; Bandyopadhyay, S.; Kulshrestha, S.V.; Mendez, A.; Ogras, U.Y. Towards wearable piezoelectric energy harvesting: Modeling and experimental validation. In Proceedings of the ACM/IEEE International Symposium on Low Power Electronics and Design, Boston, MA, USA, 10–12 August 2020; pp. 55–60. [Google Scholar]

- Goodrick, K.J.; Maksimović, D. Systematic Optimization of Multiple Voltage Domain DC Distribution Architectures. In Proceedings of the 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), Padua, Italy, 25–28 June 2018; pp. 1–8. [Google Scholar]

- Blutman, K.; Fatemi, H.; Kapoor, A.; Kahng, A.B.; Li, J.; De Gyvez, J.P. Logic Design Partitioning for Stacked Power Domains. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 3045–3056. [Google Scholar] [CrossRef]

- Agarwal, A.; Arvind. Leveraging Rule-Based Designs for Automatic Power Domain Partitioning. In Proceedings of the 2013 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 18–21 November 2013; pp. 326–333. [Google Scholar]

- Wang, B.; Xu, Y.; Hasholzner, R.; Drewes, C.; Rosales, R.; Graf, S.; Falk, J.; Glaß, M.; Teich, J. Exploration of Power Domain Partitioning for Application-Specific SoCs in System-Level Design. In Proceedings of the 19th GI/ITG/GMM Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV), Freiburg im Breisgau, Germany, 1–2 March 2016; pp. 102–113. [Google Scholar]

- Hanson, S.; Seok, M.; Lin, Y.-S.; Foo, Z.; Kim, D.; Lee, Y.; Liu, N.; Sylvester, D.; Blaauw, D. A Low-Voltage Processor for Sensing Applications with Picowatt Standby Mode. IEEE JSSC 2009, 44, 1145–1155. [Google Scholar] [CrossRef]

- Klinefelter, A.; Roberts, N.E.; Shakhsheer, Y.; González, P.; Shrivastava, A.; Roy, A.; Craig, K.; Faisal, M.; Boley, J.; Oh, S.; et al. A 6.45 μW Self-Powered IoT SoC with Integrated Energy-Harvesting Power Management and ULP Asymmetric Radios. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 384–385. [Google Scholar]

- Shang, L.; Peh, L.S.; Jha, N.K. Dynamic Voltage Scaling with Links for Power Optimization of Interconnection Networks. In Proceedings of the 9th International Symposium on High-Performance Computer Architecture (HPCA), Anaheim, CA, USA, 12 February 2003; pp. 91–102. [Google Scholar]

- Berend, D.; Tassa, T. Improved Bounds on Bell Numbers and on Moments of Sums of Random Variables. Prob. Math. Stat. 2010, 30, 185–205. [Google Scholar]

- Jang, W.; Pan, D.Z. A Voltage-Frequency Island Aware Energy Optimization Framework for Networks-on-Chip. IEEE Trans. Emerg. Sel. Top. Circuits Syst. 2011, 1, 420–432. [Google Scholar] [CrossRef]

- Liu, W.; Salman, E.; Sitik, C.; Taskin, B. Enhanced Level Shifter for Multi-Voltage Operation. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 1442–1445. [Google Scholar] [CrossRef]

- Hsu, C.P. A Practical Guide to Low-Power Design. Available online: https://projects.si2.org/events_dir/2009/PowerForward/LowPowerGuide09232009/pfi_lpg_chapters/lpg_sect1_06052009.pdf (accessed on 20 March 2020).

- Kim, W.; Gupta, M.S.; Wei, G.Y.; Brooks, D. System Level Analysis Of Fast, Per-Core DVFS Using On-Chip Switching Regulators. In Proceedings of the 2008 IEEE 14th International Symposium on High Performance Computer Architecture (HPCA), Salt Lake City, UT, USA, 16–20 February 2008; pp. 123–134. [Google Scholar]

| Symbol | Description | Symbol | Description |

|---|---|---|---|

| Set of always-on and sporadic modules, respectively | Total energy of always-on modules | ||

| Total energy of sporadic modules | Switching factor of module m | ||

| Capacitance of module m | M | Total no. of modules | |

| Leakage current of module m | Activity window duration | ||

| Active cycles of module m | Set of all domains | ||

| Voltage of module m | Frequency of module m | ||

| Exe. time of a module at a given frequency | Maximum allowed exe. time of a module m | ||

| Minimum frequency of module m | Optimum frequency for module m |

| A1 | A2 | A3 | A4 | A5 | |

|---|---|---|---|---|---|

| I (nA) | 80 | 100 | 1000 | 10 | 50 |

| C (pF) | 3.41 | 11.20 | 89.30 | 1.02 | 3.55 |

| (kHz) | 3 | 1 | 1 | 3 | 10 |

| (a) | ||||

| S1 | S2 | S3 | S4 | |

| I (nA) | 71 | 1000 | 1000 | 700 |

| C (pF) | 5 | 100 | 43 | 35 |

| Cycles | 109 | 163 | 25 | 252 |

| (b) | ||||||||

| S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | |

| I (nA) | 722 | 755 | 417 | 182 | 36 | 2670 | 123 | 866 |

| C (pF) | 58 | 29 | 41 | 7 | 5 | 193 | 9 | 81 |

| Cycles | 252 | 25 | 4 | 5 | 252 | 21 | 109 | 145 |

| ECG (2) | Single-Level Design (4) | Hierarchical Design (8) | |

|---|---|---|---|

| Exhaustive Search | 15 ms | 54 ms | 7.70 s |

| [8] | 0.20 ms | 10 ms | 0.05 s |

| This Work | 0.01 ms | 8 ms | 0.20 s |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tuncel, Y.; An, S.; Bhat, G.; Raja, N.; Lee, H.G.; Ogras, U. Voltage-Frequency Domain Optimization for Energy-Neutral Wearable Health Devices. Sensors 2020, 20, 5255. https://doi.org/10.3390/s20185255

Tuncel Y, An S, Bhat G, Raja N, Lee HG, Ogras U. Voltage-Frequency Domain Optimization for Energy-Neutral Wearable Health Devices. Sensors. 2020; 20(18):5255. https://doi.org/10.3390/s20185255

Chicago/Turabian StyleTuncel, Yigit, Sizhe An, Ganapati Bhat, Naga Raja, Hyung Gyu Lee, and Umit Ogras. 2020. "Voltage-Frequency Domain Optimization for Energy-Neutral Wearable Health Devices" Sensors 20, no. 18: 5255. https://doi.org/10.3390/s20185255

APA StyleTuncel, Y., An, S., Bhat, G., Raja, N., Lee, H. G., & Ogras, U. (2020). Voltage-Frequency Domain Optimization for Energy-Neutral Wearable Health Devices. Sensors, 20(18), 5255. https://doi.org/10.3390/s20185255