Design of a Labeling Scheme for 32-QAM Delayed Bit-Interleaved Coded Modulation

Abstract

1. Introduction

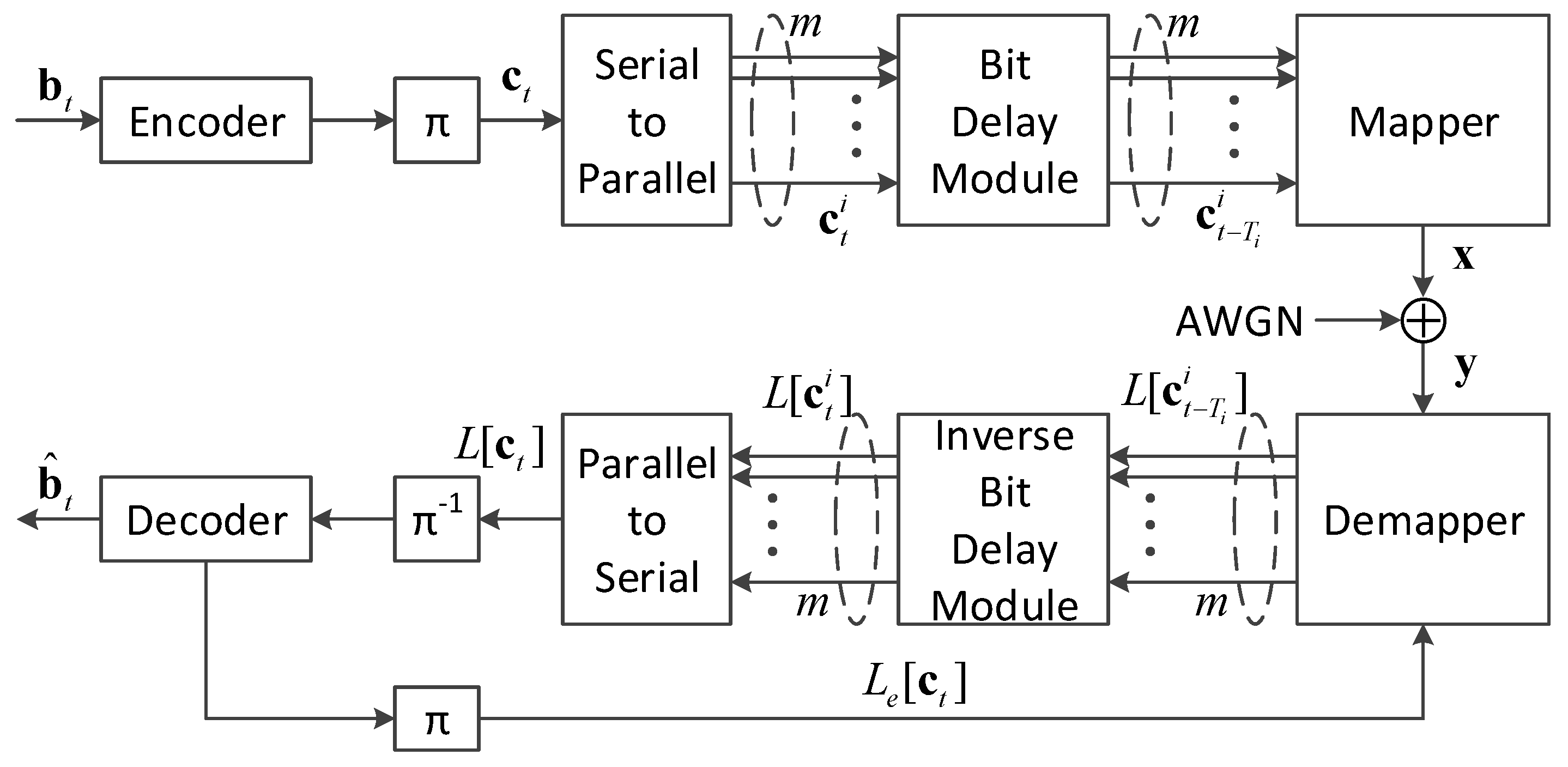

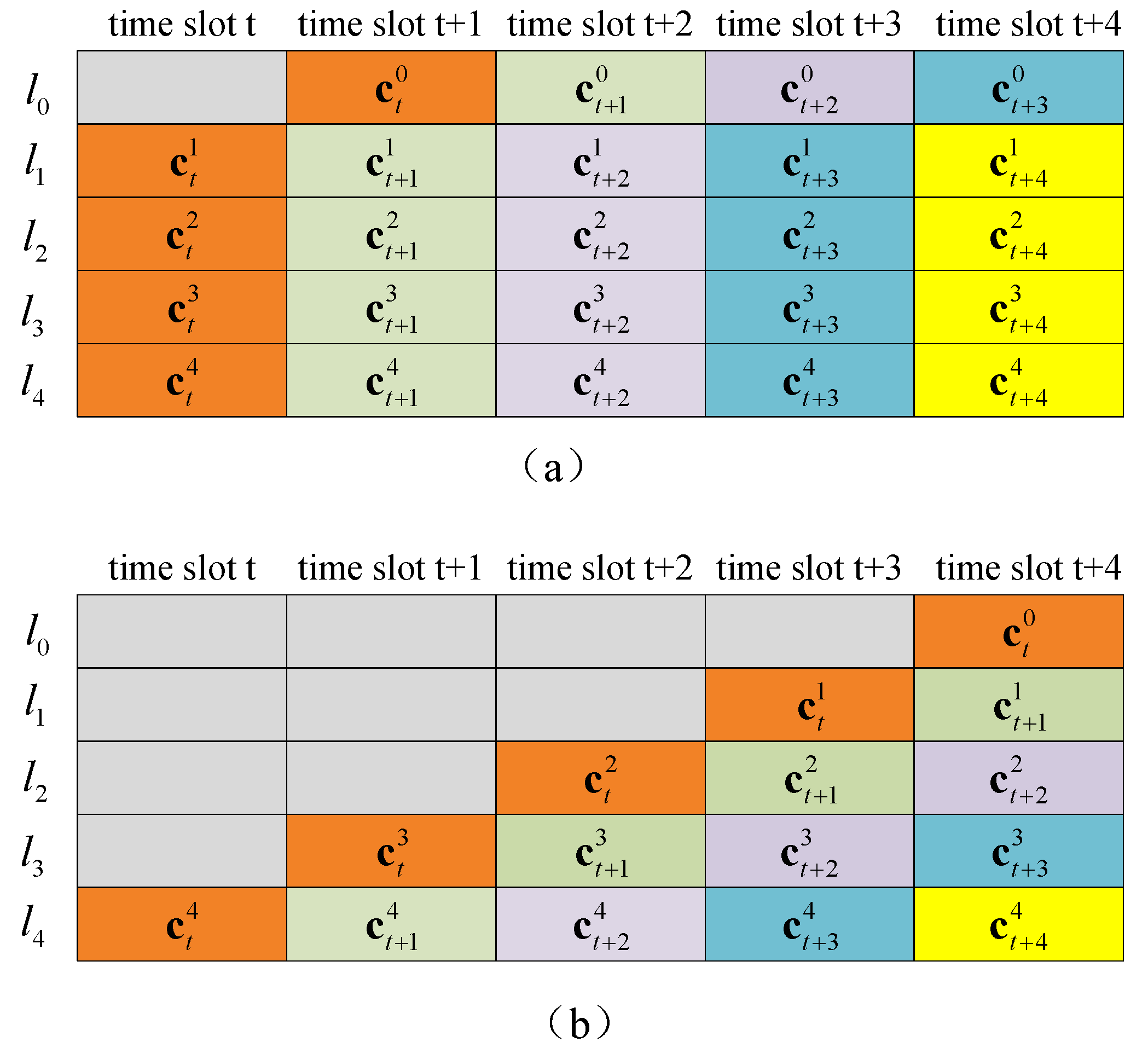

2. Delayed Bit-Interleaved Coded Modulation

3. Channel Capacity Analysis and Delay Pattern Selection

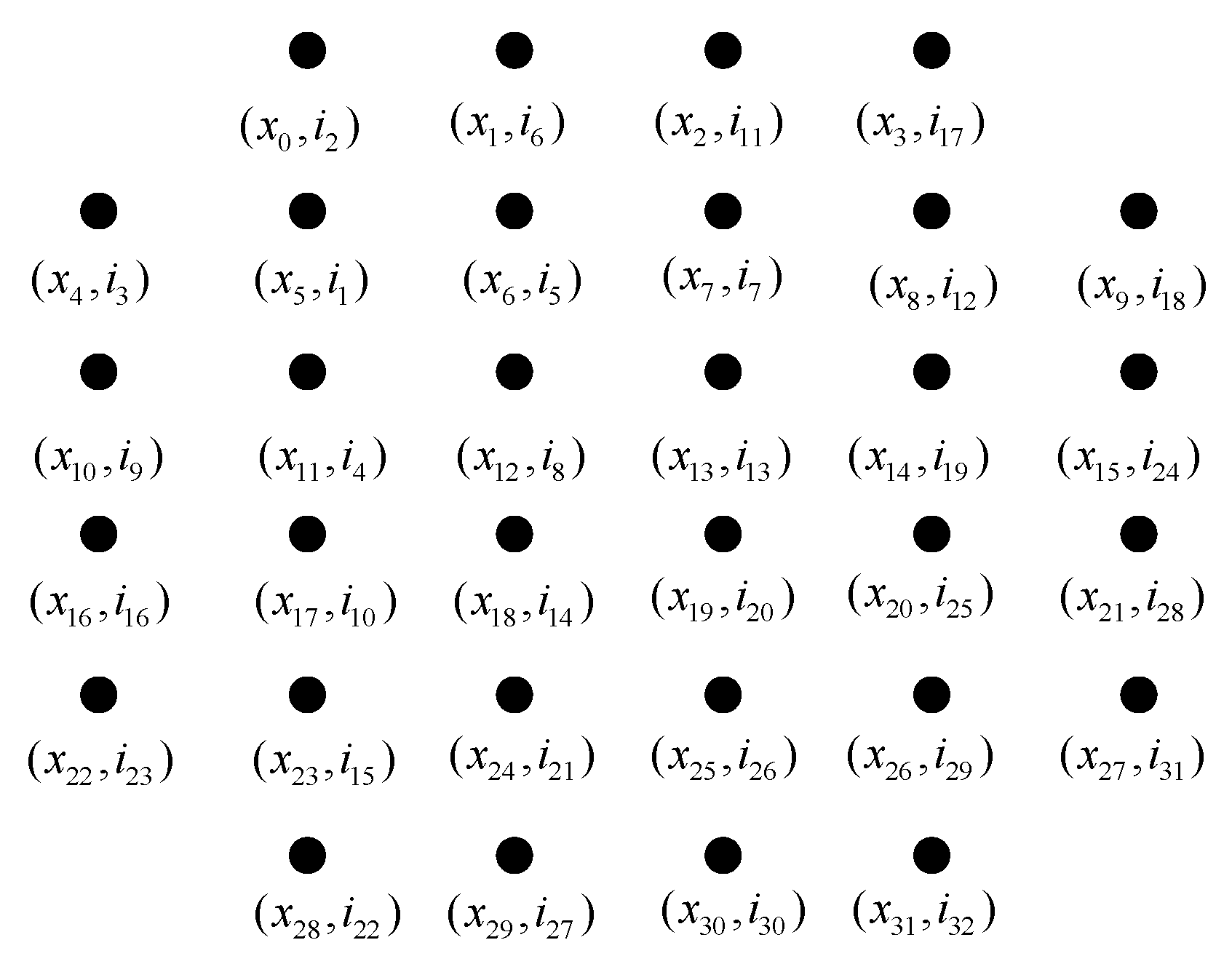

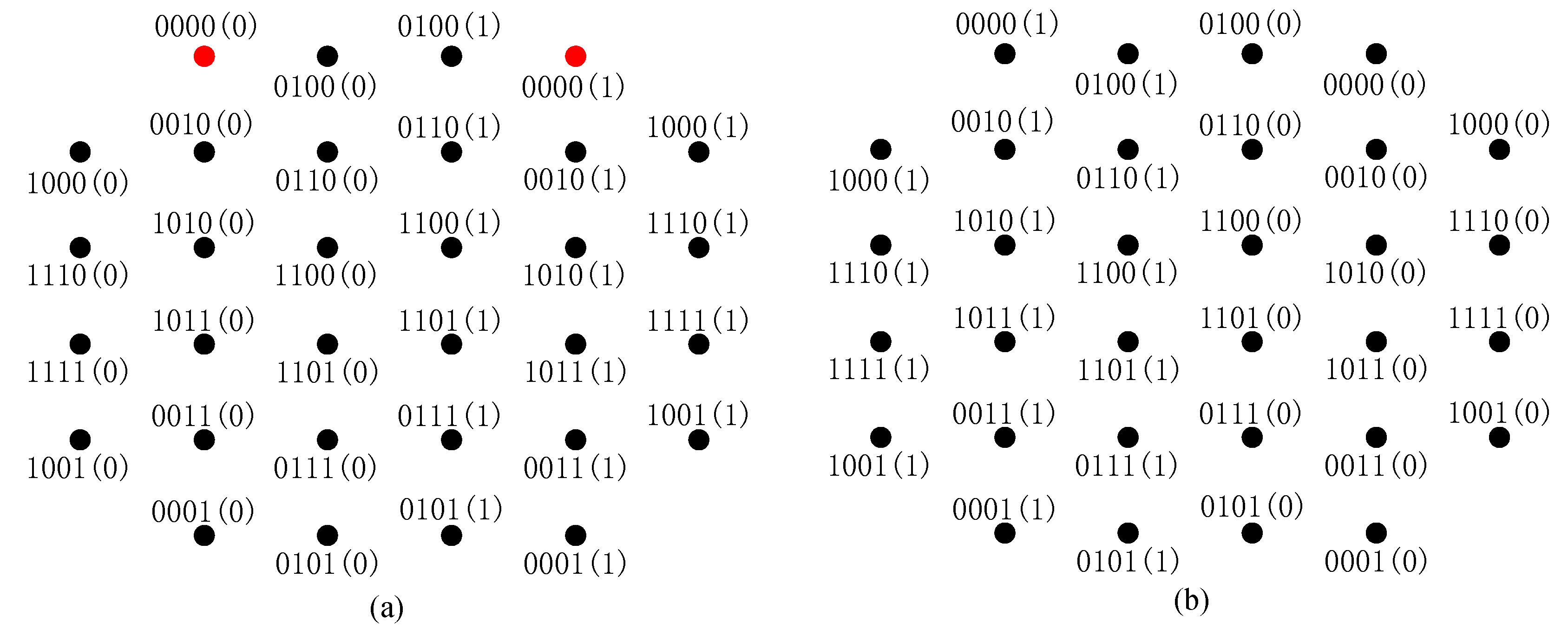

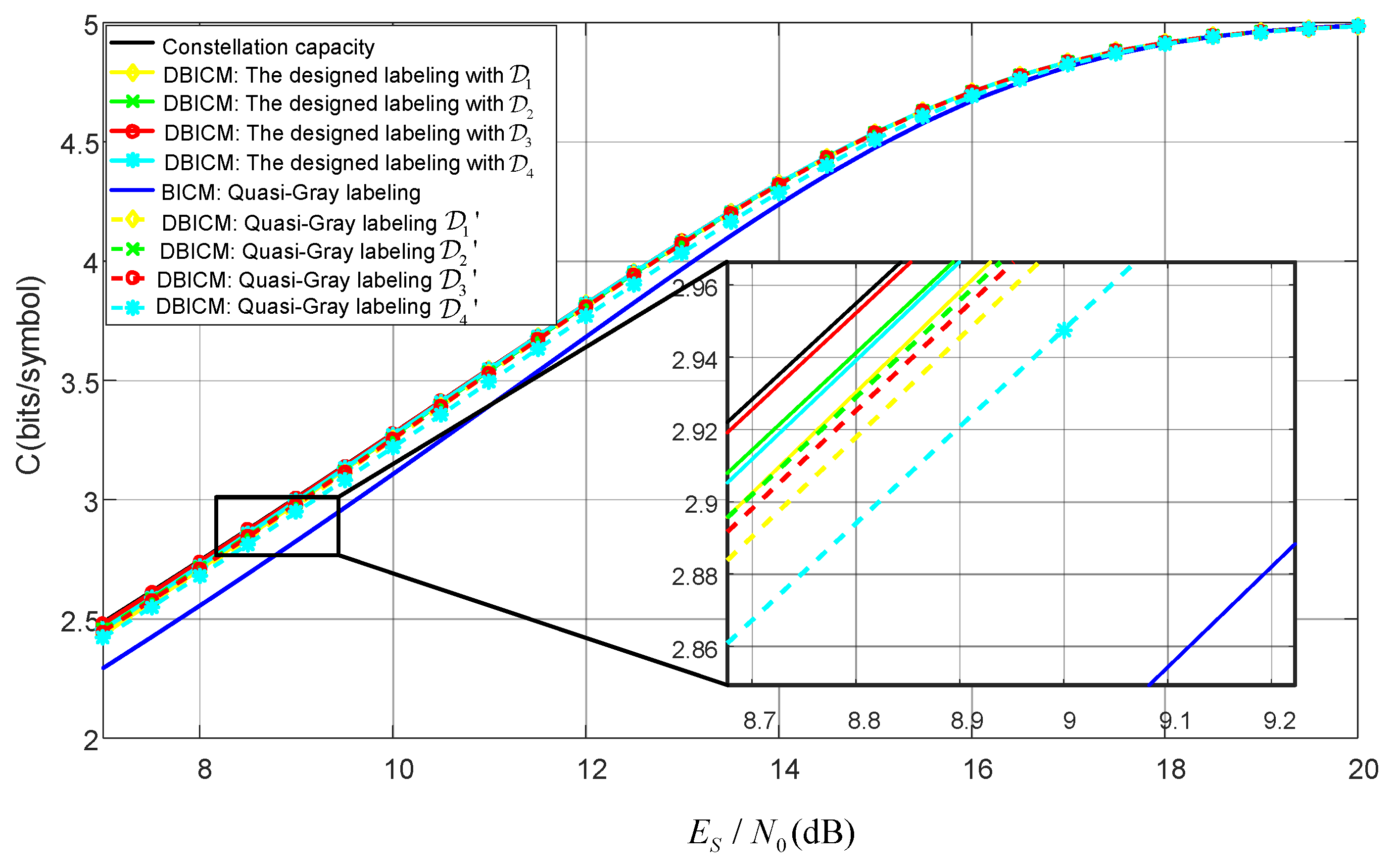

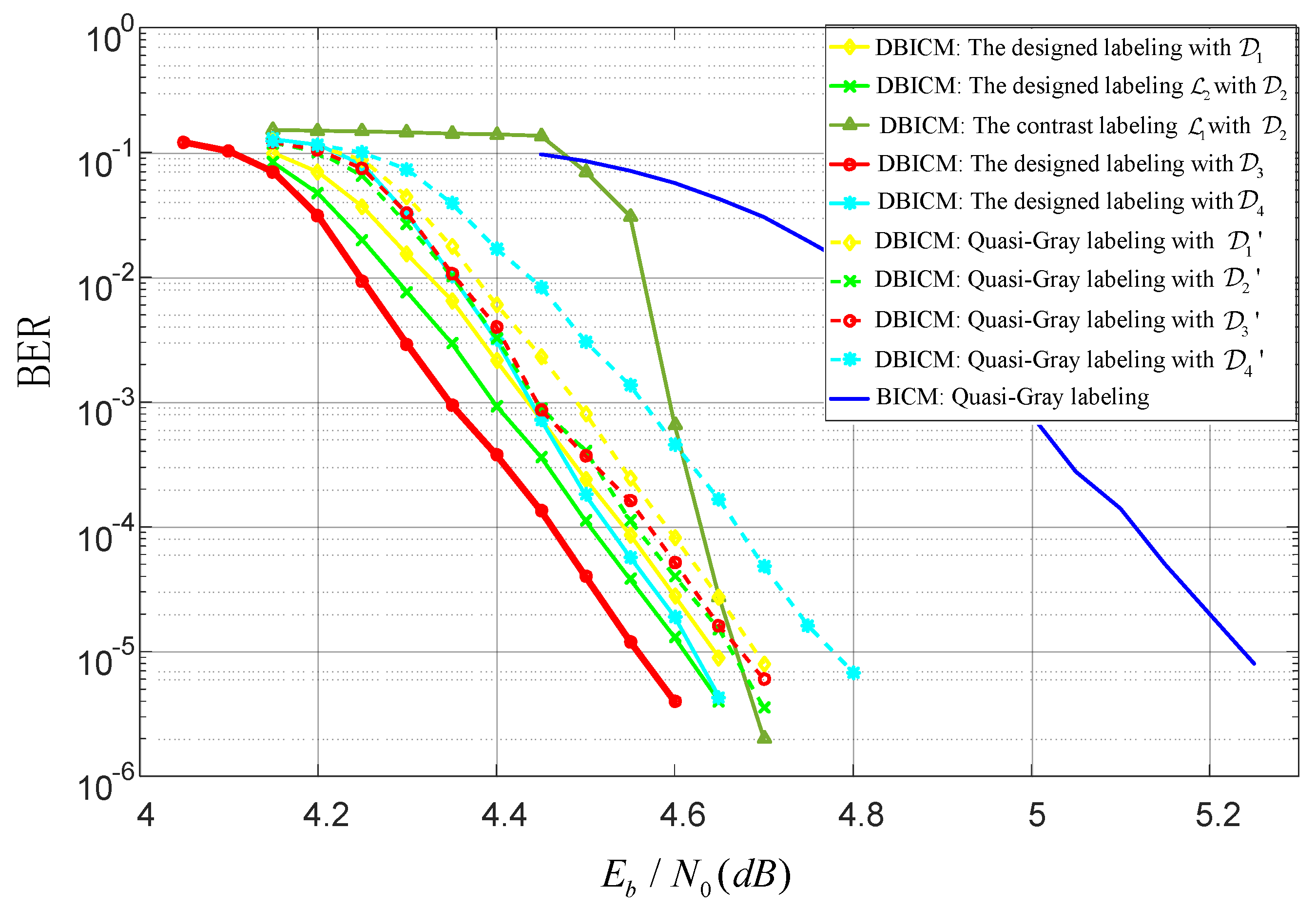

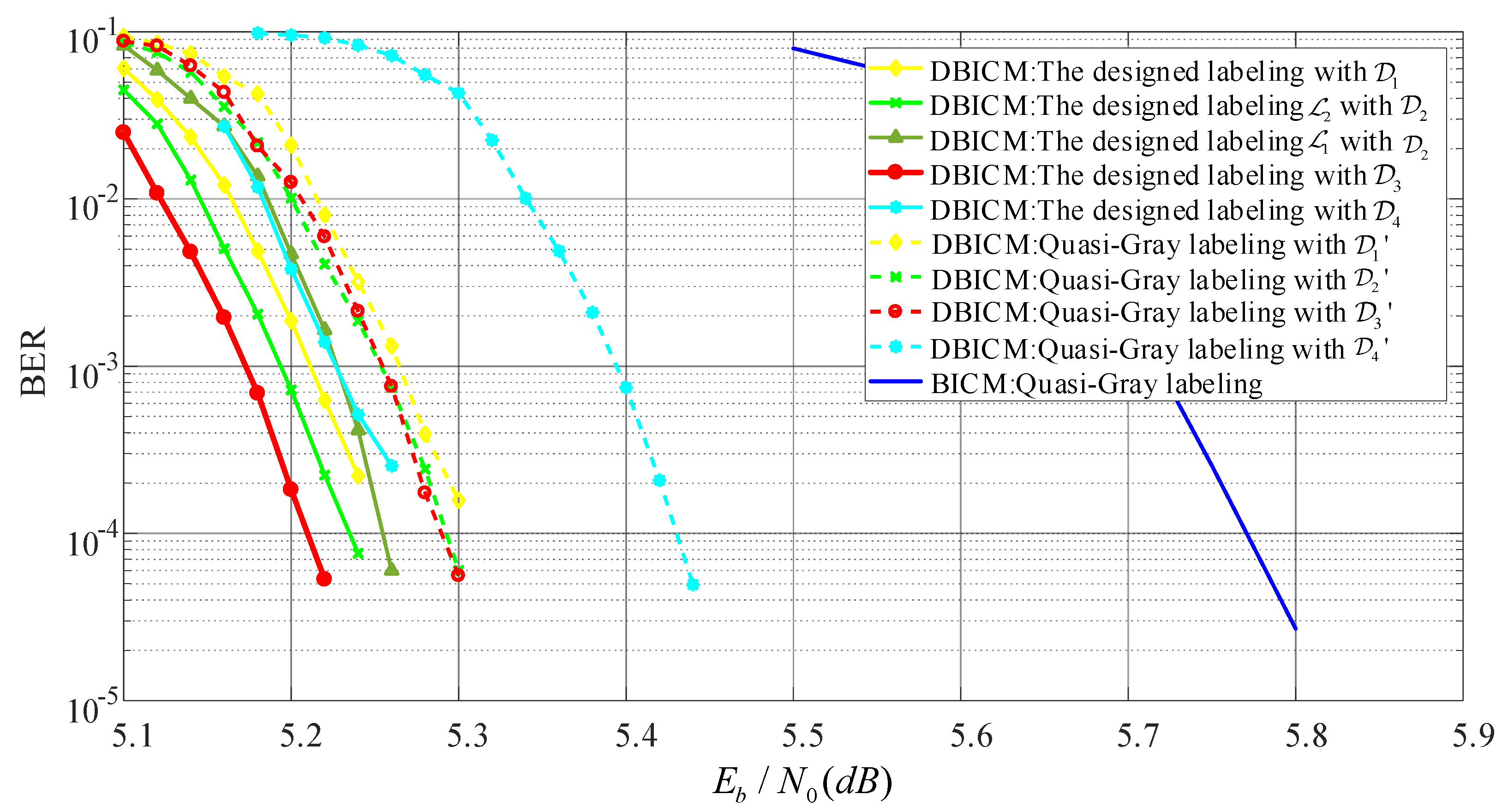

4. Design of the Labeling Scheme

4.1. Labeling Search Criteria

4.1.1. Partial Gray Labeling Scheme

4.1.2. Criterion for Optimal Labeling Schemes

- The PLS of delayed bits , i.e., , should be a PGLS.

- The labeling of undelayed bits should satisfy the Gray labeling rule in the sub-constellations for all .

4.1.3. Criteria for Good Labeling Schemes

4.2. Good Labeling Search Guideline

4.3. Search Algorithm for Good Labeling Schemes

4.4. Capacity Equivalent Labeling Schemes

5. Numerical Results

5.1. The Proposed Labeling Schemes

5.2. The Channel Capacity

5.3. BER Performance

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| QAM | Quadrature amplitude modulation |

| DBICM | Delayed bit-interleaved coded modulation |

| BICM | Bit-interleaved coded modulation |

| CM | Coded modulation |

| ASK | Amplitude-shift keying |

| BICM-ID | Bit-interleaved coded modulation iterative decoding |

| BER | Bit error rate |

| LDPC | Low density parity check |

| AWGN | Additive white Gaussian noise |

| LLR | Log-likelihood ratio |

| SNR | Signal-to-noise ratio |

| MI | Mutual information |

| PL | Partial label |

| PLS | Partial labeling scheme |

| PGLS | Partial Gray labeling scheme |

| SELS | Strictly equivalent labeling schemes |

| CELS | Capacity equivalent labeling schemes |

| PEG | Progressive edge-growth |

Appendix A. The Three-Step Search Algorithm

Appendix A.1. The PGLS Search Step

| Algorithm 1 Depth-first bit-labeling search. |

| Input:The assignment order I; |

| The label candidate set B. |

| Output: The 4 bit PGL schemes set . |

| 1: begin procedure |

| 2: initialize: let , ; set ; |

| 3: find ; |

| 4: if then |

| 5: go to 14; |

| 6: end if |

| 7: for do |

| 8: , , ; |

| 9: if then |

| 10: record the partial Gray labeling schemes in ; |

| 11: go to 14; |

| 12: end if |

| 13: return to 3; |

| 14: , ; |

| 15: end for |

| 16: return . |

| Algorithm 2 The assignment order. |

| Input:The numbered points of constellation ; |

| The label candidate set B. |

| Output:The assignment order . |

| 1: begin procedure |

| 2: initialize: let , , , ; set ; |

| 3: for do |

| 4: find for ; |

| 5: end for |

| 6: find one with minimum size in , and denote it as ; |

| 7: if there are multiple sets having the minimum number of legal PLs, one is selected randomly; |

| 8: let ; |

| 9: assign with a random label in ; |

| 10: , ; |

| 11: if then |

| 12: go to 16; |

| 13: else |

| 14: , go to 3; |

| 15: end if |

| 16: return I. |

Appendix A.1.1. The Full Labeling Generation Step

Appendix A.1.2. The Final Step

References

- Caire, G.; Taricco, G.; Biglieri, E. Bit-interleaved coded modulation. IEEE Trans. Inf. Theory 1998, 44, 927–946. [Google Scholar] [CrossRef]

- Du, J.; Zhou, L.; He, X. The joint demodulation and decoding for BICM-ID system with BEC approximation and optimized bit mapping. In Proceedings of the 2015 IEEE Global Communications Conference (GLOBECOM), San Diego, CA, USA, 6–10 December 2015. [Google Scholar]

- Du, J.; Yang, L.; Yuan, J.; Zhou, L.; He, X. Bit mapping design for LDPC coded BICM schemes with multi-edge type EXIT chart. IEEE Commun. Lett. 2017, 21, 722–725. [Google Scholar] [CrossRef]

- Hou, J.; Siegel, P.H.; Milstein, L.B.; Pfister, H.D. Capacity-approaching bandwidth-efficient coded modulation schemes based on low-density parity-check codes. IEEE Trans. Inf. Theory 2003, 49, 2141–2155. [Google Scholar]

- Zhao, Y.; Fang, Y.; Yang, Z. Interleaver Design for Small-Coupling-Length Spatially Coupled Protograph LDPC-Coded BICM Systems Over Wireless Fading Channels. IEEE Access 2020, 8, 33500–33510. [Google Scholar] [CrossRef]

- He, Y.; Jiang, M.; Ling, X.; Zhao, C. Robust BICM Design for the LDPC Coded DCO-OFDM: A Deep Learning Approach. IEEE Trans. Commun. 2020, 68, 713–727. [Google Scholar] [CrossRef]

- Zehavi, E. 8-PSK trellis codes for a Rayleigh channel. IEEE Trans. Commun. 1992, 40, 873–884. [Google Scholar] [CrossRef]

- Ungerboeck, G. Channel coding with multilevel/phase signals. IEEE Trans. Inf. Theory 1982, 28, 55–67. [Google Scholar] [CrossRef]

- Wesel, D.; Liu, X. Edge profile optimal constellation labeling. In Proceedings of the 2000 IEEE International Conference on Communications (ICC 2000): Global Convergence Through Communications, Conference Record, New Orleans, LA, USA, 18–22 June 2000. [Google Scholar]

- Wesel, D.; Liu, X.; Cioffi, J.M.; Komninakis, C. Constellation labeling for linear encoders. IEEE Trans. Inf. Theory 2001, 47, 2417–2431. [Google Scholar] [CrossRef]

- Yang, Z.; Xie, Q.; Peng, K.; Song, J. Labeling schemes optimization for BICM-ID systems. IEEE Commun. Lett. 2010, 14, 1047–1049. [Google Scholar] [CrossRef]

- Muhammad, N.S.; Speidel, J. Joint optimization of signal constellation bit labeling schemes for bit-interleaved coded modulation with iterative decoding. IEEE Commun. Lett. 2005, 9, 775–777. [Google Scholar]

- Zhang, J.; Djordjevic, I.B. Mapping design of a four-dimensional 32-ary signal constellation over an AWGN channel. Chin. Commun. 2014, 11, 775–777. [Google Scholar] [CrossRef]

- Navazi, H.M.; Hossain, M.J. Novel Method for Multi-Dimensional Mapping of Higher Order Modulations for BICM-ID Over Rayleigh Fading Channels. IEEE Trans. Wirel. Commun. 2019, 18, 1142–1154. [Google Scholar] [CrossRef]

- Yang, F.; Yan, K.; Xie, Q.; Song, J. Non-equiprobable APSK constellation labeling schemes design for BICM systems. IEEE Comm. Lett. 2013, 17, 1276–1279. [Google Scholar] [CrossRef]

- Bocherer, G. Labeling Non-Square QAM Constellations for One-Dimensional Bit-Metric Decoding. IEEE Commun. Lett. 2014, 18, 1515–1518. [Google Scholar] [CrossRef]

- Markiewicz, T.G. Construction and Labeling of Triangular QAM. IEEE Commun. Lett. 2017, 21, 1751–1754. [Google Scholar] [CrossRef]

- Colman, G.W.K.; Gohary, R.H.; El-Azizy, M.A.; Willink, T.J.; Davidson, T.N. Quasi-Gray Labelling for Grassmannian Constellations. IEEE Trans. Wirel. Commun. 2011, 10, 626–636. [Google Scholar] [CrossRef]

- Jia, L.; Shu, F.; Chen, M.; Zhang, W.; Li, J.; Wang, J. Joint Constellation-Labeling Optimization for VLC-CSK Systems. IEEE Wirel. Commun. Lett. 2019, 8, 1280–1284. [Google Scholar] [CrossRef]

- Ma, H.; Leung, W.K.; Yan, X.; Law, K.; Fossorier, M. Delayed bit interleaved coded modulation. In Proceedings of the 2016 9th International Symposium on Turbo Codes and Iterative Information Processing, Brest, France, 5–9 September 2016. [Google Scholar]

- Yan, X.; Machado, R.G.; Huang, K.; Gabry, F.; Fossorier, M.; Hafermann, H.; Zhang, H.; Land, I.; Leung, W.K. Capacity Analysis of Delayed Bit Interleaved Coded Modulation. In Proceedings of the 2018 IEEE 10th International Symposium on Turbo Codes &Iterative Information Processing (ISTC), Hong Kong, China, 3–7 December 2018. [Google Scholar]

- Wang, L.; Cai, S.; Ma, H.; Leung, W.K.; Ma, X. Bit-labeling schemes for delayed BICM with iterative decoding. In Proceedings of the 2018 IEEE International Symposium on Information Theory (ISIT), Vail, CO, USA, 17–22 June 2018. [Google Scholar]

- Liao, Y.; Yang, L.; Yuan, J.; Huang, K.; Leung, R.; Du, J. LDPC Code Design for Delayed Bit-Interleaved Coded Modulation. In Proceedings of the 2019 IEEE Information Theory Workshop (ITW), Visby, Sweden, 25–28 August 2019. [Google Scholar]

- Du, J.; Wang, Z.; Xiao, L.; Wang, L.; Qiao, W. LDPC coded DBICM Scheme for Two Way Relay Channel with a Pipeline Decoding Structure. In Proceedings of the 2018 IEEE International Conference on Communication Systems (ICCS), Chengdu, China, 19–21 December 2018. [Google Scholar]

- Yang, R.; Sherratt, R.S. Enhancing MB-OFDM throughput with dual circular 32-QAM. IEEE Trans. Consum. Electron. 2008, 54, 1640–1646. [Google Scholar] [CrossRef]

- Wake, D.; Dupont, S.; Lethien, C.; Vilcot, J.-P.; Decoster, D. Radiofrequency transmission of 32-QAM signals over multimode fibre for distributed antenna system applications. Electron. Lett. 2001, 37, 1087–1089. [Google Scholar] [CrossRef]

- Zhalehpour, S.; Guo, M.; Lin, J.; Zhang, Z.; Qiao, Y.; Shi, W.; Rusch, L.A. System Optimization of an All-Silicon IQ Modulator: Achieving 100-Gbaud Dual-Polarization 32QAM. J. Lightwave Technol. 2020, 38, 256–264. [Google Scholar] [CrossRef]

- Hamaoka, F.; Nakamura, M.; Nagatani, M.; Kobayashi, T.; Matsushita, A.; Wakita, H.; Yamazaki, H.; Nosaka, H.; Miyamoto, H. 120-GBaud 32QAM Signal Generation using Ultra-Broadband Electrical Bandwidth Doubler. In Proceedings of the Optical Fiber Communication Conference, San Diego, CA, USA, 3–7 March 2019. [Google Scholar]

- Hu, X.; Eleftheriou, E.; Arnold, D.M. Regular and irregular progressive edge-growth tanner graphs. IEEE Trans. Info. Theory 2005, 51, 386–398. [Google Scholar] [CrossRef]

- Storn, R.; Price, K. Differential evolution simple and efficient heuristic for global optimization over continuous spaces. J. Global Optim. 1997, 11, 341–359. [Google Scholar] [CrossRef]

- Morello, A.; Mignone, V. DVB-S2: The Second Generation Standard for Satellite Broad-Band Services. Proc. IEEE 2006, 94, 210–227. [Google Scholar] [CrossRef]

| Criteria Number | Description |

|---|---|

| 1 | The PLS of delayed bits , i.e., , should be a PGLS. |

| 2 | The PLS of the undelayed bits should be a PGLS. |

| 3 | PLS for which is a PGLS. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Z.; Zhou, L.; Du, J.; Zhao, Y. Design of a Labeling Scheme for 32-QAM Delayed Bit-Interleaved Coded Modulation. Sensors 2020, 20, 3528. https://doi.org/10.3390/s20123528

Zhang Z, Zhou L, Du J, Zhao Y. Design of a Labeling Scheme for 32-QAM Delayed Bit-Interleaved Coded Modulation. Sensors. 2020; 20(12):3528. https://doi.org/10.3390/s20123528

Chicago/Turabian StyleZhang, Zhe, Liang Zhou, Junyi Du, and Yue Zhao. 2020. "Design of a Labeling Scheme for 32-QAM Delayed Bit-Interleaved Coded Modulation" Sensors 20, no. 12: 3528. https://doi.org/10.3390/s20123528

APA StyleZhang, Z., Zhou, L., Du, J., & Zhao, Y. (2020). Design of a Labeling Scheme for 32-QAM Delayed Bit-Interleaved Coded Modulation. Sensors, 20(12), 3528. https://doi.org/10.3390/s20123528