A Successive Approximation Time-to-Digital Converter with Single Set of Delay Lines for Time Interval Measurements

Abstract

:1. Introduction

2. Brief Overview of Delay Line TDCs

3. Schemes of Successive Approximation in Analog-To-Digital Conversion

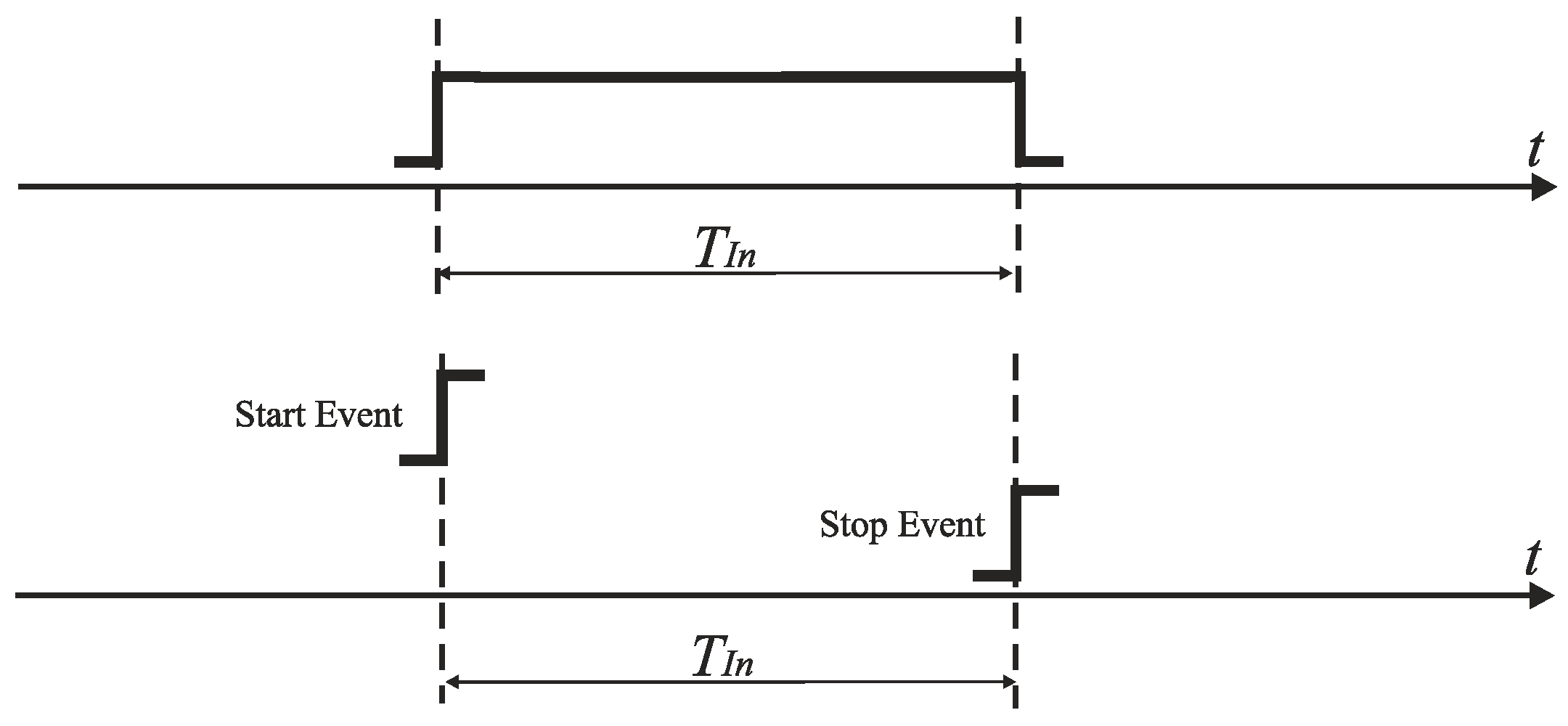

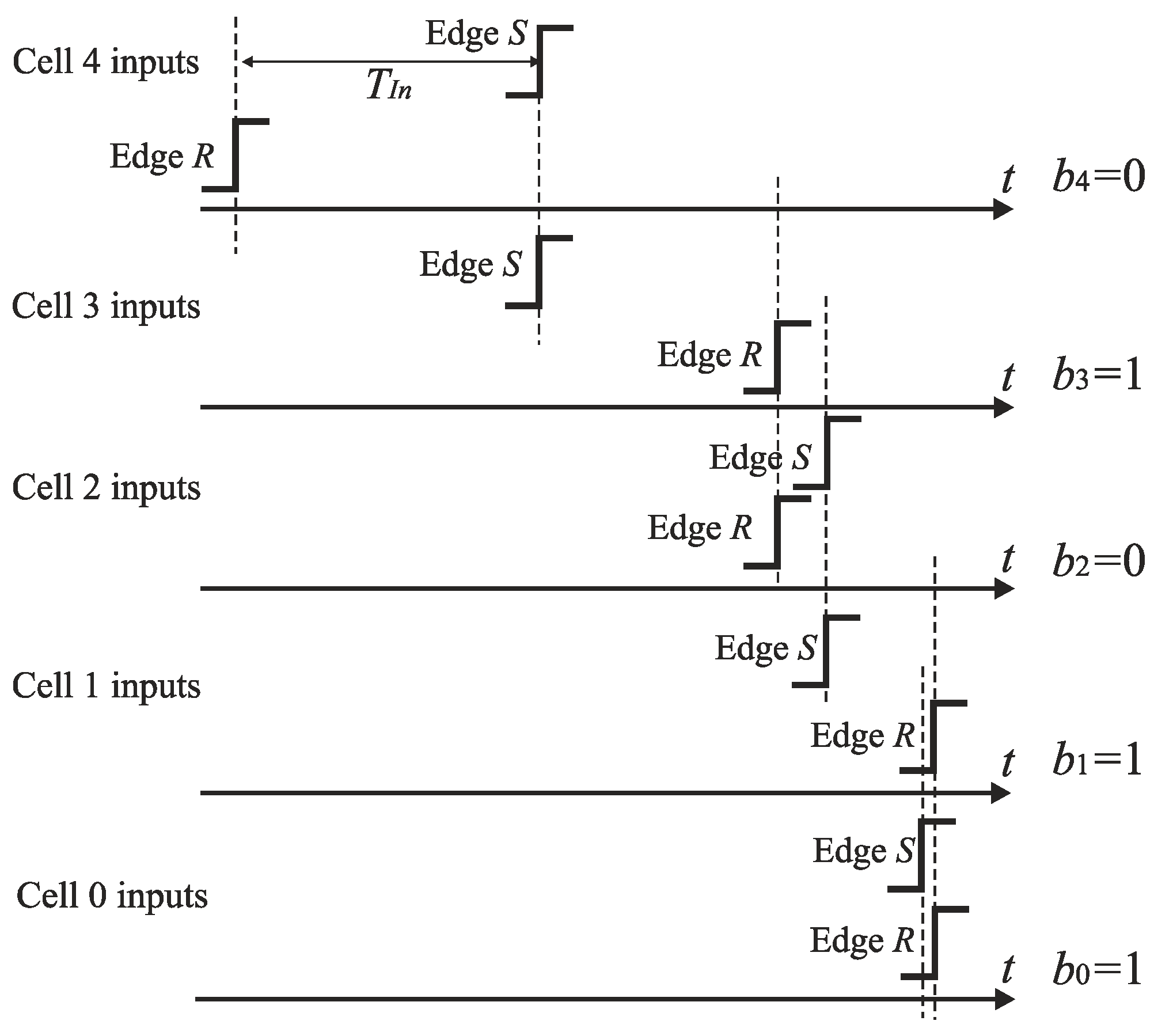

4. Time-to-Digital Conversion Based on Monotone Successive Approximation Scheme

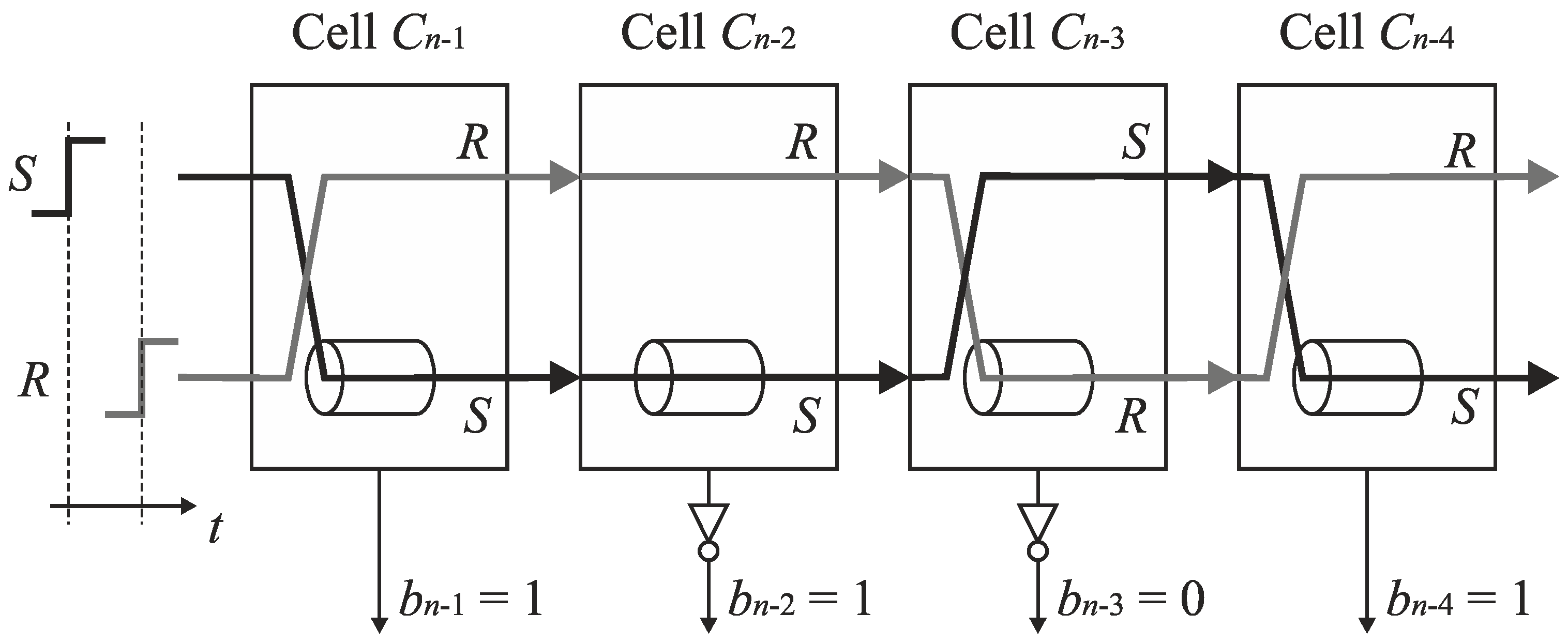

5. Basic SA-TDC Architecture

5.1. SA-TDC Architecture for Bipolar Input

5.2. SA-TDC Architecture for Unipolar Input

5.3. Related Works

6. Optimization of Basic SA-TDC Architecture

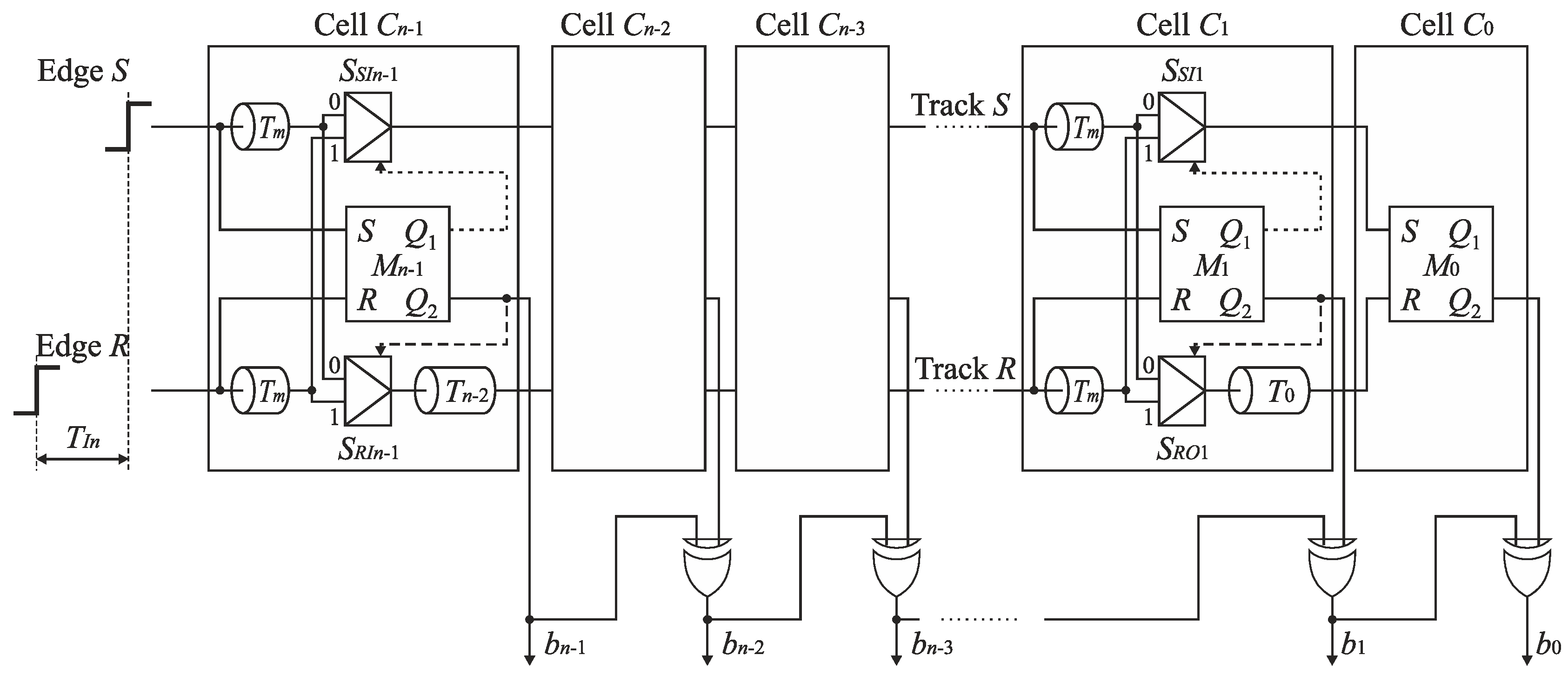

6.1. SA-TDC with Single Set of Delay Lines

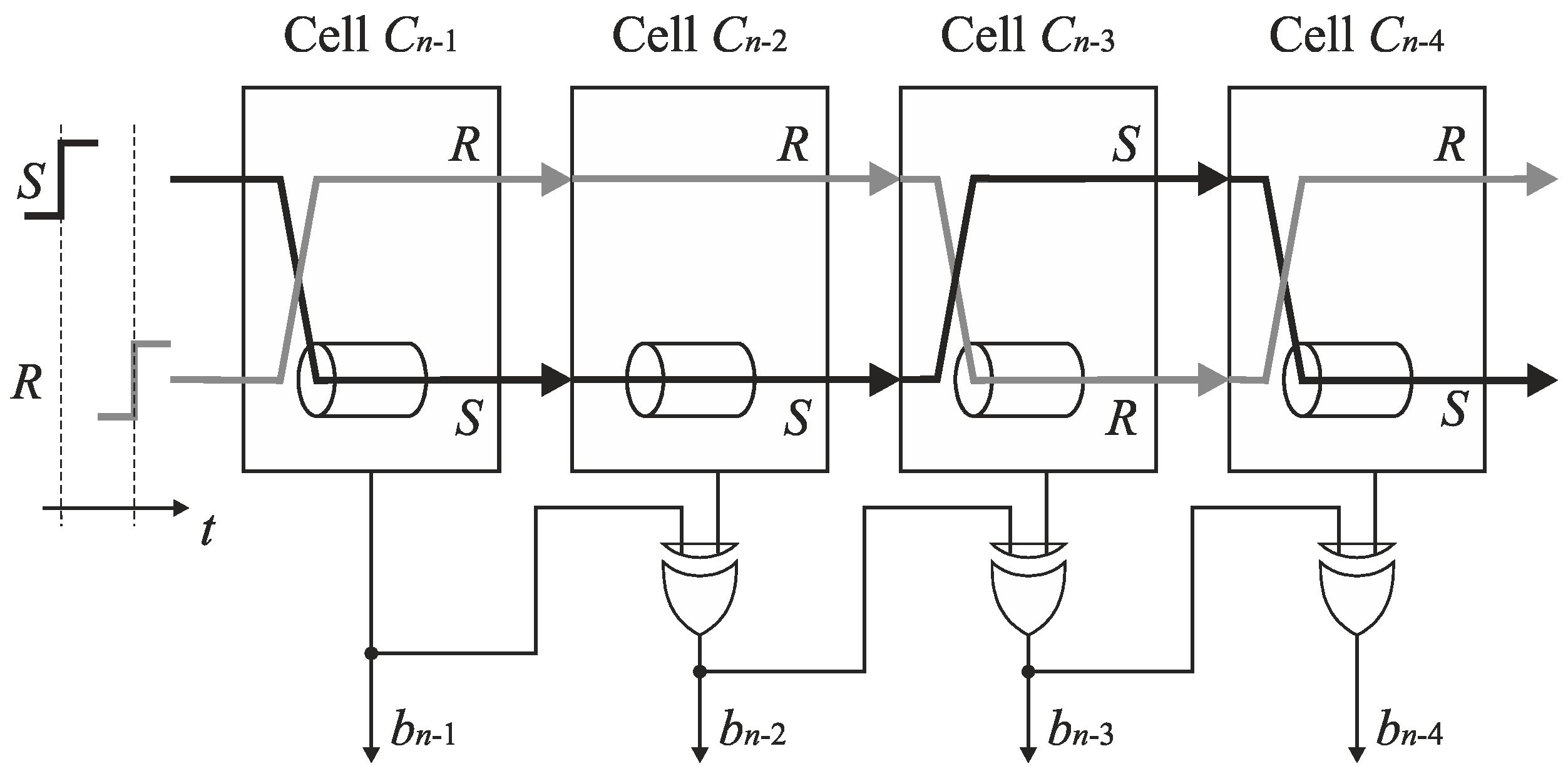

6.2. SA-TDC with Single Set of Delay Lines and Output Decoding

6.3. Compensation of Logic Propagation Delays

6.4. Evaluation of SA-TDC Circuit Complexity by Proposed Design Optimization

7. Implementation of SA-TDC in 180 nm CMOS Technology

7.1. Delay Lines

7.2. Time Comparator

7.3. Preliminary Tests of SA-TDC with Tm = 250 ps

7.4. Reducing Tm Delay by Symmetrizing Multiplexer Design

7.5. Analysis of Device Mismatch and Time Jitter

7.6. Impact of Temperature and Supply Voltage Variations

8. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Yuan, F. CMOS Time-Mode Circuits and Systems: Fundamentals and Applications; CRC Press: Boca Raton, FL, USA, 2015. [Google Scholar]

- Henzler, H. Time-To-Digital Converters; Springer: New York, NY, USA, 2010. [Google Scholar]

- Staszewski, R.B.; Balsara, P.T. All-Digital Frequency Synthesizer in Deep-Submicron CMOS; John Wiley & Sons: Hoboken, NJ, USA, 2006. [Google Scholar]

- Roberts, G.W.; Ali-Bakhshian, M. A Brief Introduction to Time-to-Digital and Digital-to-Time Converters. IEEE Trans. Circ. Syst. II: Express Briefs 2010, 57, 153–157. [Google Scholar] [CrossRef]

- Liu, S.C.; Delbruck, T.; Indiveri, G.; Douglas, R.; Whatley, A. Event-Based Neuromorphic Systems; CRC Press: Boca Raton, FL, USA, 2015. [Google Scholar]

- Tsividis, Y. Continuous-time digital signal processing. Electr. Lett. 2003, 39, 1551–1552. [Google Scholar] [CrossRef]

- Miskowicz, M. Event-Based Control and Signal Processing; CRC Press: Boca Raton, FL, USA, 2016. [Google Scholar]

- Muhammad, K.; Staszewski, R.B.; Leipold, D. Digital RF processing: Toward low-cost reconfigurable radios. IEEE Commun. Mag. 2005, 43, 105–113. [Google Scholar] [CrossRef]

- Staszewski, R.B.; Wallberg, J.L.; Hung, C.M.; Eliezer, O.E.; Vemulapalli, S.K.; Fernando, C.; Maggio, K.; Staszewski, R.; Barton, N.; Lee, M.C.; et al. All-digital PLL and transmitter for mobile phones. IEEE J. Solid-State Circ. 2005, 40, 2469–2482. [Google Scholar] [CrossRef]

- Szplet, R. Time-to-digital converters. In Design, Modeling and Testing of Data Converters; Carbone, P., Kiaei, S., Xu, F., Eds.; Springer: New York, NY, USA, 2014. [Google Scholar]

- Staszewski, R.; Vemulapalli, S.; Vallur, P.; Wallberg, J.; Balsara, P. 1.3 v 20 ps time-to-digital converter for frequency synthesis in 90-nm CMOS. IEEE Trans. Circuits Syst. II: Express Briefs 2006, 53, 220–224. [Google Scholar] [CrossRef]

- Asada, K.; Nakura, T.; Iizuka, T.; Ikeda, M. Time-domain approach for analog circuits in deep sub-micron LSI. IEICE Electr. Express 2018, 15, 1–21. [Google Scholar] [CrossRef]

- Christiansen, J. Picosecond Stopwatches: The evolution of time-to-digital converters. IEEE Solid-State Circ. Mag. 2012, 4, 55–59. [Google Scholar] [CrossRef]

- Legrele, C.; Lugol, J.C. A one nanosecond resolution time-to-digital converter. IEEE Trans. Nucl. Sci. 1983, 30, 297–300. [Google Scholar] [CrossRef]

- Vornicu, I.; Carmona-Galán, R.; Rodríguez-Vázquez, A. Compensation of PVT Variations in ToF Imagers with In-Pixel TDC. Sensors 2017, 17, 1072. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Yang, B.; Xie, X.; Li, D.; Xu, L. Influence of Waveform Characteristics on LiDAR Ranging Accuracy and Precision. Sensors 2018, 18, 1156. [Google Scholar] [CrossRef] [PubMed]

- Alayed, M.; Palubiak, D.P.; Deen, M.J. Characterization of a Time-Resolved Diffuse Optical Spectroscopy Prototype Using Low-Cost, Compact Single Photon Avalanche Detectors for Tissue Optics Applications. Sensors 2018, 18, 3680. [Google Scholar] [CrossRef] [PubMed]

- Zhang, C.; Lindner, S.; Antolovic, I.M.; Wolf, M.; Charbon, E. A CMOS SPAD Imager with Collision Detection and 128 Dynamically Reallocating TDCs for Single-Photon Counting and 3D Time-of-Flight Imaging. Sensors 2018, 18, 4016. [Google Scholar] [CrossRef] [PubMed]

- Ximenes, A.R.; Padmanabhan, P.; Charbon, E. Mutually coupled time-to-digital converters (TDCs) for direct time-of-flight (dTOF) image sensors. Sensors 2018, 18, 3413. [Google Scholar] [CrossRef] [PubMed]

- Nguyen, V.; Duong, D.; Chung, Y.; Lee, J.W. A Cyclic Vernier Two-Step TDC for High Input Range Time-of-Flight Sensor Using Startup Time Correction Technique. Sensors 2018, 18, 3948. [Google Scholar] [CrossRef] [PubMed]

- Dudek, P.; Szczepanski, S.; Hatfield, J. A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line. IEEE J. Solid-State Circ. 2000, 35, 240–247. [Google Scholar] [CrossRef]

- Kościelnik, D.; Miśkowicz, M.; Szyduczyński, J.; Rzepka, D. Optimizing time-to-digital converter architecture for successive approximation time measurements. In Proceedings of the IEEE Nordic-Mediterranean Workshop on Time-to-Digital Converters NoMe TDC, Perugia, Italy, 3 October 2013; pp. 1–8. [Google Scholar]

- Kościelnik, D.; Szyduczyński, J.; Rzepka, D.; Andrysiewicz, W.; Miśkowicz, M. Architecture of successive approximation time-to-digital converter with single set of delay lines. In Proceedings of the 18th International Workshop on ADC Modelling and Testing IWADC, Benevento, Italy, 15–17 September 2014; pp. 1–6. [Google Scholar]

- Kościelnik, D.; Szyduczyński, J.; Rzepka, D.; Andrysiewicz, W.; Miśkowicz, M. Optimized Design of Successive Approximation Time-To-Digital Converter with Single Set of Delay Lines. In Proceedings of the 2nd International Conference on Event-Based Control, Communication, and Signal Processing EBCCSP, Krakow, Poland, 13–15 June 2016; pp. 1–6. [Google Scholar]

- Ragab, K.O.; Mostafa, H.; Eladawy, A. A Novel 10-Bit 2.8-mW TDC Design Using SAR with Continuous Disassembly Algorithm. IEEE Trans. Circ. Syst. II Express Briefs 2015, 63, 909–913. [Google Scholar] [CrossRef]

- Akgun, O.C. An Asynchronous Pipelined Time-to-Digital Converter Using Time-Domain Subtraction. In Proceedings of the IEEE International Symposium on Circuits and Systems ISCAS, Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Maevsky, O.V.; Edel, E.A. Converter of Time Intervals to Code. USSR Patent 1591183.

- Kinniment, D.J.; Maevsky, O.V.; Bystrov, A.; Yakovlev, A.V. On-chip structures for timing measurement and test. In Proceedings of the IEEE International Symposium on Asynchronous Circuits and Systems ASYNC, Manchester, UK, 8–11 April 2002; pp. 190–197. [Google Scholar]

- Abas, M.A.; Russell, G.; Kinniment, D.J. Design of Sub-10-Picoseconds On-Chip Time Measurement Circuit. In Proceedings of the Design, Automation and Test in Europe Conference and Exhibition, Washington, DC, USA, 16–20 February 2004; pp. 804–809. [Google Scholar]

- Abas, M.A.; Russell, G.; Kinniment, D.J. Built-in time measurement circuits—a comparative design study. IET Comput. Dig. Techn. 2007, 1, 87–97. [Google Scholar] [CrossRef]

- Miyashita, D.; Yamaki, R.; Hashiyoshi, K.; Kobayashi, H.; Kousai, S.; Oowaki, Y.; Unekawa, Y. An LDPC decoder with time-domain analog and digital mixed-signal processing. IEEE J. Solid-State Circ. 2014, 49, 73–83. [Google Scholar] [CrossRef]

- Chung, H.; Ishikuro, H.; Kuroda, T. A 10-bit 80-MS/s decision-select successive approximation TDC in 65 nm CMOS. IEEE J. Solid-State Circ. 2012, 47, 1232–1241. [Google Scholar] [CrossRef]

- Mantyniemi, A.; Rahkonen, T.; Kostamovaara, J. A CMOS Time-to-Digital Converter (TDC) Based on a Cyclic Time Domain Successive Approximation Interpolation Method. IEEE J. Solid-State Circ. 2009, 44, 3067–3078. [Google Scholar] [CrossRef]

- Al-Ahdab, S.; Mantyniemi, A.; Kostamovaara, J. Cyclic time domain successive approximation time-to-digital converter (TDC) with sub-ps-level resolution. In Proceedings of the IEEE Instrumentation and Measurement Technology Conference I2MTC, Binjiang, China, 10–12 May 2011; pp. 1–4. [Google Scholar]

- Al-Ahdab, S.; Mantyniemi, A.; Kostamovaara, J. A time-to-digital converter (TDC) with a 13-bit cyclic time domain successive approximation interpolator with sub-ps-level resolution using current DAC and differential switch. In Proceedings of the IEEE 56th International Midwest Symposium on Circuits and Systems MWSCAS 2013, Columbus, OH, USA, 4–7 August 2013; pp. 828–831. [Google Scholar]

- Szyduczyński, J.; Kościelnik, D.; Miśkowicz, M. Dynamic Equalization of Logic Delays in Feedback-Based Successive Approximation TDCs. In Proceedings of the 3rd International Conference on of Event-Based Control, Communication, and Signal Processing, Funchal, France, 24–26 May 2017; pp. 1–6. [Google Scholar]

- Szyduczyński, J.; Nguyen, V.; Schembari, F.; Staszewski, R.B.; Kościelnik, D.; Miśkowicz, M. Behavioral Modelling and Optimization of a Cyclic Feedback-Based Successive Approximation TDC with Dynamic Delay Equalization. In Proceedings of the 4th International Conference on Event-Based Control, Communication, and Signal Processing EBCCSP, Perpignan, France, 27–29 June 2018; pp. 1–9. [Google Scholar]

- Straayer, M.Z.; Perrott, M.H. A multi-path gated ring oscillator TDC with first-order noise shaping. IEEE J. Solid-State Circ. 2009, 44, 1089–1098. [Google Scholar] [CrossRef]

- Cao, Y.; De Cock, W.; Steyaert, M.; Leroux, P. 1-1-1 MASH ΣΔ Time-to-Digital Converters With 6 ps Resolution and Third-Order Noise-Shaping. IEEE J. Solid-State Circ. 2012, 47, 2093–2106. [Google Scholar] [CrossRef]

- Yu, W.; Kim, K.S.; Cho, S.H. A 0.22 ps rms Integrated Noise 15 MHz Bandwidth Fourth-Order ΔΣ Time-to-Digital Converter Using Time-Domain Error-Feedback Filter. IEEE J. Solid-State Circ. 2015, 50, 1251–1262. [Google Scholar] [CrossRef]

- Kratyuk, V.; Hanumolu, P.K.; Ok, K.; Moon, U.-K.; Mayaram, K. A digital PLL with a stochastic time-to-digital converter. IEEE Trans. Circ. Syst. I-Reg. Pap. 2009, 56, 1612–1621. [Google Scholar] [CrossRef]

- Jabłeka, M.; Miśkowicz, M.; Kościelnik, D. Uncertainty of asynchronous analog-to-digital converter output state. In Proceedings of the IEEE International Symposium on Industrial Electronics ISlE 2010, Bari, Italy, 4–7 July 2010; pp. 1692–1697. [Google Scholar]

- McCreary, J.L.; Gray, P.R. All-MOS charge redistribution analog-to-digital conversion techniques. I. IEEE J. Solid-State Circ. 1975, 10, 371–379. [Google Scholar] [CrossRef]

- Kościelnik, D.; Miśkowicz, M. Time-to-digital converters based on event-driven successive charge redistribution: A theoretical approach. Measurement 2012, 45, 2511–2528. [Google Scholar] [CrossRef]

- Liu, C.-C.; Chang, S.-J.; Huang, G.-Y.; Lin, Y.-Z. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circ. 2010, 34, 731–740. [Google Scholar] [CrossRef]

- Polzer, T.; Steininger, A. A general approach for comparing metastable behavior of digital CMOS gates. In Proceedings of the 19th International Symposium on Design and Diagnostics of Electronic Circuits & Systems DDECS, Kosice, Slovakia, 20–22 April 2016; pp. 1–6. [Google Scholar]

- Baronti, F.; Lunardini, D.; Roncella, R.; Saletti, R. A self-calibrating delay-locked delay line with shunt-capacitor scheme. IEEE J. Solid-State Circ. 2004, 39, 384–387. [Google Scholar] [CrossRef]

| Number of Bits n | Basic SA-TDC with Two Sets of Delay Lines | SA-TDC with Single Set of Delay Lines and Output Decoding | ||

|---|---|---|---|---|

| Tm = 0 | Tm = 250 ps | Tm = 0 | Tm = 250 ps | |

| 2 | 60 | 140 | 68 | 148 |

| 3 | 116 | 276 | 128 | 288 |

| 4 | 188 | 428 | 196 | 436 |

| 5 | 292 | 612 | 280 | 600 |

| 6 | 460 | 860 | 396 | 796 |

| 7 | 756 | 1236 | 576 | 1056 |

| 8 | 1308 | 1868 | 884 | 1444 |

| 9 | 2372 | 3012 | 1448 | 2088 |

| 10 | 4460 | 5180 | 2524 | 3244 |

| 11 | 8596 | 9396 | 4624 | 5424 |

| 12 | 16,828 | 17,708 | 8772 | 9652 |

| Transistor | W (µm) | L (µm) | Fingers |

|---|---|---|---|

| P1 | 0.27 | 0.18 | 1 |

| N1 | 12.22 | 0.18 | 47 |

| P2 | 18.00 | 0.18 | 1 |

| N2 | 0.27 | 0.18 | 1 |

| Bits | ±T (ps) | T0 (ps) | Tm (ps) | RMS DNL | RMS INL |

|---|---|---|---|---|---|

| 8 | 3175 | 25 | 250 | 0.14 | 0.16 |

| Feature | Reference | |||

|---|---|---|---|---|

| [33] | [32] | [31] | This Work | |

| Architecture | Feedback | Feedforward | Feedforward | Feedforward |

| Technology (nm) | 350 | 65 | 65 | 180 |

| Nominal resolution (ps) | 1.22 | 9.77 | 50 | 25 |

| Number of bits | 13 | 10 | 5 | 8 |

| Full scale (ns) | 0.32 | 10 | 1.5 | 6.35 |

| Number of sets of binary-scaled delay components | 2 | 2 | 2 | 1 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Szyduczyński, J.; Kościelnik, D.; Miśkowicz, M. A Successive Approximation Time-to-Digital Converter with Single Set of Delay Lines for Time Interval Measurements. Sensors 2019, 19, 1109. https://doi.org/10.3390/s19051109

Szyduczyński J, Kościelnik D, Miśkowicz M. A Successive Approximation Time-to-Digital Converter with Single Set of Delay Lines for Time Interval Measurements. Sensors. 2019; 19(5):1109. https://doi.org/10.3390/s19051109

Chicago/Turabian StyleSzyduczyński, Jakub, Dariusz Kościelnik, and Marek Miśkowicz. 2019. "A Successive Approximation Time-to-Digital Converter with Single Set of Delay Lines for Time Interval Measurements" Sensors 19, no. 5: 1109. https://doi.org/10.3390/s19051109

APA StyleSzyduczyński, J., Kościelnik, D., & Miśkowicz, M. (2019). A Successive Approximation Time-to-Digital Converter with Single Set of Delay Lines for Time Interval Measurements. Sensors, 19(5), 1109. https://doi.org/10.3390/s19051109