Minimally-Invasive Neural Interface for Distributed Wireless Electrocorticogram Recording Systems

Abstract

:1. Introduction

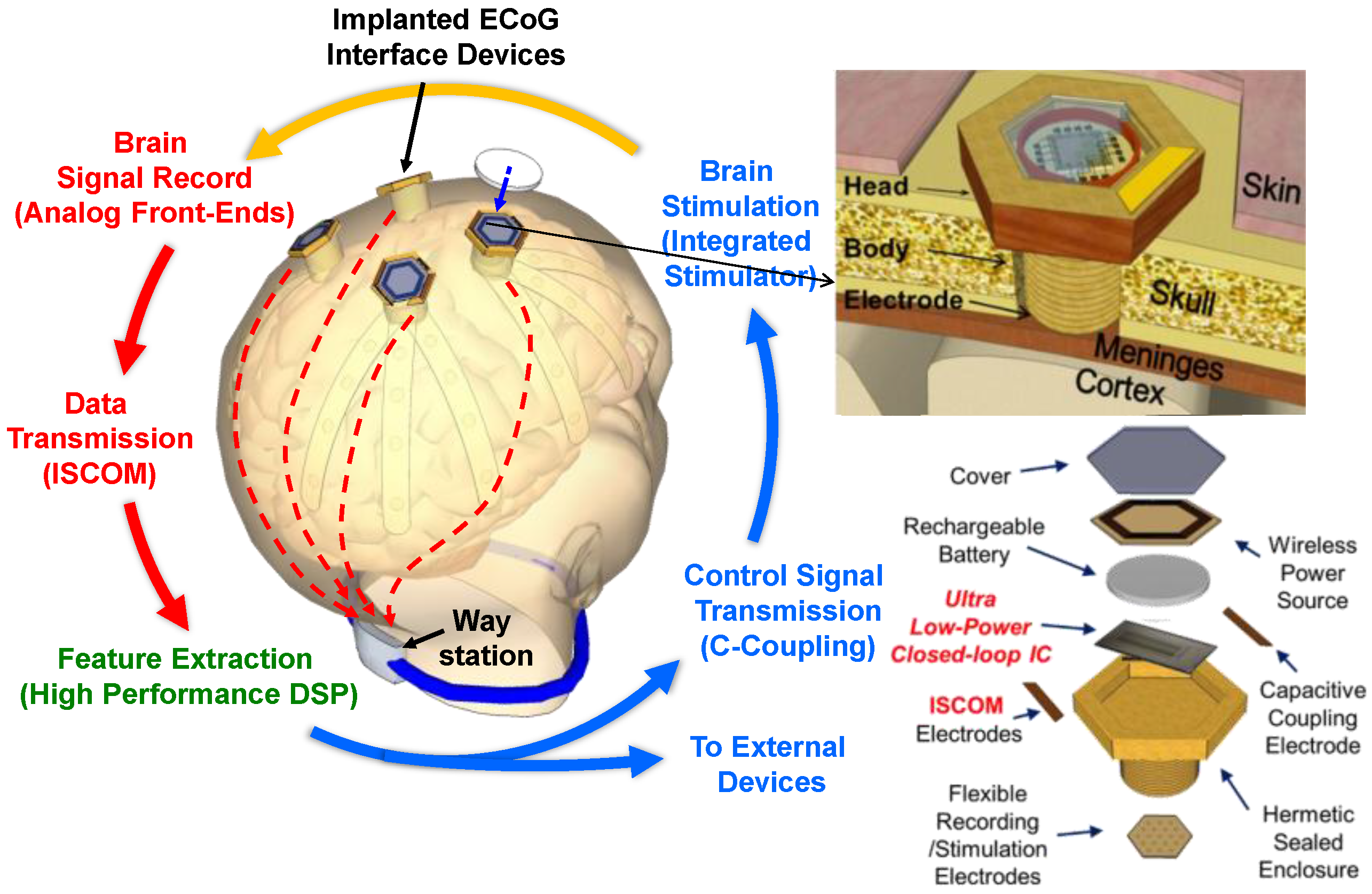

2. System Architecture

2.1. Concept of Distributed Wireless ECoG Recording

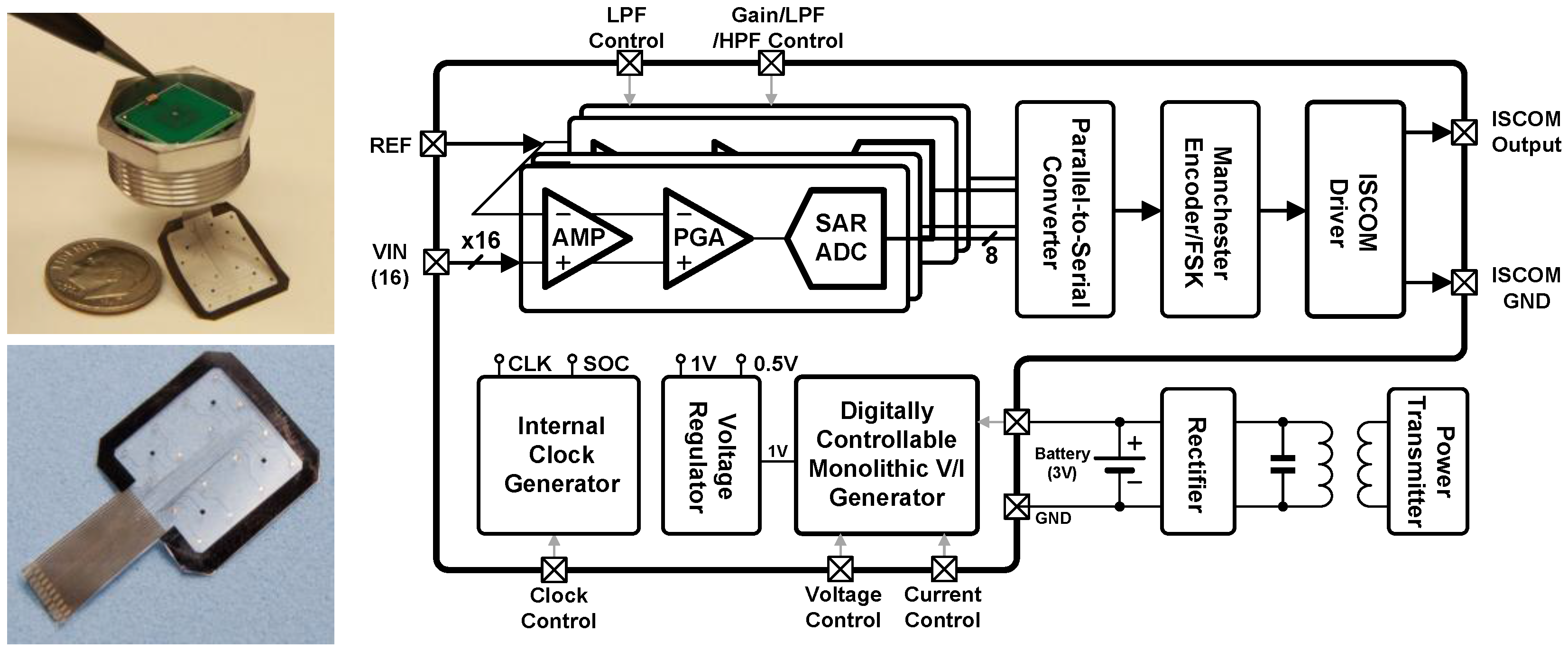

2.2. Architecture of Neural Interface

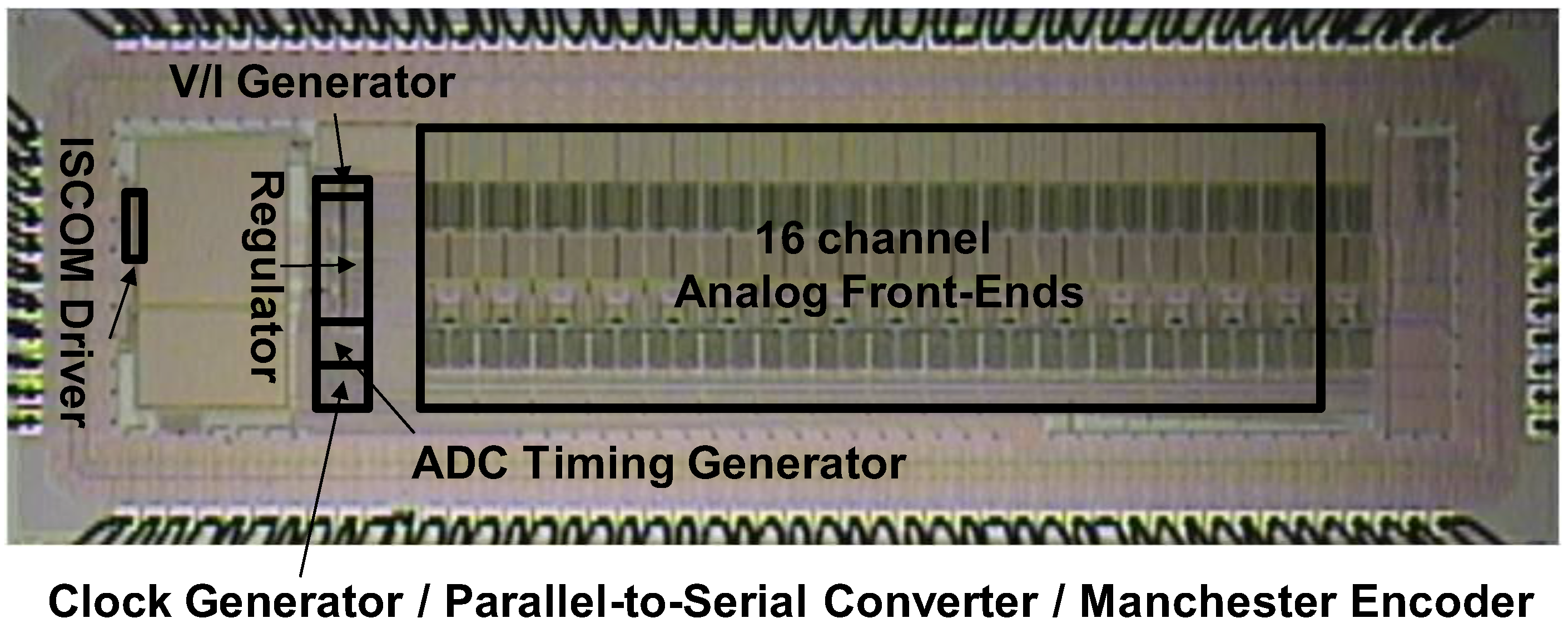

3. Integrated Circuits

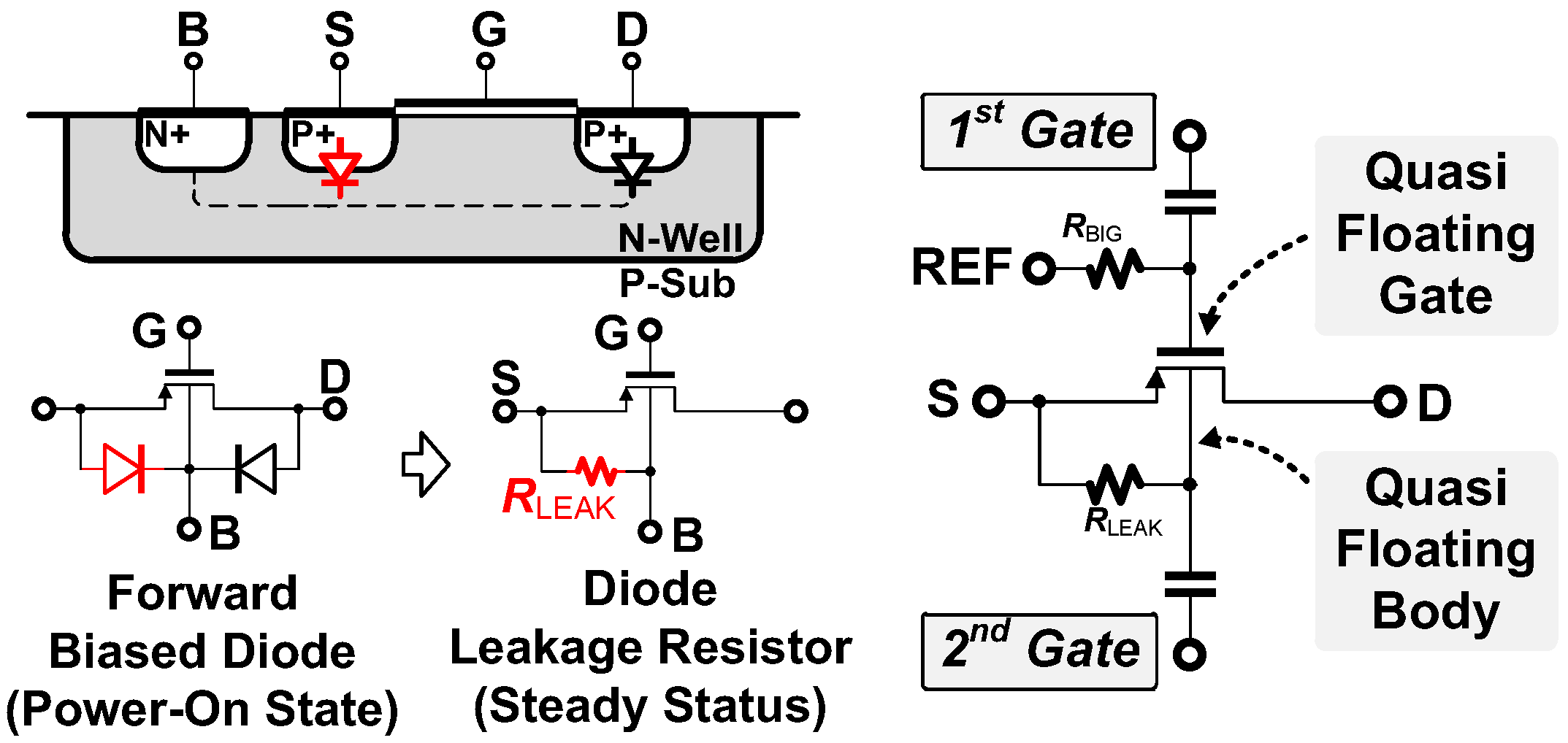

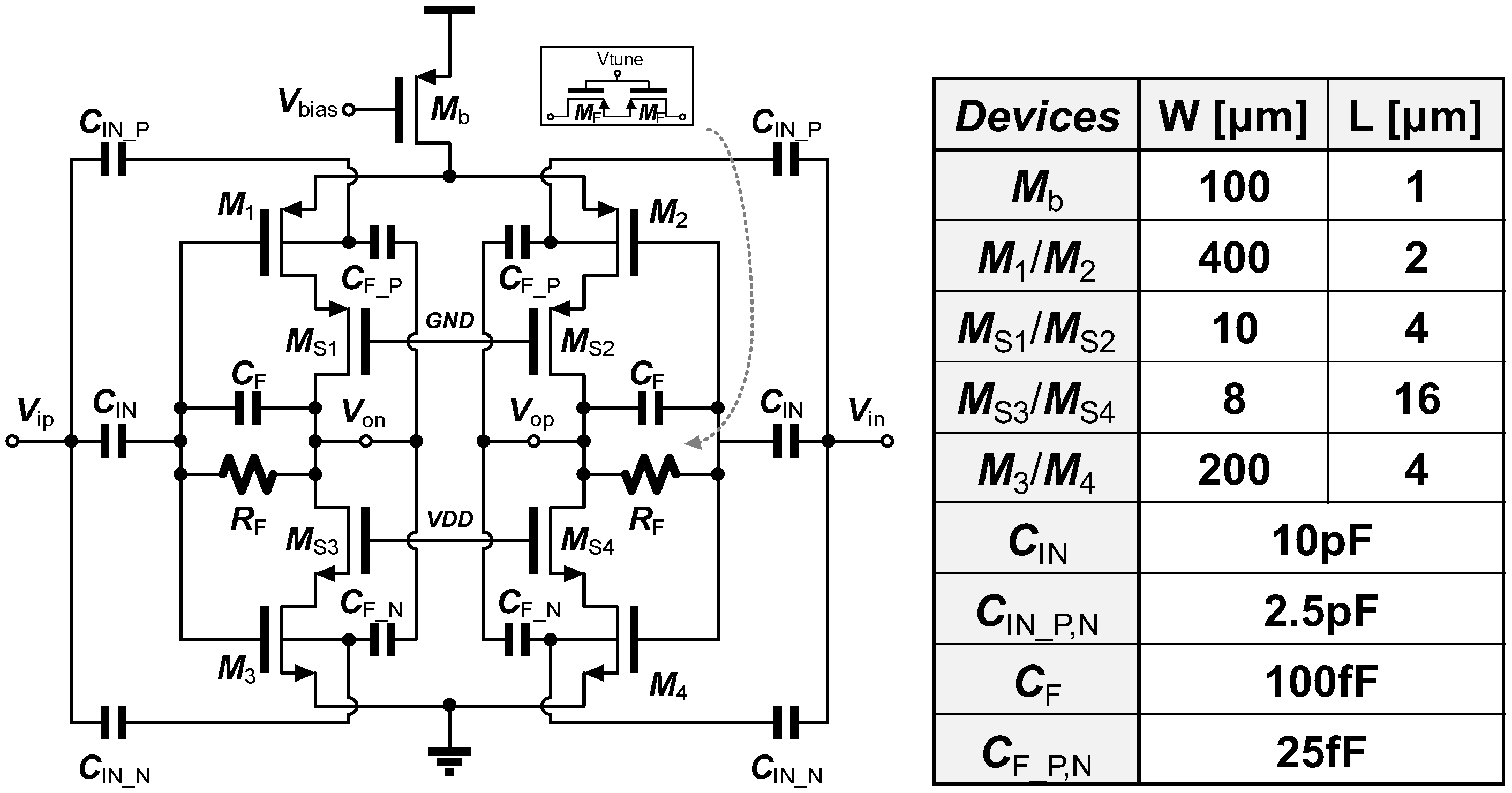

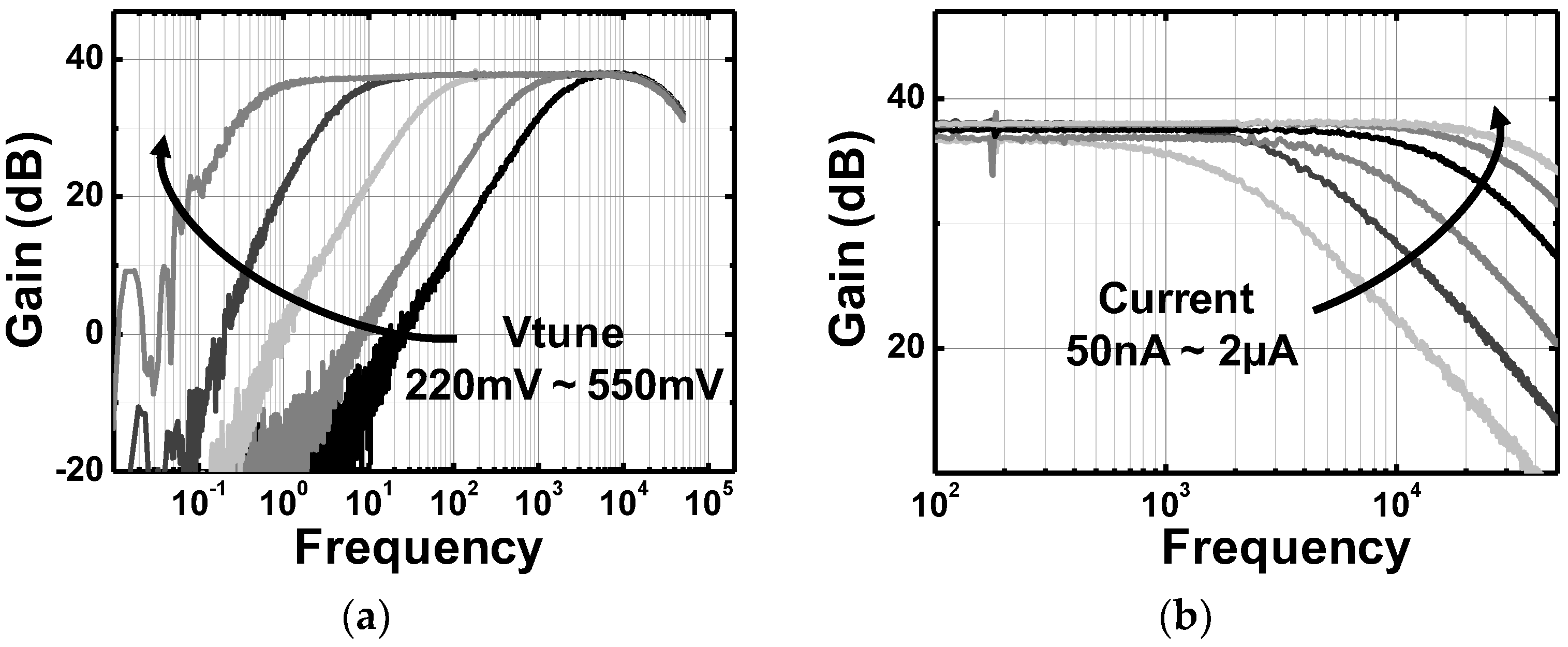

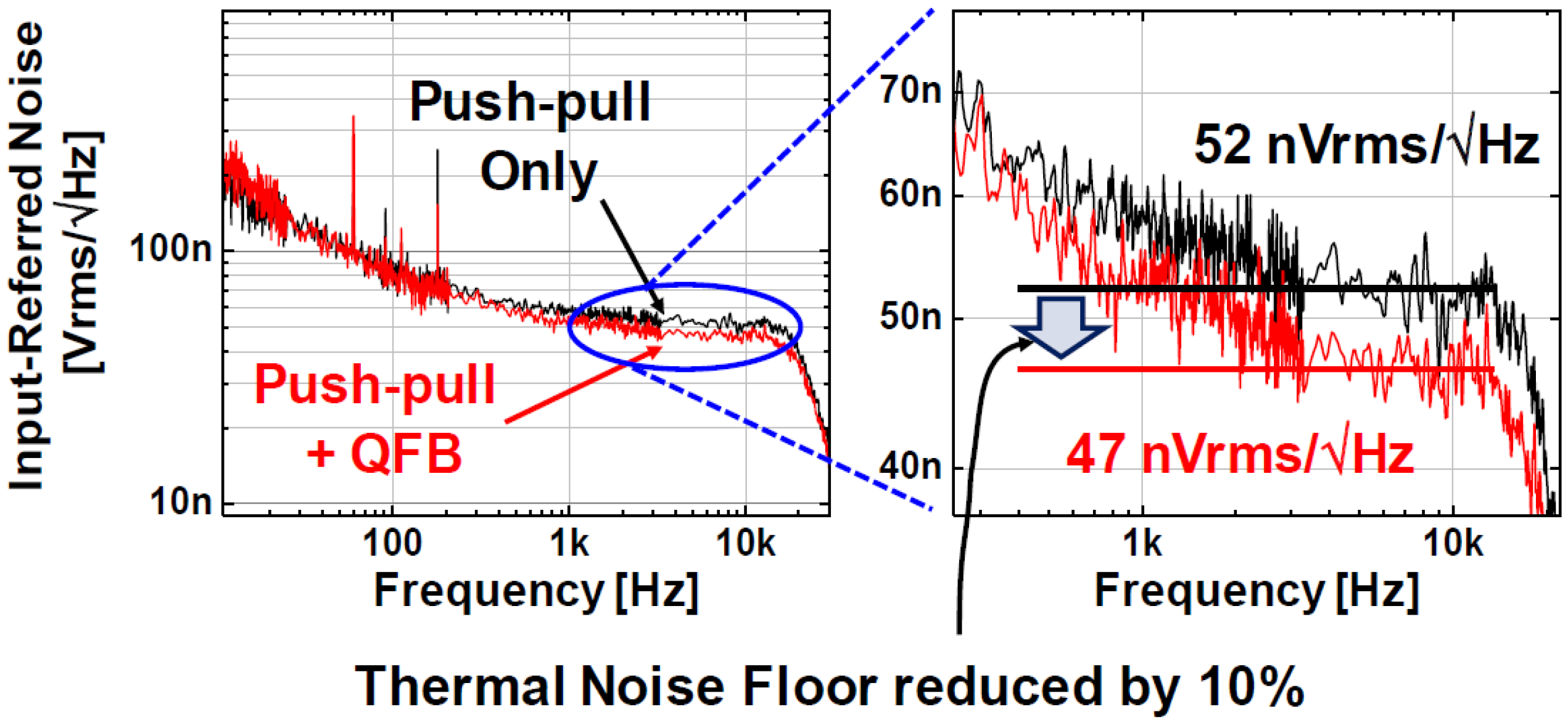

3.1. Noise-Power Efficient Double-Gated Push-Pull Preamplifier Using Quasi-Floating Body

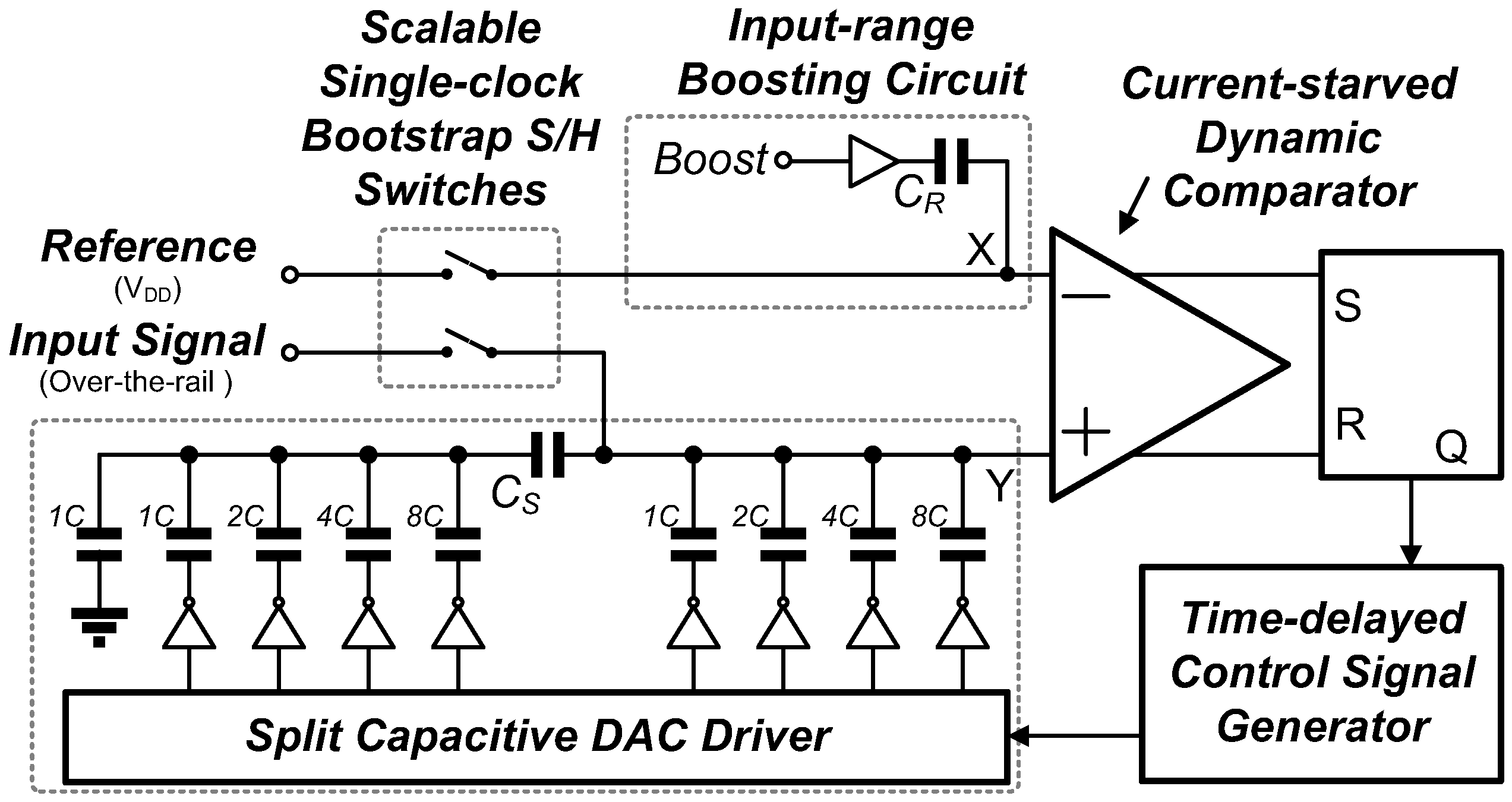

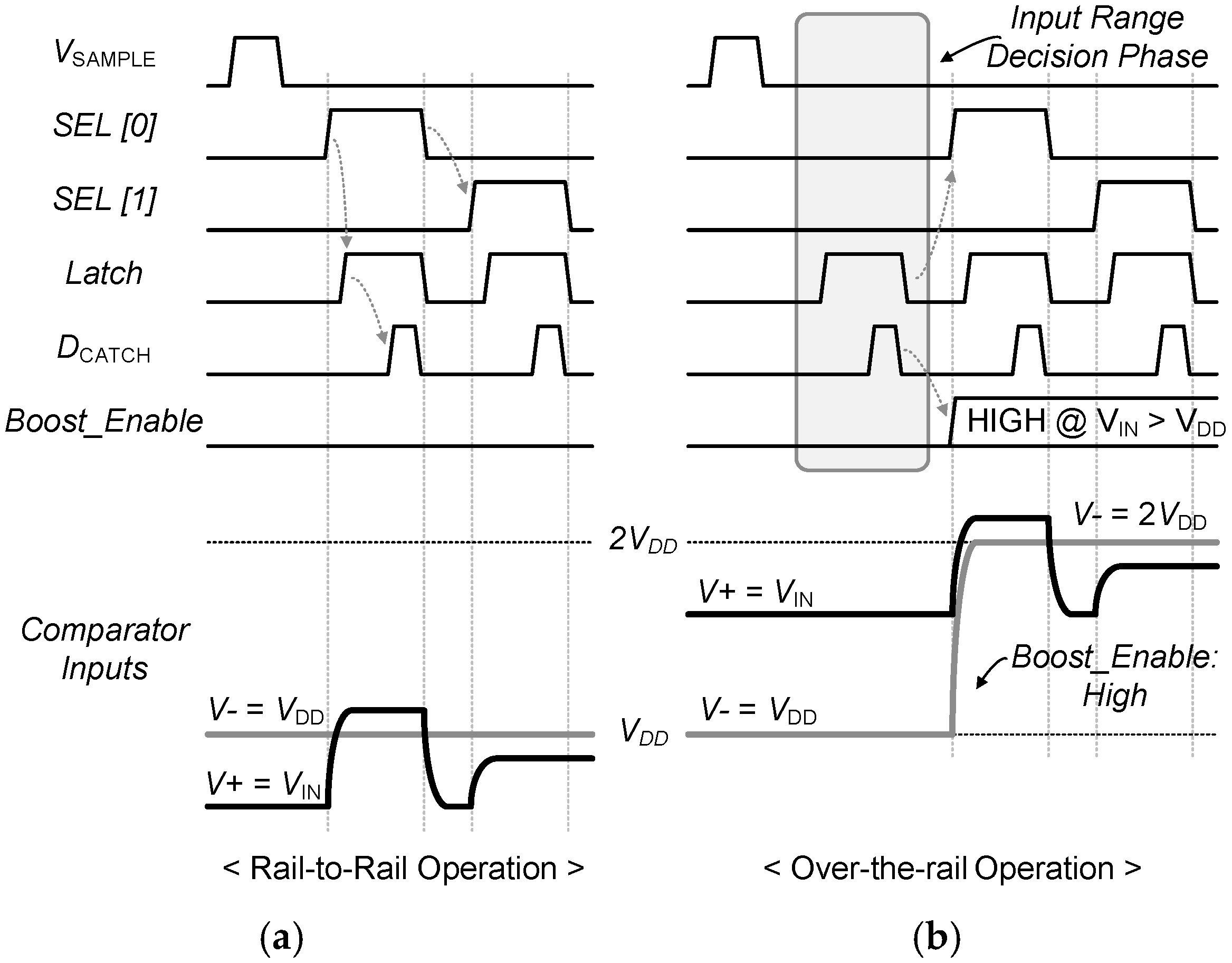

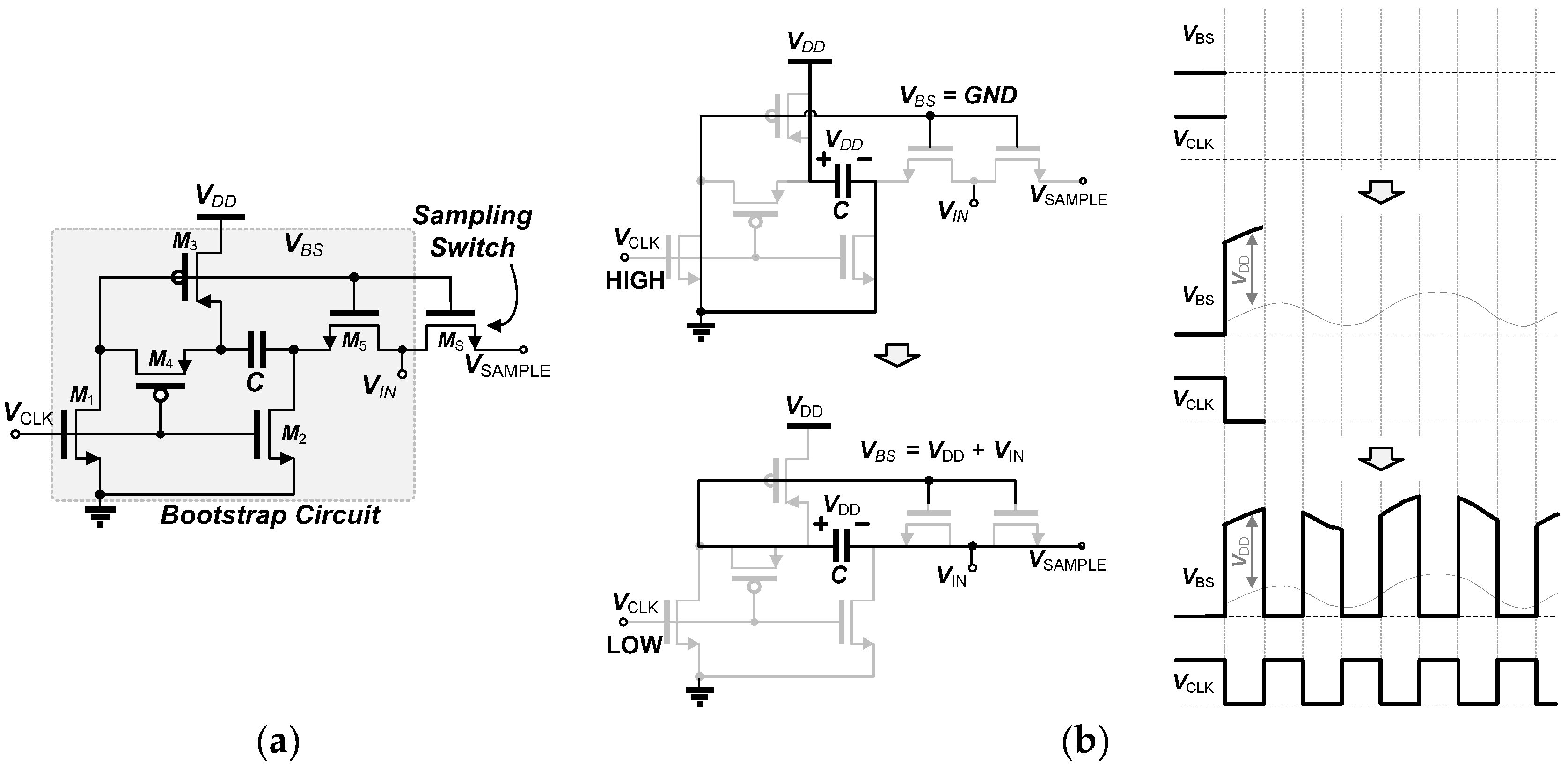

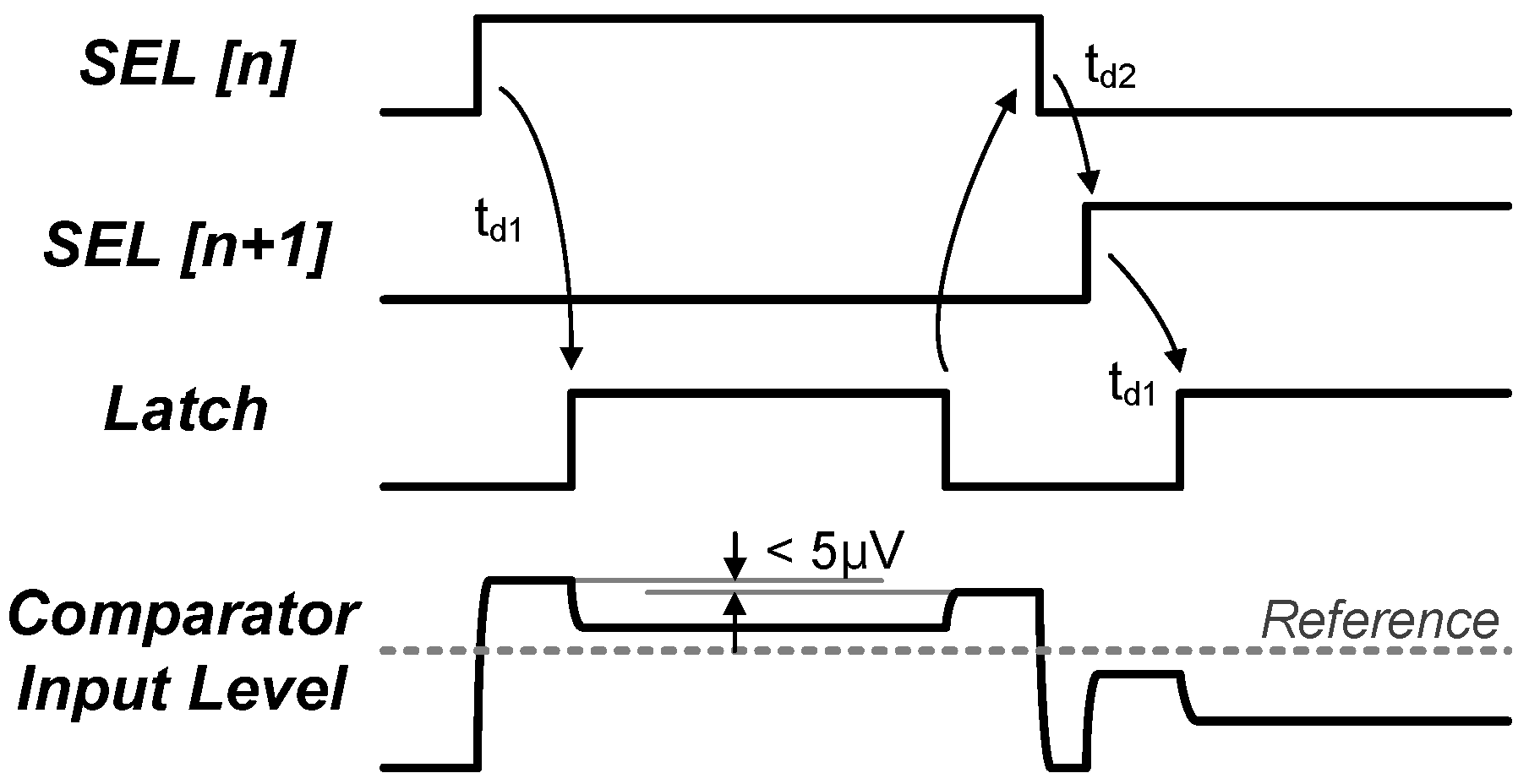

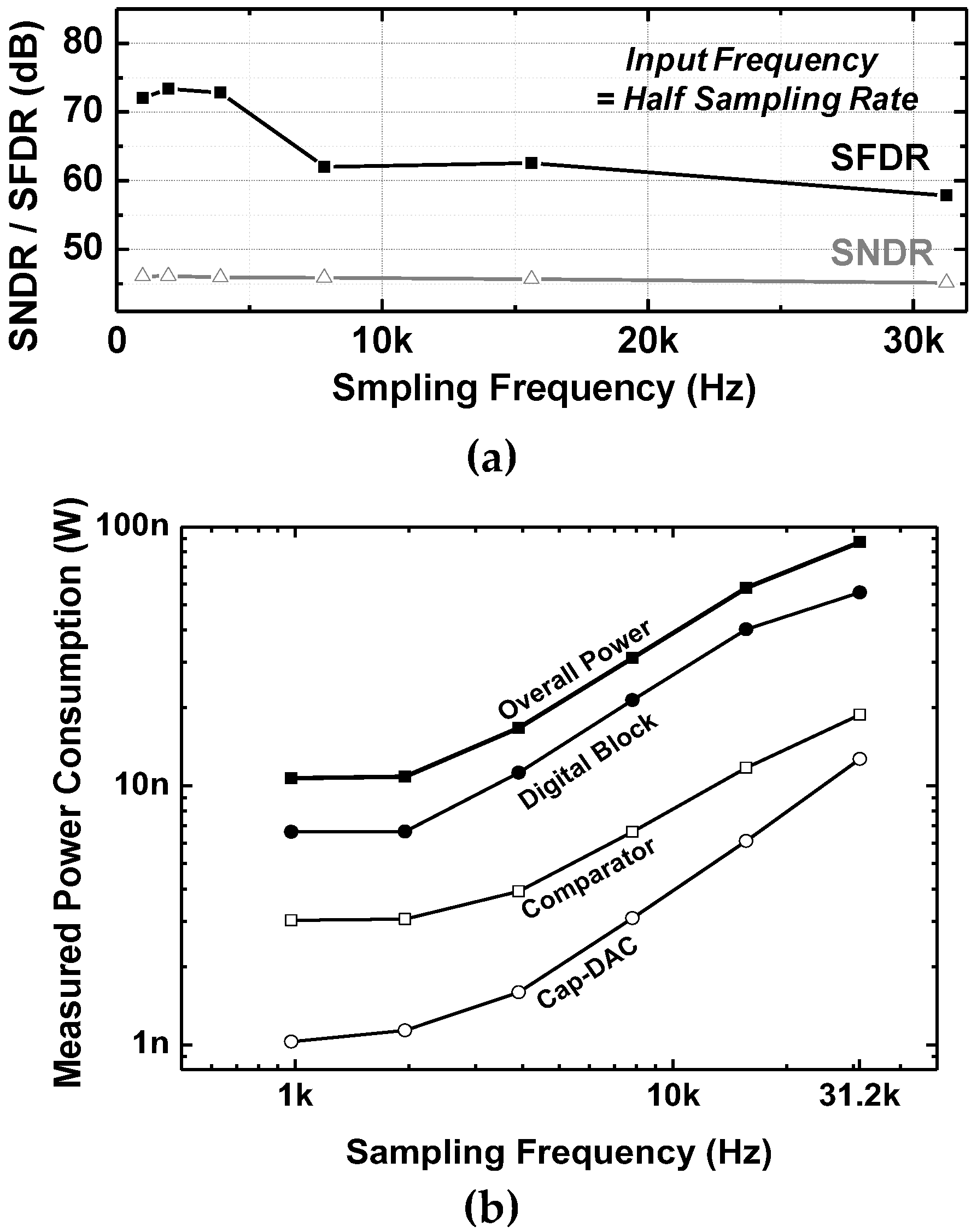

3.2. 0.5 V-SAR ADC with Single-Clock Bootstrapping and Time-Delay Based Controller

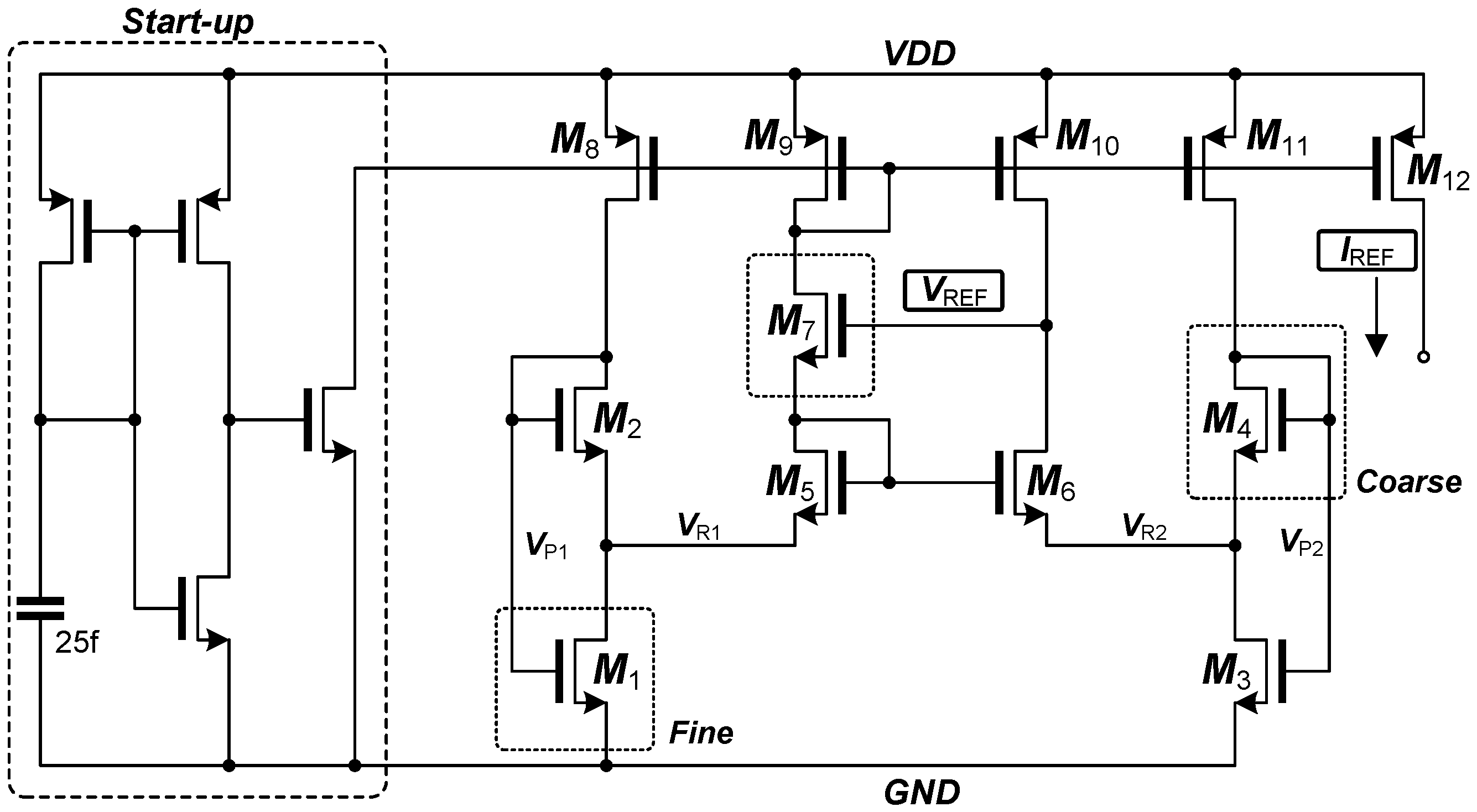

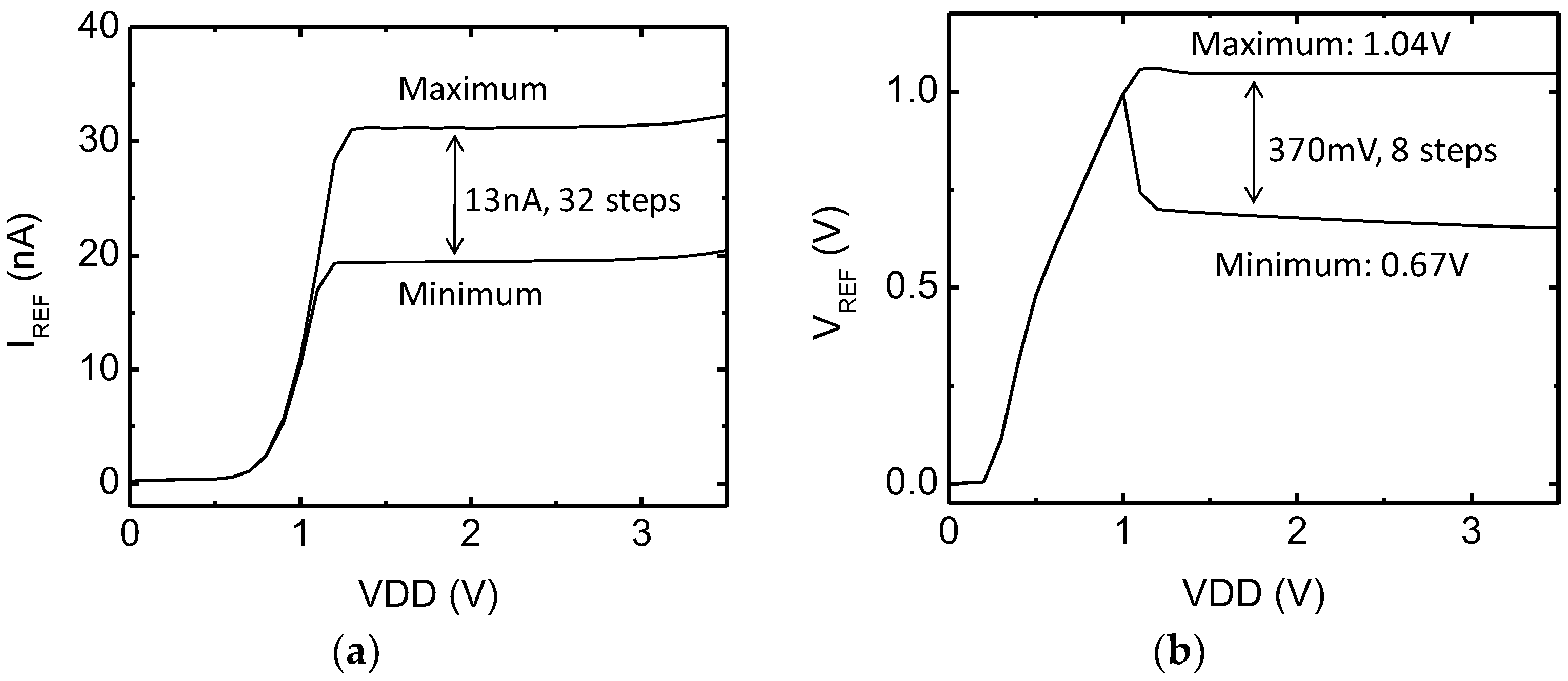

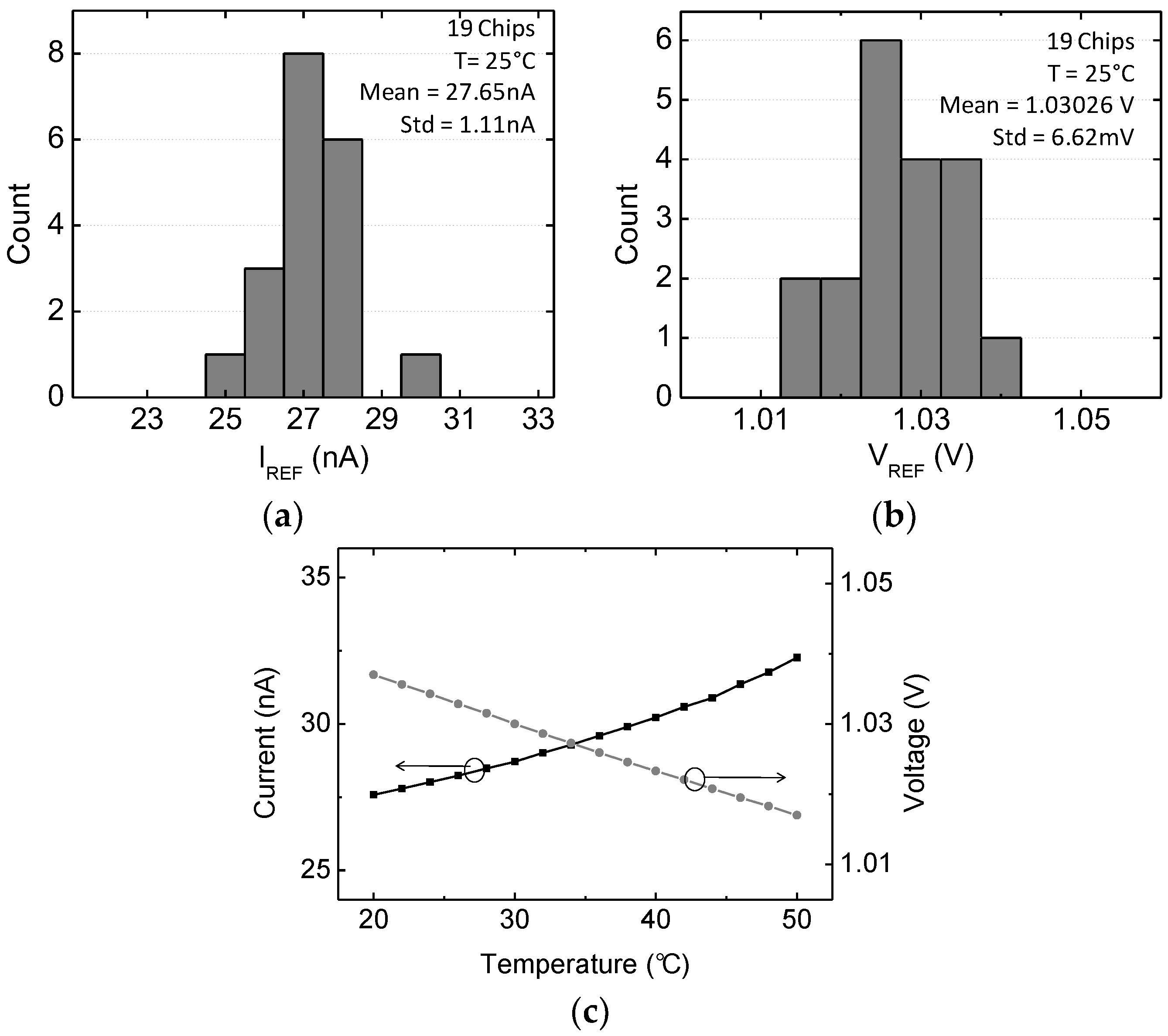

3.3. Programmable Monolithic Voltage and Current Reference

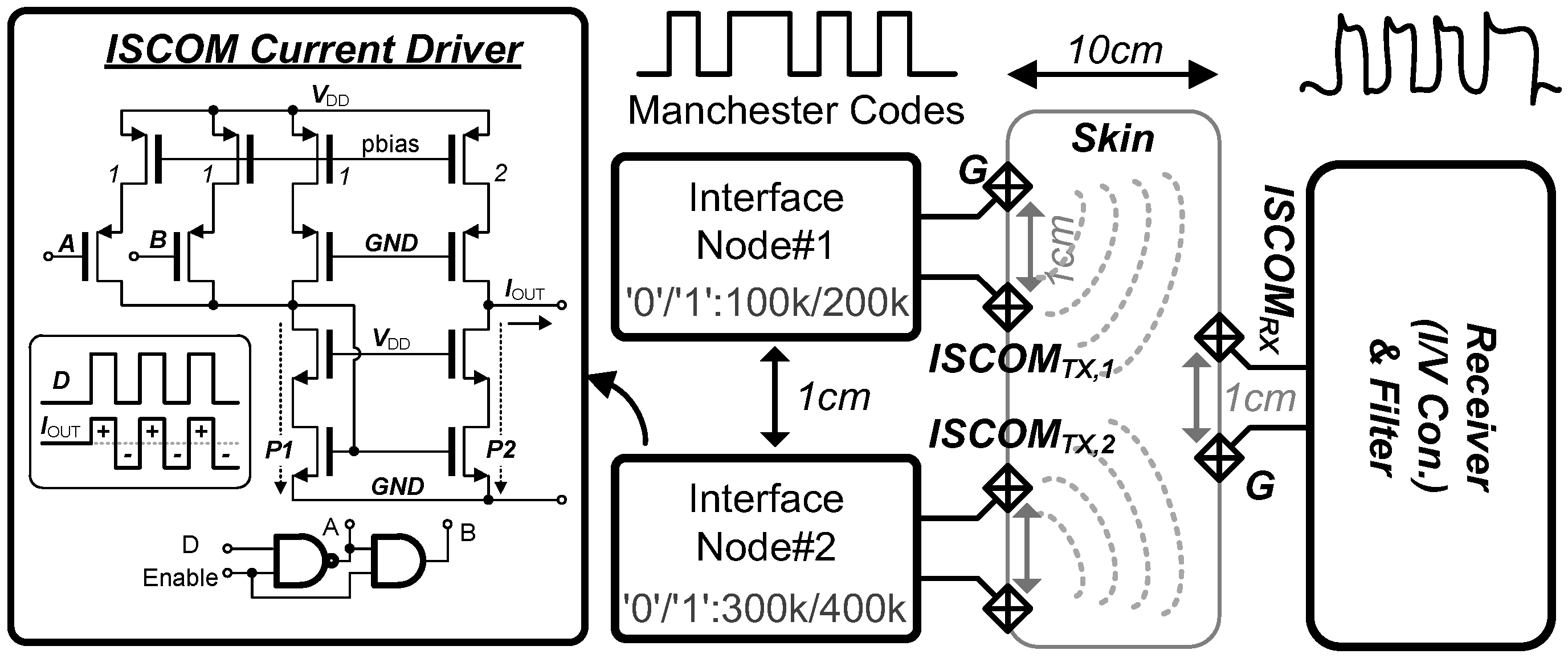

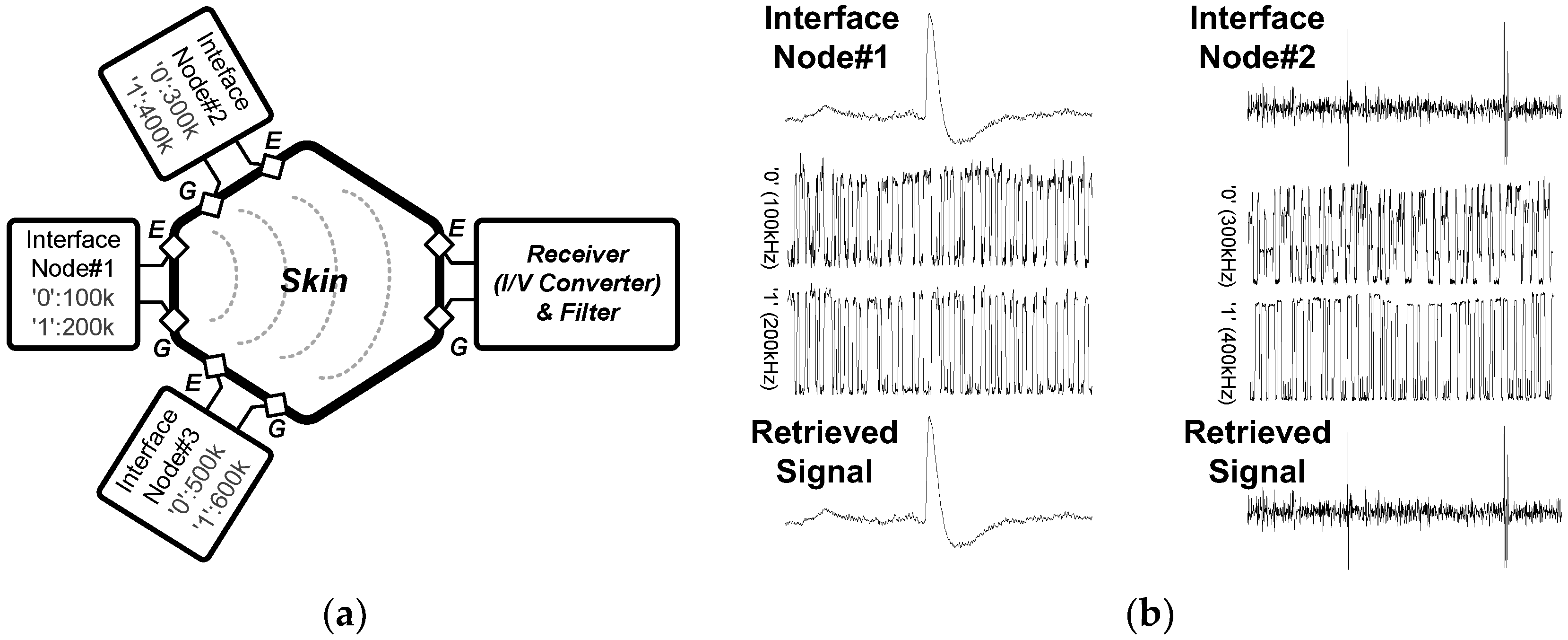

3.4. Intra-Skin Communication for Modular Expandable Systems

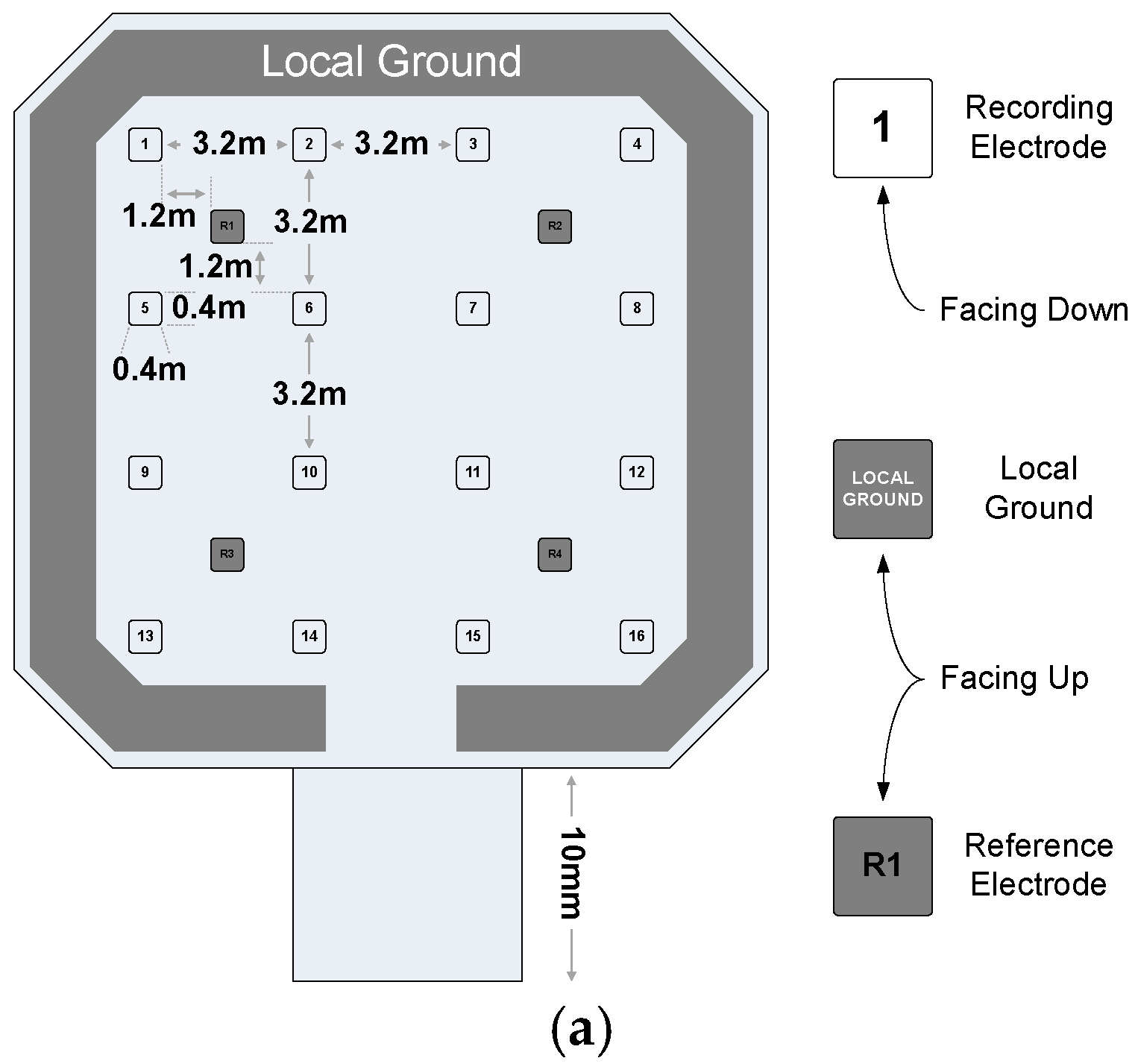

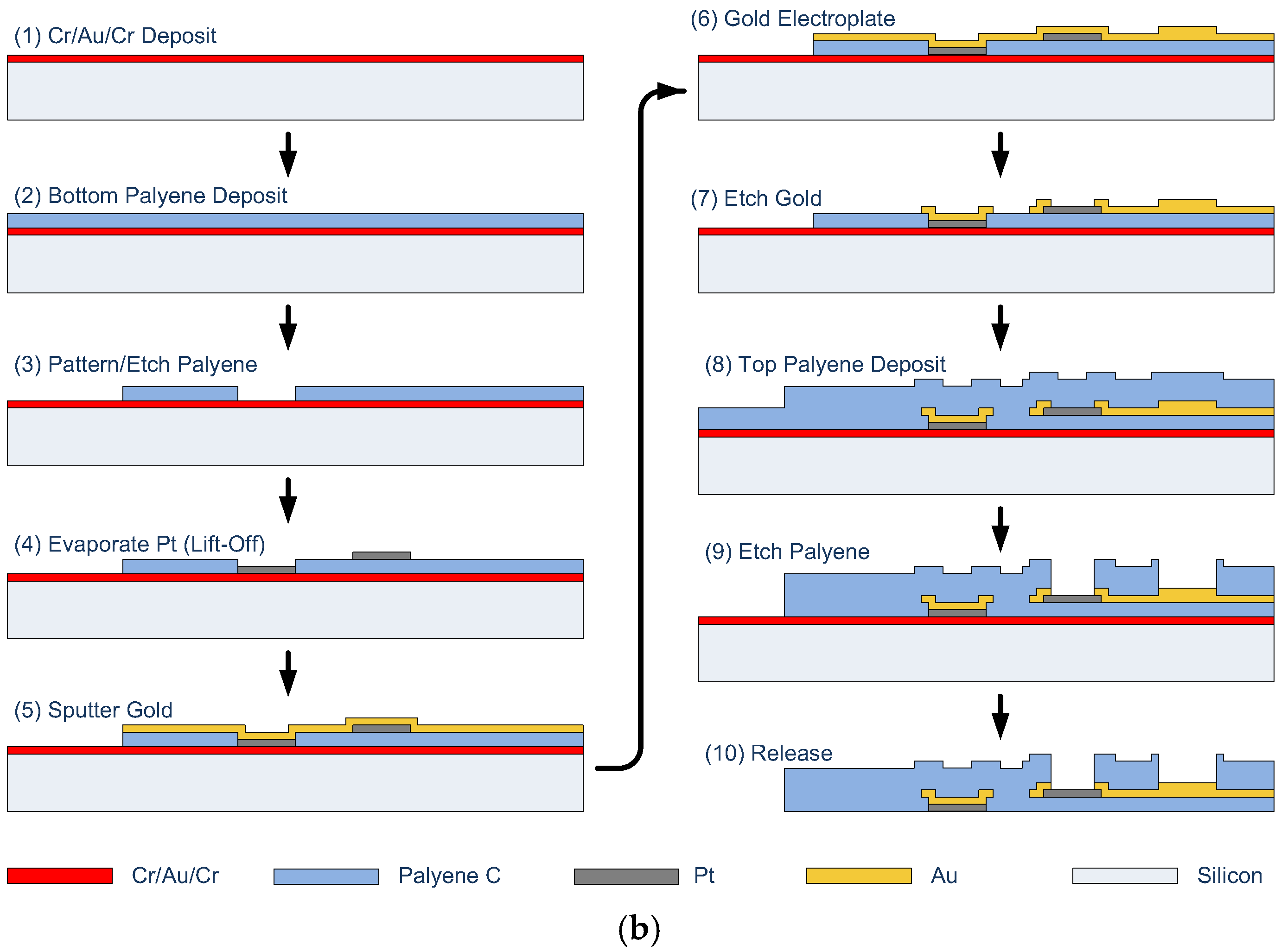

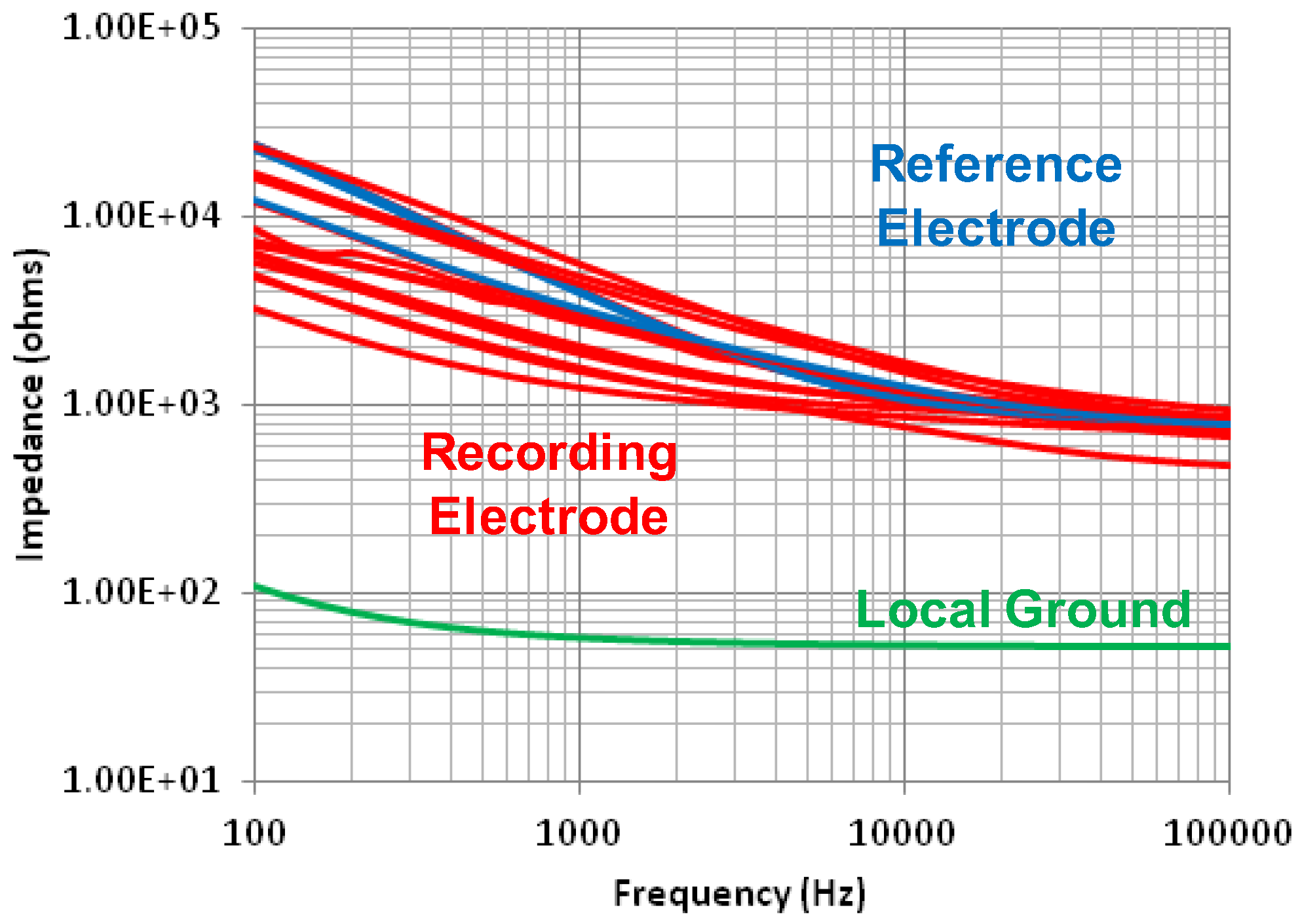

4. Microfabricated Flexible Electrode Array

5. Measurement Results

5.1. System Characteristics Measurement

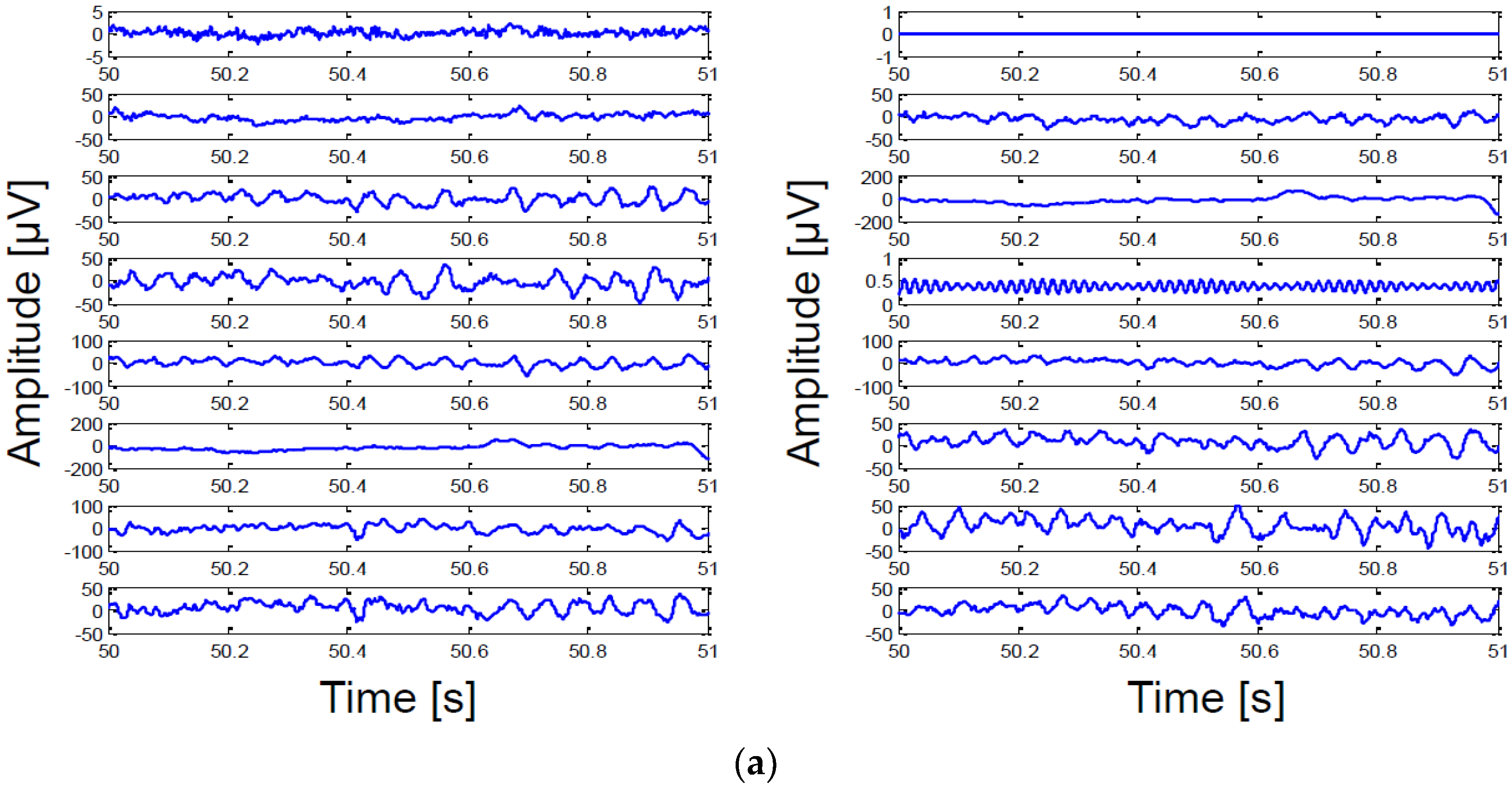

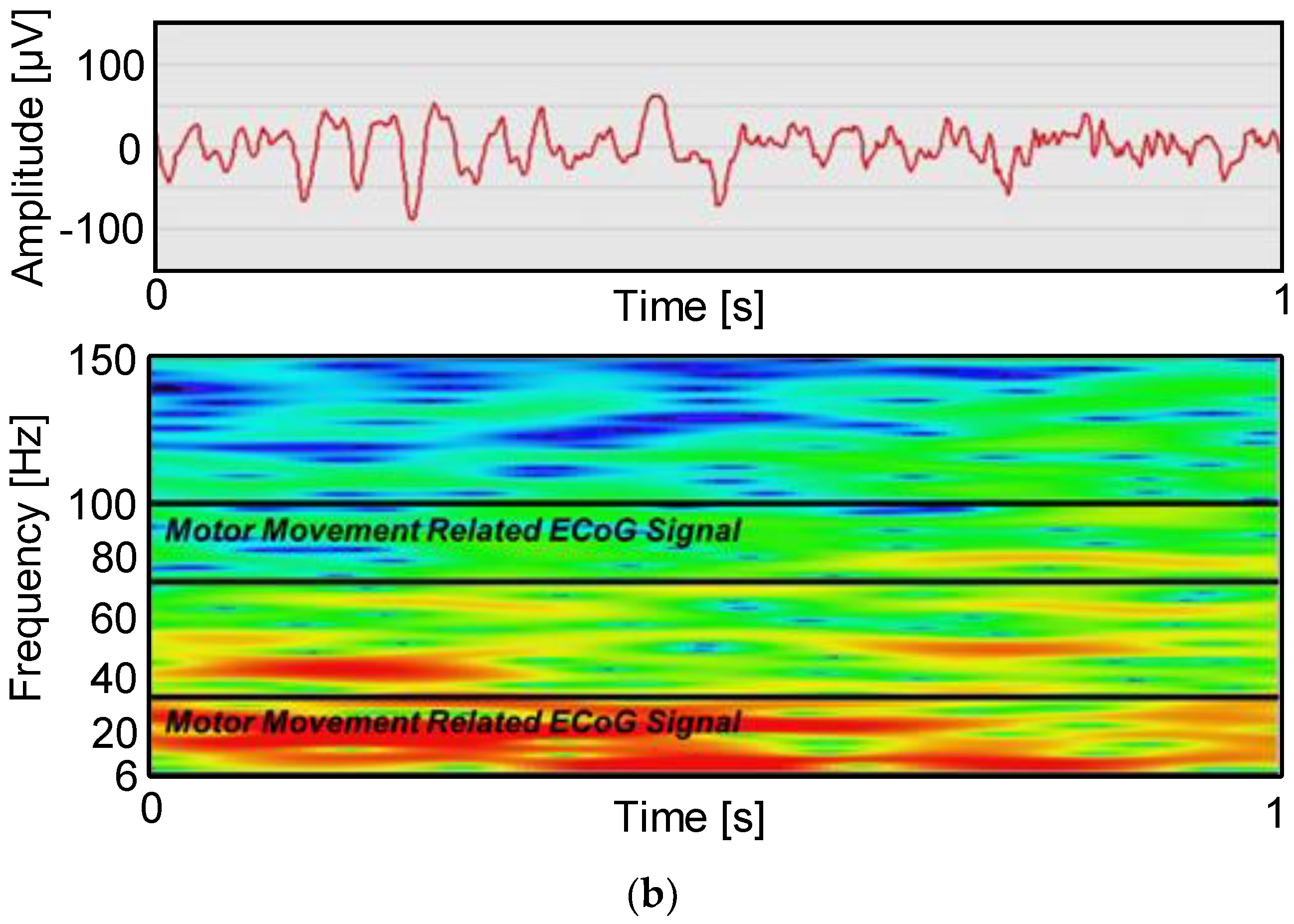

5.2. In Vivo Measurement

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Schwarz, D.A.; Lebedev, M.A.; Hanson, T.L.; Dimitrov, D.F.; Lehew, G.; Meloy, J.; Rajangam, S.; Subramanian, V.; Ifft, P.J.; Li, Z.; et al. Chronic, wireless recordings of large-scale brain activity in freely moving rhesus monkeys. Nat. Methods 2014, 11, 670–676. [Google Scholar] [CrossRef] [PubMed]

- Buzsáki, G.; Stark, E.; Berényi, A.; Khodagholy, D.; Kipke, D.R.; Yoon, E.; Wise, K.D. Tools for Probing Local Circuits: High-Density Silicon Probes Combined with Optogenetics. Neuron 2015, 86, 92–105. [Google Scholar] [CrossRef] [PubMed]

- Suner, S.; Fellows, M.R.; Vargas-Irwin, C.; Nakata, G.K.; Donoghue, J.P. Reliability of Signals from a Chronically Implanted, Silicon-Based Electrode Array in Non-Human Primate Primary Motor Cortex. IEEE Trans. Neural Syst. Rehabil. Eng. 2005, 13, 524–541. [Google Scholar] [CrossRef] [PubMed]

- Schalk, G. Can Electrocorticography (ECoG) Support Robust and Powerful Brain-Computer Interfaces? Front. Neuroeng. 2010, 3, 9. [Google Scholar] [CrossRef] [PubMed]

- Muller, R.; Le, H.P.; Li, W.; Ledochowitsch, P.; Gambini, S.; Bjorninen, T.; Koralek, A.; Carmena, J.M.; Maharbiz, M.M.; Alon, E.; et al. A Minimally Invasive 64-Channel Wireless µECoG Implant. IEEE J. Solid-State Circuits 2015, 50, 344–359. [Google Scholar] [CrossRef]

- Mestais, C.S.; Charvet, G.; Sauter-Starace, F.; Foerster, M.; Ratel, D.; Benabid, A.L. WIMAGINE: Wireless 64-channel ECoG Recording Implant for Long Term Clinical Applications. IEEE Trans. Neural Syst. Rehabil. Eng. 2015, 23, 10–21. [Google Scholar] [CrossRef] [PubMed]

- Borton, D.A.; Yin, M.; Aceros, J.; Nurmikko, A. An implantable wireless neural interface for recording cortical circuit dynamics in moving primates. J. Neural Eng. 2013, 10, 26010. [Google Scholar] [CrossRef] [PubMed]

- Chang, S.; Alashmouny, K.; Mccormick, M.; Chen, Y.; Yoon, E. BioBolt: A Minimally-Invasive Neural Interface for Wireless Epidural Recording by Intra-Skin Communication. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 15–17 June 2011; Volume 2. [Google Scholar]

- Zhang, F.; Mishra, A.; Richardson, A.G.; Otis, B. A Low-Power ECoG/EEG Processing IC with Integrated Multiband Energy Extractor. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 2069–2082. [Google Scholar] [CrossRef]

- Robinet, S.; Audebert, P.; Régis, G.; Zongo, B.; Beche, J.; Condemine, C.; Filipe, S.; Charvet, G. A Low-Power 0.7µVrms 32-Channel Mixed-Signal Circuit for ECoG Recordings. IEEE J. Emerg. Sel. Top. Circuits Syst. 2012, 1, 451–460. [Google Scholar] [CrossRef]

- Verma, N.; Shoeb, A.; Bohorquez, J.; Dawson, J.; Guttag, J.; Chandrakasan, A.P. A Micro-Power EEG Acquisition SoC with Integrated Feature Extraction Processor for a Chronic Seizure Detection System. IEEE J. Solid-State Circuits 2010, 45, 804–816. [Google Scholar] [CrossRef]

- Kellis, S.S.; House, P.A.; Thomson, K.E.; Brown, R.; Greger, B. Human neocortical electrical activity recorded on nonpenetrating microwire arrays: Applicability for neuroprostheses. Neurosurg. Focus 2009, 27, E9. [Google Scholar] [CrossRef] [PubMed]

- Castagnola, E.; Maiolo, L.; Maggiolini, E.; Minotti, A.; Marrani, M.; Maita, F.; Pecora, A.; Angotzi, G.N.; Ansaldo, A.; Fadiga, L.; et al. Ultra-flexible and brain-conformable micro-electrocorticography device with low impedance PEDOT-carbon nanotube coated microelectrodes. In Proceedings of the 2013 6th International IEEE/EMBS Conference on Neural Engineering (NER), San Diego, CA, USA, 6–8 November 2013; pp. 927–930. [Google Scholar]

- Fukushima, M.; Saunders, R.C.; Mullarkey, M.; Doyle, A.M.; Mishkin, M.; Fujii, N. An electrocorticographic electrode array for simultaneous recording from medial, lateral, and intrasulcal surface of the cortex in macaque monkeys. J. Neurosci. Methods 2014, 233, 155–165. [Google Scholar] [CrossRef] [PubMed]

- Branco, M.P.; Freudenburg, Z.V.; Aarnoutse, E.J.; Bleichner, M.G.; Vansteensel, M.J.; Ramsey, N.F. Decoding hand gestures from primary somatosensory cortex using high-density ECoG. Neuroimage 2017, 147, 130–142. [Google Scholar] [CrossRef] [PubMed]

- Khodagholy, D.; Gelinas, J.N.; Thesen, T.; Doyle, W.; Devinsky, O.; Malliaras, G.G.; Buzsáki, G. NeuroGrid: Recording action potentials from the surface of the brain. Nat. Neurosci. 2015, 18, 310–315. [Google Scholar] [CrossRef] [PubMed]

- Rubehn, B.; Bosman, C.; Oostenveld, R.; Fries, P.; Stieglitz, T. A MEMS-based flexible multichannel ECoG-electrode array. J. Neural Eng. 2009, 6, 36003. [Google Scholar] [CrossRef] [PubMed]

- Rizk, M.; Obeid, I.; Callender, S.H.; Wolf, P.D. A single-chip signal processing and telemetry engine for an implantable 96-channel neural data acquisition system. J. Neural Eng. 2007, 4, 309–321. [Google Scholar] [CrossRef] [PubMed]

- Avestruz, A.; Santa, W.; Carlson, D. A 5 µW/Channel Spectral Analysis IC for Chronic Bidirectional Brain–Machine Interfaces. IEEE J. Solid-State Circuits 2008, 43, 3006–3024. [Google Scholar] [CrossRef]

- Denison, T.; Consoer, K.; Santa, W.; Molnar, G.; Mieser, K. A 2 μW, 95 nV/√Hz, chopper-stabilized instrumentation amplifier for chronic measurement of bio-potentials. IEEE J. Solid-State Circuits 2007, 42, 1–6. [Google Scholar] [CrossRef]

- Ng, K.A.; Xu, Y.P. A Low-Power, High CMRR Neural Amplifier System Employing CMOS Inverter-Based OTAs with CMFB through Supply Rails. J. Solid-State Circuits 2015, 51, 1–14. [Google Scholar]

- Chang, S.; Park, S.-Y.; Yoon, E. Low-Power Low-Noise Pseudo-Open-Loop Preamplifier for Neural Interfaces. IEEE Sens. J. 2017, 17, 4843–4852. [Google Scholar] [CrossRef]

- Park, S.-Y.; Cho, J.; Yoon, E. 3.37 µW/Ch Modular Scalable Neural Recording System with Embedded Lossless Compression for Dynamic Power Reduction. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. 168–169. [Google Scholar]

- Park, S.-Y.; Cho, J.; Na, K.; Yoon, E. Toward 1024-Channel Parallel Neural Recording: Modular Δ-ΔΣ Analog Front-End Architecture with 4.84fJ/C-s·mm2 Energy-Area Product. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 17–19 June 2015; pp. 112–113. [Google Scholar]

- Zhang, F.; Holleman, J.; Otis, B.P. Design of Ultra-Low Power Biopotential Amplifiers for Biosignal Acquisition Applications. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 344–355. [Google Scholar] [CrossRef] [PubMed]

- Liu, L.; Zou, X.; Goh, W.L.; Ramamoorthy, R.; Dawe, G.; Je, M. 800 nW 43 nV/√Hz Neural Recording Amplifier with Enhanced Noise Efficiency Factor. Electron. Lett. 2012, 48, 479–480. [Google Scholar] [CrossRef]

- Chang, S.; Al-ashmouny, K.; Yoon, E. A 0.5 V 20fJ/Conversion-Step Rail-to-rail SAR ADC with Programmable Time-Delayed Control Units for Low-Power Biomedical Application. In Proceedings of the IEEE European Solid State Circuit Conference, Helsinki, Finland, 12–16 September 2011; pp. 8–11. [Google Scholar]

- Starzyk, J.A.; Jan, Y.; Qiu, F. A DC—DC Charge Pump Design Based on Voltage Doublers. IEEE Trans. Circuits Syst. Theory Appl. 2001, 48, 350–359. [Google Scholar] [CrossRef]

- Abo, A.M.; Gray, P.R. A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter. IEEE J. Solid-State Circuits 1999, 34, 599–606. [Google Scholar] [CrossRef]

- Chang, S.; Alashmouny, K.; Yoon, E. A 1.5 V 120 nW CMOS Programmable Monolithic Reference Generator for Wireless Implantable System. In Proceedings of the 2011 Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Boston, MA, USA, 30 August–3 September 2011; pp. 2981–2984. [Google Scholar]

- Handa, T.; Shoji, S.; Ike, S.; Takeda, S.; Sekiguchi, T. A very low-power consumption wireless ECG monitoring system using body as a signal transmission medium. In Proceedings of the 1997 International Conference on Solid State Sensors and Actuators, 1997. TRANSDUCERS ’97 Chicago, Chicago, IL, USA, 19 June 1997; Volume 2, pp. 1003–1006. [Google Scholar]

- Wegmüller, M.S.; Anatomie, P. Intra-Body Communication for Biomedical Sensor Networks. Ph.D. Thesis, ETH Zurich, Zürich, Switzerland, September 1977. [Google Scholar]

- BIOPAC. Application Note 257 Safe Use of Electrical Stimulators; BIOPAC Systems, Inc.: Goleta, CA, USA, 2010. [Google Scholar]

- Park, S.-Y.; Cho, J.; Lee, K.; Yoon, E. PWM Buck Converter with >80% PCE in 45 uA-to-4 mA Loads Using Analog-Digital Hybrid Control for Biomedical Systems. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 22–26 February 2015; pp. 218–220. [Google Scholar]

- Park, S.-Y.; Cho, J.; Lee, K.; Yoon, E. A PWM Buck Converter with Load-Adaptive Power Transistor Scaling Scheme Using Analog-Digital Hybrid Control for High Energy Efficiency in Implantable Biomedical Systems. Trans. Biomed. Circuits Syst. 2015, 9, 885–895. [Google Scholar] [CrossRef] [PubMed]

- Leuthardt, E.C.; Schalk, G.; Wolpaw, J.R.; Ojemann, J.G.; Moran, D.W. A brain-computer interface using electrocorticographic signals in humans. J. Neural Eng. 2004, 1, 63–71. [Google Scholar] [CrossRef] [PubMed]

| Parameters | Measured Results | |

|---|---|---|

| Recording Integrated Circuit | ||

| Supply voltage (internally generated) | 0.5/1.0 V | |

| Supply voltage (externally supplied) | 1.5–3.3 V (Li-Ion rechargeable battery) | |

| Power/Ch. | 2.5 µW | |

| Gain | 100–1000 V/V (variable) | |

| NEF/PEF | (1~500 Hz) | 5.2/27.04 |

| (10 Hz to 10 kHz) | 1.69/2.86 | |

| Resolution | 8 bit | |

| CMRR | 35 dB | |

| PSRR | 48 dB | |

| Active area | 3.2 mm × 0.9 mm (with ISCOM) | |

| Wireless Communication | ||

| Communication method | Intra-Skin Communication (ISCOM) | |

| Supply voltage | 1.0 V | |

| Modulation | FSK | |

| Data bandwidth | >100 kb/s | |

| Link gain | −17 dB | |

| Power | 160 µW | |

| Carrier frequency | 2–4 MHz | |

| Bit error rate | 10−6 | |

| Flexible Microelectrode Array | ||

| Materials | Pt on Parylene-C | |

| Number of recording/reference channel | 16/4 | |

| Impedance of electrodes @ 1 kHz | 1.2–5.6 kΩ | |

| Electrode size | 400 µm in diameter | |

| Total Area | 18 mm × 18 mm | |

| [5] | [6] | [9] | [11] | [19] (2) | [20] (2) | This Work | ||

|---|---|---|---|---|---|---|---|---|

| Integrated Circuits | Power/Ch. (µW) | 2.3 | 134 | 10.8 | 3.5 | 5 | 2 | 2.5 |

| Total Power (µW) | 225 | − | − | 3.5 | 20 | 2 | 365 | |

| Supply (V) | 0.5 | 3 | 1.2 | 1 | 1.4–3.3 | 1.8 | 1.0/0.5 | |

| N. of channel | 64 | 64 | 1 | 1 | 4 | 1 | 16 | |

| Channel gain (dB) | 30 | 60 | 40–75 | 72 | 54–80 | 41,50.5 | 40–60 | |

| Noise PSD (µVrms/√Hz) (nV/√Hz) | 58 | 30 (1) | 85 | 130 | 100 | 100 | 47 | |

| NEF | 4.76 | 3.5 | 5.38 | 9.37 | 4.6 | 4.6 | 1.69/5.86 | |

| PEF | 11.3 | 42.9 (1) | 34.7 | 87.8 | 38.1 (1) | 38.1 (1) | 2.86/27.04 | |

| CMRR (dB) | 82 | 51 | 80 | 60 | >80 | 100 | 35 | |

| PSRR (dB) | 75 | 69 | 60 | − | >80 | − | 48 | |

| Area/Ch. (mm2) | 0.025 | 2.69 | 2.8 | 0.6 | 5 | 0.8 | 0.155 | |

| Resolution (bit) | 15 | 12 | 24 (3) | 12 | − | − | 8 | |

| SNDR/SFDR (dB) | −/52 | 66.17/- | −/− | 65.3/− | −/− | −/− | 45.14/73 | |

| fS (kS/s) | − | 3 | − | 100 | − | − | 31.25 | |

| Wireless (Y/N) | Yes | Yes | No | No | No | No | Yes | |

| Technology (µm) | 0.065 | 0.35 | 0.13 | 0.18 | 0.8 | 0.8 | 0.25 | |

| Electrode Array | Fabrication | Yes | Yes | No | No | No | No | Yes |

| Diameter (µm) | 260 | − | − | − | − | − | 300–500 | |

| Impedance (kΩ) | 10 @100 Hz | − (4) | − | − | − | − | 1.2–5.6 @1 kHz | |

| Material for electrode | Pt/Au | Pt/Ir | − | − | − | − | Pt | |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chang, S.-I.; Park, S.-Y.; Yoon, E. Minimally-Invasive Neural Interface for Distributed Wireless Electrocorticogram Recording Systems. Sensors 2018, 18, 263. https://doi.org/10.3390/s18010263

Chang S-I, Park S-Y, Yoon E. Minimally-Invasive Neural Interface for Distributed Wireless Electrocorticogram Recording Systems. Sensors. 2018; 18(1):263. https://doi.org/10.3390/s18010263

Chicago/Turabian StyleChang, Sun-Il, Sung-Yun Park, and Euisik Yoon. 2018. "Minimally-Invasive Neural Interface for Distributed Wireless Electrocorticogram Recording Systems" Sensors 18, no. 1: 263. https://doi.org/10.3390/s18010263

APA StyleChang, S.-I., Park, S.-Y., & Yoon, E. (2018). Minimally-Invasive Neural Interface for Distributed Wireless Electrocorticogram Recording Systems. Sensors, 18(1), 263. https://doi.org/10.3390/s18010263