0.5 V and 0.43 pJ/bit Capacitive Sensor Interface for Passive Wireless Sensor Systems

Abstract

:1. Introduction

2. Operating Principle

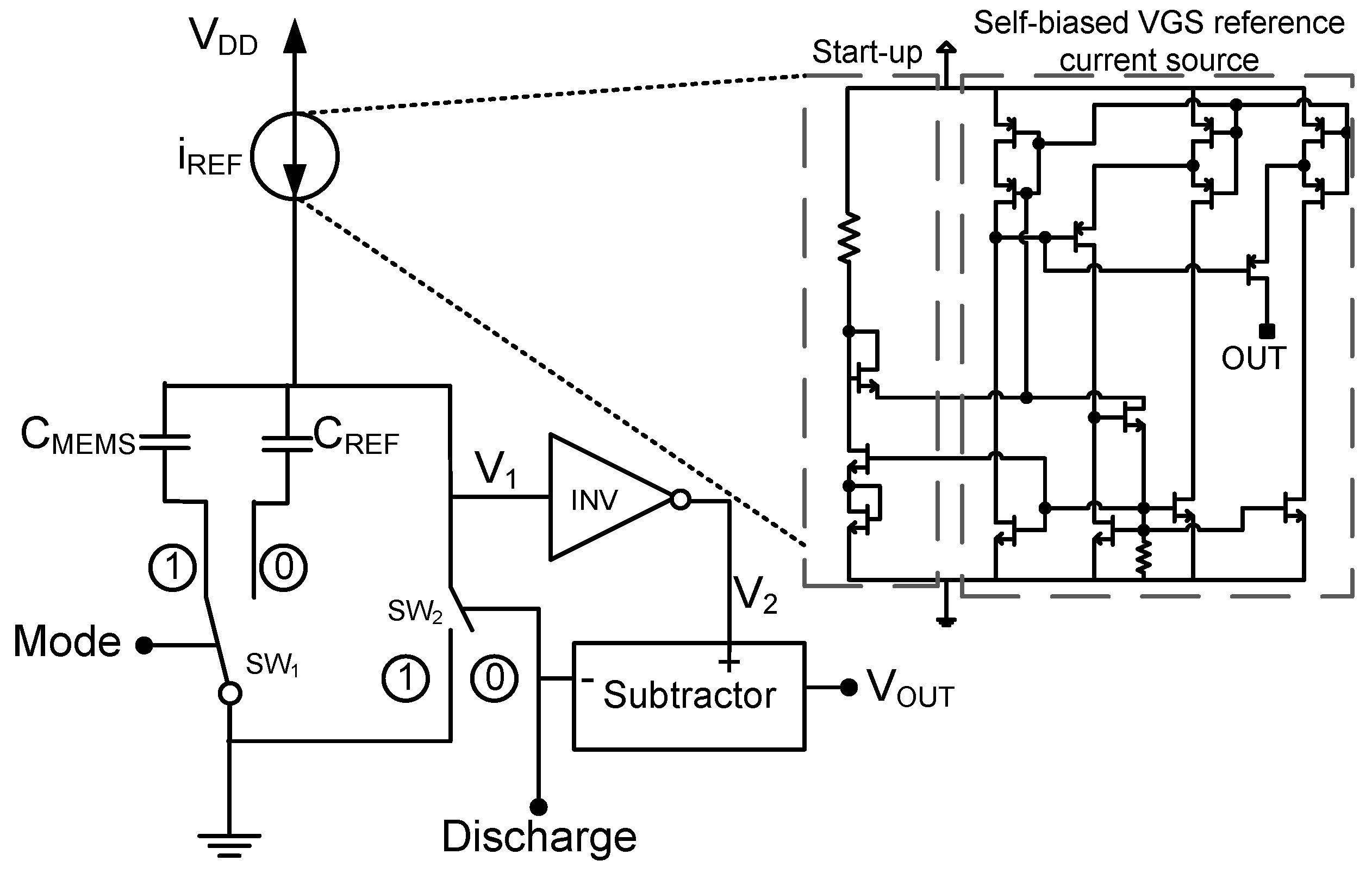

2.1. Architecture

2.2. PVT Variations

2.3. Parasitic Capacitance

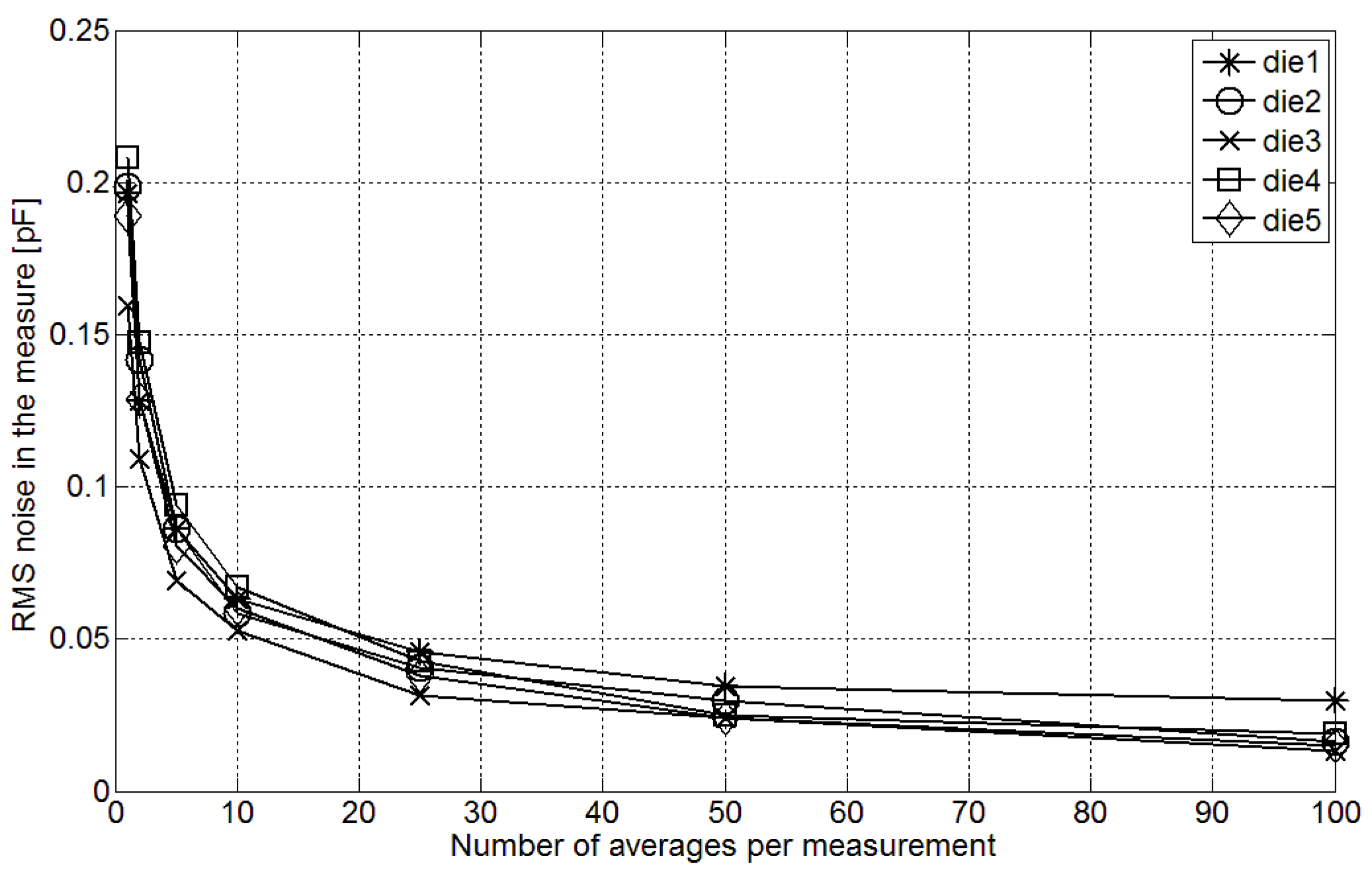

2.4. Resolution

2.5. Current Source

2.6. Model Validation

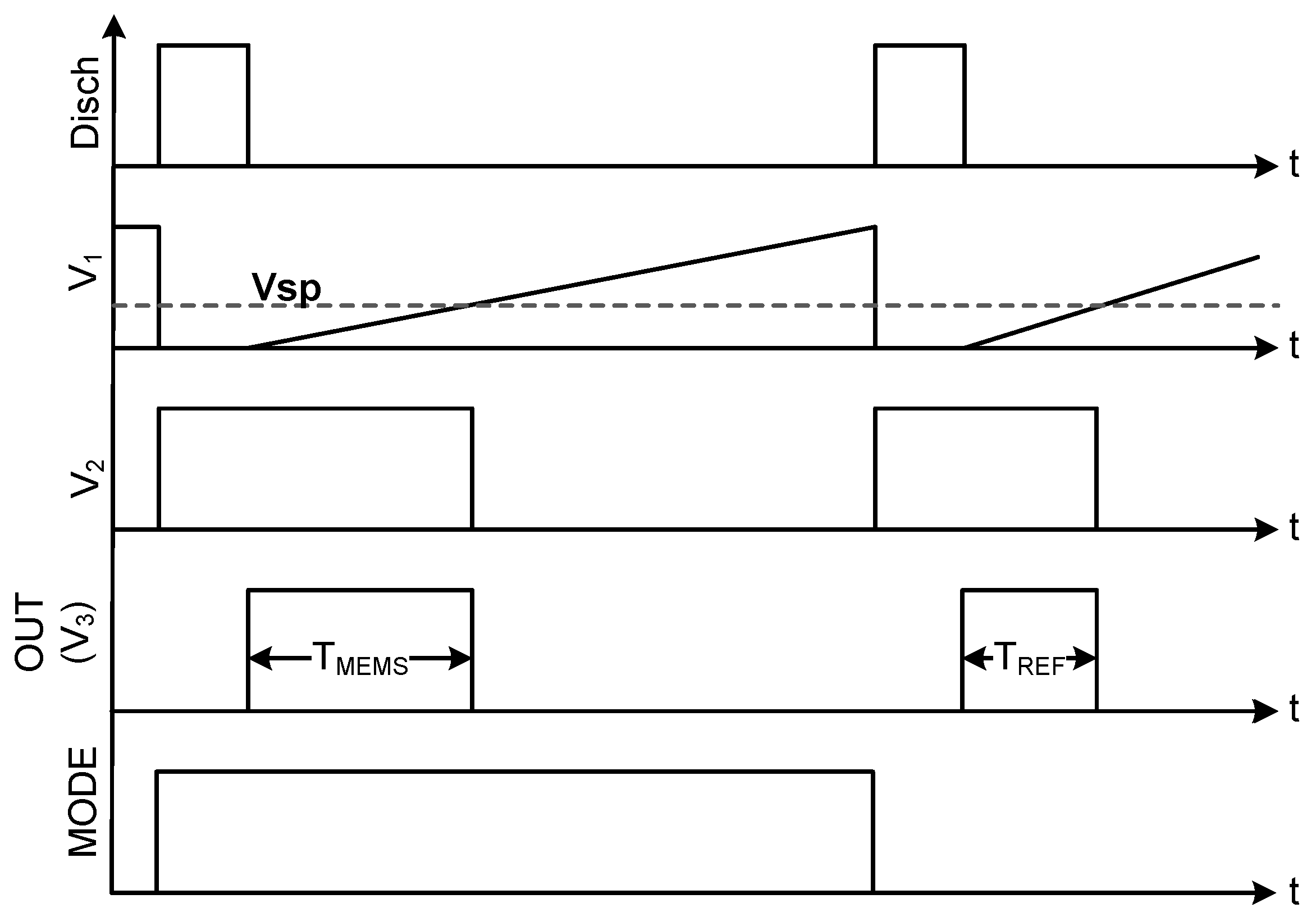

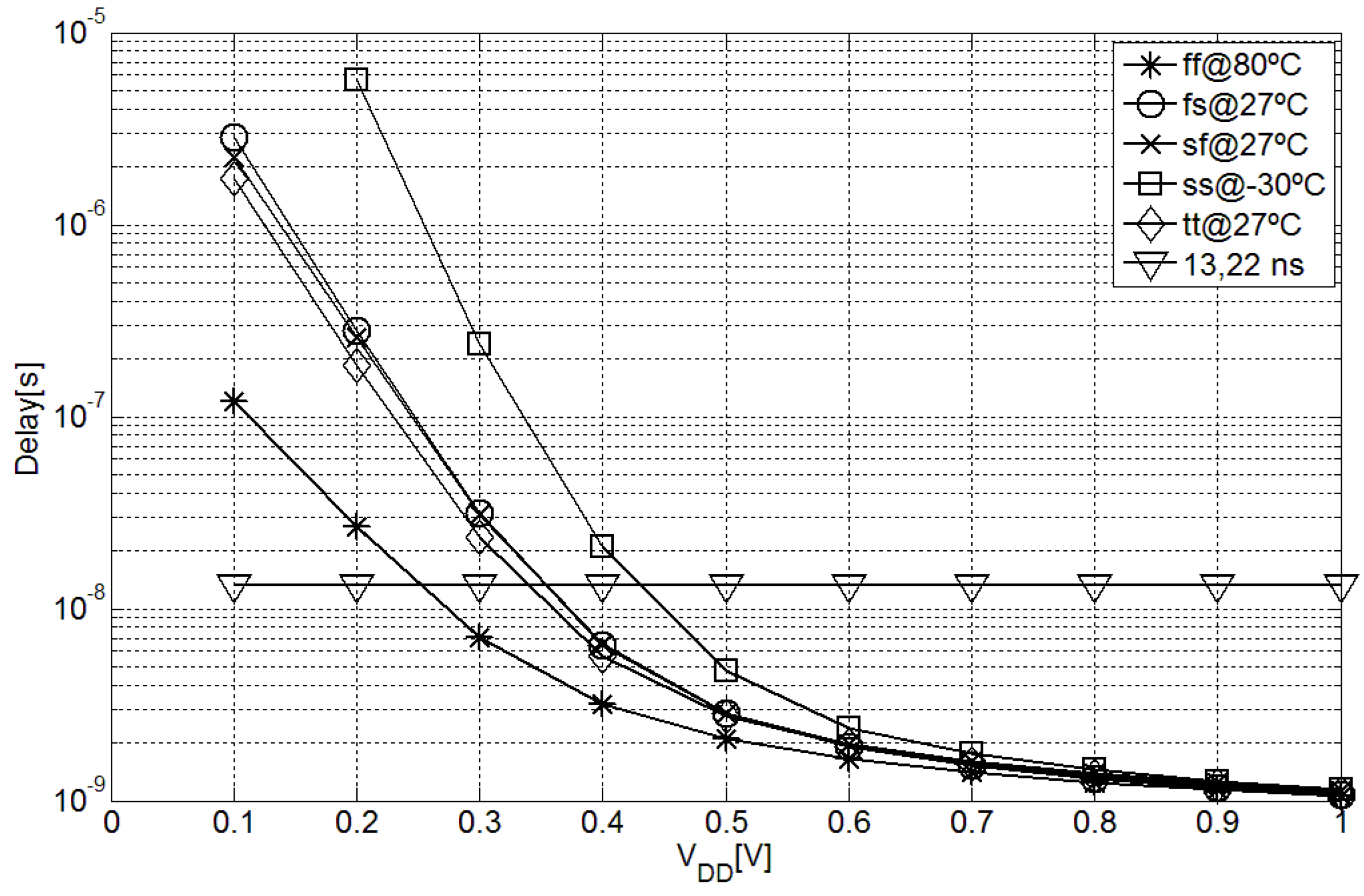

2.6.1. Delay

2.6.2. Switching Voltage

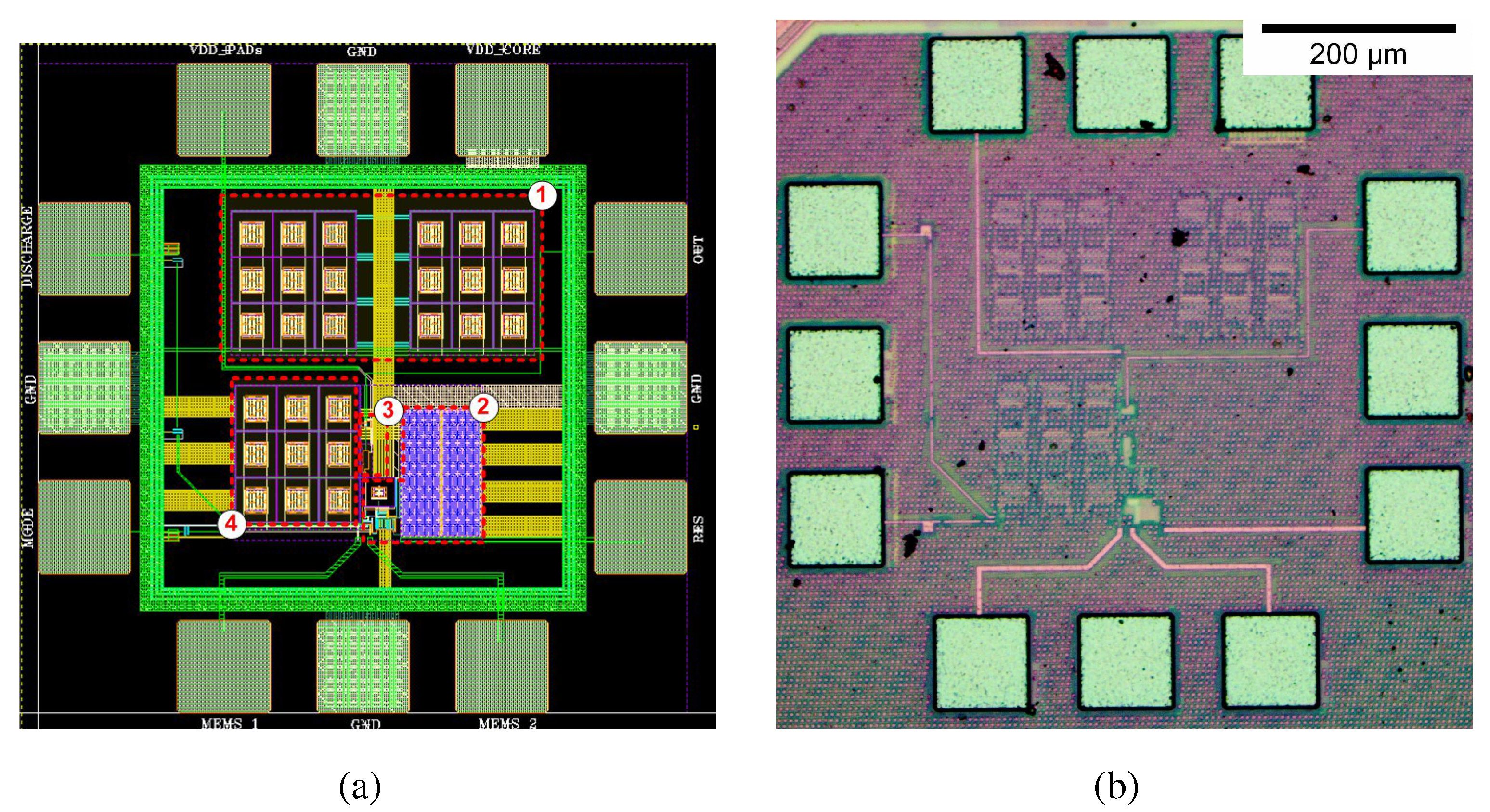

3. Experimental Section

3.1. Results

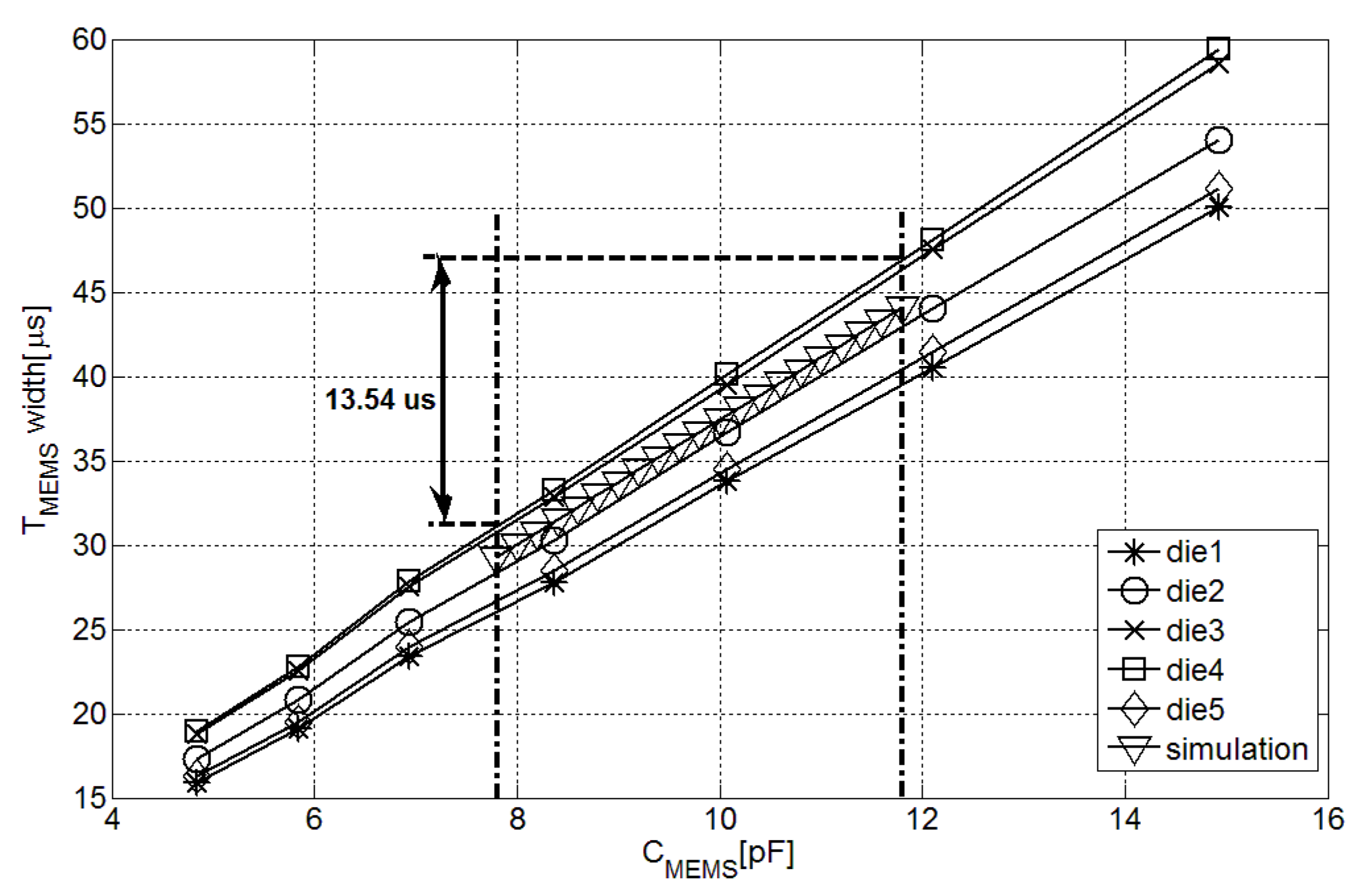

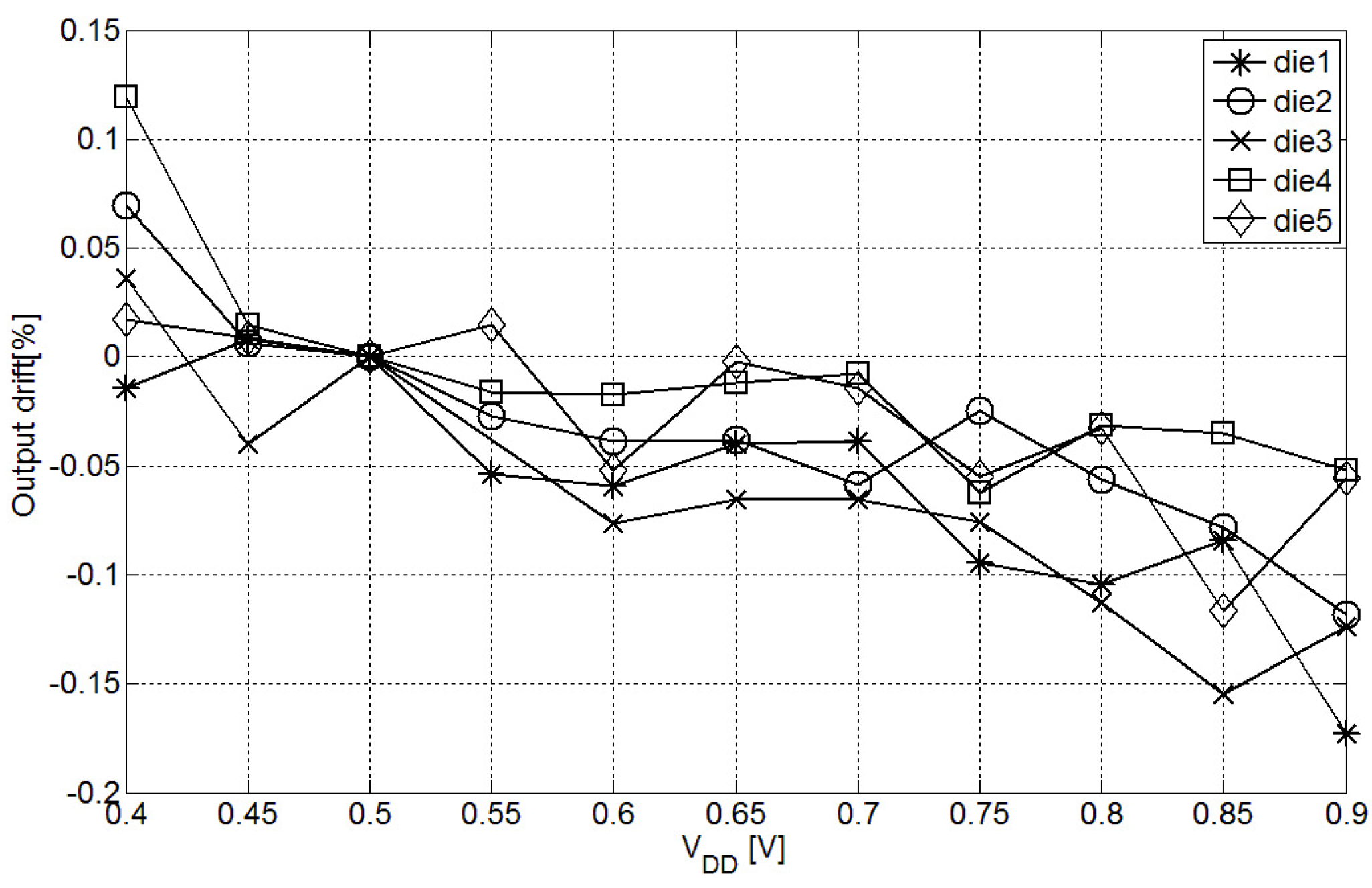

3.1.1. Capacitance-to-Time Conversion

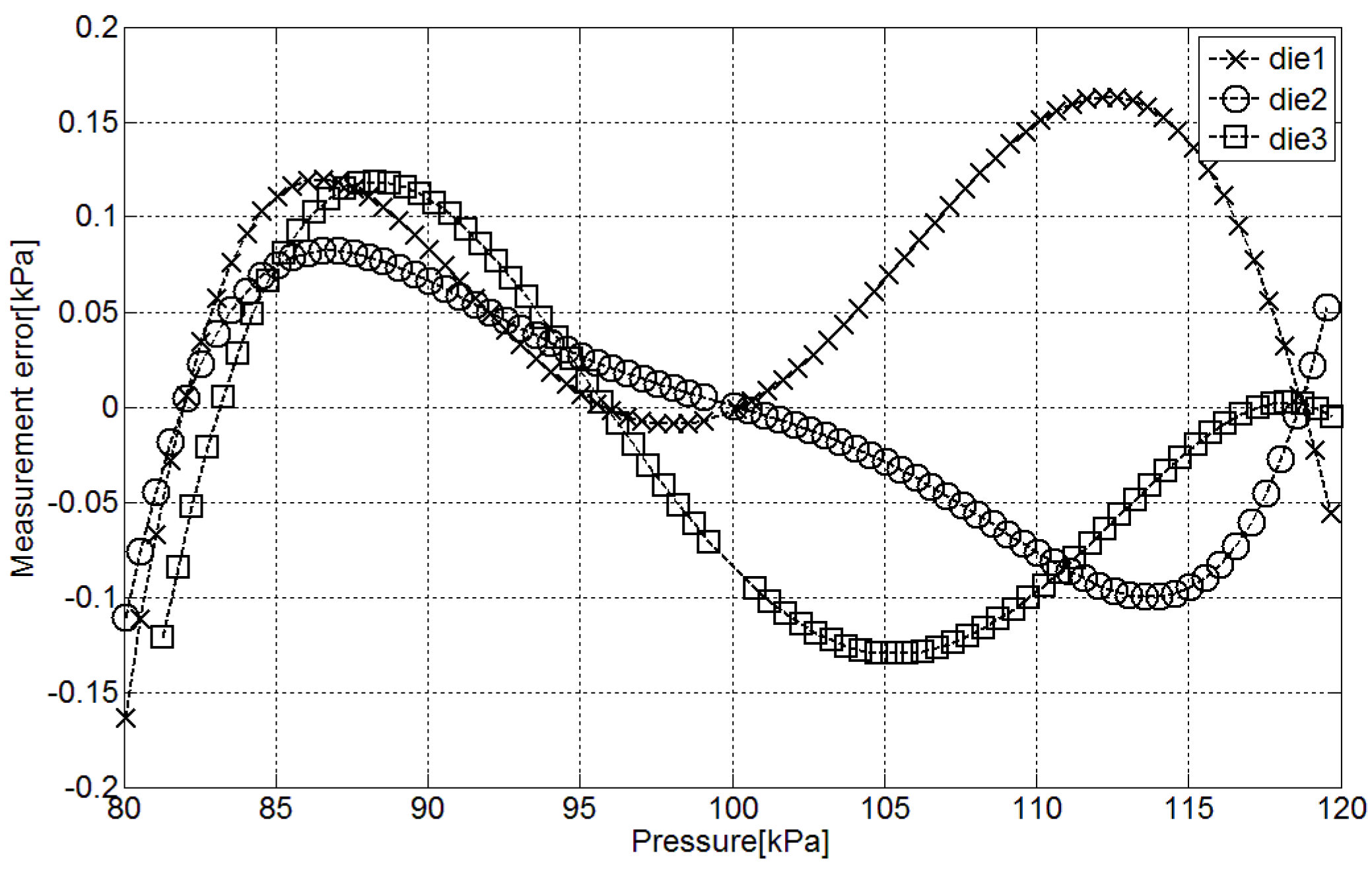

3.1.2. Pressure-to-Time Conversion

3.2. Discussion

| Ref. | Type | Tech | Act. Area | Input | Supply | Current | Meas. | Eff. Res. | Out | FOM |

|---|---|---|---|---|---|---|---|---|---|---|

| (μm) | (mm) | Cap. (pF) | (V) | Cons. | Time. | (bit) | ||||

| ISCC’14 [9] | SAR ADC | 0.18 | 0.49 | 2.5∖75.3 | 1.2–0.9 | 160 | 4 ms | 13.3 | Digital | 0.063 pJ |

| TCASII’11 [10] | 0.35 | 0.048 | –0.5∖0.5 | 3.3 | 436 μA | 0.128 ms | 11 | Digital | 90 pJ | |

| A-SSCC’11 [11] | 0.16 | 0.25 | 0.4∖1.2 | 1.8 | 5.85 μA | 10 ms | 13 | Time | 13 pJ | |

| ESSCIRC’11 [5] | PM | 0.13 | 0.0725 | 6∖6.3 | 0.3 | 0.9 μA | 1 ms | 6.1 | Time | 3.9 pJ |

| JSSC’12 [4] | PM | 0.35 | 0.51 | 6.8 | 3.3 | 64 μA | 7.6 ms | 15 | Time | 49 pJ |

| ESSCIRC’08 [6] | PWM | 0.32 | 0.528 | 0.5∖0.76 | 3 | 28 μA | 0.033 ms | 8 | Time | 10.8 pJ |

| TIM’12 [3] | PWM | 0.35 | 0.09 | 2.5∖2.82 | 3 | 18 μA | 0.04 ms | 9.3 | Time | 3.4pJ |

| This work | PWM | 0.09 | 0.045 | 10 | 0.5 | 1.02 ms | 10 | Time | 0.43 pJ |

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Harrop, P.; Das, R. Wireless Sensor Networks (WSN) 2012-2022: Forecasts, Technologies, Players. The New Market for Ubiquitous Sensor Networks (USN); Technical Report; IDTechEx: Cambridge, UK, 2012. [Google Scholar]

- Bergeret, E.; Gaubert, J.; Pannier, P.; Gaultier, J. Modeling and Design of CMOS UHF Voltage Multiplier for RFID in an EEPROM Compatible Process. IEEE Trans. Circuits Syst. II Express Briefs 2007, 54, 833–837. [Google Scholar] [CrossRef]

- Sheu, M.L.; Hsu, W.H.; Tsao, L.J. A Capacitance-Ratio-Modulated Current Front-End Circuit with Pulsewidth Modulation Output for a Capacitive Sensor Interface. IEEE Trans. Instrum. Meas. 2012, 61, 447–455. [Google Scholar] [CrossRef]

- Tan, Z.; Shalmany, S.; Meijer, G.; Pertijs, M. An Energy-Efficient 15-Bit Capacitive-Sensor Interface Based on Period Modulation. IEEE J. Solid-State Circuits 2012, 47, 1703–1711. [Google Scholar] [CrossRef]

- Danneels, H.; Coddens, K.; Gielen, G. A fully-digital, 0.3V, 270 nW capacitive sensor interface without external references. In Proceedings of the ESSCIRC (ESSCIRC), Helsinki, Finland, 12–16 September 2011; pp. 287–290.

- Bruschi, P.; Nizza, N.; Dei, M. A low-power capacitance to pulse width converter for MEMS interfacing. In Proceedings of the 34th European Solid-State Circuits Conference (ESSCIRC 2008), Edinburgh, UK, 15–19 September 2008; pp. 446–449.

- Tanguay, L.F.; Sawan, M.; Savaria, Y. A very-high output impedance current mirror for very-low voltage biomedical analog circuits. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems, (APCCAS 2008), Macao, China, 30 November–3 December 2008; pp. 642–645.

- Capacitive Pressure Sensor 1.2 BAR SCB10H-B012FB Datasheet; Technical Report; Murata Electronics Oy: Vantaa, Finland, 2010.

- Ha, H.; Sylvester, D.; Blaauw, D.; Sim, J.Y. 12.6 A 160nW 63.9 fJ/conversion-step capacitance-to-digital converter for ultra-low-power wireless sensor nodes. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 220–221.

- Shin, D.Y.; Lee, H.; Kim, S. A Delta Sigma Interface Circuit for Capacitive Sensors with an Automatically Calibrated Zero Point. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 90–94. [Google Scholar] [CrossRef]

- Tan, Z.; Daamen, R.; Humbert, A.; Souri, K.; Chae, Y.; Ponomarev, Y.; Pertijs, M. A 1.8 V 11 uW CMOS smart humidity sensor for RFID sensing applications. In Proceedings of the 2011 IEEE Asian Solid State Circuits Conference (A-SSCC), Jeju, Korea, 14–16 November 2011; pp. 105–108.

- Jimenez-Irastorza, A.; Beriain, A.; Sevillano, J.; Rebollo, I.; Berenguer, R. A 0.6 V and 0.53 uW nonius TDC for a passive UHF RFID pressure sensor tag. In Proceedings of the 2012 IEEE International Conference on RFID-Technologies and Applications (RFID-TA), Nice, France, 5–7 November 2012; pp. 216–221.

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Beriain, A.; Gutierrez, I.; Solar, H.; Berenguer, R. 0.5 V and 0.43 pJ/bit Capacitive Sensor Interface for Passive Wireless Sensor Systems. Sensors 2015, 15, 21554-21566. https://doi.org/10.3390/s150921554

Beriain A, Gutierrez I, Solar H, Berenguer R. 0.5 V and 0.43 pJ/bit Capacitive Sensor Interface for Passive Wireless Sensor Systems. Sensors. 2015; 15(9):21554-21566. https://doi.org/10.3390/s150921554

Chicago/Turabian StyleBeriain, Andoni, Iñigo Gutierrez, Hector Solar, and Roc Berenguer. 2015. "0.5 V and 0.43 pJ/bit Capacitive Sensor Interface for Passive Wireless Sensor Systems" Sensors 15, no. 9: 21554-21566. https://doi.org/10.3390/s150921554

APA StyleBeriain, A., Gutierrez, I., Solar, H., & Berenguer, R. (2015). 0.5 V and 0.43 pJ/bit Capacitive Sensor Interface for Passive Wireless Sensor Systems. Sensors, 15(9), 21554-21566. https://doi.org/10.3390/s150921554