Performance Comparison of Cross-Like Hall Plates with Different Covering Layers

Abstract

: This paper studies the effects of the covering layers on the performance of a cross-like Hall plate. Three different structures of a cross-like Hall plate in various sizes are designed and analyzed. The Hall plate sensitivity and offset are characterized using a self-built measurement system. The effect of the P-type region over the active area on the current-related sensitivity is studied for different Hall plate designs. In addition, the correlation between the P-type covering layer and offset is analyzed. The best structure out of three designs is determined. Besides, a modified eight-resistor circuit model for the Hall plate is presented with improved accuracy by taking the offset into account.1. Introduction

Nowadays, magnetic sensors based on the Hall effect possess an increasingly wide application in the contact-less measurement for linear position, angular position, velocity, and so on [1–3]. The cross-like Hall plate provides an approach to realize high reliability, compact size, high accuracy and low cost.

As the important characteristics of a Hall sensor, both the current-related sensitivity and the offset have strong impacts on the performance of a Hall plate. A high sensitivity that improves the signal-to-noise ratio of the Hall sensor is often strongly limited by the short-circuit effect [4]. Another major limitation that affects Hall effect sensor performance is the offset. The possible reasons for the offset generation are related to the sensor fabrication process, packaging, operating conditions and aging [5]. Therefore, a real Hall sensor generally has a zero-field offset. In order to eliminate the offset of Hall sensors, a dynamic method known as the “current spinning technique” is often used [6–9]. The geometry plays an important role in the sensitivity and offset [10–15]. In the last few decades, Hall devices with various geometries had been studied, such as square, octagon, cross-like, etc. [16–18]. During these works, it is found that the most promising magnetic sensor with high sensitivity and a low offset is the cross-like Hall plate. For the according design of the signal conditioning circuit, an accurate circuit model for the Hall plate with offset is needed. Even though the existing circuit models for Hall plates are outstanding in some aspects, they more or less have a few disadvantages [19–22]. Some of them have even not obtained high accuracy. On the other side, others have not taken into account the essential physical effects, such as the temperature effect, parasitic effect, offset, and so on.

This work studies the current-related sensitivity and offset of a cross-like Hall plate with different covering layers in detail. We designed multiple Hall cells with different structures. Section 2 introduces these designs and the measurement data. Section 3 analyzes the measurement data from two major aspects: the current-related sensitivity and the offset. Moreover, a modified eight-resistor circuit model with improved accuracy is presented to help the sensor design. Section 4 summarizes all of the work and gives the conclusion.

2. Design and Experiment

2.1. Design of Hall Plate

In this study, we designed three different structures implemented in three Hall chips, and each chip contains five Hall cells in different sizes. All of the Hall chips are fabricated in 0.18-μm BCDliteTM technology provided by GLOBALFOUNDRIES. Existing implants are employed to form the Hall devices without additional processes.

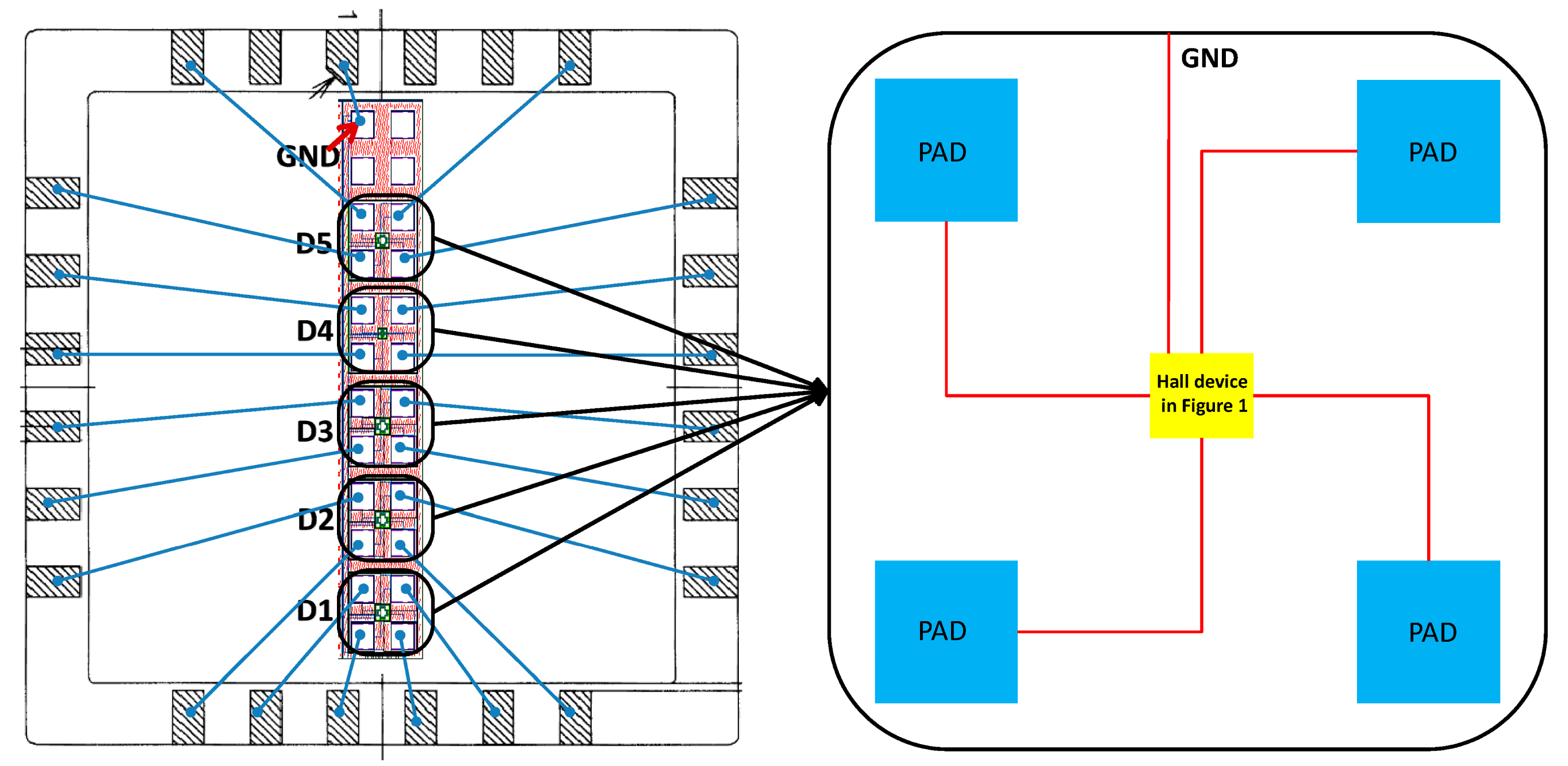

The top and sectional view of the first structure (S1) are shown in Figure 1a and Figure 1b, respectively. This structure consists of an N-well in a P-substrate and four contacts. The active area of the Hall plate is the N-type well region, which is formed in the step of the low voltage P-channel device substrate. The four contacts implemented with N+ implantation are 90° symmetrical. Additionally, two pairs of opposite contacts serve as biasing contacts and measurement contacts, respectively. Figure 1c and Figure 1d illustrate the top view and the cross-section of the second structure (S2). Compared to S1, the active region of the Hall plate is covered with MVPLDD, which is formed in the drain extension of an LDPMOS (laterally-diffused P-channel metal oxide semiconductor). The MVPLDD connected to the ground can generate a depletion region to protect the active region of the Hall plate from the interference of the upper surface. The third structure (S3) of the Hall plate only replaces the MVPLDD by the P+ implant to bury the active area of the Hall plate. In order to improve the stability of the Hall device, both the P+ and MVPLDD layers act as P-type layers to protect the active region of the Hall plate [18]. The schematic block diagram of Hall cells in a chip is shown in Figure 2.

2.2. Measurement

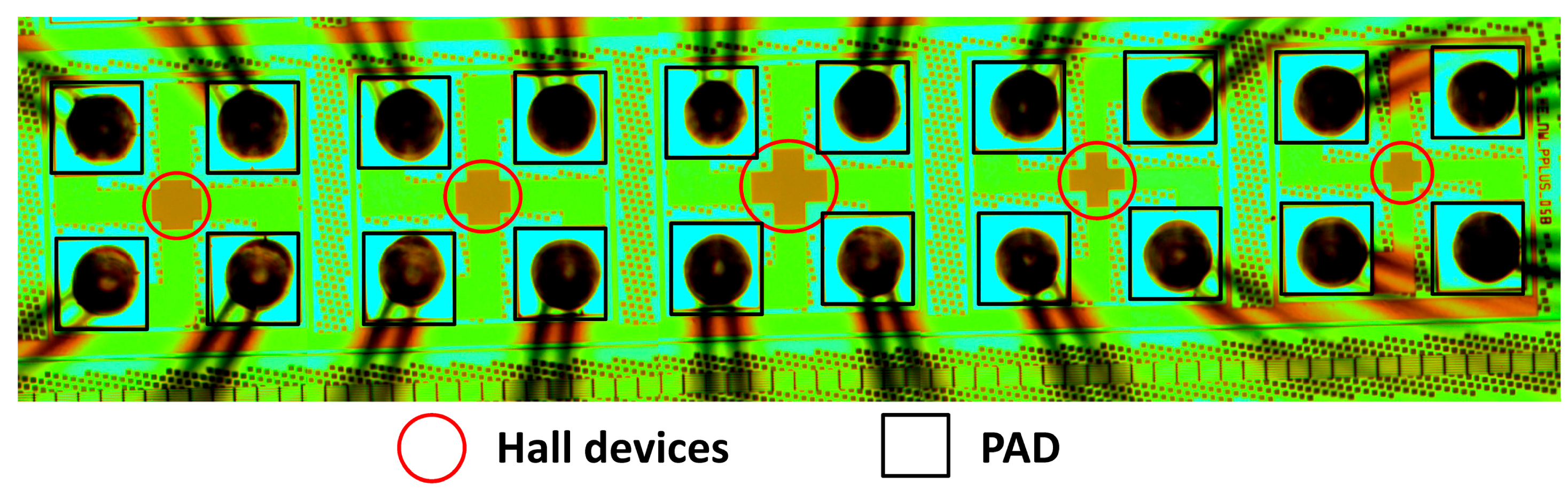

The whole test system for Hall voltage is shown in Figure 3e. We use MATLAB to control other measurement components. The Keithley 6220 shown in Figure 3a, a DC precision current source, supplies a stable current to a Hall chip, which is shown in Figure 4, and the microphotograph of the Hall chip is shown in Figure 5. As an electromagnet power-supplying equipment, the Eastchanging 50110 in Figure 3d is used to generate a uniform magnetic field at the center of the electromagnet shown in Figure 3c. According to the principle of the Hall effect, the Hall voltage appears when the biased Hall chip is placed in the magnetic field. The Nanovoltmeter Keithley 2182A in Figure 3b can measure the values of the Hall voltage and send this information to a PC. All of the equipment runs at room temperature (∼30 °C). The biasing current is set at 0.1 mA. The value of the magnetic field varies from −1 T (tesla) to 1 T in 50 steps. Figure 6 illustrates three groups of the original test data. In order to avoid the influence from the residual magnetic field on the offset voltage, the Hall chips are taken away from the center of the electromagnet. The Keithley 6220 and Keithley 2182A are also used as the DC precision current source to supply a stable current for Hall cells and the nanovoltmeter to measure the offset voltage. Currents of 0.02 mA, 0.04 mA, 0.06 mA, 0.08 mA and 0.1 mA are applied in sequence to bias the Hall cells, and the corresponding offset voltages are measured.

3. Results and Discussions

3.1. Current-Related Sensitivity

When a Hall device is biased with a current I and placed in an orthogonal magnetic field B, the Hall voltage VH appears between two measurement contacts. The Hall voltage VH is defined as:

Generally, as an important parameter for current-related sensitivity, the geometrical correction factor G depends on not only the shape, but also the size of the Hall plate. For a cross-like Hall plate, the L/W (length/width) ratio works as the major influence on the geometrical correction factor of the Hall plate. The cross-like Hall plates with a high L/W ratio have been analyzed, and the geometrical correction factor G is expressed as follows [16]:

If L/W ≥ 3.63, G of the above equation has an accuracy better than 0.5%; while the sizes of our Hall plates are not in this range. The correspondence among length (L), width (W), L/W, the structures and the current-related sensitivity is presented in Table 1. The current-related sensitivity with the same L is increased with the decreasing of W. In other words, the increase of the L/W ratio is beneficial to the current-related sensitivity for the Hall plate with the same L. However, if L and W are proportionally reduced, the value of current-related sensitivity also becomes smaller. Therefore, the current-related sensitivity not only depends on the L/W ratio, but also has a strong correlation with the value of the length and width. The larger length, width and L/W ratio lead to the improvement of the current-related sensitivity of the Hall plate.

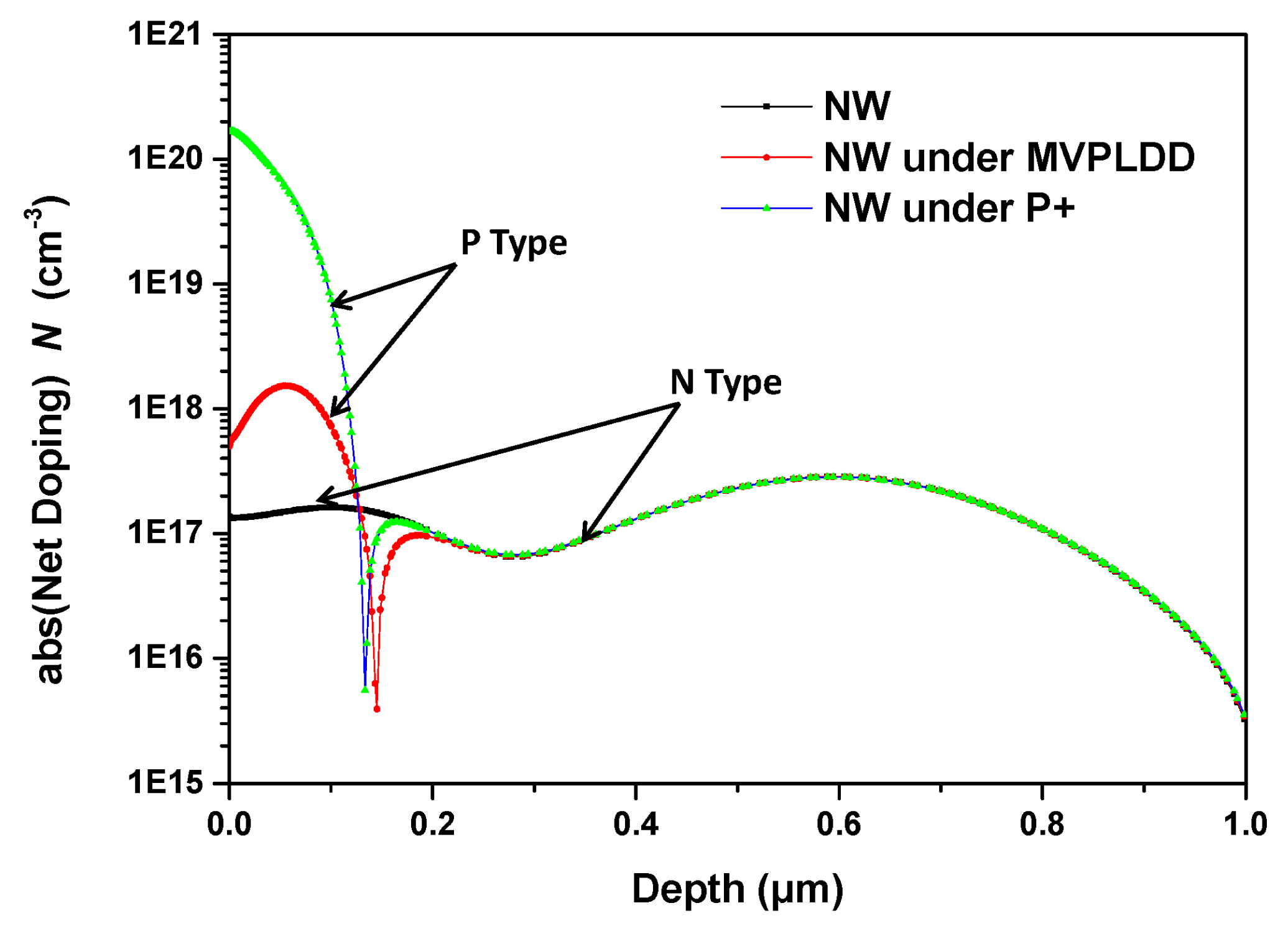

On the other hand, both the doping concentration and the effective thickness of the Hall device's active region have a strong influence on the current-related sensitivity. The doping profiles of three structures are shown in Figure 7. The majority of the three curves in the N-type region coincide perfectly. Therefore, the depth of the N-type region can be used to estimate the current-related sensitivity. S2 shows the highest sensitivity among the three structures due to the smallest depth of the active region. Meanwhile, the areal concentration nteff can be used to predicate the current-related sensitivity. The areal concentration is obtained by integrating the carrier concentration along the depth [23]:

3.2. Offset

It is well know that the tested voltage VT contains two parts, the Hall voltage VH and the offset voltage Voff. The tested voltage can be expressed by:

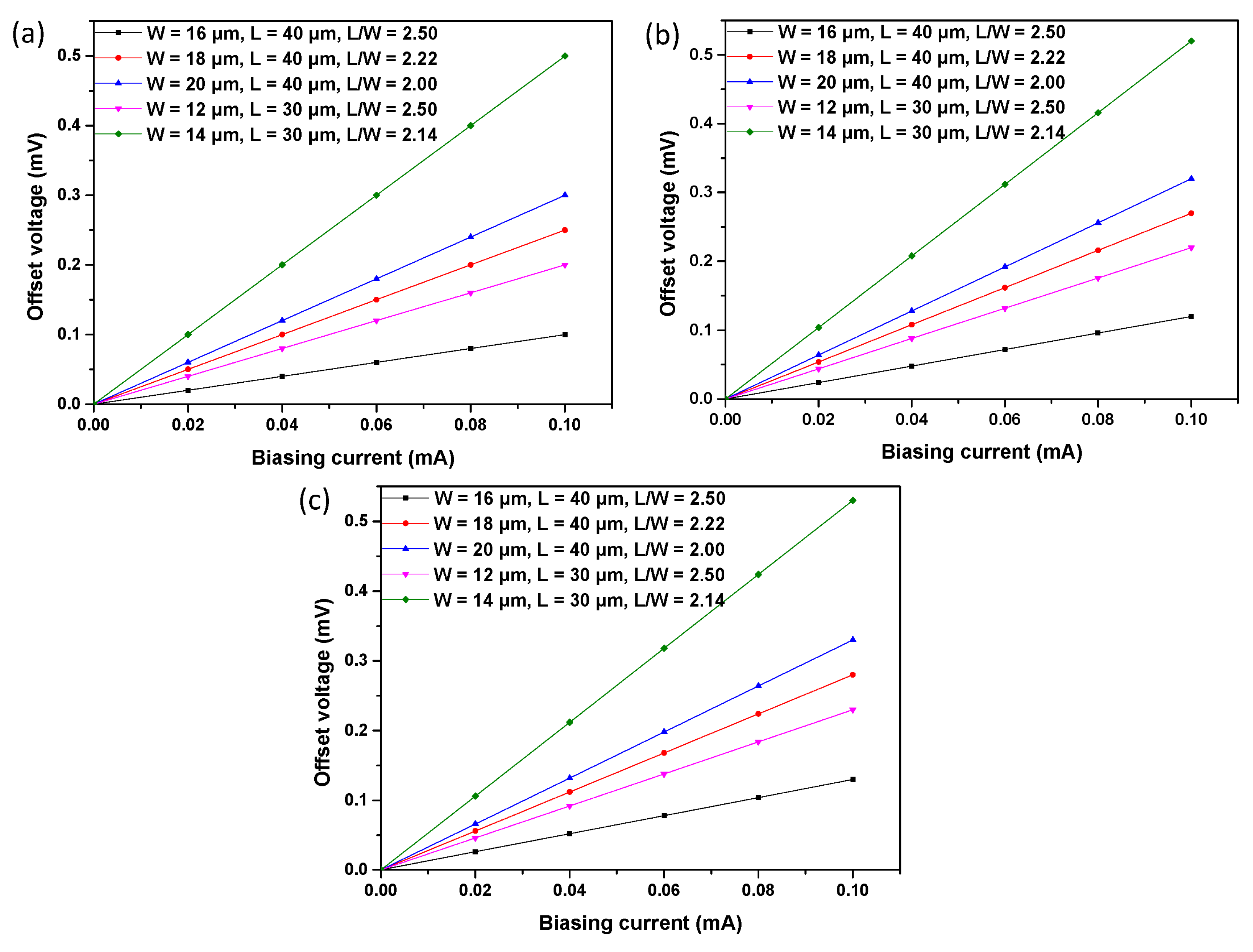

Figure 8 displays the measured offset voltage at room temperature with respect to the biasing current of the three proposed structures. The offset voltage Voffset is almost proportional to the biasing current Ib. Therefore, we introduce a parameter Roffset, which is defined as the following equation to express the value of the offset:

The values of Roffset of the three proposed structures are presented in Table 2. For S1, the Hall plate with a W of 16 μm and an L of 40 μm has the smallest Roffset of 0.05 Ω. S2 with a W of 16 μm and an L of 40 μm shows the best performance in the aspect of offset. However, S3 with a W of 18 μm and an L of 40 μm performs best with the smallest offset. It is well known that the offset is influenced by several factors, while L and W are not the most important among them.

When the Roffset is compared among the three structures, S1 is the best and S3 is the worst in the aspect of offset. Although the P-type doping region is necessary for the Hall plate to improve the stability, it increases the offset of the Hall plate. Both S2 and S3 have a lager offset than S1, with one more process on the active region of P-type doping. To our knowledge, the mask misalignment is a major cause of the offset [24]. As a result, the mask-misalignment that is inevitably introduced into the additional process increases the offset. On the other hand, the offset voltage is modulated by the PN junction depletion width at the P-layer and N-well, which also induces a more asymmetric contact region as a result of process variation. In addition, the P+ layer has higher doping than the MVPLDD, and the depletion width on the N-well side is larger than that of the MVPLDD side. As a result, the offset becomes worse, because the implants are not perfectly aligned and the dopant variation induces more asymmetry. Therefore, in order to have better stability and a lower offset voltage, the N-well under MVPLDD is preferred for the active region of the Hall plate.

3.3. Simulations by Silvaco TCAD

To further assess the Hall effect sensor performance of the current-related sensitivity and offset, three different structures of Hall effect devices are modeled by Silvaco TCAD. The simulation tool helps in modeling the specific structures, to obtain the sensitivity and offset of the Hall plate. The simulation results provide useful information to verify the analysis of the experimental results. The three-dimensional representations of the three simulated structures are illustrated in Figure 9.

For the analysis of current-related sensitivity, all of the structures were simulated using the biasing currents ramped from 0 to 1 mA, with a magnetic field of 1 T. Figure 10 shows the Hall voltage versus biasing current. Meanwhile, in order to simulate the offset, the asymmetry is introduced in the simulated structures by modify the size of the contact. Figure 11 illustrates the offset voltage with respect to the biasing current. Because of the packaging stress, heterogeneous doping concentration and technology process uncertainty, the simulation results and experiment results are not identical. However, the simulation results show the same tendency as the experiment results to demonstrate the correctness of the analysis of the experiment results.

3.4. Eight-Resistor Model with Offset

In order to use the spinning current method to eliminate the offset in the signal conditioning circuit, a circuit model with offset is required in the design of the signal conditioning circuit [25–27]. A recent circuit model with eight non-linear resistors in Figure 12a can be used accurately and suitably for our proposed Hall plate [22]. This model covers the voltage-dependent non-linear effects, geometrical effects, temperature effects and packaging stress influences. In addition, it is relatively simple by only including a small number of physical and technological parameters. R1 and R2 are obtained by the symmetry of the Hall plate and the van der Pauw method of measuring the sheet resistance Rs. R1 and R2 can be expressed as:

However, this model does not take the offset into account. We modified this model by taking the offset into account.

Because the relationship between offset voltage and biasing current is approximately linear, the offset is modeled by an offset resistor ΔR, as shown in Figure 12b. The right and left are used as biasing ports, and the top and bottom are defined for measurement. Without the offset resistor ΔR, when the circuit is biased by a current, the voltage difference between the top and bottom is zero. The offset resistor leads to the asymmetry of the Hall plate, which actually exists in the practical situation. Therefore, even though the model is without the influence of the magnetic field, an offset voltage still appears between the top and bottom due to the offset resistor, when the circuit is biased by a current. ΔR that we defined can be used to model the offset caused by all of the influence factors. By Kirchhoff's circuit law, ΔR can be calculated by:

The modified model has been written in the behavioral Verilog-A language and tested in a Cadence Spectre simulator. The modified eight-resistor model shows the same accuracy in sensitivity and temperature behavior as the model in [22], while the correctness and accuracy in the offset aspect are demonstrated by the corresponding experimental results of the Hall plate. A very good agreement with the model's simulation results is achieved and shown in Figure 13. Consequently, in SPICE-like (SPICE, simulation program with integrated circuit emphasis) EDA (electronic design automation) tools, the modified model can be used to do circuit simulation in the design of the signal conditioning circuit.

4. Conclusions

In order to analyze the current-related sensitivity and offset of the cross-like Hall plates with different covering layers, we designed and fabricated three structures of Hall plate in 0.18-μm BCDliteTM technology provided by GLOBALFOUNDRIES. Each structure is implemented in a Hall chip with multiple Hall cells to study the impact of the L, W and L/W ratio on the performance of the Hall plate. Moreover, we demonstrate that the Hall plate with the MVPLDD layer above the active region is the best structure in both the current-related sensitivity and offset. Besides, we greatly improved the accuracy of the eight-resistor circuit model for the Hall plate by taking the offset into account.

Acknowledgments

This work was supported by National Nature Science Foundation of China under Grant Nos. 61176024, 61006018, 61370040, 61376075; the Research Fund for the Doctoral Program of Higher Education of China under Grant No. 20120091110029; The IUR (Industry-University-Research) Cooperative Innovation Foundation-Prospective Research Project of Jiangsu Province under Grant No. BY2013072-05; a project funded by the Priority Academic Program Development of Jiangsu Higher Education Institutions (PAPD).

Author Contributions

F. Lyu wrote and revised the manuscript, and also carried out the simulation in Silvaco TCAD and Cadence. E. -H. Toh, X. Liu and Y. Ding analyzed the measured data in aspect of technology process. Z. Zhang, Y. Pan and C. Li carried out the experiments. L. Li and J. Sha gave a keen insight in this manuscript. H. Pan arranged all the work in this project.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Ramsden, E. Hall-Effect Sensors: Theory and Application, 2nd ed.; Newnes: Burlington, MA, USA, 2006. [Google Scholar]

- Popovic, R.S. Hall Effect Devices: Magnetic Sensors and Characterisation of Semiconductors, 1st ed.; Taylor & Francis: New York, NY, USA, 1991. [Google Scholar]

- Boero, G.; Demierre, M.; Besse, P.A.; Popovic, R.S. Micro-Hall devices: Performance, technologies and applications. Sens. Actuator A Phys. 2003, 106, 314–320. [Google Scholar]

- Kammerer, J.B.; Hebrard, L.; Frick, V.; Poure, P.; Braun, F. Horizontal hall effect sensor with high maximum absolute sensitivity. IEEE Sens. J. 2003, 3, 700–707. [Google Scholar]

- Manic, D.; Igic, P.M.; Mawby, P.A.; Haddab, Y.; Popovic, R.S. Mechanical stress related instabilities in silicon under metal coverage. IEEE Trans. Electron Devices 2000, 47, 2429–2437. [Google Scholar]

- Kerlain, A.; Mosser, V. Dynamic low-frequency noise cancellation in quantum well Hall sensors (QWHS). Sens. Actuators A Phys. 2008, 142, 528–532. [Google Scholar]

- Steiner, R.; Maier, C.; Haberli, A.; Steiner, F.P.; Baltes, H. Offset reduction in Hall devices by continuous spinning current method. Sens. Actuators A Phys. 1998, 66, 167–172. [Google Scholar]

- Muller-Schwanneke, C.; Jost, F.; Marx, K.; Lindenkreuz, S.; von Klitzing, K. Offset reduction in silicon Hall sensors. Sens. Actuators A Phys. 2000, 81, 18–22. [Google Scholar]

- Bellekom, S.; Sarro, P.M. Offset reduction of Hall plates in three different crystal planes. Sens. Actuators A Phys. 1998, 66, 23–28. [Google Scholar]

- Paun, M.A.; Sallese, J.M.; Kayal, M. Comparative Study on the Performance of Five Different Hall Effect Devices. Sensors 2013, 13, 2093–2112. [Google Scholar]

- Paun, M.-A.; Sallese, J.-M.; Kayal, M. Offset and drift analysis of the Hall Effect sensors. The geometrical parameters influence. Dig. J. Nanomater. Biostruct. 2012, 7, 883–891. [Google Scholar]

- Paun, M.-A.; Sallese, J.-M.; Kayal, M. Geometrical parameters influence on the Hall effect sensors offset and drift. Proceedings of 2011 7th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Trento, Italy, 3–7 July 2011; pp. 145–148.

- Paun, M.-A.; Sallese, J.-M.; Kayal, M. Hall effect sensors design, integration and behavior analysis. J. Sens. Actuator Netw. 2013, 2, 85–97. [Google Scholar]

- Paun, M.-A.; Sallese, J.-M.; Kayal, M. A specific parameters analysis of CMOS Hall effect sensors with various geometries. Proceedings of 19th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Warsaw, Poland, 24–26 May 2012; pp. 335–339.

- Paun, M.-A.; Sallese, J.-M.; Kayal, M. Hall effect sensors performance investigation using three-dimensional simulations. Proceedings of the 18th International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES), Gliwice, Poland, 16–18 June 2011; pp. 450–455.

- Versnel, W. Analysis of Symmetrical Hall Plates with Finite Contacts. J. Appl. Phys. 1981, 52, 4659–4666. [Google Scholar]

- Versnel, W. The Geometrical Correction Factor for a Rectangular Hall Plate. J. Appl. Phys. 1982, 53, 4980–4986. [Google Scholar]

- Popovic, R.S. Hall Effect Devices; CRC Press: Boca Raton, FL, USA, 2010. [Google Scholar]

- Schweda, J.; Riedling, K. A nonlinear simulation model of integrated Hall devices in CMOS silicon technology. Proceedings of 2002 IEEE International Workshop on Behavioral Modeling and Simulation, Santa Rosa, CA, USA, 6–8 October 2002; pp. 14–20.

- Dimitropoulos, P.D.; Drljaca, P.M.; Popovic, R.S.; Chatzinikolaou, P. Horizontal Hall devices: A lumped-circuit model for EDA simulators. Sens. Actuators A Phys. 2008, 145, 161–175. [Google Scholar]

- Madec, M.; Kammerer, J.; Hebrard, L. An improved compact model of cross-shaped horizontal CMOS-integrated Hall-effect sensor. Proceedings of 2010 8th IEEE International NEWCAS Conference (NEWCAS), Montreal, QC, Canada, 20–23 June 2010; pp. 397–400.

- Xu, Y.; Pan, H.B. An Improved Equivalent Simulation Model for CMOS Integrated Hall Plates. Sensors 2011, 11, 6284–6296. [Google Scholar]

- Sun, K.; Wang, M. 1/f noise measurement and its doping dependencies of Si Hall sensors. Proceedings of 19th IEEE International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA 2012), Singapore, Singapore, 2–6 July 2012; pp. 1–4.

- Randjelovic, Z. Low-power high sensitivity integrated Hall magnetic sensor microsystems. Ph.D. Thesis, EPFL, Lausanne, Switzerland, 2000. [Google Scholar]

- Frick, V.; Pascal, J.; Blondé, J.-P.; Hébrard, L. Chopper stabilized CMOS integrated front-end for magnetic field measurement. Proceedings of 32nd Annual Conference on IEEE Industrial Electronics (IECON 2006), Paris, France, 6–10 November 2006; pp. 3090–3094.

- Bilotti, A.; Monreal, G.; Vig, R. Monolithic magnetic Hall sensor using dynamic quadrature offset cancellation. IEEE J. Solid-State Circuits 1997, 32, 829–836. [Google Scholar]

- Xu, Y.; Pan, H.-B.; He, S.-Z.; Li, L. A Highly Sensitive CMOS Digital Hall Sensor for Low Magnetic Field Applications. Sensors 2012, 12, 2162–2174. [Google Scholar]

| Sensitivity of S1 (V/(A·T)) | Sensitivity of S2 (V/(A·T)) | Sensitivity of S3 (V/(A·T)) | |

|---|---|---|---|

| W = 16 μm, L = 40 μm, L/W = 2.50 | 37.8 | 52.7 | 48.1 |

| W = 18μm, L = 40 μm, L/W = 2.22 | 34.7 | 47.6 | 43.8 |

| W = 20 μm, L = 40 μm, L/W = 2.00 | 30.6 | 42.0 | 38.9 |

| W = 12μm, L = 30 μm, L/W = 2.50 | 36.6 | 50.5 | 46.4 |

| W = 14 μm, L = 30 μm, L/W = 2.14 | 31.3 | 43.1 | 39.7 |

| Roffset of S1(Ω) | Roffset of S2(Ω) | Roffset of S3(Ω) | |

|---|---|---|---|

| W = 16 μm, L = 40 μm, L/W = 2.50 | 0.050 | 0.157 | 0.604 |

| W = 18 μm, L = 40 μm, L/W = 2.22 | 0.180 | 0.330 | 0.335 |

| W = 20 μm, L = 40 μm, L/W = 2.00 | 0.070 | 0.257 | 0.692 |

| W = 12 μm, L = 30 μm, L/W = 2.50 | 0.285 | 0.300 | 0.420 |

| W = 14 μm, L = 30 μm, L/W = 2.14 | 0.120 | 0.238 | 0.750 |

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lyu, F.; Zhang, Z.; Toh, E.-H.; Liu, X.; Ding, Y.; Pan, Y.; Li, C.; Li, L.; Sha, J.; Pan, H. Performance Comparison of Cross-Like Hall Plates with Different Covering Layers. Sensors 2015, 15, 672-686. https://doi.org/10.3390/s150100672

Lyu F, Zhang Z, Toh E-H, Liu X, Ding Y, Pan Y, Li C, Li L, Sha J, Pan H. Performance Comparison of Cross-Like Hall Plates with Different Covering Layers. Sensors. 2015; 15(1):672-686. https://doi.org/10.3390/s150100672

Chicago/Turabian StyleLyu, Fei, Zhenyan Zhang, Eng-Huat Toh, Xinfu Liu, Yinjie Ding, Yifan Pan, Chengjie Li, Li Li, Jin Sha, and Hongbing Pan. 2015. "Performance Comparison of Cross-Like Hall Plates with Different Covering Layers" Sensors 15, no. 1: 672-686. https://doi.org/10.3390/s150100672

APA StyleLyu, F., Zhang, Z., Toh, E.-H., Liu, X., Ding, Y., Pan, Y., Li, C., Li, L., Sha, J., & Pan, H. (2015). Performance Comparison of Cross-Like Hall Plates with Different Covering Layers. Sensors, 15(1), 672-686. https://doi.org/10.3390/s150100672