Field-Programmable Gate Array-Based Chaos Oscillator Implementation for Analog–Discrete and Discrete–Analog Chaotic Synchronization Applications

Abstract

1. Introduction

- We implement discrete chaos oscillator models in fixed-point arithmetic for FPGA applications;

- We experimentally demonstrate the possibility of chaotic synchronization of the chaos oscillator circuit and discrete model implemented on an FPGA.

2. Chaos Oscillator FPGA Implementation

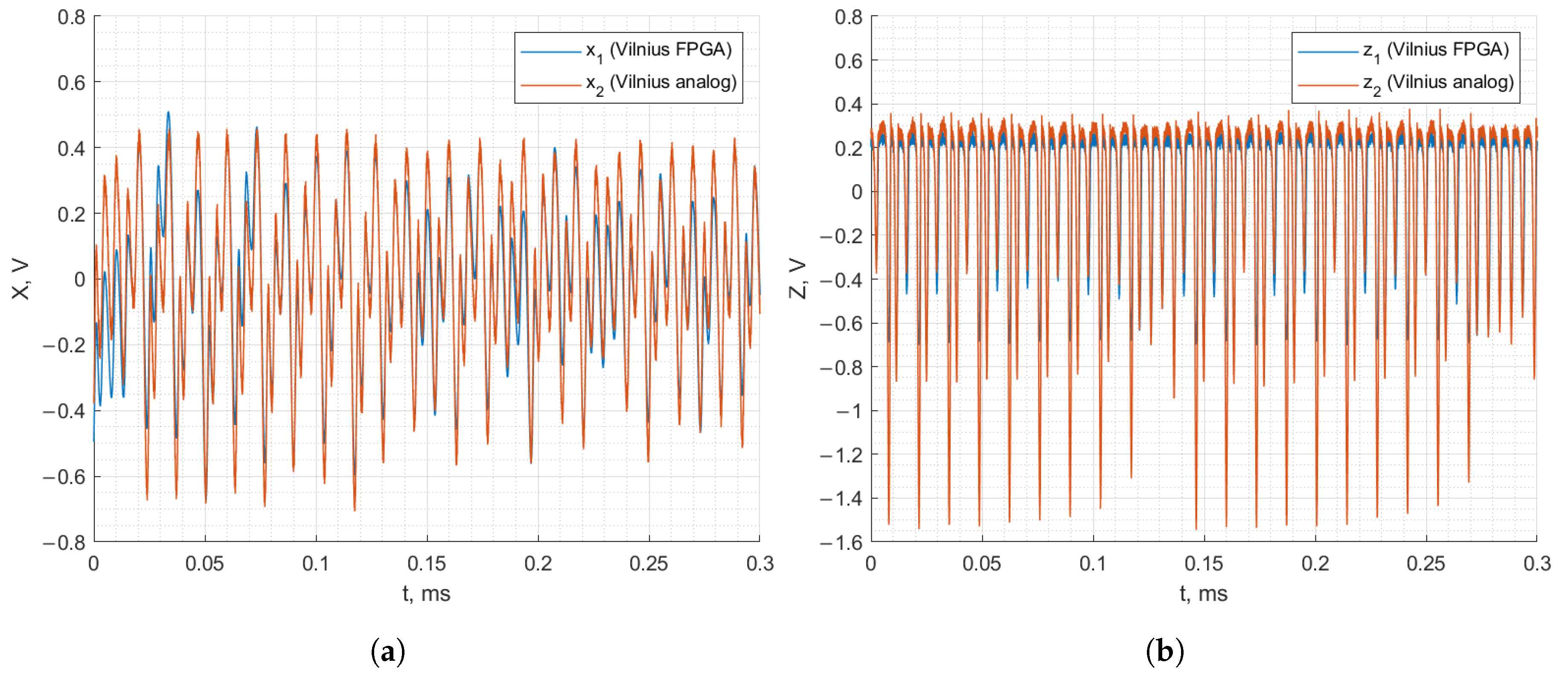

2.1. Vilnius Chaos Oscillator

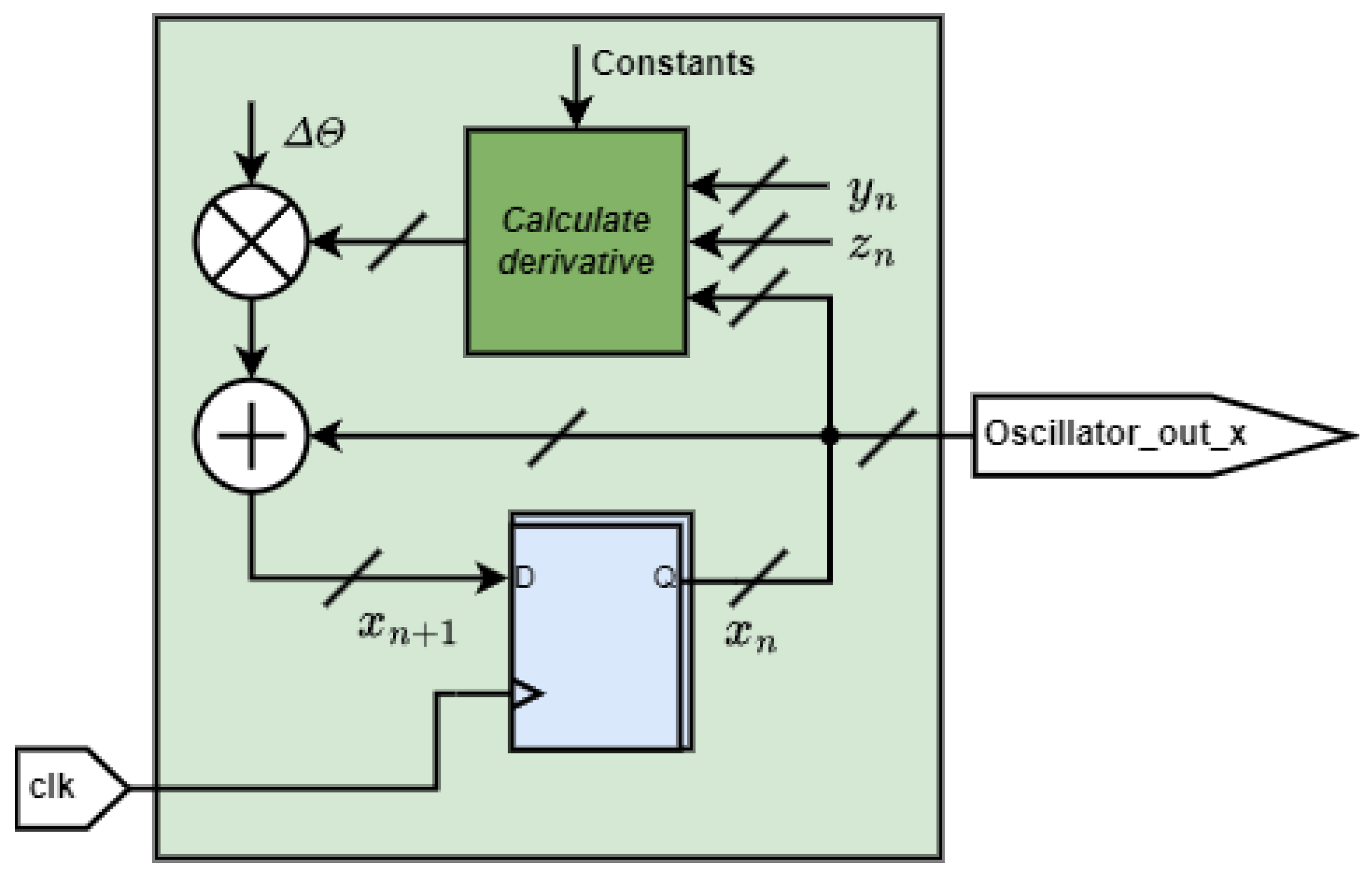

2.2. Vilnius Chaos Oscillator FPGA Implementation

2.3. RC Chaos Oscillator

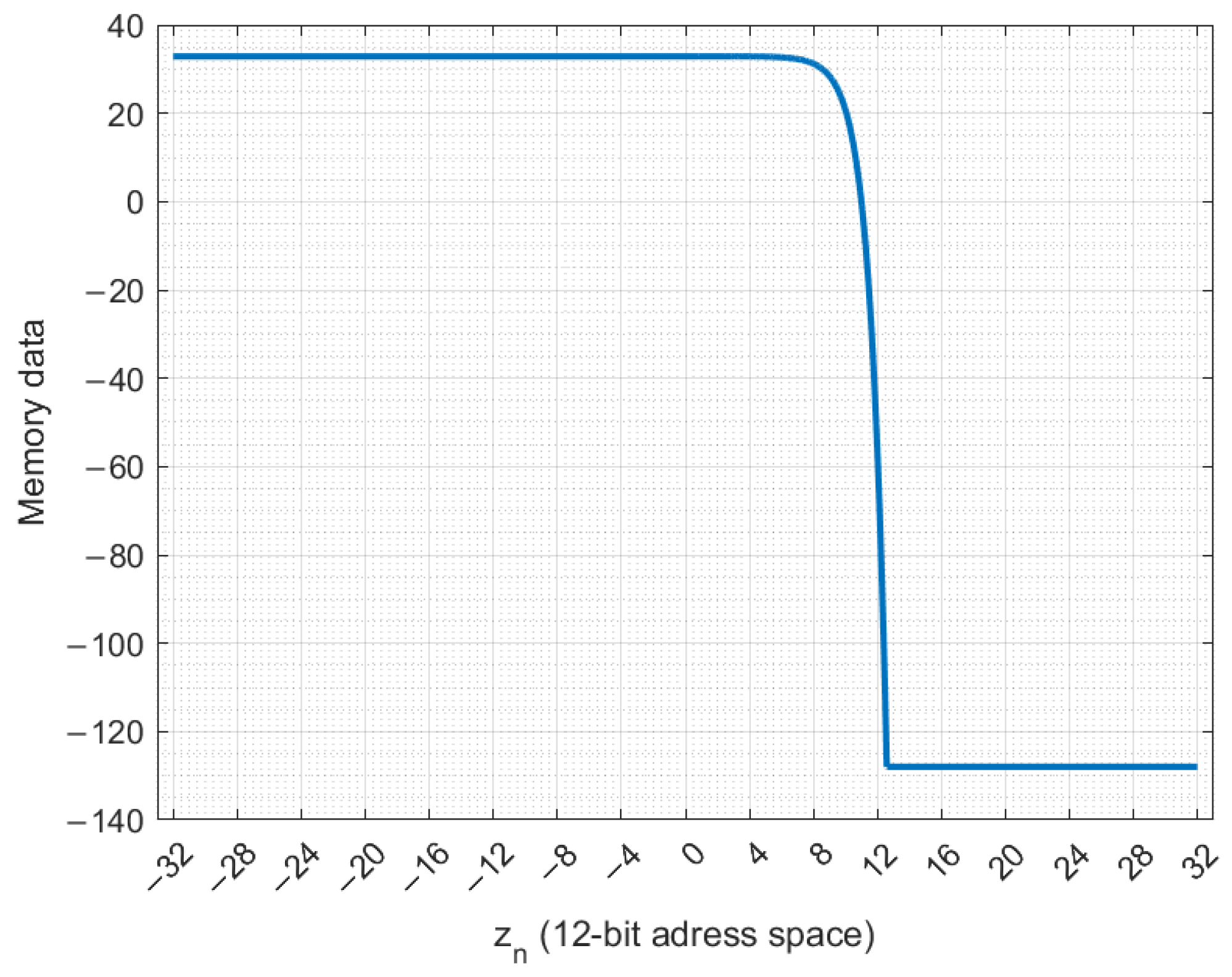

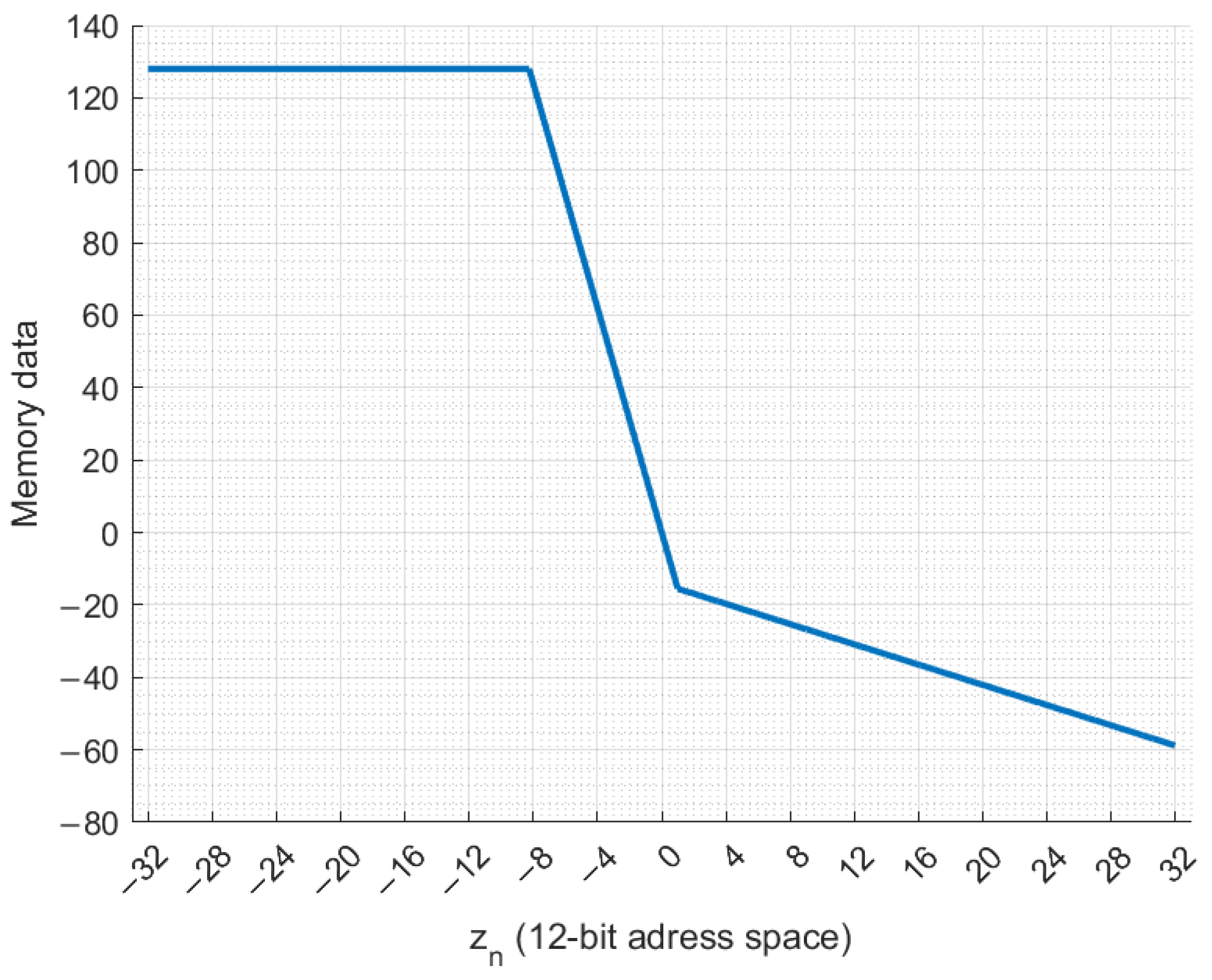

2.4. RC Chaos Oscillator FPGA Implementation

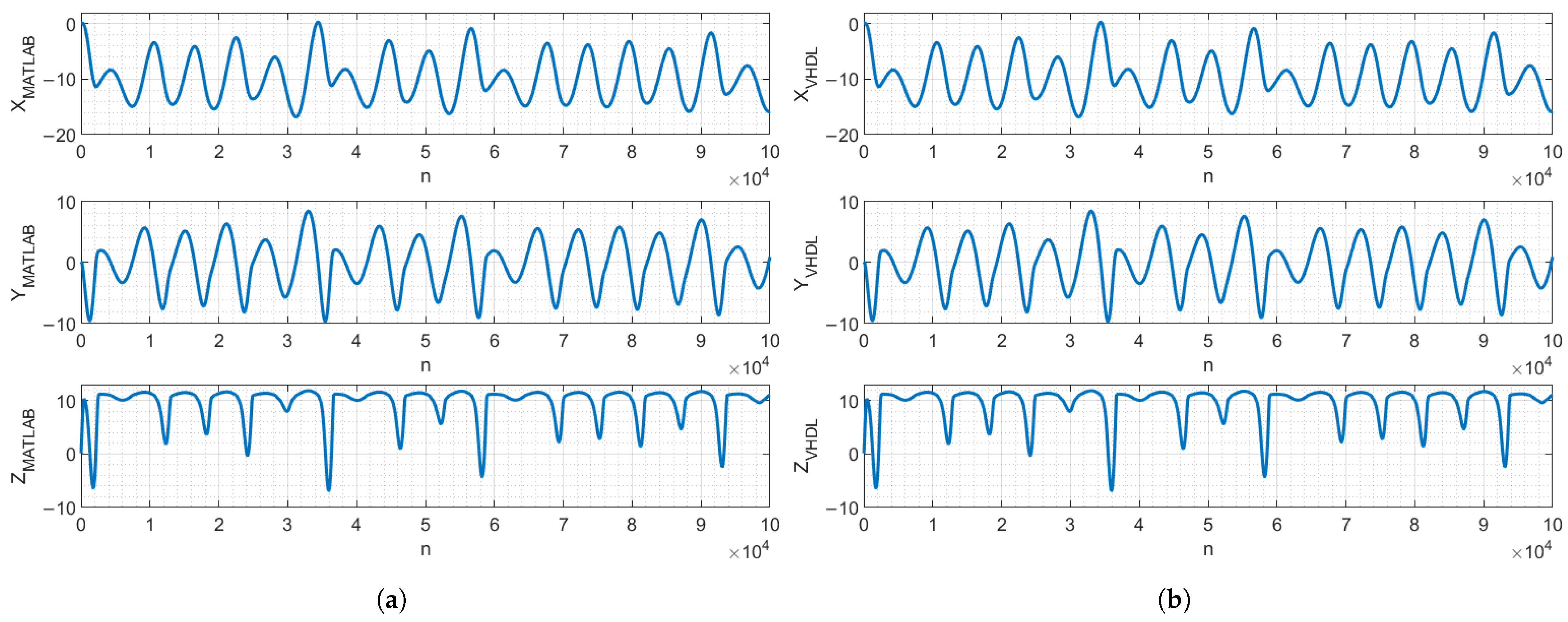

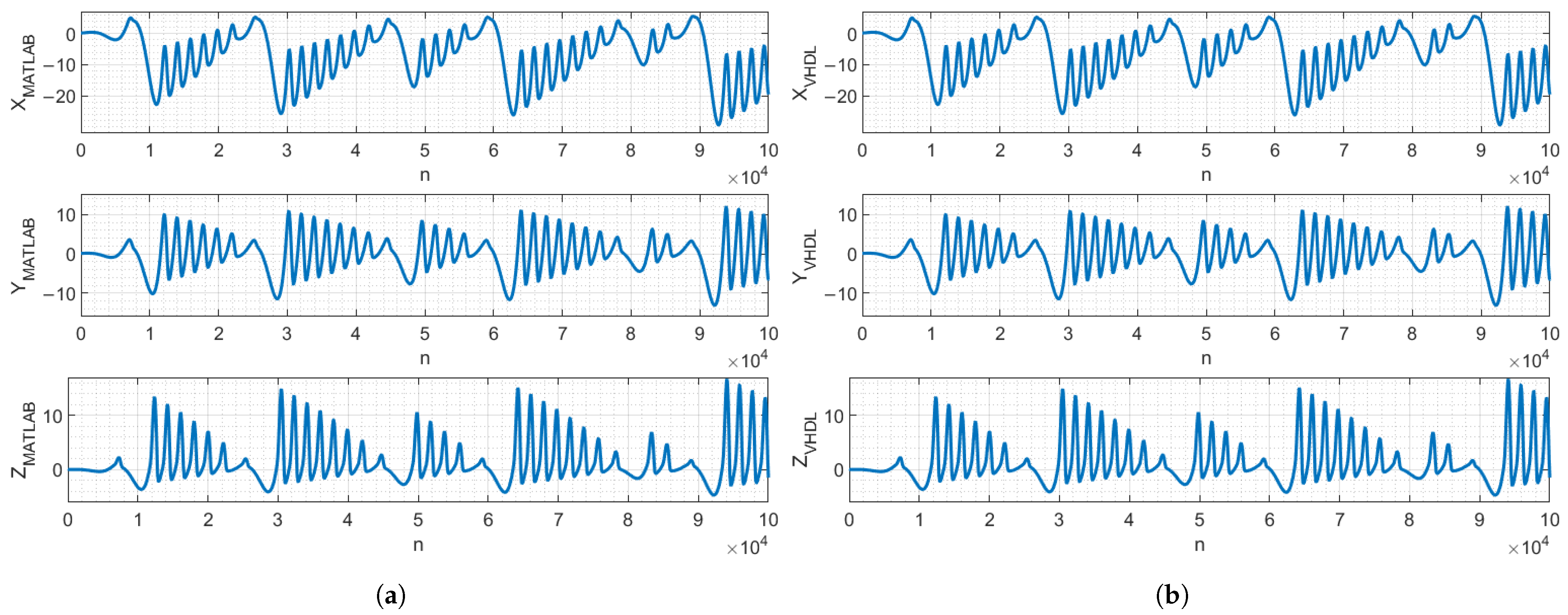

2.5. MATLAB Model and VHDL Design Comparison

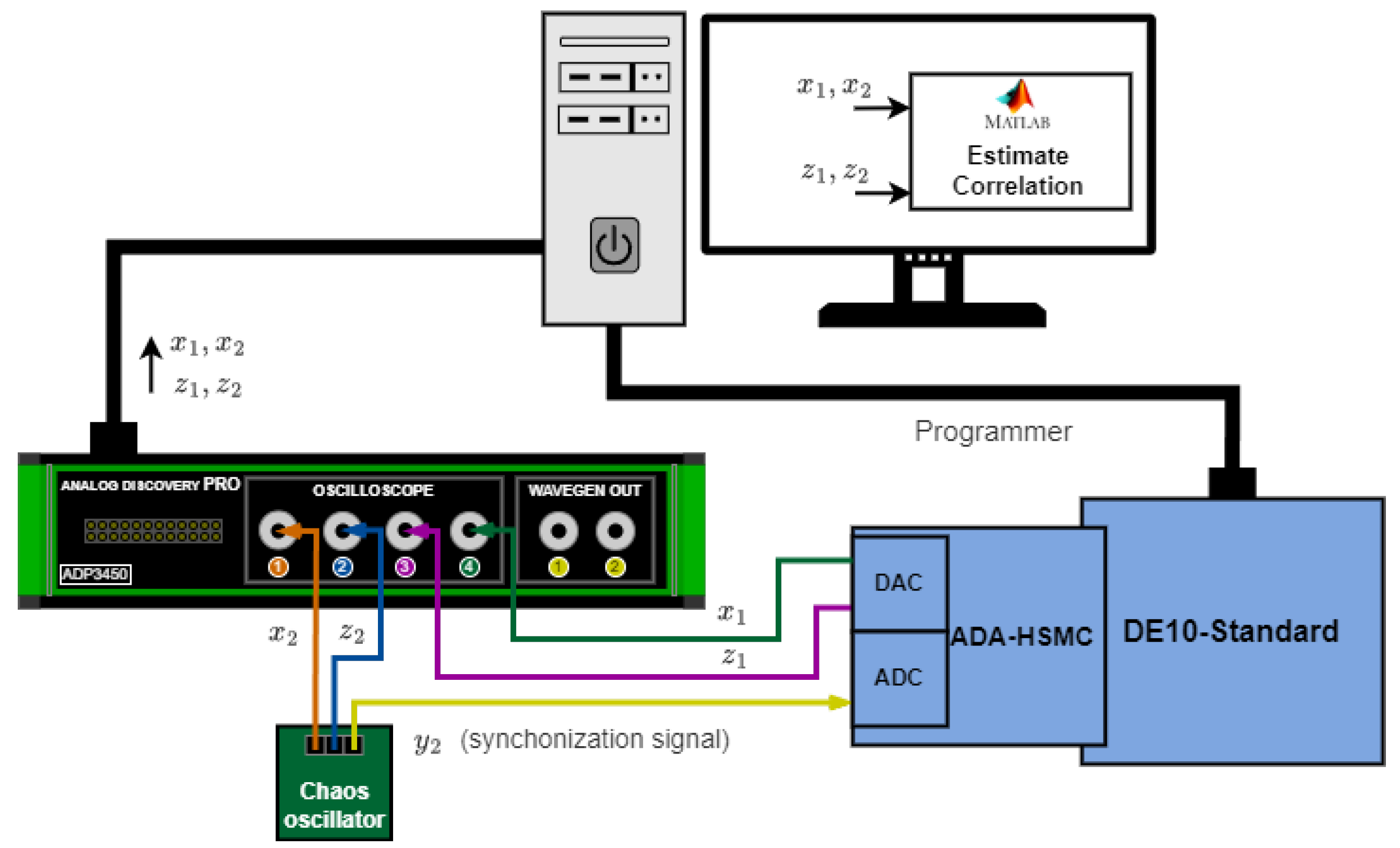

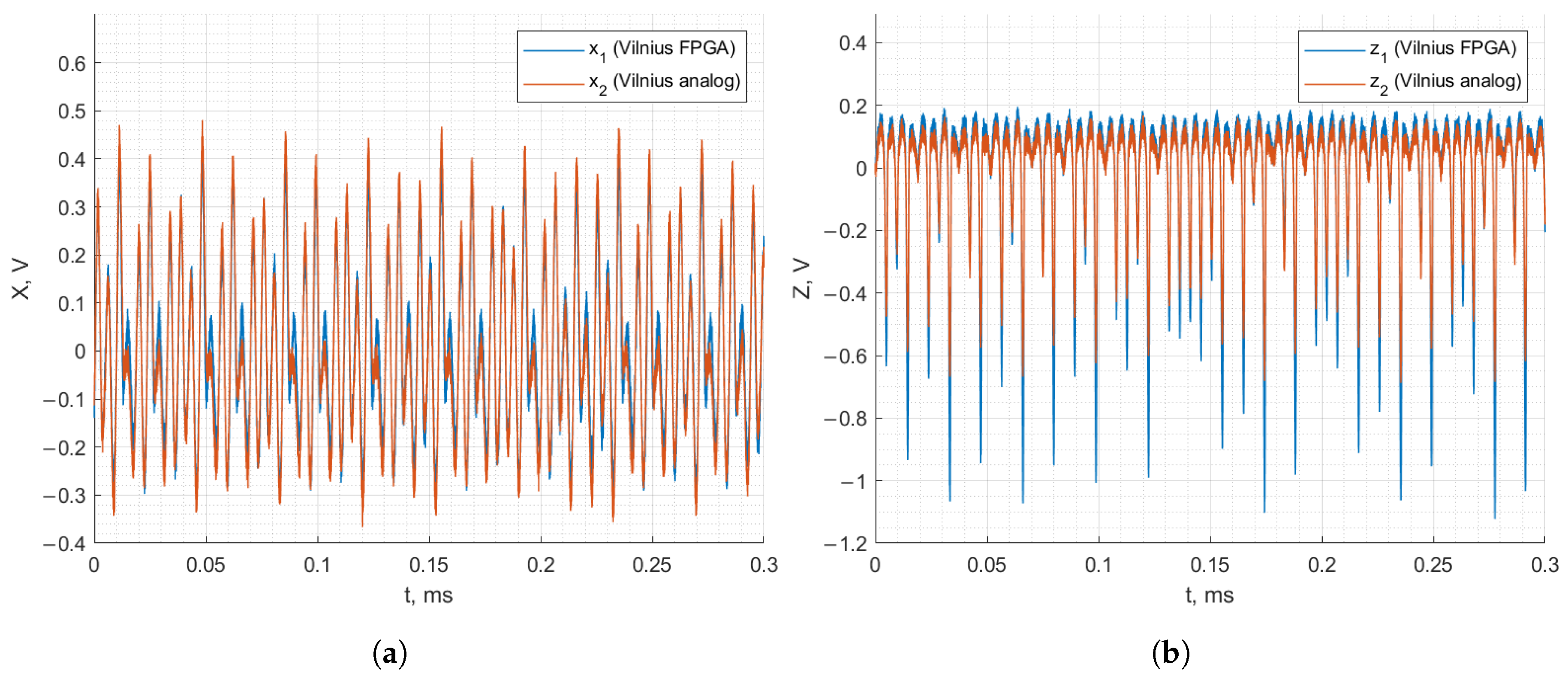

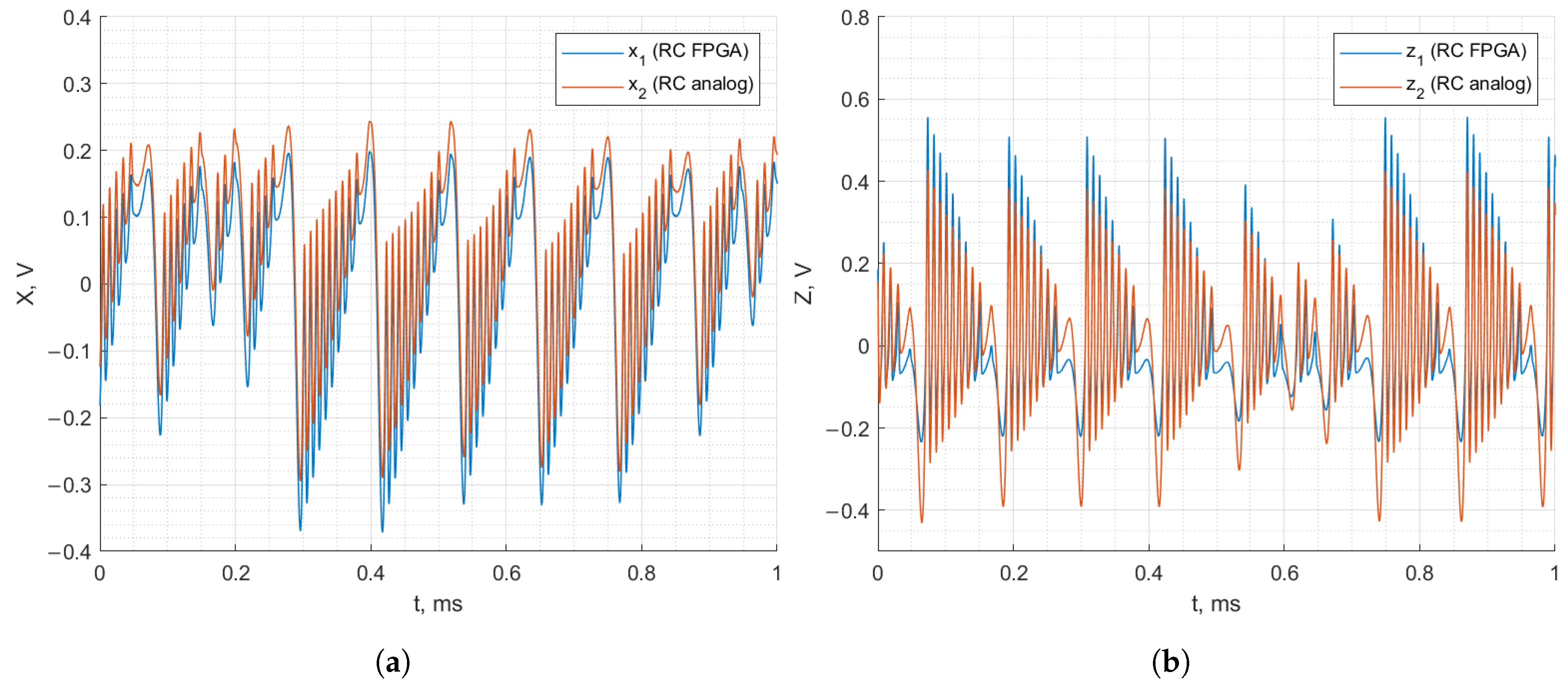

3. Experimental Verification of FPGA-Based Analog–Discrete and Discrete–Analog Synchronization

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| ALM | Adaptive logic module |

| ADC | Analog-to-digital converter |

| DAC | Digital-to-analog converter |

| DSP | Digital signal processing |

| FPGA | Field-programmable gate array |

| HSMC | High-Speed Mezzanine Card |

| IoT | Internet of Things |

| PCB | Printed circuit board |

| ROM | Read-only memory |

| VHDL | VHSIC Hardware Description Language |

| VHSIC | Very High-Speed Integrated Circuit |

| WSN | Wireless Sensor Network |

References

- Ericsson Mobility Report November 2024; Technical Report; Ericsson: Stockholm, Sweden, 2024.

- El Hanine, M.; El-Yahyaoui, A.; Es-Sadaoui, R. Three Layer IoT Architecture: Attacks and Security Mechanisms. In Proceedings of the 2024 11th International Conference on Future Internet of Things and Cloud (FiCloud), Vienna, Austria, 19–21 August 2024; pp. 32–38. [Google Scholar] [CrossRef]

- Frustaci, M.; Pace, P.; Aloi, G.; Fortino, G. Evaluating Critical Security Issues of the IoT World: Present and Future Challenges. IEEE Internet Things J. 2018, 5, 2483–2495. [Google Scholar] [CrossRef]

- Neshenko, N.; Bou-Harb, E.; Crichigno, J.; Kaddoum, G.; Ghani, N. Demystifying IoT Security: An Exhaustive Survey on IoT Vulnerabilities and a First Empirical Look on Internet-Scale IoT Exploitations. IEEE Commun. Surv. Tutor. 2019, 21, 2702–2733. [Google Scholar] [CrossRef]

- Chua, L.; Wu, C.; Huang, A.; Zhong, G.-Q. A universal circuit for studying and generating chaos. I. Routes to chaos. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1993, 40, 732–744. [Google Scholar] [CrossRef]

- Kennedy, M. Chaos in the Colpitts oscillator. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1994, 41, 771–774. [Google Scholar] [CrossRef]

- Tamaševičius, A.; Mykolaitis, G.; Pyragas, V.; Pyragas, K. A simple chaotic oscillator for educational purposes. Eur. J. Phys. 2004, 26, 61. [Google Scholar] [CrossRef]

- Namajunas, A.; Tamasevicius, A. Simple RC chaotic oscillator. Electron. Lett. 1996, 32, 945–946. [Google Scholar] [CrossRef]

- Chen, X.; Du, H.; Luo, J.; Chen, Y. Memristor-based chaotic synchronization control and circuit experiments via single-input controller. In Proceedings of the 2024 36th Chinese Control and Decision Conference (CCDC), Xi’an, China, 25–27 May 2024; pp. 5431–5436. [Google Scholar] [CrossRef]

- Escudero, M.; Spiga, S.; Marco, M.D.; Forti, M.; Innocenti, G.; Tesi, A.; Corinto, F.; Brivio, S. Chua’s Circuit with Tunable Nonlinearity Based on a Nonvolatile Memristor: Design and Realization. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 62–72. [Google Scholar] [CrossRef]

- Chen, W.L.; Zheng, L.H.; Song, X.X. Design of two-stage chaotic Colpitts oscillator. In Proceedings of the 2016 IEEE International Conference on Microwave and Millimeter Wave Technology (ICMMT), Beijing, China, 5–8 June 2016; pp. 1029–1031. [Google Scholar] [CrossRef]

- Semenov, A.O.; Savytskyi, A.Y.; Bisikalo, O.V.; Kulakov, P.I. Mathematical modeling of the two-stage chaotic colpitis oscillator. In Proceedings of the 2018 14th International Conference on Advanced Trends in Radioelecrtronics, Telecommunications and Computer Engineering (TCSET), Lviv-Slavske, Ukraine, 20–24 February 2018; pp. 835–839. [Google Scholar] [CrossRef]

- Petrzela, J.; Kaller, O.; Vavra, J. The Reinartz Oscillator: Analysis Beyond Regular Behavior of the Circuit. IEEE Access 2024, 12, 77891–77902. [Google Scholar] [CrossRef]

- Sadia, M.; Paul, P.S.; Hossain, M.R.; Muldrey, B.; Hasan, M.S. Robust Chaos with Novel 4-Transistor Maps. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 914–918. [Google Scholar] [CrossRef]

- Jiang, Y.; Li, C.; Zhang, C.; Lei, T.; Jafari, S. Constructing Meminductive Chaotic Oscillator. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 2675–2679. [Google Scholar] [CrossRef]

- Banerjee, T.; Karmakar, B.; Sarkar, B.C. Chaotic electronic oscillator from single amplifier biquad. AEU Int. J. Electron. Commun. 2012, 66, 593–597. [Google Scholar] [CrossRef]

- Wang, L.; Wang, C.; Zhang, H.; Ma, P.; Zhang, S. Estimation-Correction Modeling and Chaos Control of Fractional-Order Memristor Load Buck-Boost Converter. Complex Syst. Model. Simul. 2024, 4, 67–81. [Google Scholar] [CrossRef]

- Benadero, L.; Aroudi, A.E.; Martínez-Salamero, L.; Tse, C.K. Period Doubling Route to Chaos in Open Loop Boost Converters under Constant Power Loading and Discontinuous Conduction Mode Conditions. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Zhang, C.; Zhang, S.; Liang, K.; Chen, Z. Double Image Encryption Algorithm Based on Parallel Compressed Sensing and Chaotic System. IEEE Access 2024, 12, 54745–54757. [Google Scholar] [CrossRef]

- Kumar Thukral, M. SCLLCM: A Robust One Dimesional Chaotic Map for Image Encryption Application. In Proceedings of the 2024 Asia Pacific Conference on Innovation in Technology (APCIT), Mysore, India, 26–27 July 2024; pp. 1–5. [Google Scholar] [CrossRef]

- Atteya, A.M.; Madian, A.H. A hybrid Chaos-AES encryption algorithm and its impelmention based on FPGA. In Proceedings of the 2014 IEEE 12th International New Circuits and Systems Conference (NEWCAS), Trois-Rivieres, QC, Canada, 22–25 June 2014; pp. 217–220. [Google Scholar] [CrossRef]

- Moysis, L.; Kafetzis, I.; Volos, C.; Tutueva, A.V.; Butusov, D. Application of a Hyperbolic Tangent Chaotic Map to Random Bit Generation and Image Encryption. In Proceedings of the 2021 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), St. Petersburg, Moscow, Russia, 26–29 January 2021; pp. 559–565. [Google Scholar] [CrossRef]

- Butusov, D.N.; Karimov, T.I.; Lizunova, I.A.; Soldatkina, A.A.; Popova, E.N. Synchronization of analog and discrete Rössler chaotic systems. In Proceedings of the 2017 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), St. Petersburg and Moscow, Russia, 1–3 February 2017; pp. 265–270. [Google Scholar] [CrossRef]

- Zhang, J.; Qi, L. Detection of Weak Signals Based on the Duffing Chaotic System and FPGA Implementation. In Proceedings of the 2024 5th International Seminar on Artificial Intelligence, Networking and Information Technology (AINIT), Nanjing, China, 29–31 March 2024; pp. 2212–2218. [Google Scholar] [CrossRef]

- Bonny, T.; Al Nassan, W. NeuroChaosCrypt: Revolutionizing Chaotic-Based Cryptosystem with Artificial Neural Networks—A Comparison with Traditional Cryptosystems. IEEE Access 2024, 12, 62030–62046. [Google Scholar] [CrossRef]

- Addabbo, T.; Fort, A.; Moretti, R.; Mugnaini, M.; Takaloo, H.; Vignoli, V. A New Class of Chaotic Sources in Programmable Logic Devices. In Proceedings of the 2020 IEEE International Workshop on Metrology for Industry 4.0 & IoT, Roma, Italy, 3–5 June 2020; pp. 6–10. [Google Scholar] [CrossRef]

- Karataş, O.; Demir, K.; Ergün, S. Chaotic Sampling of Double Scroll Chaos for Digital Random Number Generation. In Proceedings of the 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Shenzhen, China, 11–13 November 2022; pp. 424–427. [Google Scholar] [CrossRef]

- Azzaz, M.S.; Kaibou, R.; Smahi, A. FPGA Implementation using Novel Co-Design Approach of Real-Time Speech Chaos based Crypto-Watermarking Prototype. In Proceedings of the 2023 International Conference on Advances in Electronics, Control and Communication Systems (ICAECCS), Blida, Algeria, 6–7 March 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Hobincu, R.; Datcu, O. FPGA Implementation of a Chaos Based PRNG Targetting Secret Communication. In Proceedings of the 2018 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania, 8–9 November 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Azzaz, M.S.; Tanougast, C.; Adoudi, S.; Bouridane, A.; Dandache, A. An FPGA implementation of a Feed-Back Chaotic Synchronization for secure communications. In Proceedings of the 2010 7th International Symposium on Communication Systems, Networks and Digital Signal Processing, CSNDSP 2010, Newcastle Upon Tyne, UK, 21–23 July 2010; pp. 239–243, ISBN 9781861353696. [Google Scholar] [CrossRef]

- Babu, R.R.; Karthikeyan, R. Adaptive synchronization of novel chaotic system and its FPGA implementation. In Proceedings of the 2015 International Conference on Smart Technologies and Management for Computing, Communication, Controls, Energy and Materials, ICSTM 2015, Avadi, India, 6–8 May 2015; pp. 449–454, ISBN 9781479998555. [Google Scholar] [CrossRef]

- Guillén-Fernández, O.; Meléndez-Cano, A.; Tlelo-Cuautle, E.; Núñez-Pérez, J.C.; de Jesus Rangel-Magdaleno, J. On the synchronization techniques of chaotic oscillators and their FPGA-based implementation for secure image transmission. PLoS ONE 2019, 14, e0209618. [Google Scholar] [CrossRef]

- Kaddoum, G. Wireless Chaos-Based Communication Systems: A Comprehensive Survey. IEEE Access 2016, 4, 2621–2648. [Google Scholar] [CrossRef]

- Kvitko, D.; Babkin, I.; Shirnin, K.; Karimov, T.; Kolev, G.; Rybin, V. Chaos Shift Keying Coherent Communication Based on Different Types of Operational Amplifiers. In Proceedings of the 2023 12th Mediterranean Conference on Embedded Computing (MECO), Budva, Montenegro, 6–10 June 2023; pp. 1–4. [Google Scholar] [CrossRef]

- George, A.E.; Gelóczi, E.; Mexis, N.; Arul, T.; Katzenbeisser, S.; Stavrinides, S.G.; Picos, R.; Anagnostopoulos, N.A. Real-World Secure Communication based on Synchronised Lorenz Chaotic Circuits. In Proceedings of the 2024 13th International Conference on Modern Circuits and Systems Technologies (MOCAST), Sofia, Bulgaria, 26–28 June 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Han, T.; Dou, X.; Lin, B. A Non-orthogonal Multi-carrier Frequency Hopping Based Secure Differential Chaos Shift Keying for Autonomous Ummanned Systems. In Proceedings of the 2024 IEEE/CIC International Conference on Communications in China (ICCC Workshops), Hangzhou, China, 7–9 August 2024; pp. 885–888. [Google Scholar] [CrossRef]

- Kennedy, M.; Kolumban, G.; Kis, G.; Jako, Z. Performance evaluation of FM-DCSK modulation in multipath environments. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2000, 47, 1702–1711. [Google Scholar] [CrossRef]

- Babajans, R.; Cirjulina, D.; Capligins, F.; Kolosovs, D.; Litvinenko, A. Synchronization of Analog-Discrete Chaotic Systems for Wireless Sensor Network Design. Appl. Sci. 2024, 14, 915. [Google Scholar] [CrossRef]

- An, Y.H.; Xu, H.; Zhang, Y.Y.; Wang, H.Z.; Xie, K.Y.; Zhang, C.K. Design and implementation of master-slave synchronization for chaotic Lur’e systems using Chua’s circuit. In Proceedings of the 2024 43rd Chinese Control Conference (CCC), Kunming, China, 28–31 July 2024; pp. 682–686. [Google Scholar] [CrossRef]

- Cheng, H.; Li, H.; Dai, Q.; Yang, J. A deep reinforcement learning method to control chaos synchronization between two identical chaotic systems. Chaos Solitons Fractals 2023, 174, 113809. [Google Scholar] [CrossRef]

- Chou, H.G.; Chuang, C.F.; Wang, W.J.; Lin, J.C. A fuzzy-model-based chaotic synchronization and its implementation on a secure communication system. IEEE Trans. Inf. Forensics Secur. 2013, 8, 2177–2185. [Google Scholar] [CrossRef]

- Du, L.; Wang, F.; Han, Z.; Dong, J. Chaos Synchronization of a Class of Chaotic Systems via Linear State Error Feedback Control. In Proceedings of the 2nd International Conference on Advances in Mechanical Engineering and Industrial Informatics (AMEII 2016), Hangzhou, China, 9–10 April 2016. [Google Scholar] [CrossRef]

- Bendoukha, S.; Abdelmalek, S.; Ouannas, A. Secure communication systems based on the synchronization of chaotic systems. Stud. Syst. Decis. Control 2019, 200, 281–311. [Google Scholar] [CrossRef]

- Bilgehan, B.; Sabuncu, O. Synchronization and Analysis of Chaotic Circuit with Application to Communication in the internet of things (IoT) Services. In Proceedings of the 2022 International Conference on Artificial Intelligence in Everything (AIE), Lefkosa, Cyprus, 2–4 August 2022; pp. 674–678. [Google Scholar] [CrossRef]

- Çiçek, S.; Kocamaz, U.E.; Uyaroğlu, Y. Secure Chaotic Communication with Jerk Chaotic System Using Sliding Mode Control Method and Its Real Circuit Implementation. Iran. J. Sci. Technol. Trans. Electr. Eng. 2019, 43, 687–698. [Google Scholar] [CrossRef]

- Deniz, H.I.; Gulru Cam Taskiran, Z.; Sedef, H. Chaotic Lorenz Synchronization Circuit Design for Secure Communication. In Proceedings of the 2018 6th International Conference on Control Engineering & Information Technology (CEIT), Istanbul, Turkey, 25–27 October 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Gularte, K.H.; Gomez, J.C.; Vizcarra Melgar, M.E.; Vargas, J.A. Chaos Synchronization and its Application in Parallel Cryptography. In Proceedings of the 2021 IEEE 5th Colombian Conference on Automatic Control (CCAC), Ibague, Colombia, 19–22 October 2021; pp. 198–203. [Google Scholar] [CrossRef]

- Karimov, T.; Butusov, D.; Andreev, V.; Karimov, A.; Tutueva, A. Accurate Synchronization of Digital and Analog Chaotic Systems by Parameters Re-Identification. Electronics 2018, 7, 123. [Google Scholar] [CrossRef]

| Chaos Oscillator | Adaptive Logic Modules (ALMs) | Digital Signal-Processing (DSP) Blocks | Block Memory Bits |

|---|---|---|---|

| Vilnius | 67 (<1%) | 1 (1%) | 90,122 (2%) |

| RC | 115 (<1%) | 5 (6%) | 90,122 (2%) |

| Discrete–Analog | Analog–Discrete | |||

|---|---|---|---|---|

| Chaos Oscillator | and | and | and | and |

| Vilnius | 0.97 | 0.98 | 0.93 | 0.92 |

| RC | 0.72 | 0.97 | 0.89 | 0.90 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Babajans, R.; Cirjulina, D.; Kolosovs, D. Field-Programmable Gate Array-Based Chaos Oscillator Implementation for Analog–Discrete and Discrete–Analog Chaotic Synchronization Applications. Entropy 2025, 27, 334. https://doi.org/10.3390/e27040334

Babajans R, Cirjulina D, Kolosovs D. Field-Programmable Gate Array-Based Chaos Oscillator Implementation for Analog–Discrete and Discrete–Analog Chaotic Synchronization Applications. Entropy. 2025; 27(4):334. https://doi.org/10.3390/e27040334

Chicago/Turabian StyleBabajans, Ruslans, Darja Cirjulina, and Deniss Kolosovs. 2025. "Field-Programmable Gate Array-Based Chaos Oscillator Implementation for Analog–Discrete and Discrete–Analog Chaotic Synchronization Applications" Entropy 27, no. 4: 334. https://doi.org/10.3390/e27040334

APA StyleBabajans, R., Cirjulina, D., & Kolosovs, D. (2025). Field-Programmable Gate Array-Based Chaos Oscillator Implementation for Analog–Discrete and Discrete–Analog Chaotic Synchronization Applications. Entropy, 27(4), 334. https://doi.org/10.3390/e27040334