Low-Voltage Control Circuits of Formula Student Electric Racing Cars

Abstract

1. Introduction

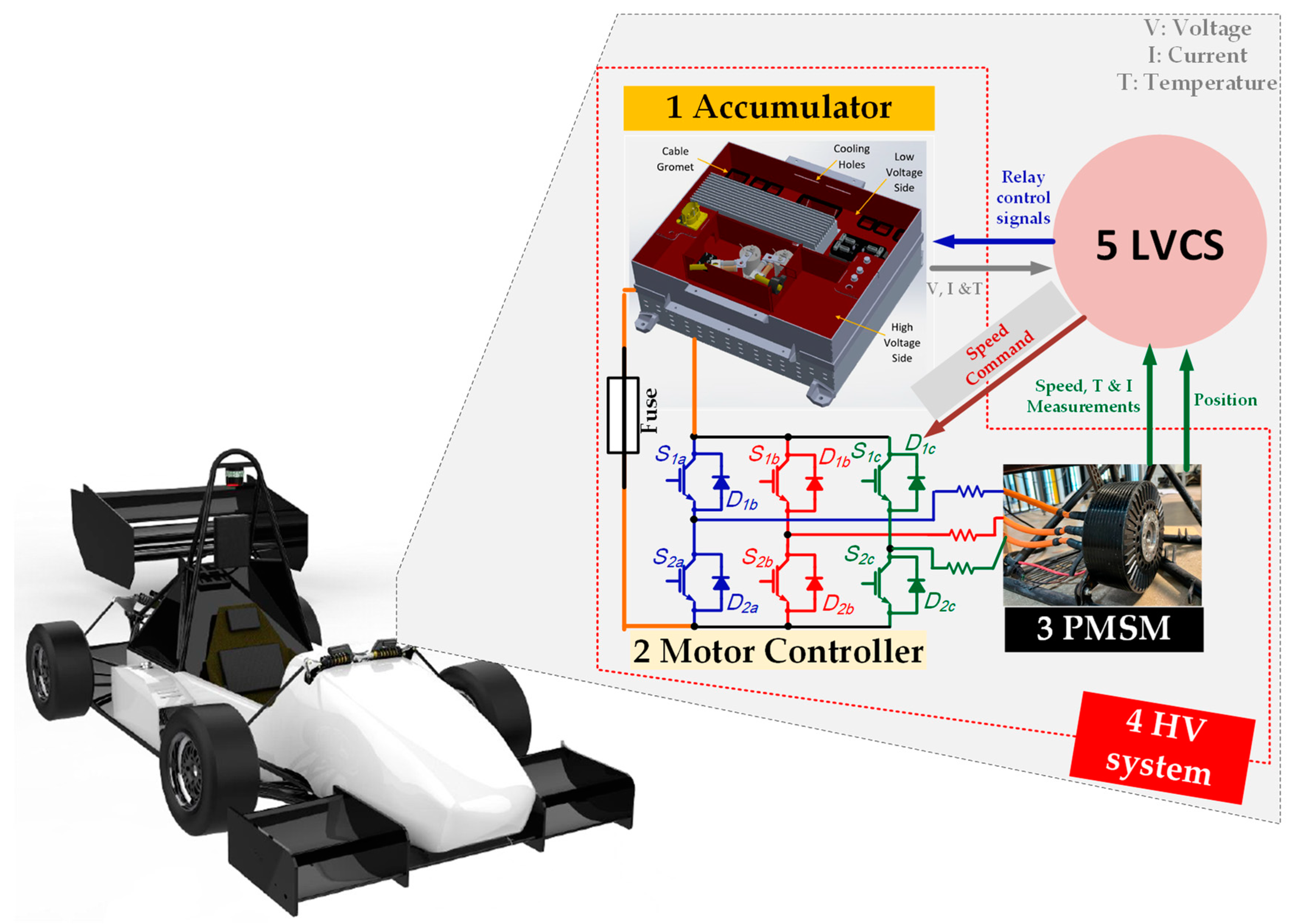

- The accumulator: This comprises the battery cells, high-voltage (HV) cables, protection devices, and the battery management system (BMS) which is responsible for monitoring and managing the batteries. Typically, the accumulator voltage is in the range of 100 V to 600 V based on the designed value of the DC-link voltage and hence the nominal voltage of the selected motor and its controller.

- The motor controller (traction inverter): Typically, this component is a DC-AC inverter for AC motors or a DC-DC chopper for DC motors.

- The electric motor: In the 2023 FSUK, all FSERCs utilized AC machines, either synchronous or induction. AC machines are favoured for their enhanced efficiency, compact size, higher power density, and the absence of carbon brushes, which require servicing every six months of operation [6]. Brushless DC (BLDC) motors utilize permanent magnet synchronous machines (PMSM) to generate a trapezoidal-shaped AC back electromotive force (EMF), which simplifies the modulation of the motor controller.

- The HV system: This system encompasses the HV cables situated outside the accumulator, along with the protection fuses and the HV disconnect (HVD) interlocks. Its primary function is to manage the connection, disconnection, and safeguarding of electric current flow from the accumulator to the motor through the motor controller. It includes all components connected to the motor, inverter, the accumulator, and the DC-link between them.

- The low-voltage (LV) system: This comprises the electronic system responsible for operating and controlling the HV systems within the FSERC. It usually operates at low voltage (LV) levels ranging from 6V to 24 V, with 12 V being a common value. The LV control system (LVCS) consists of various electronic circuits (ECs) assigned to different functions within the FSERC. These ECs are distributed across nearly every subsystem to fulfil a range of tasks, including toggling operations on/off, issuing warnings, transmitting data, or executing safety routines.

2. Design Overview

2.1. Shutdown Line

- (a)

- LV master switch (LVMS): this is an NO switch responsible for linking the LVB to the remainder of the line. The first EC connected to the SD line is the brake system plausibility device (BSPD), which will be presented alongside the other ECs in subsequent subsections.

- (b)

- SD switches: these are three normally closed (NC) manual emergency switches fitted in the cockpit, as well as on the right and left sides of the FSERC. The users can disconnect the SD line by pressing any of these three switches.

- (c)

- Inertia switch: this is an NC switch employed to safeguard the FSERC by detecting the sudden deceleration indicative of an accident and hence trip the SD line. The inertia switch is connected in series with the SD line following the three manual SD switches.

- (d)

- Brake over travel switch (BOTS): this is an NC switch located physically beyond the brake pedal and is used to trip the SD line when the driver exceeds the permissible range for pressing the pedal.

- (e)

- HVD interlock: this is a NC contact integrated within the HVD connector but electrically isolated from the HV path. The main function of the HVD interlock is to guarantee that the SD line is disconnected whenever the HVD plug is removed. This will ensure that the battery voltage will not be present at the terminals of the HVD if the plug is removed for any reason.

- (f)

- Tractive system master switch (TSMS): this NO manual switches should be the final connector in the SD line which will be switched on when the FSERC is ready to operate. Activating the TSMS signifies that the accumulator of the FSERC is prepared to be connected to the DC-link of the motor controller. The HV circuit will be closed by the activation logic (AL) EC which is responsible for turning the accumulator insulation relays (AIRs) on. It is worth noting that the negative terminal of the HV system is left floating while the ground of the LV system is connected to all conductive parts in the chassis.

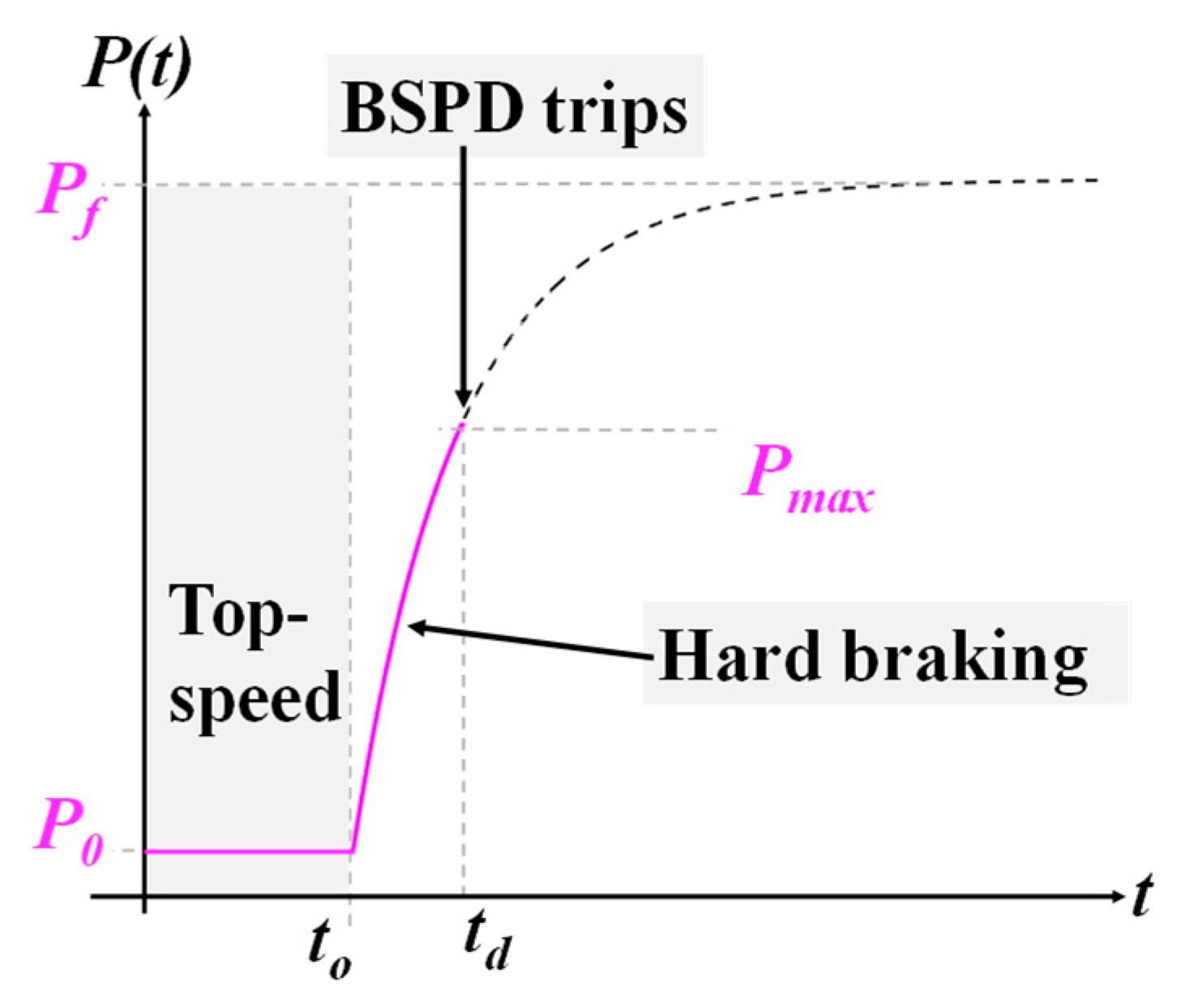

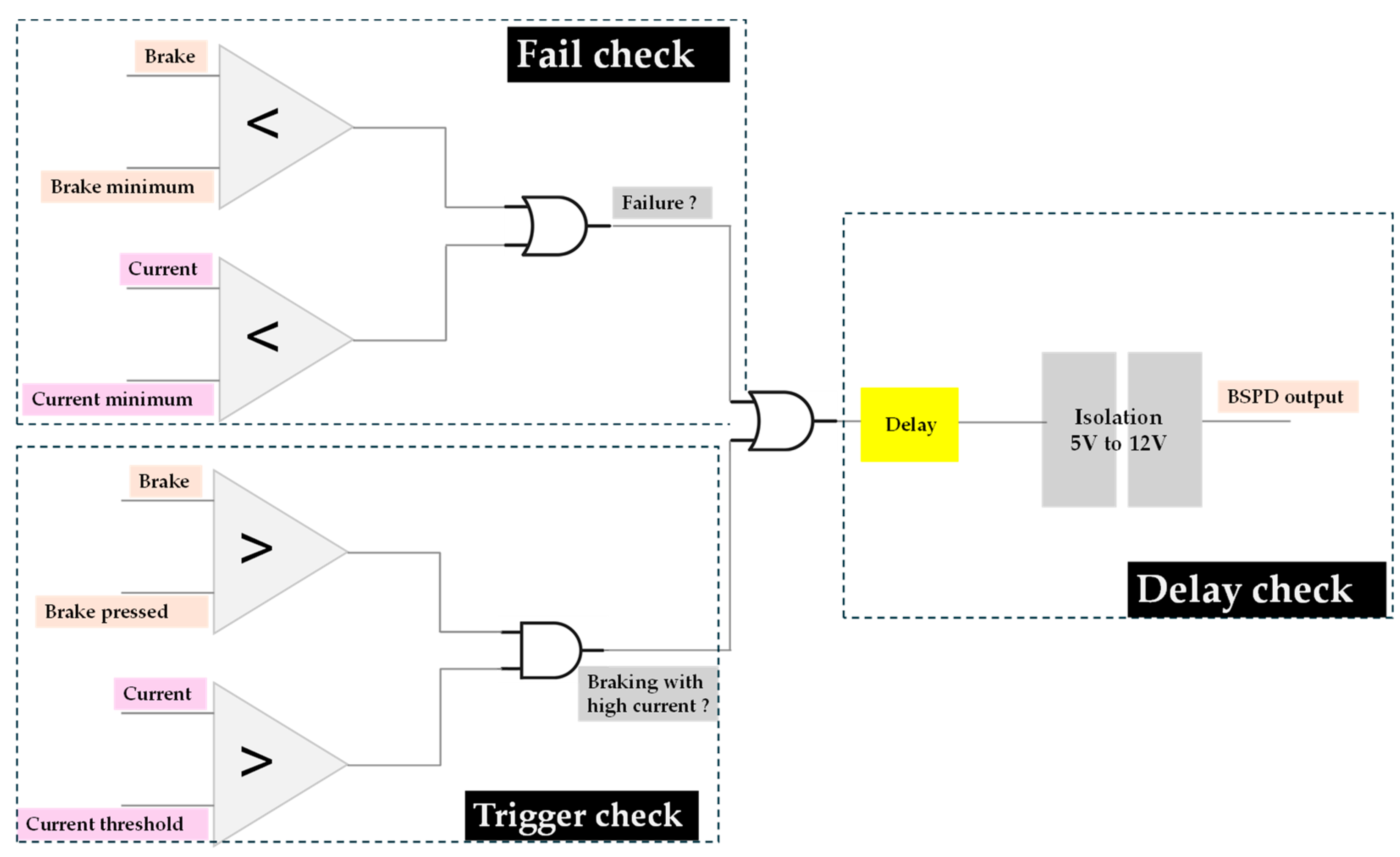

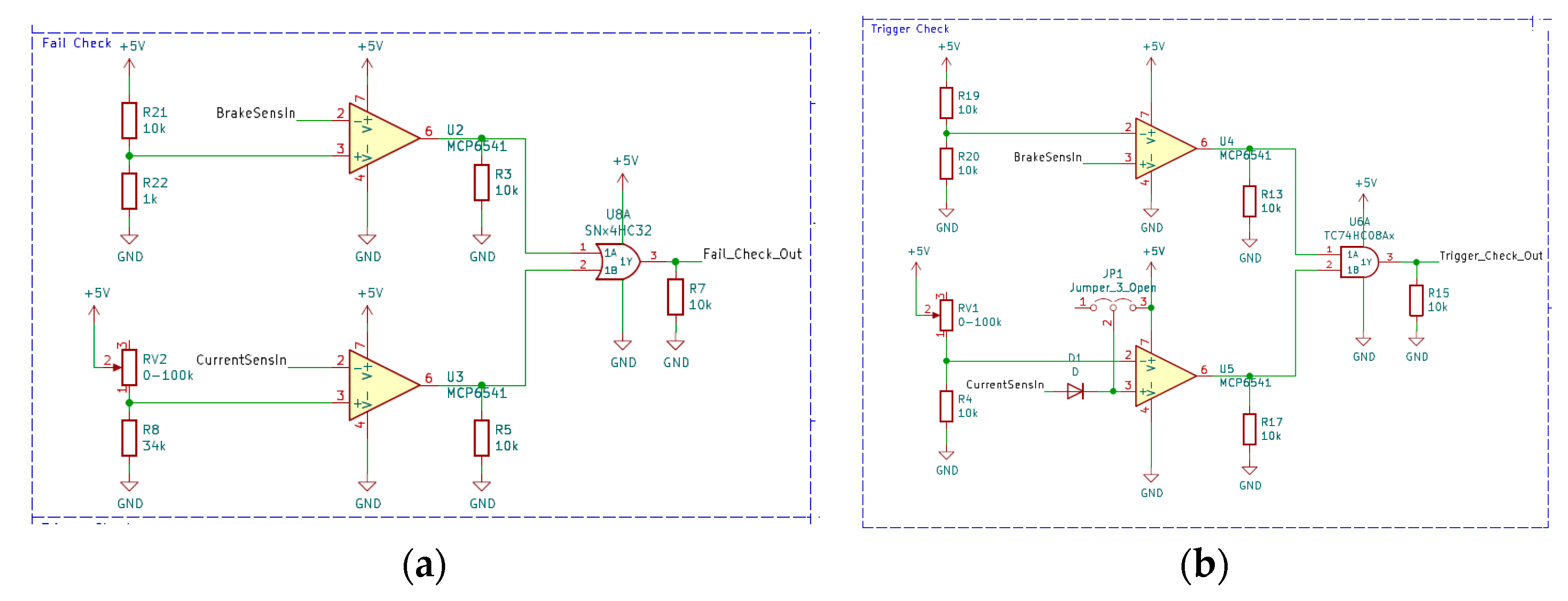

2.2. BSPD Circuit

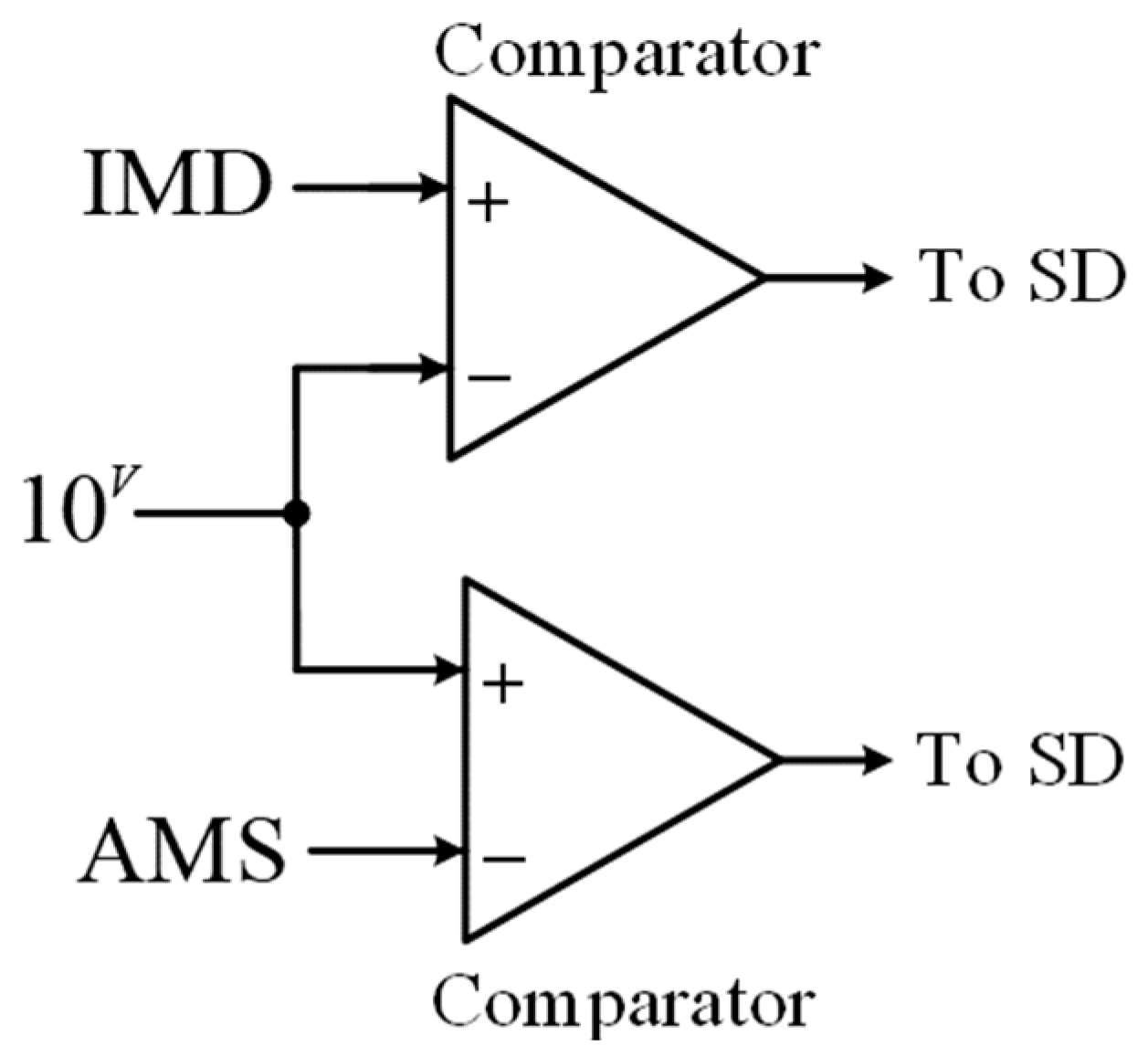

2.3. IMD and AMS

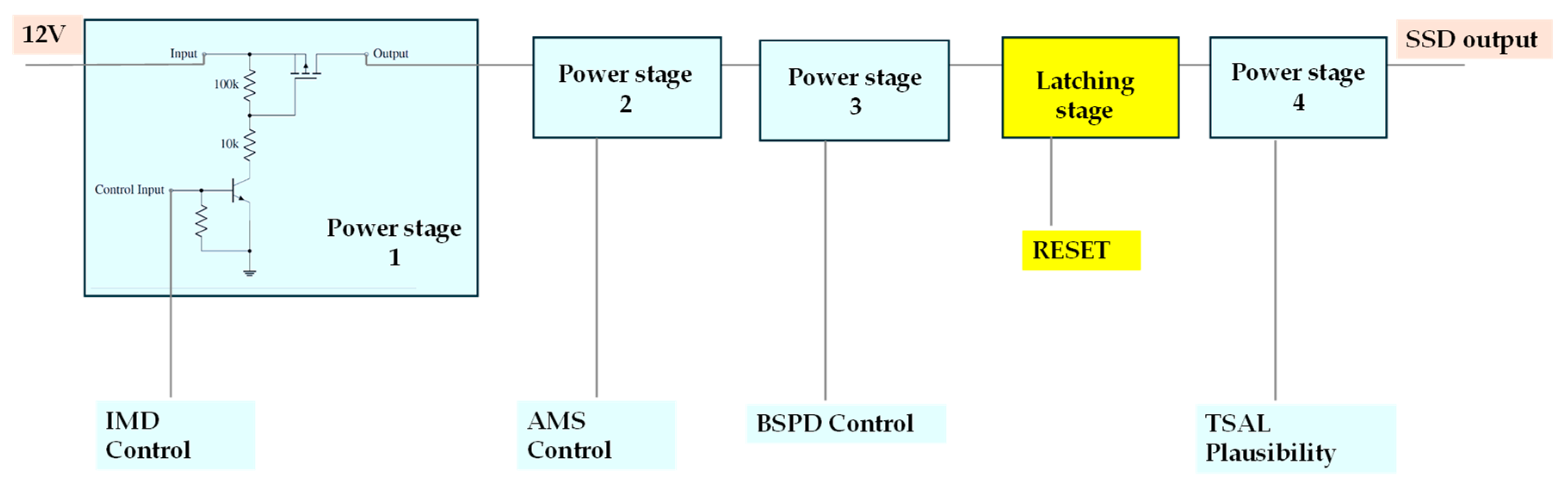

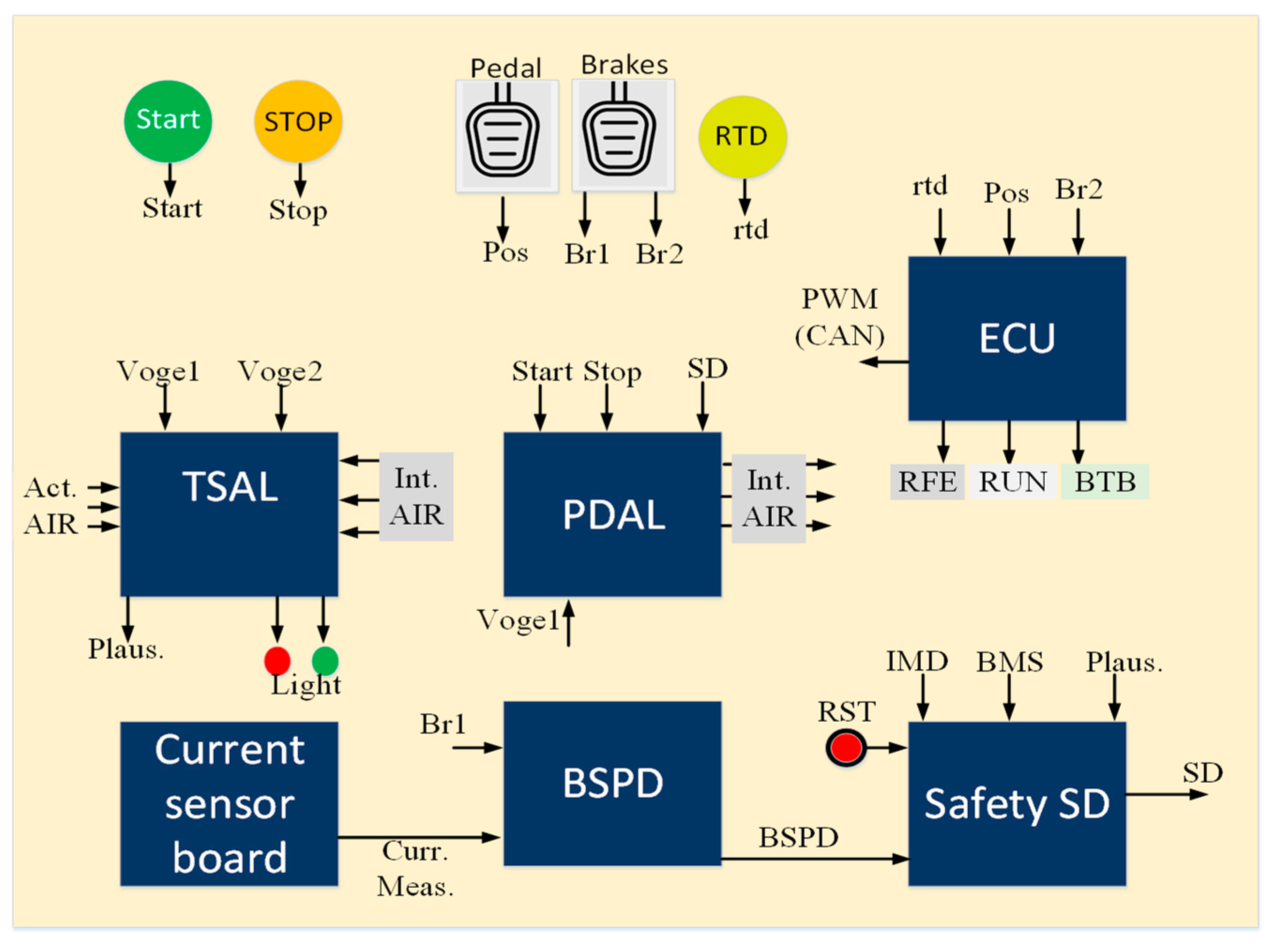

2.4. SSD Circuit

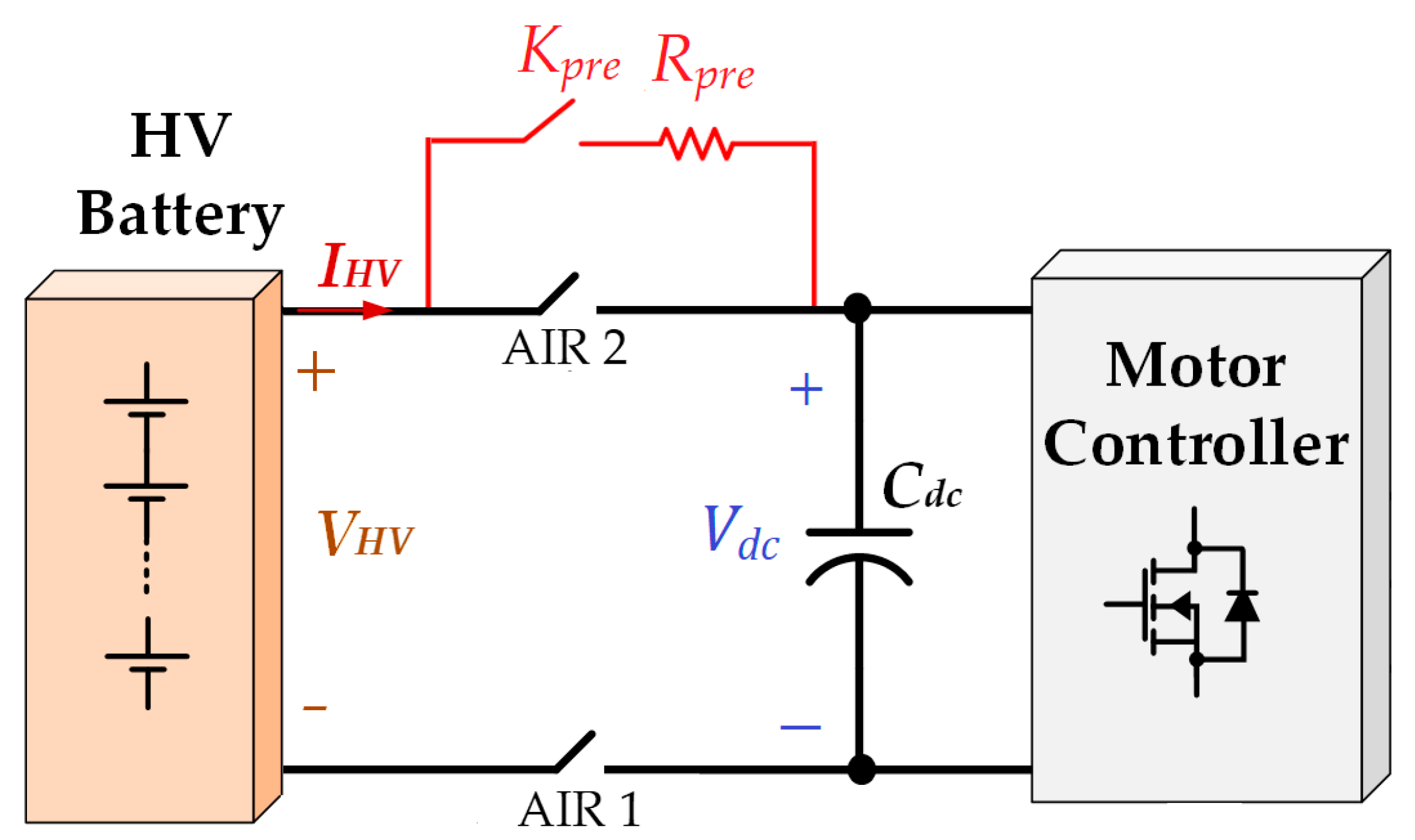

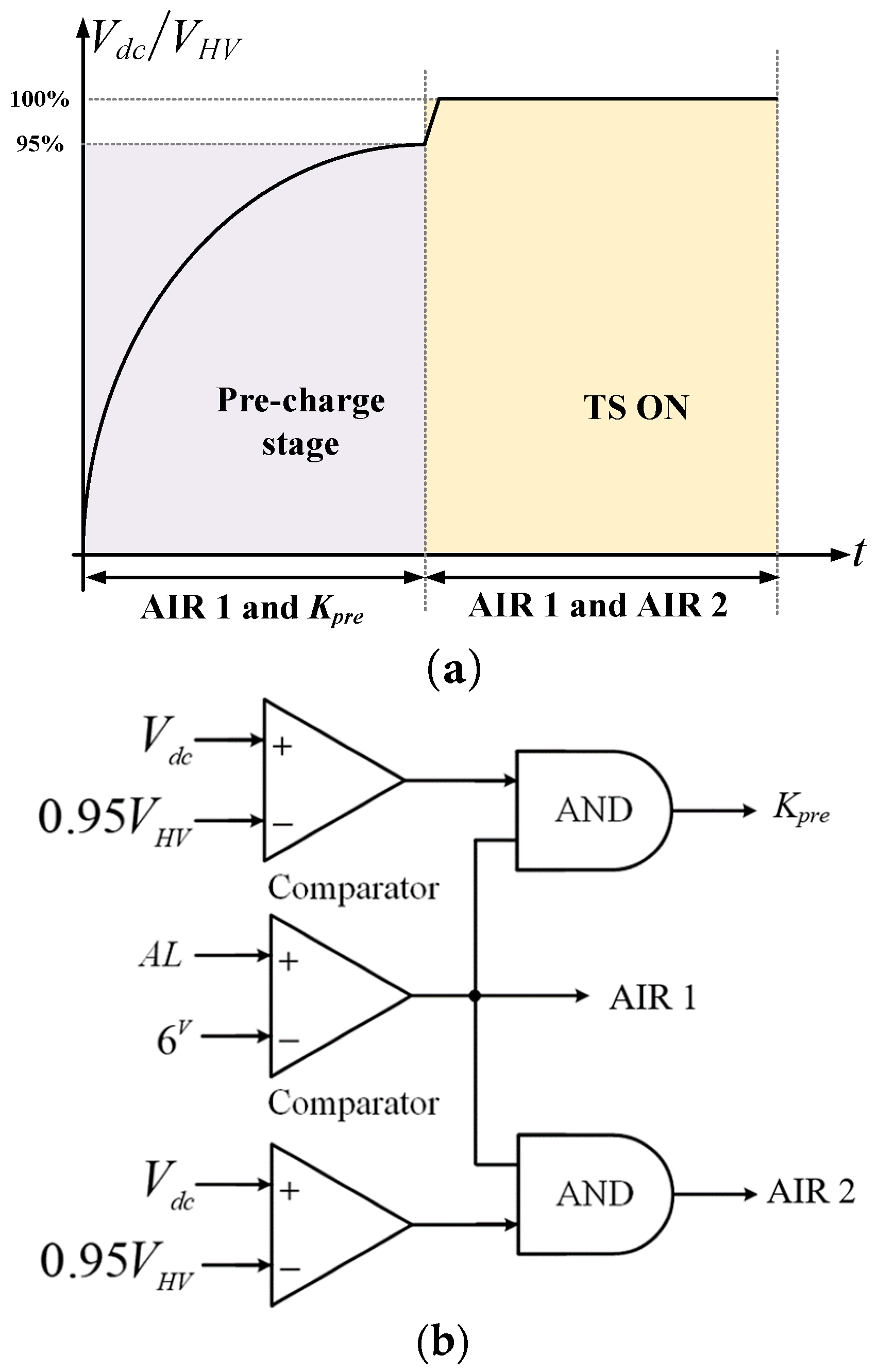

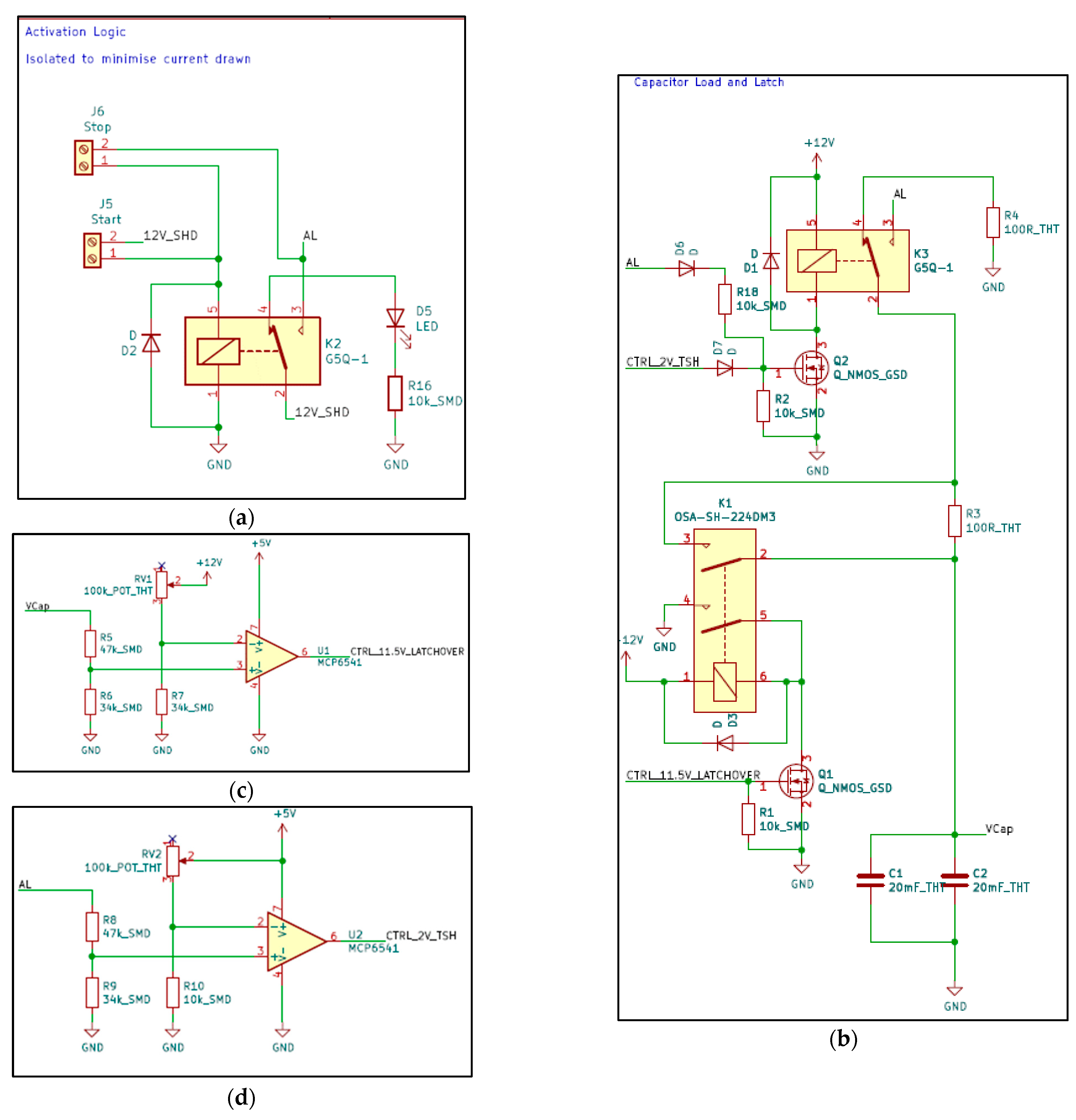

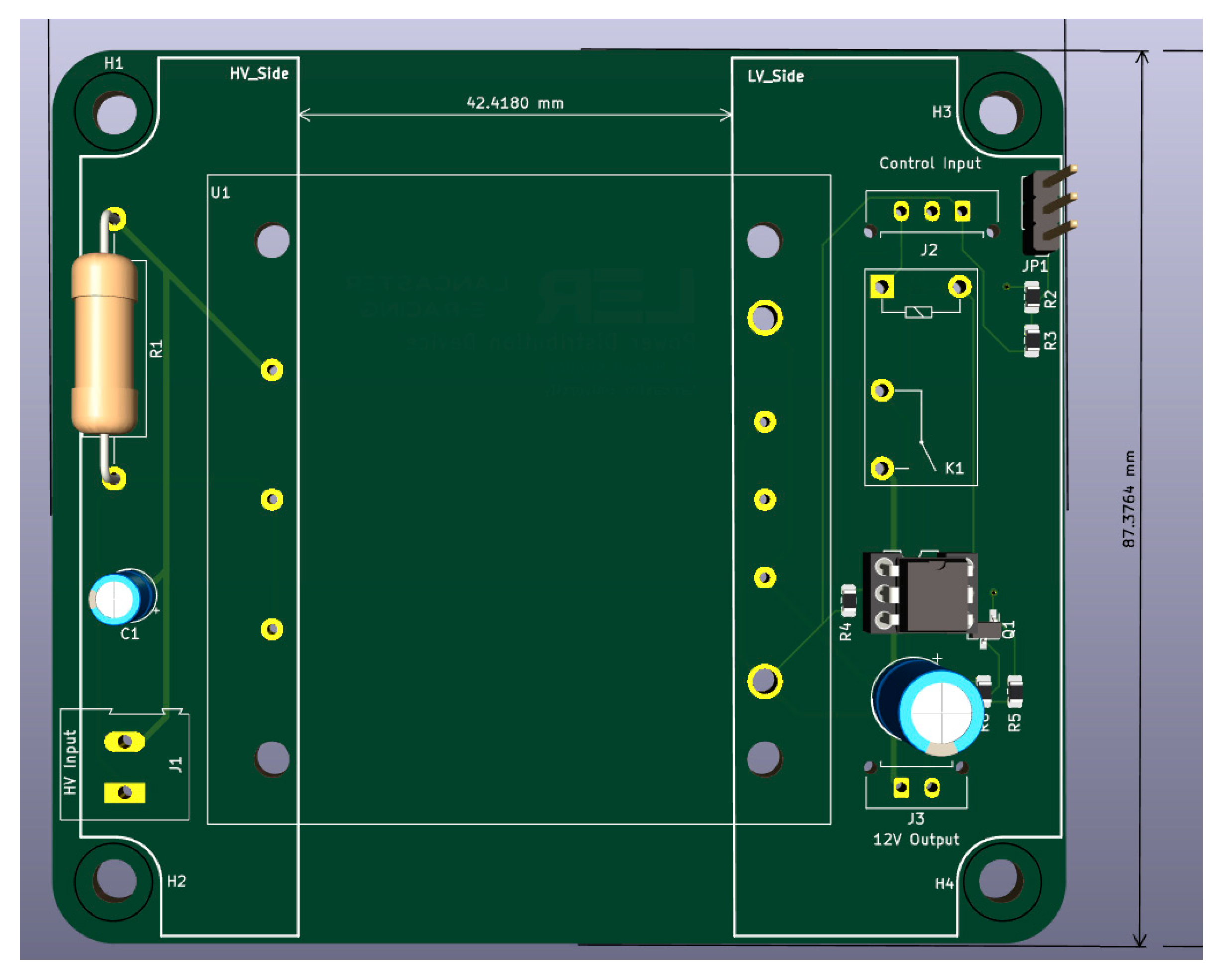

2.5. Pre Charge/Discharge/Activation Logic Circuit

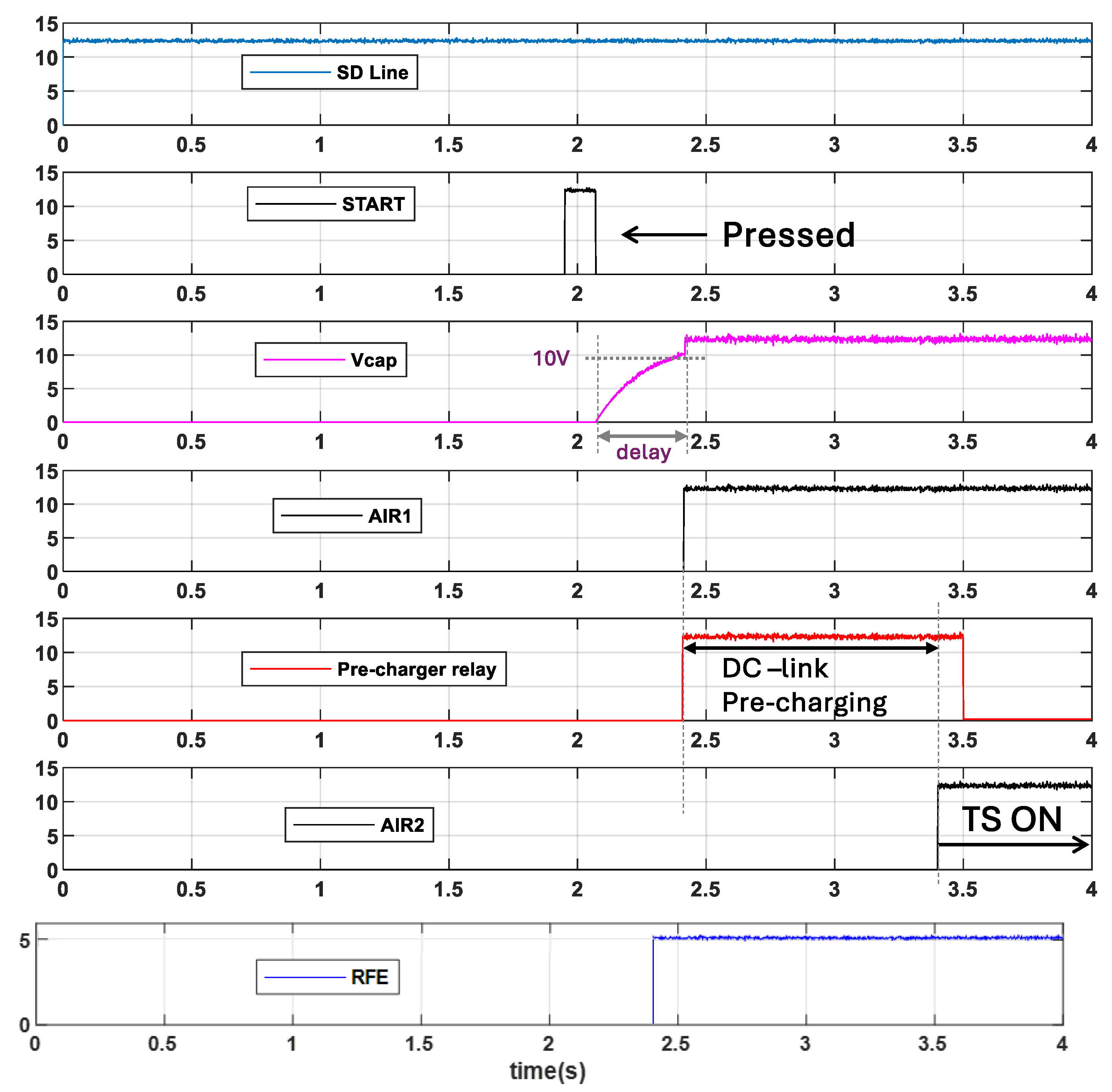

2.5.1. Pre-Charge

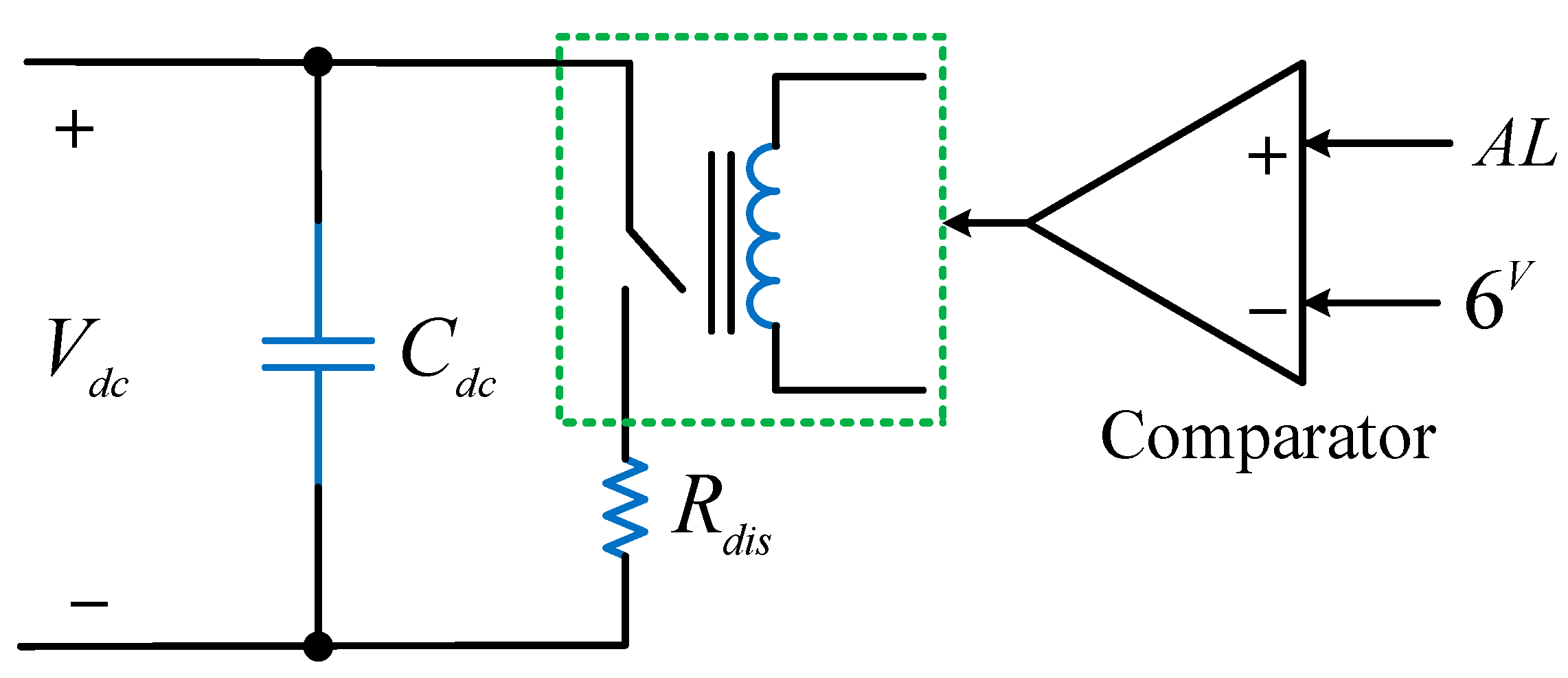

2.5.2. Discharge

2.5.3. Activation Logic

- (1)

- Turn on the TS when the driver is ready to start racing using a START button within the cockpit. This should start with the pre-charge stage as discussed in Section 2.5.1. For safety reason, the START button should be of a push-release type and therefore the PDAL should latch this command.

- (2)

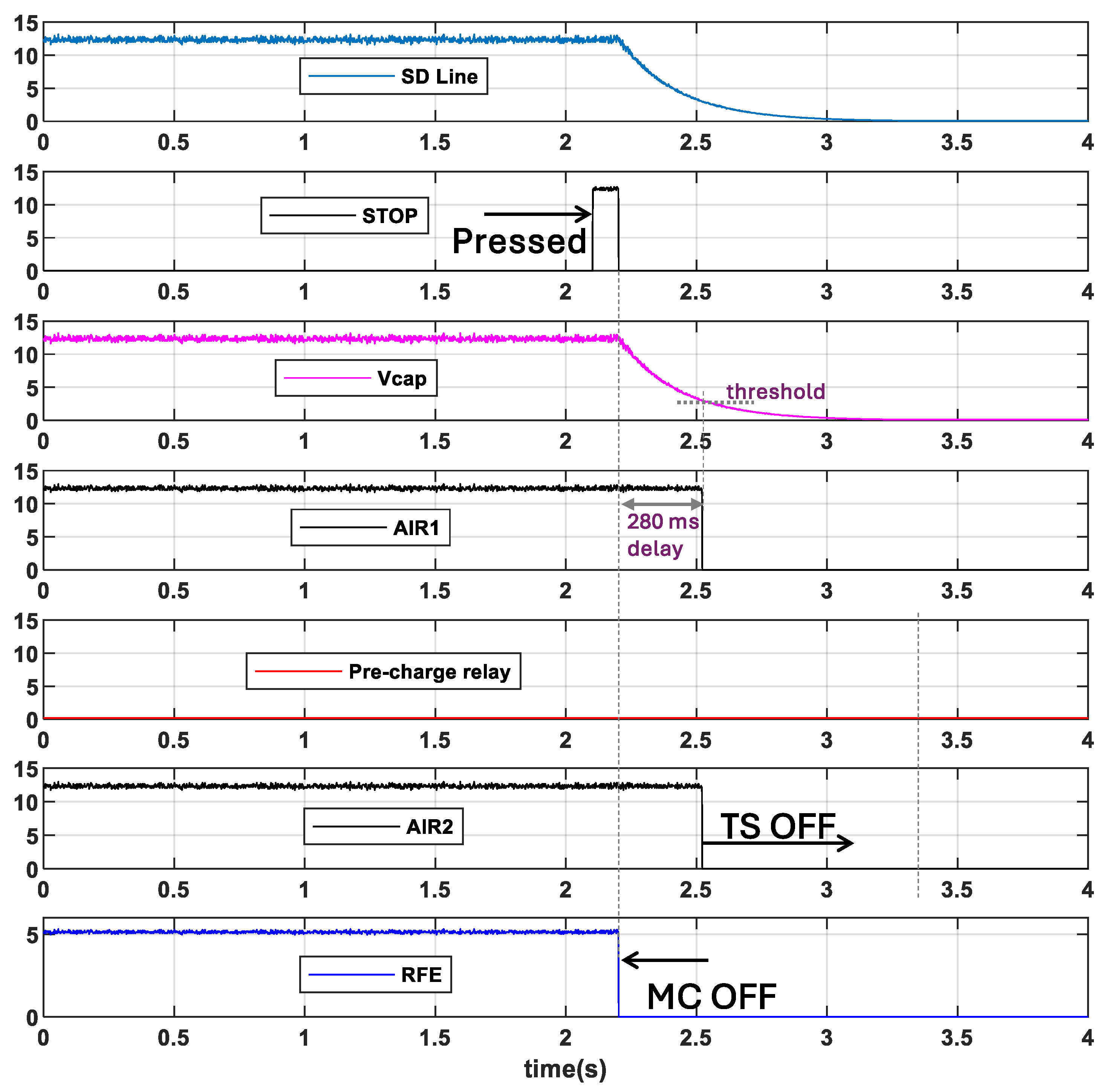

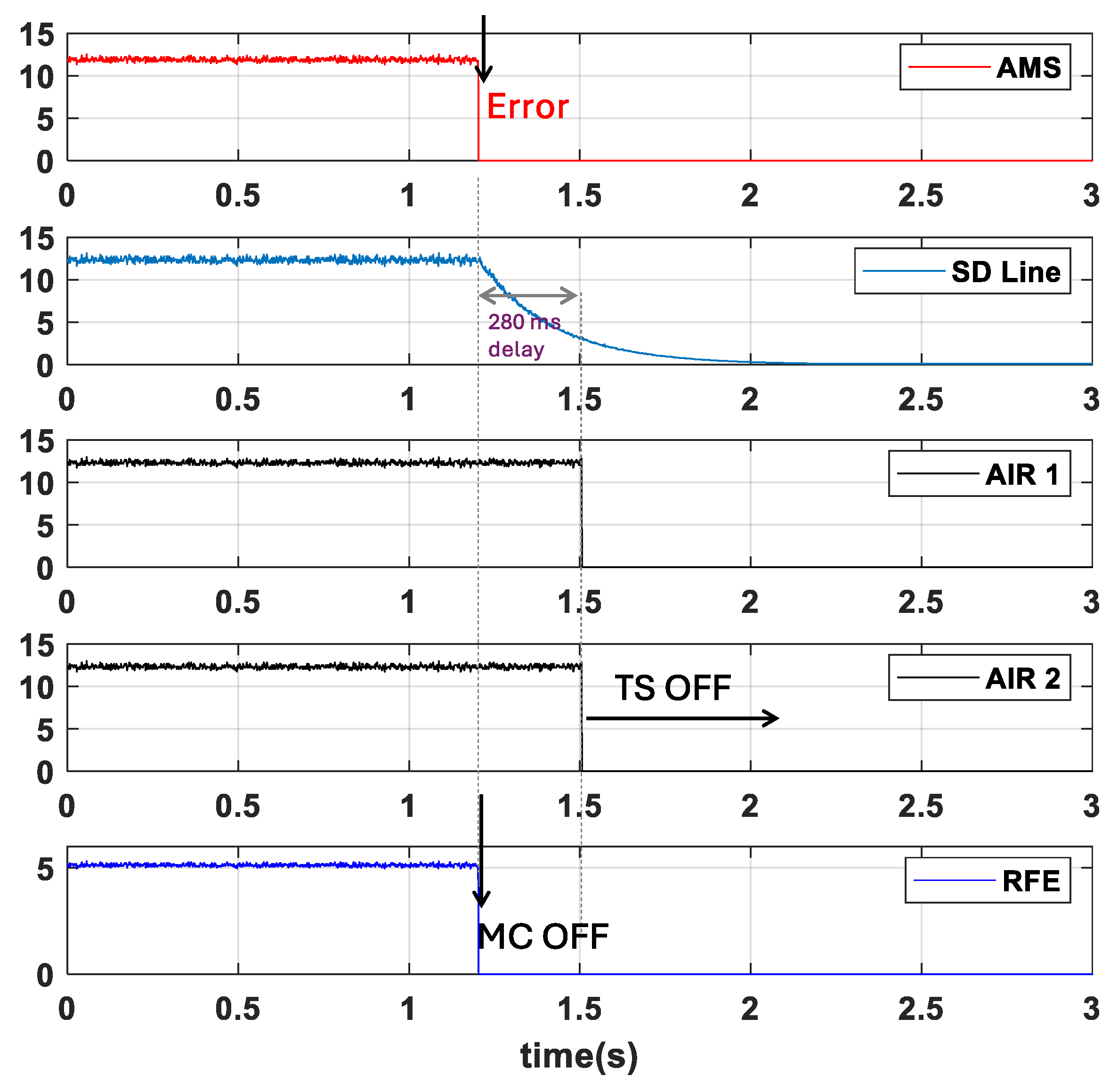

- Turn off the TS when driver wants to disconnect the TS system using a STOP button within the cockpit. This should be followed by the discharge routine in Section 2.5.2 to ensure that the dc-link capacitor is completely discharged.

- (3)

- The PDAL should disconnect the TS when any error signal arises, an emergency button is pressed, or any switch is opened as shown in Figure 2. In this case, the PDAL should not allow for a re-start without clearing the error and resetting the SD line by the ESOs.

- (4)

- If the TS is needed to be disconnected as in (2) or (3), a delay should be given between the command and the action to allow the motor controller to turn off the PMSM rotating magnetic field (RFE) before disconnecting the TS circuit. This is to protect the semiconductor devices (such as IGBTs or MOSFETs) from the voltage and current spikes that may occur. Usually, a time delay of around 200 ms should be sufficient to ensure the safe operation of the motor controller.

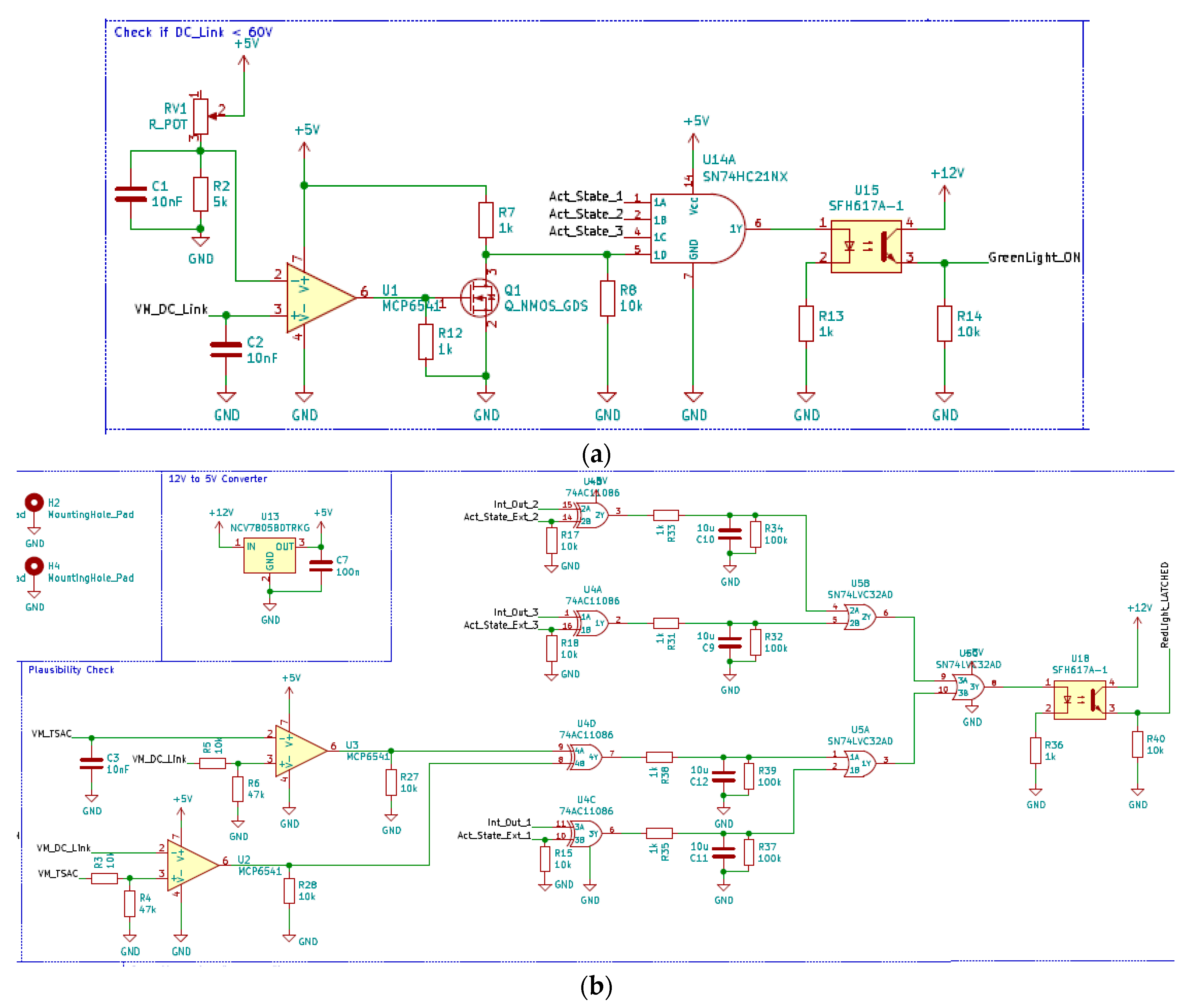

2.6. Tractive System Active Light

- ▪

- The TSAL light is green when only the LV is present at the vehicle side by turning the LVMS on. This indicates to the users that the FSERC is safe to approach and scrutinize.

- ▪

- The TSAL light is flashing red when any of the following is true:

- (1)

- AIR 1 or AIR 2 is on

- (2)

- Kpre is on

- (3)

- Vdc > 60 VDC

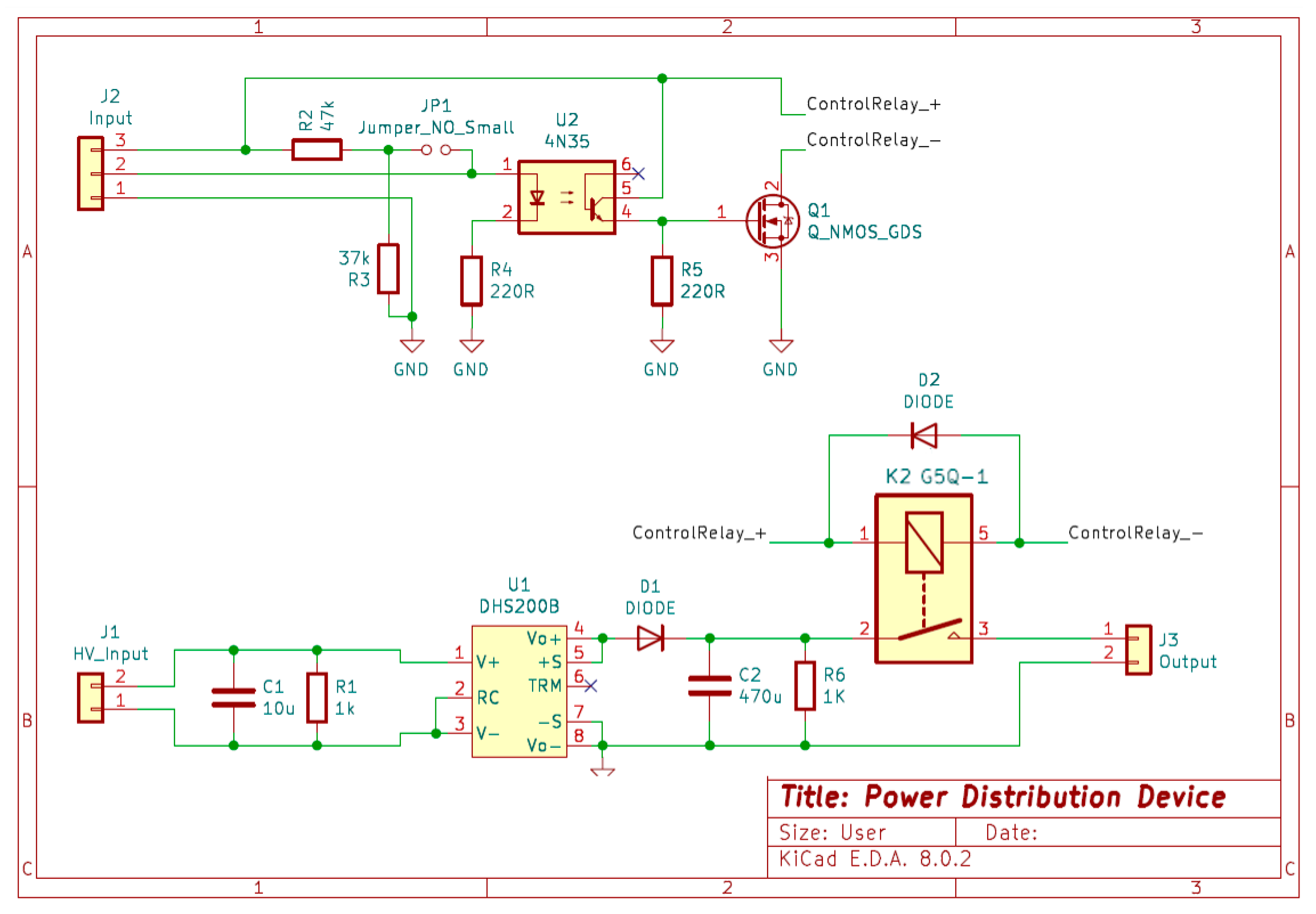

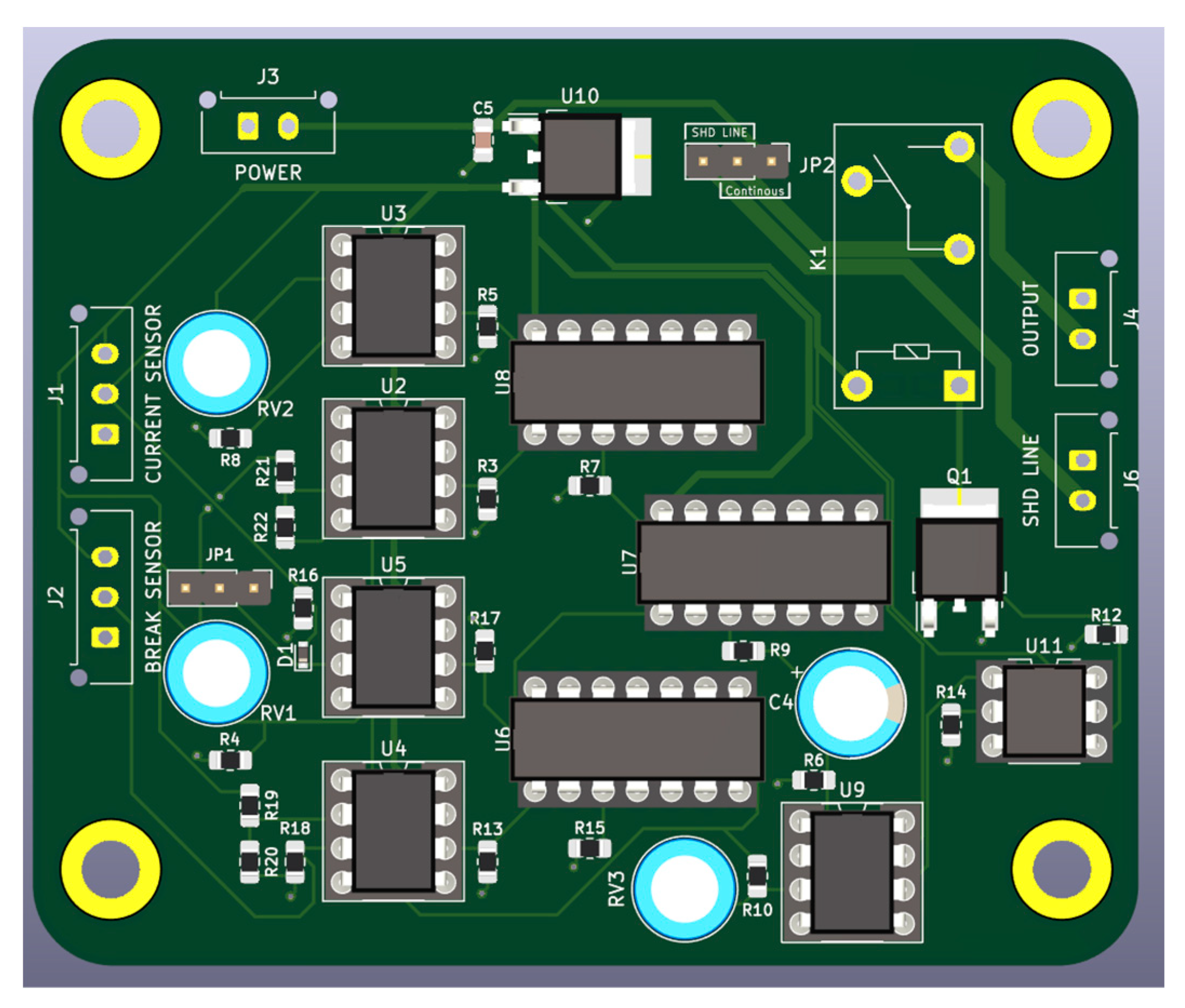

2.7. Power Distribution Board

2.8. Electronic Control Unit

- ▪

- APPS and Brake sensors: these are analogue input voltages in the range 0–5 V.

- ▪

- Ready-to-drive (RTD) button: this is a push-release button connected to the 5 V rail. The driver presses the RTD button with the brake pedal to awake the FSERC program providing that the TS is active, and the pre-charge stage has passed.

- ▪

- PDAL input: the status of the AL is sent to the ECU to inform the motor controller when the TS is about to be disconnected and accordingly the RFE of the motor should be shut down as explained earlier in Section 2.5.3. As the PDAL EC operates at 12 V, this signal needs to be stepped down to 5 V to be compatible with the µC analogue-to-digital (A2D) inputs.

- ▪

- Brake light control: the required voltage to turn on the red brake light at the back of the FSERC chassis. As the digital outputs (DOs) of the µC provide 5 V output voltages, opto-couplers are employed to provide the required 12 V voltage to the brake light circuit.

- ▪

- RTD Buzzer: to control the buzzer which gives an audible sound to the personnel indicating that the FSERC is ready to race.

- ▪

- Enable signals: 12 V signals to start and stop the motor controller.

- ▪

- Motor controller torque/speed command: this is an analogue 12 V signal to control the torque/speed of the motor.

3. Build Instructions

3.1. BSPD

3.1.1. Fail Check

3.1.2. Tigger Check

3.1.3. Power and Delay Stage

3.2. SSD

3.3. PDAL

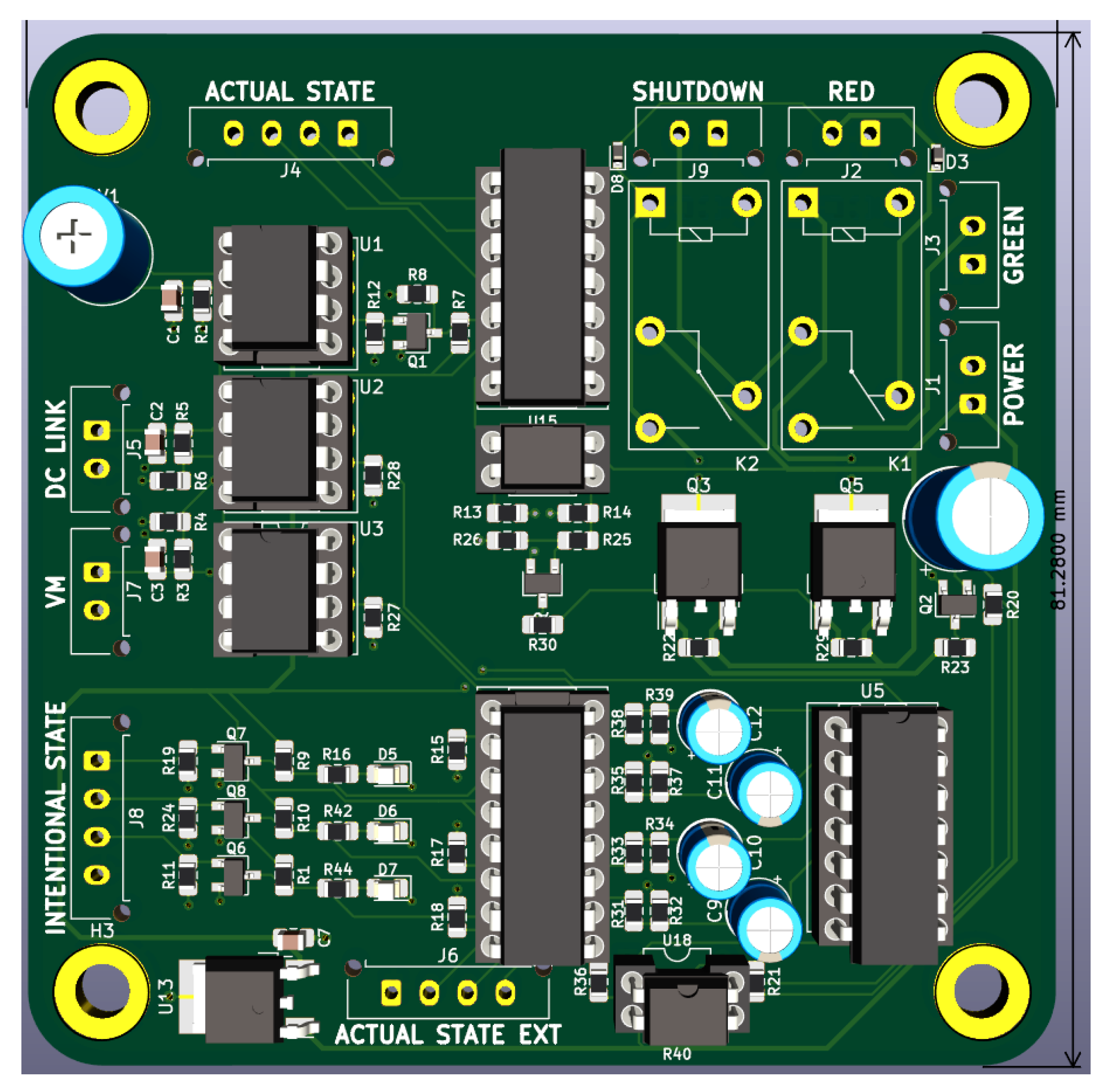

3.4. TSAL

3.4.1. Green Light Control

3.4.2. Red Light Control

3.4.3. Green and Red Lights Power Stage

3.5. PDB

3.6. ECU

4. Operating Instructions

4.1. BSPD

4.2. SSD

4.3. PDAL

4.4. TSAL

4.5. PDB

4.6. ECU

5. Validation

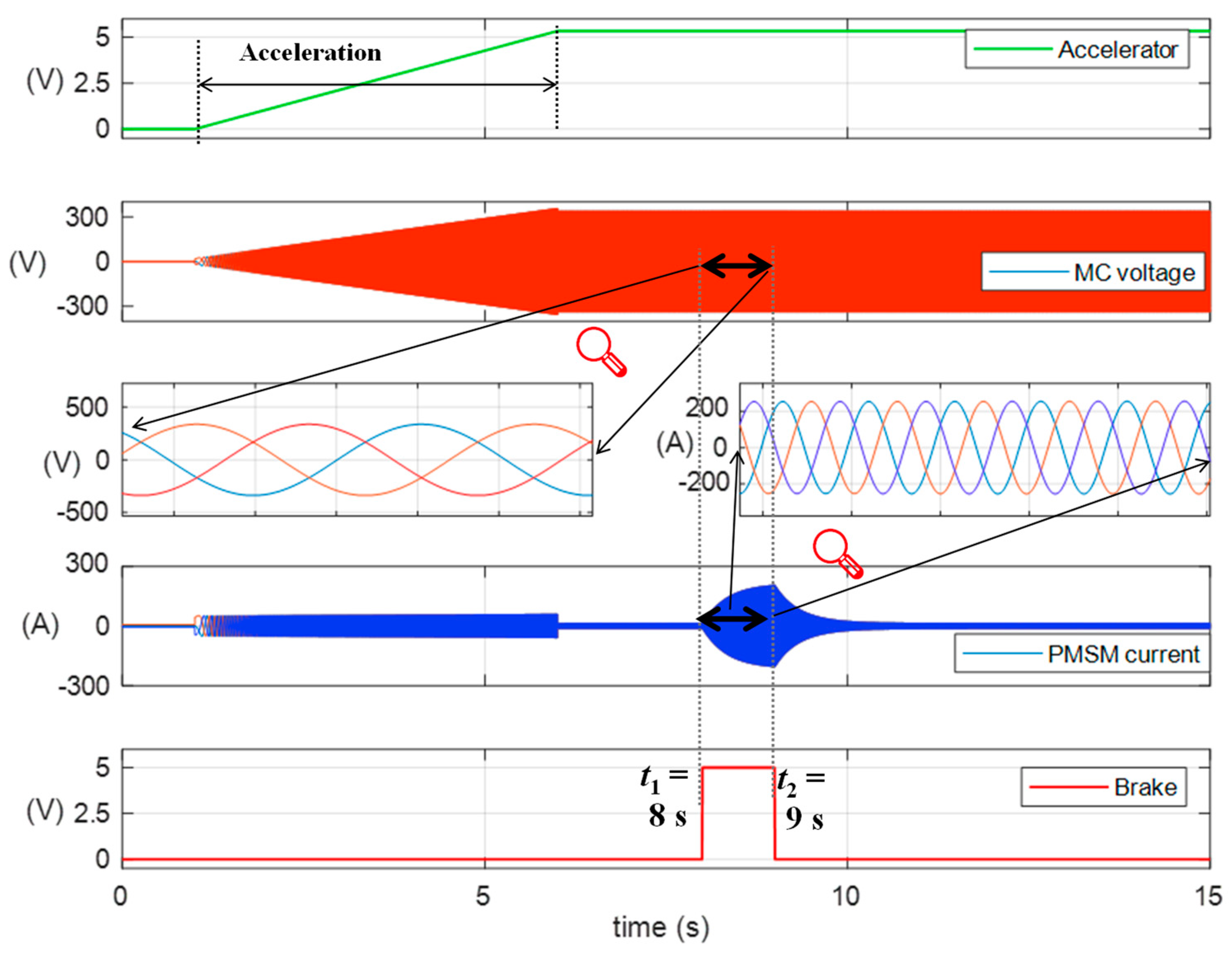

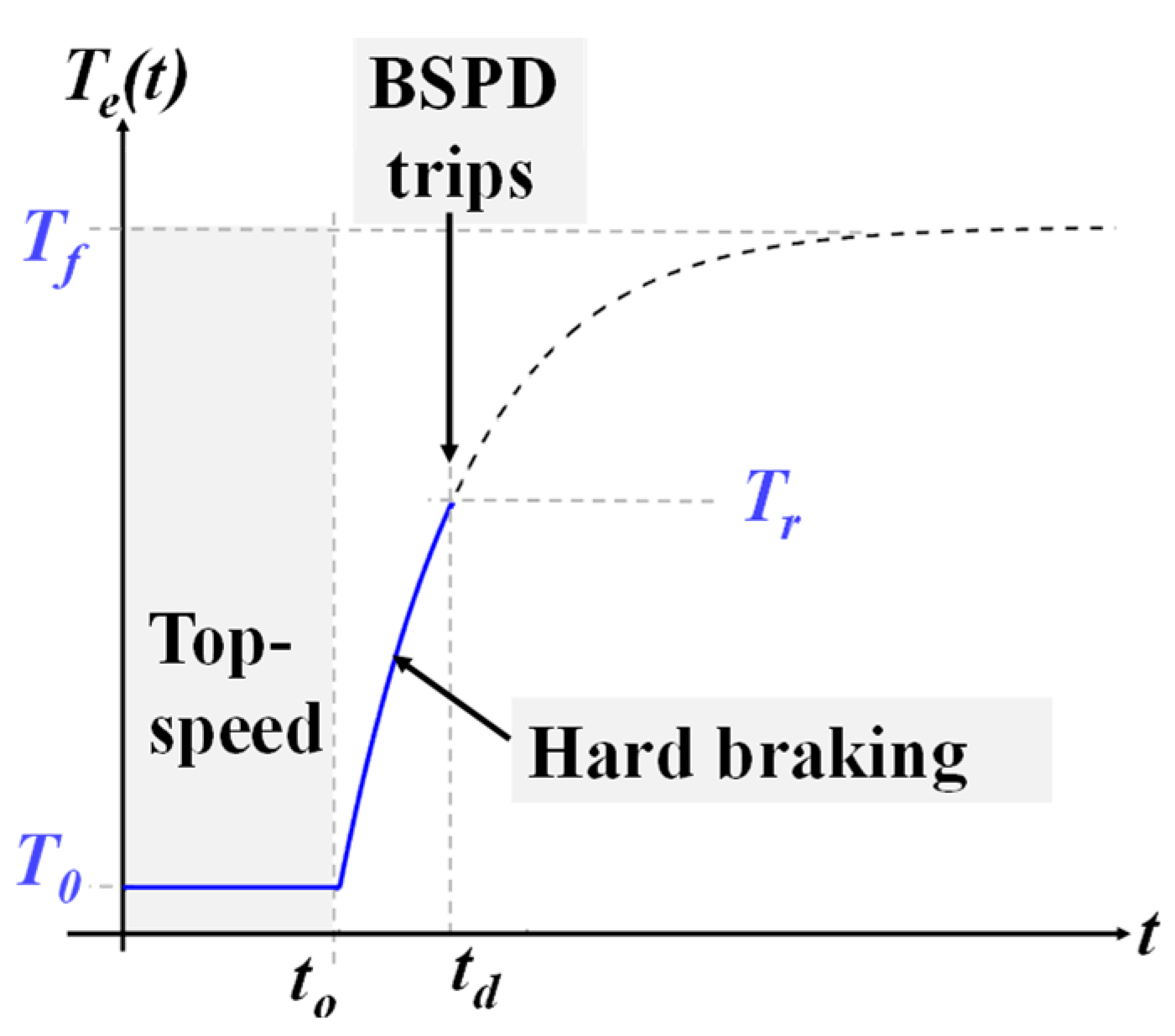

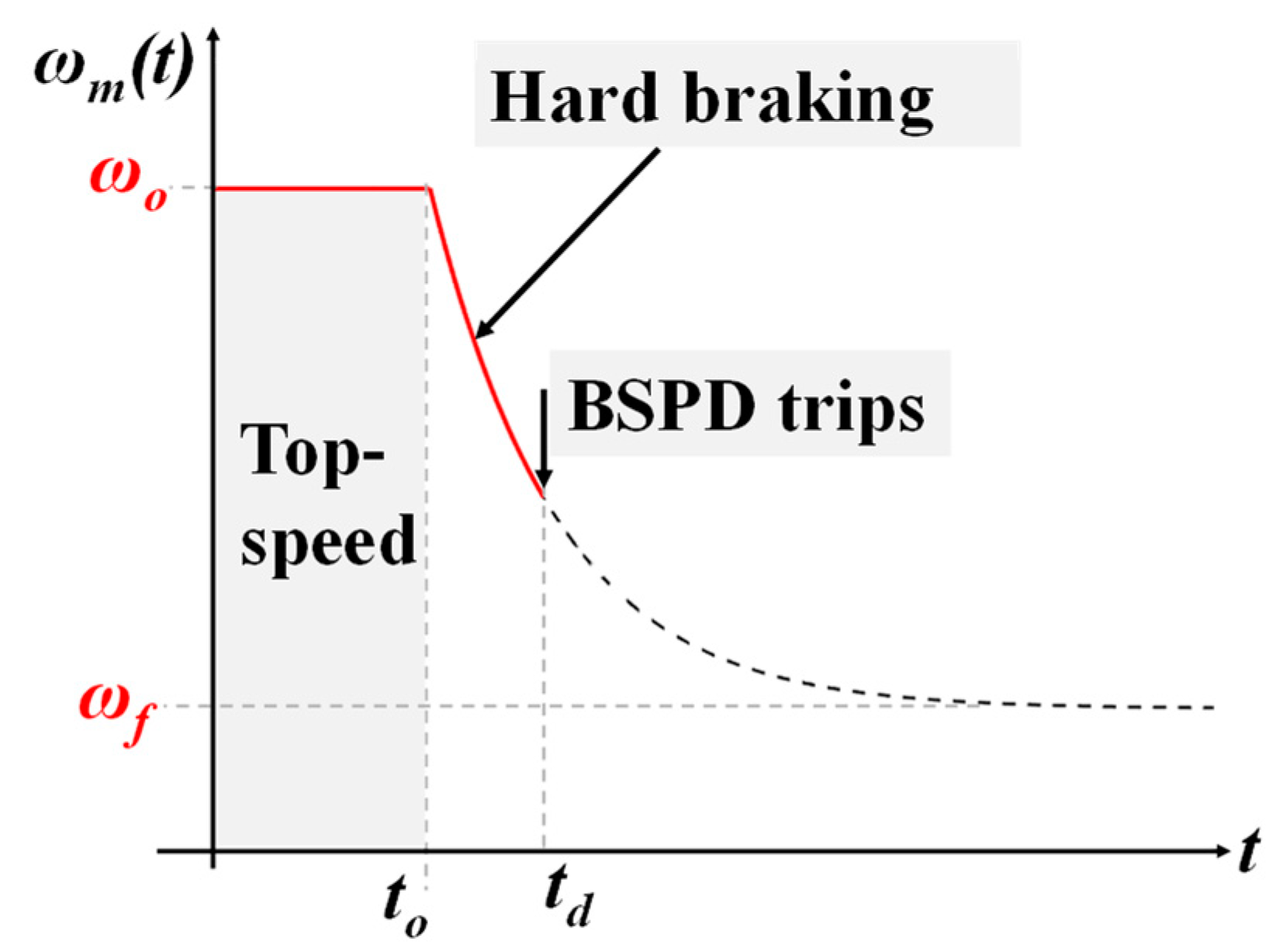

5.1. BSPD

5.2. SSD

5.3. PDAL

5.3.1. Turning the TS on

5.3.2. Turning the TS off

5.3.3. TS off Due to an SD Line Error

5.4. TSAL

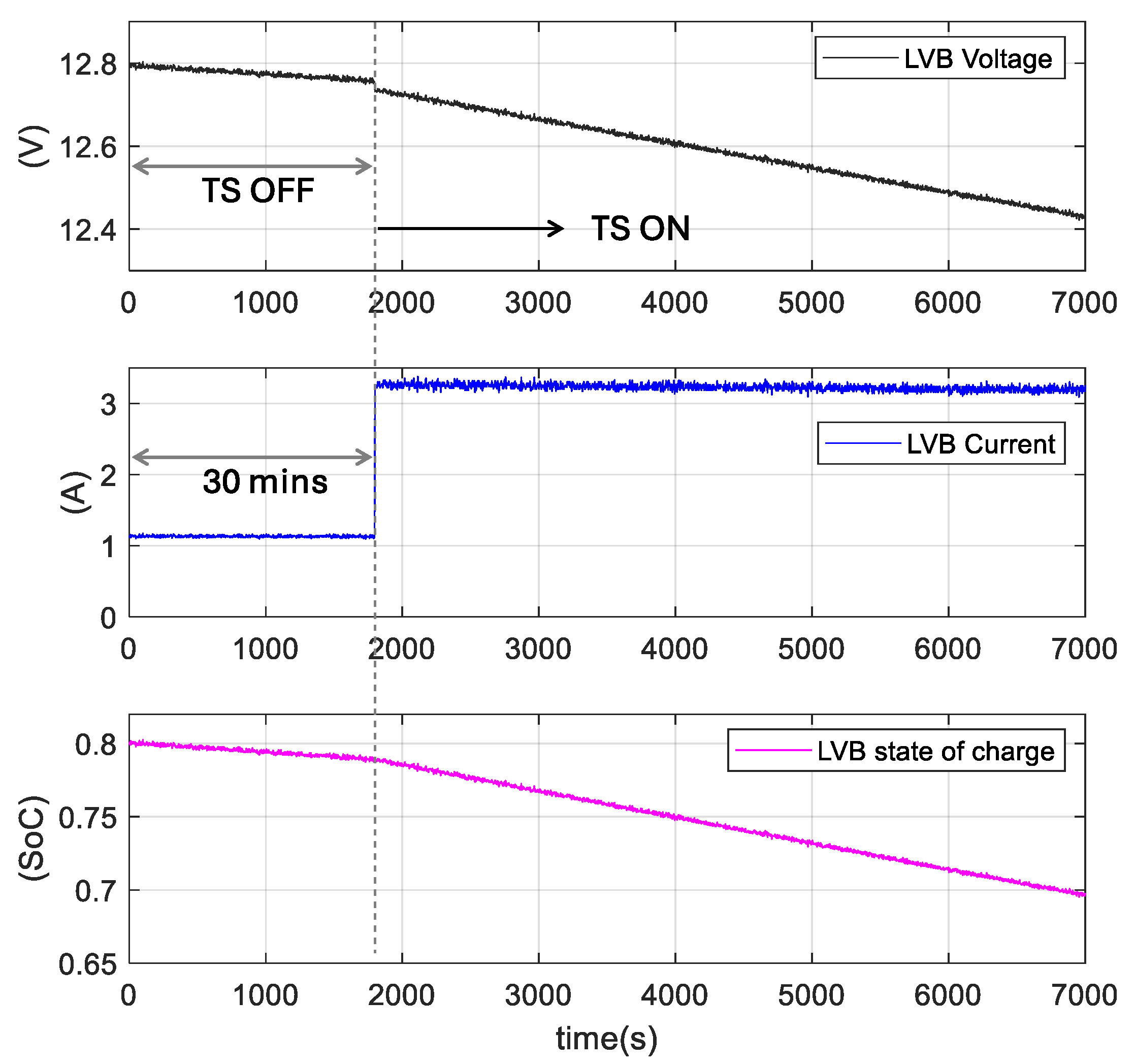

5.5. LVB

5.6. PDB

6. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| AMS | Accumulator Management System | LVB | Low Voltage Battery |

| APPS | Accelerator Pedal Position Sensor | LVCS | Low Voltage Control System |

| BMS | Battery Management System | LVMS | Low Voltage Master Switch |

| BOTS | Brake Over-Travel Switch | PCB | Printed Circuit Board |

| BSPD | Brake System Plausibility Device | PDAL | Pre-charge Discharge Activation Logic |

| BPPS | Brake Pedal Position Sensor | PDB | Power Distribution Board |

| EC | Electronic Circuit | PMSM | Permanent Magnet Synchronous Motor |

| ECU | Electronic Control Unit | SD | Shutdown |

| FSERC | Formula Student Electric Racing Car | TS | Tractive System |

| HV | High Voltage | TSMS | Tractive System Master Switch |

| HVD | High Voltage Disconnect | TSAL | Tractive System Active Light |

| IMD | Insulation Monitoring Device |

References

- Lai, N.Y.G.; Foo, W.C.; Tan, C.S.; Kang, M.S.; Kang, H.S.; Wong, K.H.; Yu, L.J.; Sun, X.; Tan, N.M.L. Understanding Learning Intention Complexities in Lean Manufacturing Training for Innovation on the Production Floor. J. Open Innov. Technol. Mark. Complex. 2022, 8, 110. [Google Scholar] [CrossRef]

- Tarle, N.; Kulkarni, R.; Desale, N.; Pawar, V. Design of a Battery Management System for Formula Student Electric Race Vehicle. In Proceedings of the 5th International Conference on Computing, Communication, Control and Automation (ICCUBEA), Pune, India, 19–21 September 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Carraro, E.; Degano, M.; Morandin, M.; Bianchi, N. Formula SAE electric competition: Electrical motor design. In Proceedings of the Electric Machines & Drives Conference, Chicago, IL, USA, 12–15 May 2013. [Google Scholar]

- Akop, M.Z.; Rosli, M.A.M.; Mansor, M.R.; Alkahari, M.R. Soft skills development of Engineering undergraduate students through Formula Varsity. In Proceedings of the International Conference on Engineering Education (ICEED), Kuala Lumpur, Malaysia, 7–8 December 2009; pp. 106–110. [Google Scholar] [CrossRef]

- ImechE Formula Student Rules. Available online: https://www.imeche.org/events/formula-student/team-information/rules (accessed on 31 July 2024).

- Biswas, A.; Yadav, R. Modeling and Simulation of Launch Control System for Formula Student Electric Vehicle. In Proceedings of the 2021 IEEE Transportation Electrification Conference (ITEC-India), New Delhi, India, 16–19 December 2021; pp. 1–7. [Google Scholar] [CrossRef]

- Porra, F. The Electronic Architecture of a Formula Student Electric Car. 2020. Available online: https://webthesis.biblio.polito.it/secure/14504/1/tesi.pdf (accessed on 31 July 2024).

- Pérez-Blanco, J. Design of the Systems of an Electric Powertrain for a Formula Student. 2020. Available online: https://dadun.unav.edu/bitstream/10171/59600/1/Perez%20Blanco_Jon_904869_IE.pdf (accessed on 31 July 2024).

- Oliveira, G.L.D. Desenvolvimento do Sistema Eletrônico de um Veículo do Tipo Formula Student Elétrico Baseado Nas Regras da Fórmula SAE. 2020. Available online: https://www.wisconsinracing.org/wp-content/uploads/2020/10/2018_ESF_Submission.pdf (accessed on 31 July 2024).

- Stanislav, T. Design of an Electric Powertrain for the Formula Student-Class Vehicle. 2019. Available online: http://hdl.handle.net/10467/82551 (accessed on 31 July 2024).

- Esfahani, F.N.; Darwish, A.; Ma, X. Design and Control of a Modular Integrated On-Board Battery Charger for EV Applications with Cell Balancing. Batteries 2024, 10, 17. [Google Scholar] [CrossRef]

- Esfahani, F.N.; Darwish, A. Regenerative Braking for EVs Using PMSM with CHB as Bidirectional Traction Converter. In Proceedings of the 2022 IEEE 16th International Conference on Compatibility, Power Electronics, and Power Engineering (CPE-POWERENG), Birmingham, UK, 29 June–1 July 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 1–7. [Google Scholar]

- Darwish, A.; Abdelsalam, A.; Massoud, A.; Ahmed, S. Single phase grid connected curent source inverter: Mitigation of oscillating power effect on the grid current. In Proceedings of the IET Conference on Renewable Power Generation (RPG 2011), Edinburgh, UK, 6–8 September 2011. [Google Scholar]

| Paramater | Value |

|---|---|

| Nominal DC-link voltage | 400 V |

| Motor | PMSM |

| No. of poles | 10 |

| Motor phase inductance | Ld = Lq = 0.28 mH |

| Motor phase resistance | Rs = 0.2 Ω |

| EV mass | 300 kg |

| Differential ratio | 1:4 |

| Wheel radius | r = 30 cm |

| Intentional | Actual | Results in Discrepancy | Voltage Measure >60 | Green Light | Red Light | ||||

|---|---|---|---|---|---|---|---|---|---|

| AIR 2 | AIR 1 | PRE | AIR 2 | AIR 1 | PRE | ||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ON | OFF |

| × | × | 0 | × | × | 1 | 1 | × | OFF | Latch |

| × | 0 | × | × | 1 | × | 1 | × | OFF | Latch |

| 0 | × | × | 1 | × | × | 1 | × | OFF | Latch |

| × | × | 1 | × | × | 0 | 1 | × | OFF | Latch |

| × | 1 | × | × | 0 | × | 1 | × | OFF | Latch |

| 1 | × | × | 0 | × | × | 1 | × | OFF | Latch |

| × | × | × | × | × | × | 0 | 1 | OFF | Flashing |

| 1 | × | × | 1 | × | × | 0 | × | OFF | Flashing |

| × | 1 | × | × | 1 | × | 0 | × | OFF | Flashing |

| × | × | 1 | × | × | 1 | 0 | × | OFF | Flashing |

| Component | Part No. | Description |

|---|---|---|

| U2, U3, U4, U5, U9 | MCP6541 | Push-Pull Output Sub-Microamp Comparators |

| U7 and U8 | SN54HC32 | 4-channel, 2-input 2–6 V OR gate |

| U6 | TC74HC08A | Quad 2-Input AND Gate |

| U11 | 4N35 | Optocoupler with Phototransistor Output |

| Q1 | PJA3404 | 30 V N-Channel Enhancement Mode MOSFET |

| K1 | 653-G5Q-1A-HADC12 | General Purpose PCB Power Relay Mini 1-pole 10A |

| Component | Part No. | Description |

|---|---|---|

| Q1, Q3, Q5,Q7 | MMBT3904VL | NPN switching transistor |

| Q2, Q4, Q6, Q8 | RSD160P05 | 45 V Drive P-channel MOSFET |

| Q9,Q10 | H6327 | P-Ch −20 V MOSFET −630 mA |

| K1 | 653-G5Q-1A-HADC12 | General Purpose PCB Relay Mini 1-pole 10 A |

| Component | Part No. | Description |

|---|---|---|

| K1 | OSA-SH-224DM | General Purpose PCB Relay |

| K2, K3 | 653-G5Q-1A-HADC12 | General Purpose Power Relay Mini 1-pole 10 A |

| Q1–Q5 | PJA3404 | 30 V N-Channel Enhancement Mode MOSFET |

| U1–U4 | MCP6541 | Push-Pull Output Sub-Microamp Comparators |

| U5 | LT1086CT-12 | Low Dropout Positive 12 V/5 V Regulator |

| U6 | TC74HC08A | QUAD 2-INPUT AND GATE |

| Component | Part No. | Description |

|---|---|---|

| U15, U18 | SFH617A | Phototransistor Output Optocoupler, Through Hole, 4-Pin DIP |

| K1, K2 | 653-G5Q-1A-HADC12 | General Purpose Power Relay Mini 1-pole 10 A |

| Q1, Q2, Q4, Q6, Q7, Q8 | PJA3404 | 30 V N-Channel Enhancement Mode MOSFET |

| Q3, Q5 | RSD160P05 | 45 V Drive P-channel MOSFET |

| U1–U3 | MCP6541 | Push-Pull Output Sub-Microamp Comparators |

| U13 | NCV7805BDTRKG | Linear Voltage Regulator 700 mA, 5 V |

| U6 | SN74HC08N | Dual 4-Input AND Gate |

| Component | Part No. | Description |

|---|---|---|

| K1 | 653-G5Q-1A-HADC12 | General Purpose Power Relay 1-pole 10 A |

| U1 | DHS250B15 | 400 V/12 V Isolated DC-DC Converter |

| U2 | 4N35 | Phototransistor Optocoupler |

| Component | Part No. | Description |

|---|---|---|

| U1 | F303RE | STM32F303RET6 microcontroller 3.6 V—72 MHz—51 GPIO |

| U2 | MCP2551-I/SN | CAN Transceiver 1Mbps, 8-Pin |

| U3, U4, U5, U6 | EL817 | 4 PIN DIP PHOTOTRANSISTOR PHOTOCOUPLER |

| U7 | TC74HC08A | Quad 2-Input AND Gate |

| Q1, Q2 | PJA3404 | 30 V N-Channel Enhancement Mode MOSFET |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Badawy, A.D.; Sfranciog, S.; Hiranoyama, J.T.; Ibarrola, J.L.; Engstrom, J.; Mikhail, K.; Hunt, W.; Hartley, J.; Nasr Esfahani, F.; Dexter, A. Low-Voltage Control Circuits of Formula Student Electric Racing Cars. Hardware 2024, 2, 190-222. https://doi.org/10.3390/hardware2030010

Badawy AD, Sfranciog S, Hiranoyama JT, Ibarrola JL, Engstrom J, Mikhail K, Hunt W, Hartley J, Nasr Esfahani F, Dexter A. Low-Voltage Control Circuits of Formula Student Electric Racing Cars. Hardware. 2024; 2(3):190-222. https://doi.org/10.3390/hardware2030010

Chicago/Turabian StyleBadawy, Ahmed Darwish, Stefan Sfranciog, Jorge Takeshi Hiranoyama, Jaime Lacasta Ibarrola, James Engstrom, Kirollos Mikhail, William Hunt, Joshua Hartley, Fatemeh Nasr Esfahani, and Amos Dexter. 2024. "Low-Voltage Control Circuits of Formula Student Electric Racing Cars" Hardware 2, no. 3: 190-222. https://doi.org/10.3390/hardware2030010

APA StyleBadawy, A. D., Sfranciog, S., Hiranoyama, J. T., Ibarrola, J. L., Engstrom, J., Mikhail, K., Hunt, W., Hartley, J., Nasr Esfahani, F., & Dexter, A. (2024). Low-Voltage Control Circuits of Formula Student Electric Racing Cars. Hardware, 2(3), 190-222. https://doi.org/10.3390/hardware2030010