High-Efficiency Reconfigurable CMOS RF-to-DC Converter System for Ultra-Low-Power Wireless Sensor Nodes with Efficient MPPT Circuitry

Abstract

1. Introduction

- Development of a system-level strategy for correctly biasing the operating point of the RF-to-DC converter, which is a novel concept not commonly found in existing architectures. This strategy focuses on optimizing the output voltage of the rectifier by properly biasing the system, rather than just the rectifier itself. This approach provides a more effective way to maximize power conversion efficiency with no impact on the power sensitivity performance, with negligible impact on circuit complexity and effective die area. The proposed method and guidelines provide a practical solution for achieving optimal performance in RF-to-DC converter architectures.

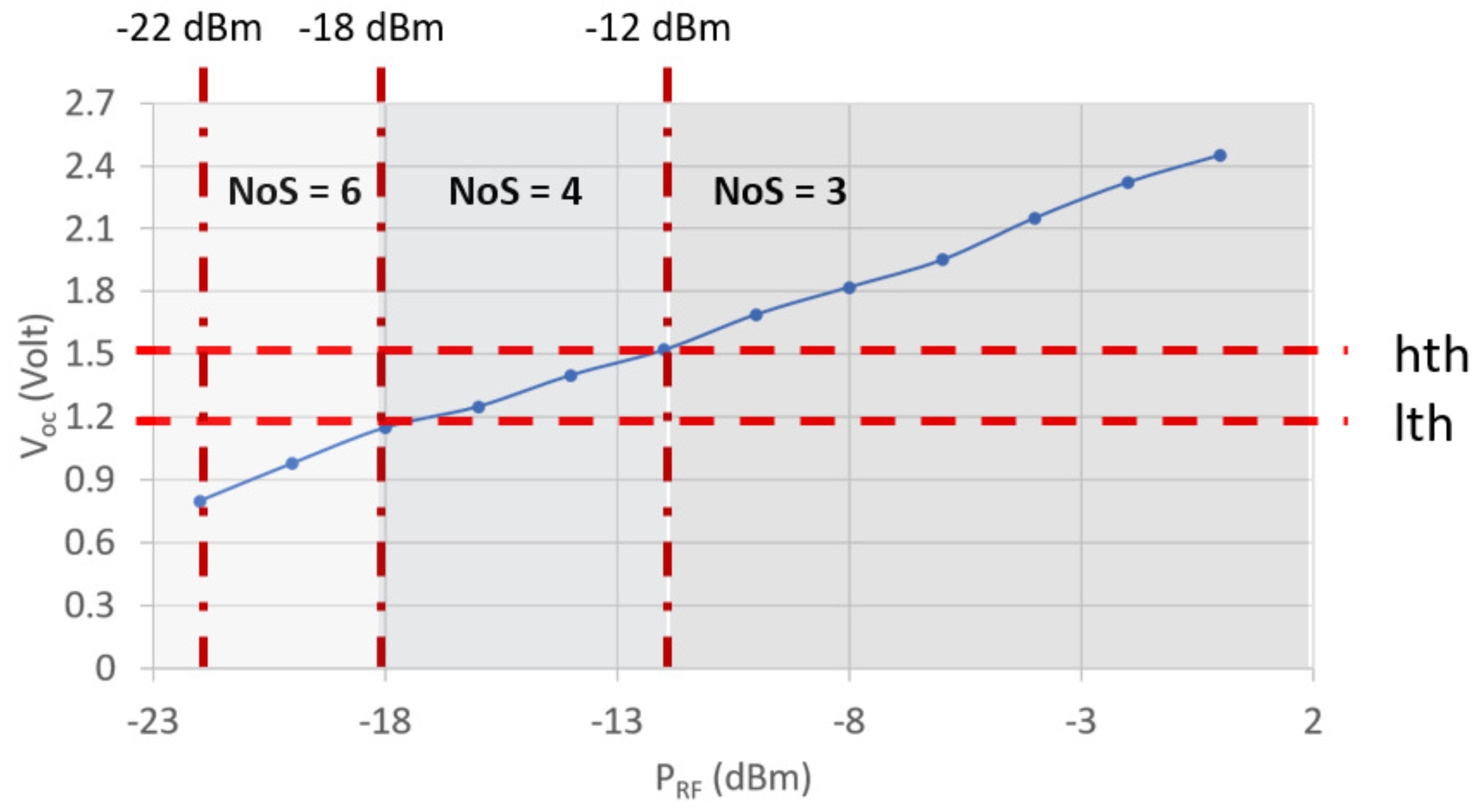

- Implementation of an innovative ultra-low power voltage measurement technique that uses a simple rectifier to indirectly monitor input-received power, which is a novel concept not commonly found in existing RF-to-DC converter architectures and provides a more accurate and efficient way to optimize power conversion efficiency. This technique uses a very small silicon area, making it a cost-effective solution for practical applications.

- Combination of reconfigurable voltage rectifiers with indirect monitoring of input-received power to create a cost-effective and silicon area-effective MPPT system that increases the PCE of the system, regardless of the voltage rectifier topology. The proposed MPPT system uses an ultra-low power circuit with minimal impact in terms of extra power consumption and effective die area increase, making it a practical solution for energy harvesting applications.

2. Materials and Methods

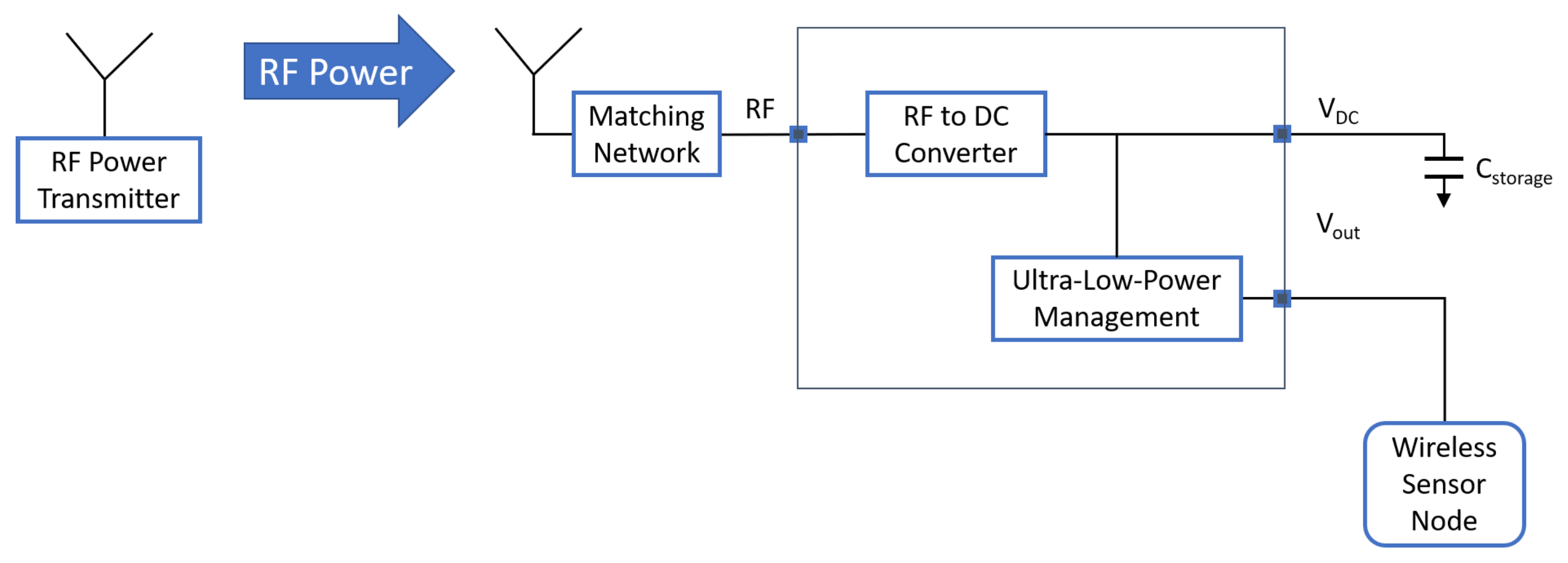

- The RF power transmitter is responsible for transmitting a maximum RF power in compliance with regulations that ensure human health is not compromised.

- The Matching Network (MN) matches the impedance of the antenna with that of the RF-to-DC converter to optimize the power transfer.

- The RF-to-DC converter rectifies and amplifies the input voltage.

- The storage capacitor stores the harvested energy.

- The ultra-low-power management system regulates and controls the voltage supplied to the load, which is typically a wireless sensor node.

- Free-space WPT.

- Unity gain for both transmitter and receiver antennas.

- Transmitted power = 27 dBm.

- Frequency = 868 MHz.

- = −22 dBm = 6.3

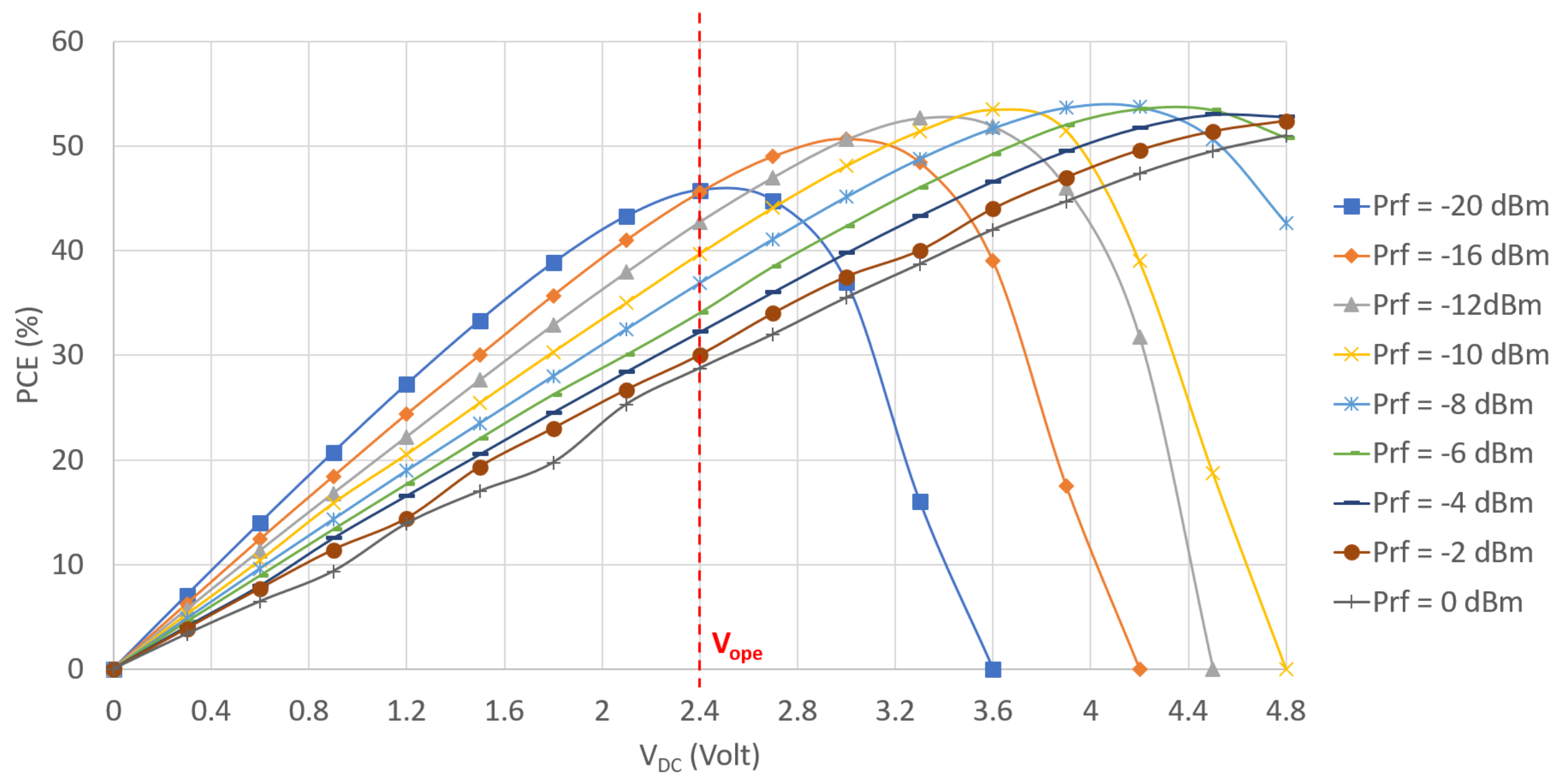

- Output voltage = 4.8 V (Open Circuit condition).

- Output Voltage = 2.4 V (at = 1 ).

- Min Output Power = 2.4 = −26 dBm.

3. Results

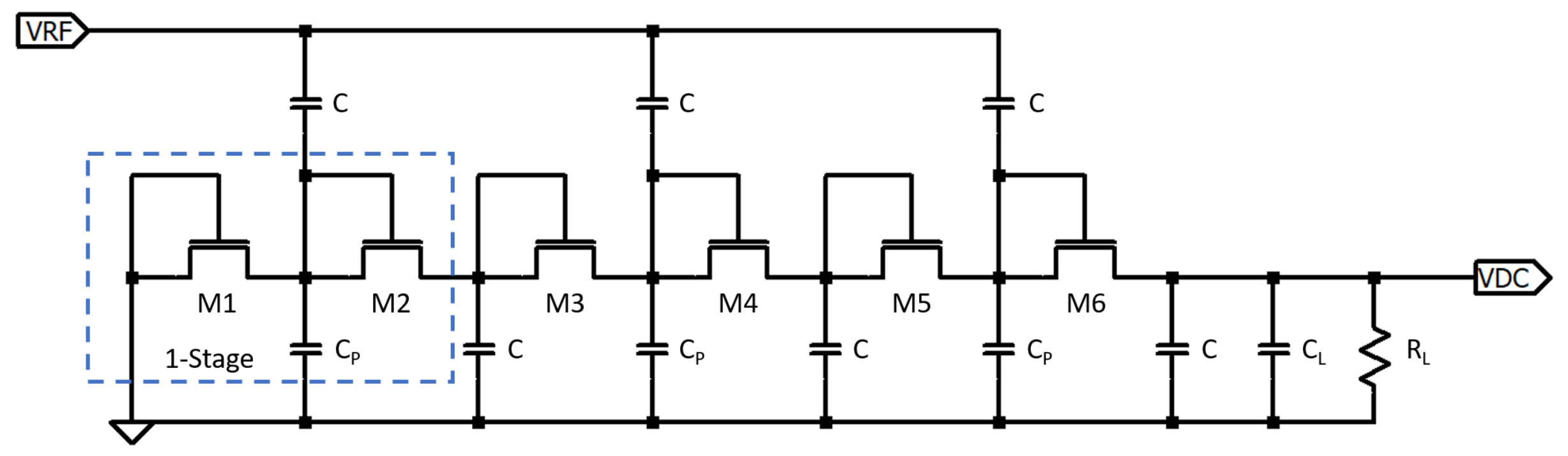

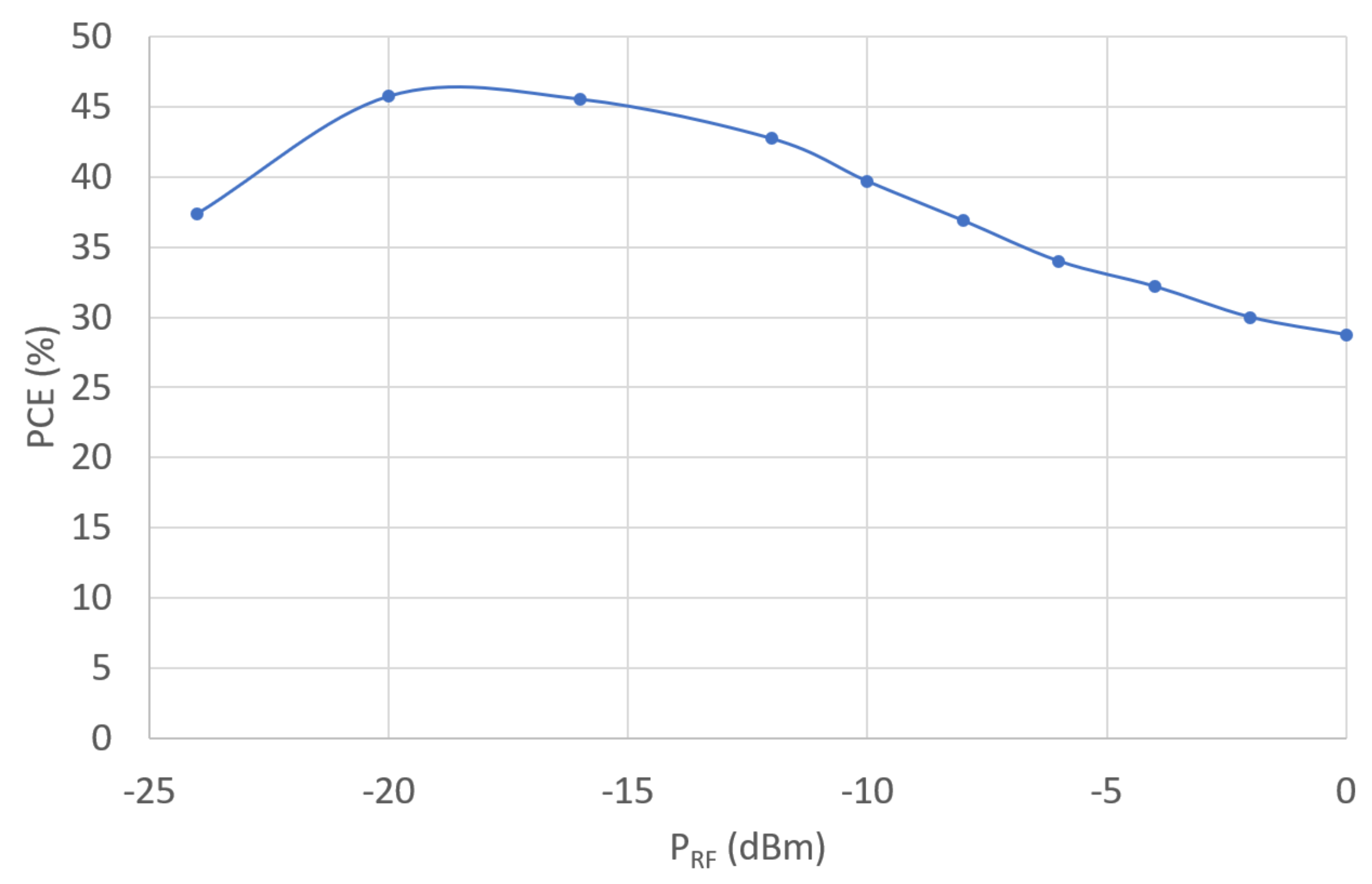

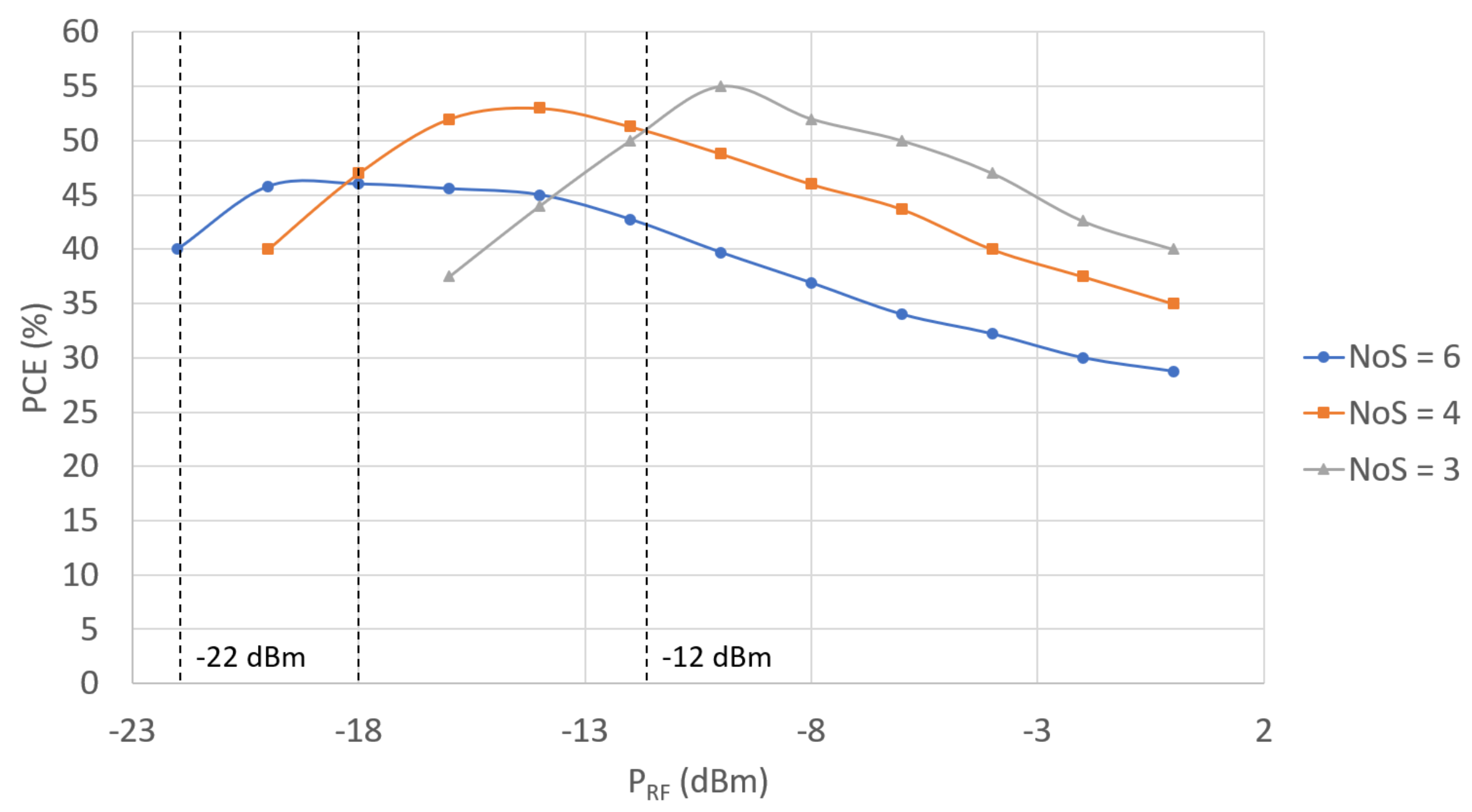

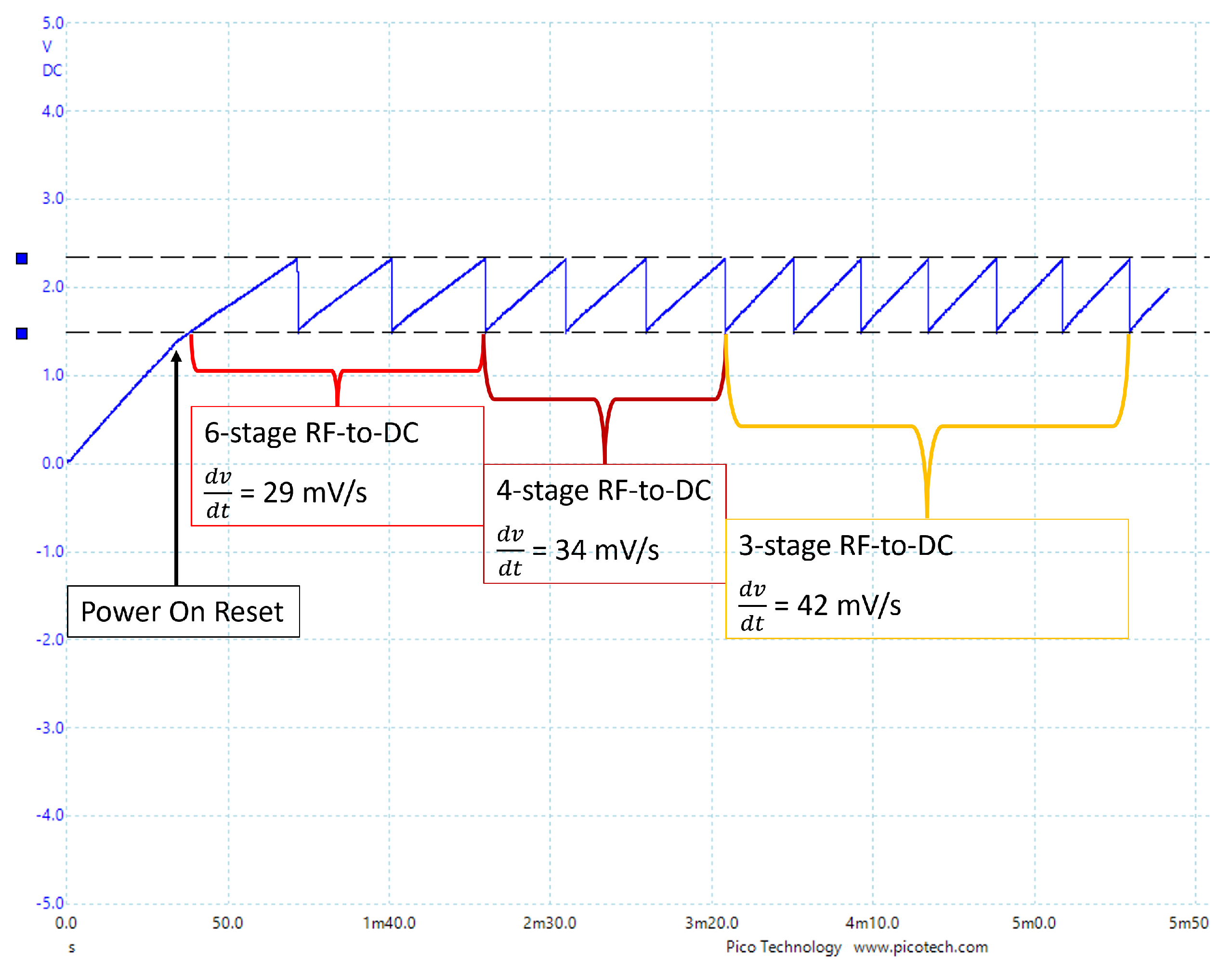

3.1. MPPT Technique with Reconfigurable RF-to-DC Converter

3.2. MPPT System Architecture: System Design, Experimental Measurements and Validation

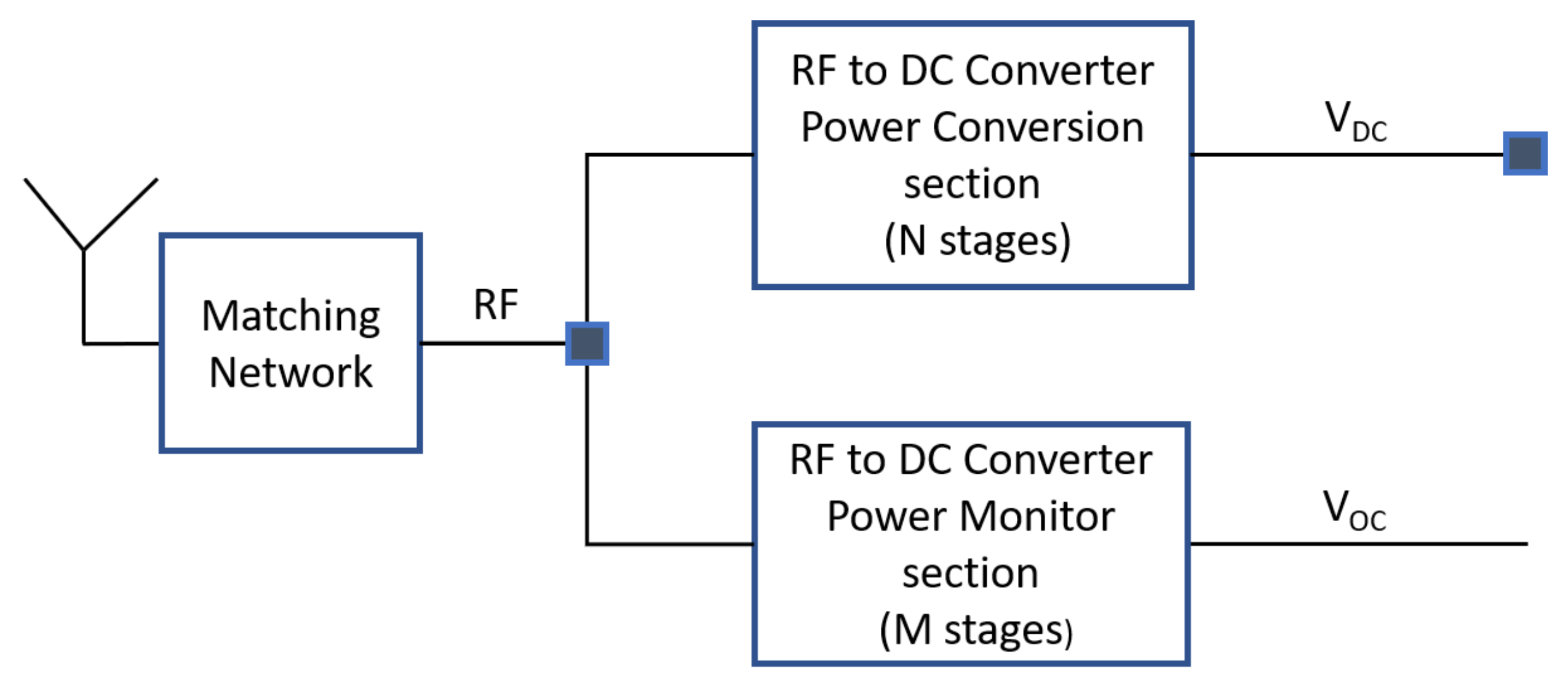

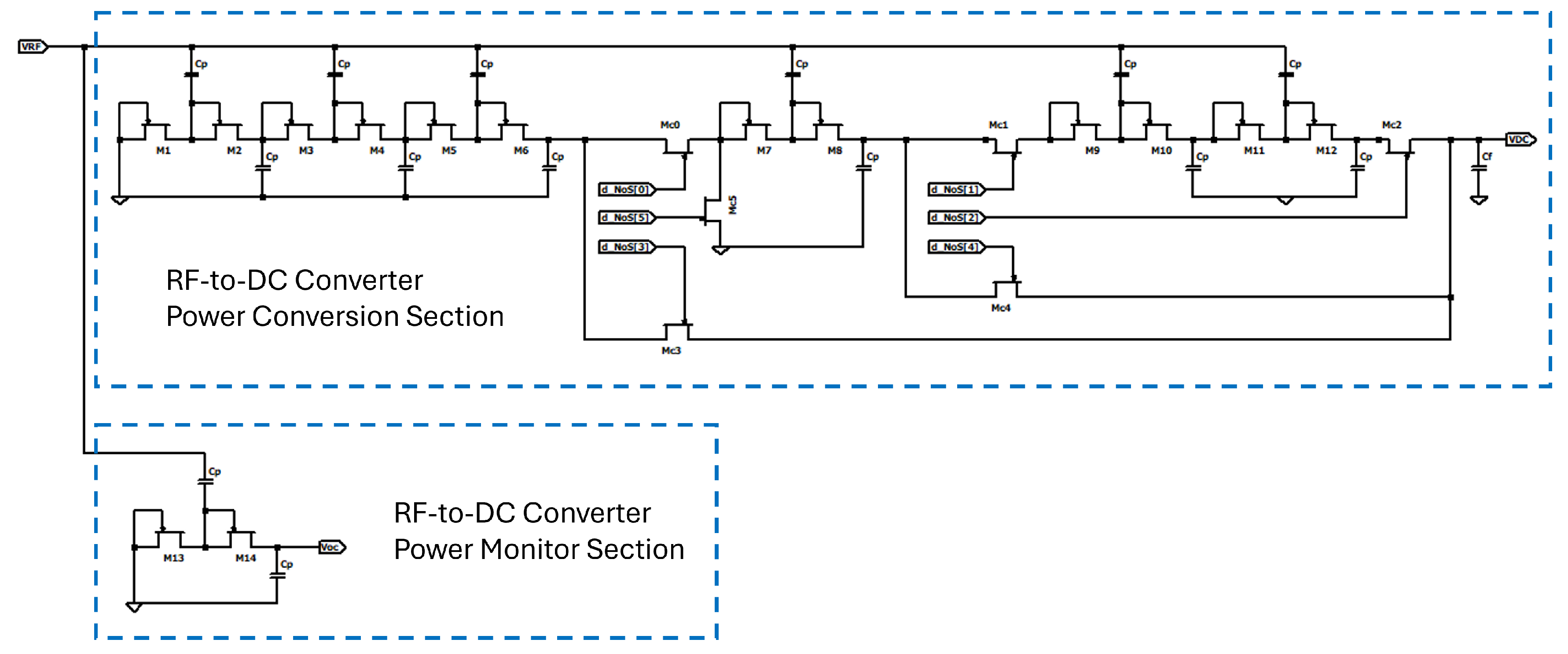

3.3. Dual RF-to-DC Converter for Power Monitoring and Power Conversion

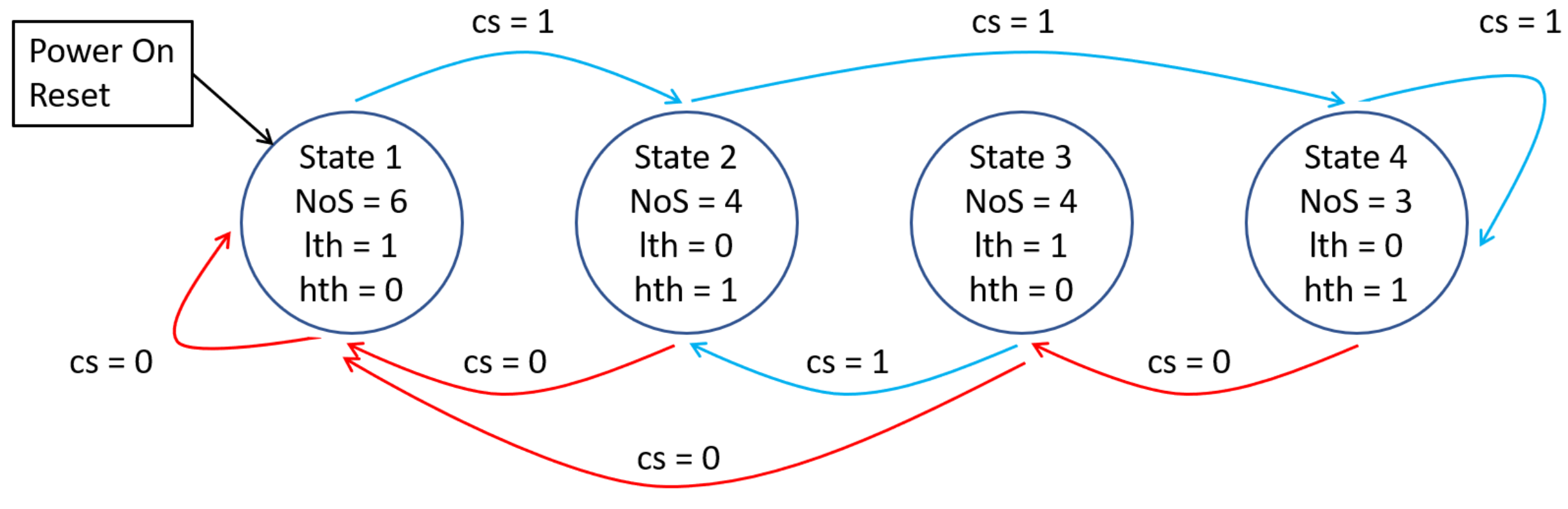

3.4. Finite State Machine

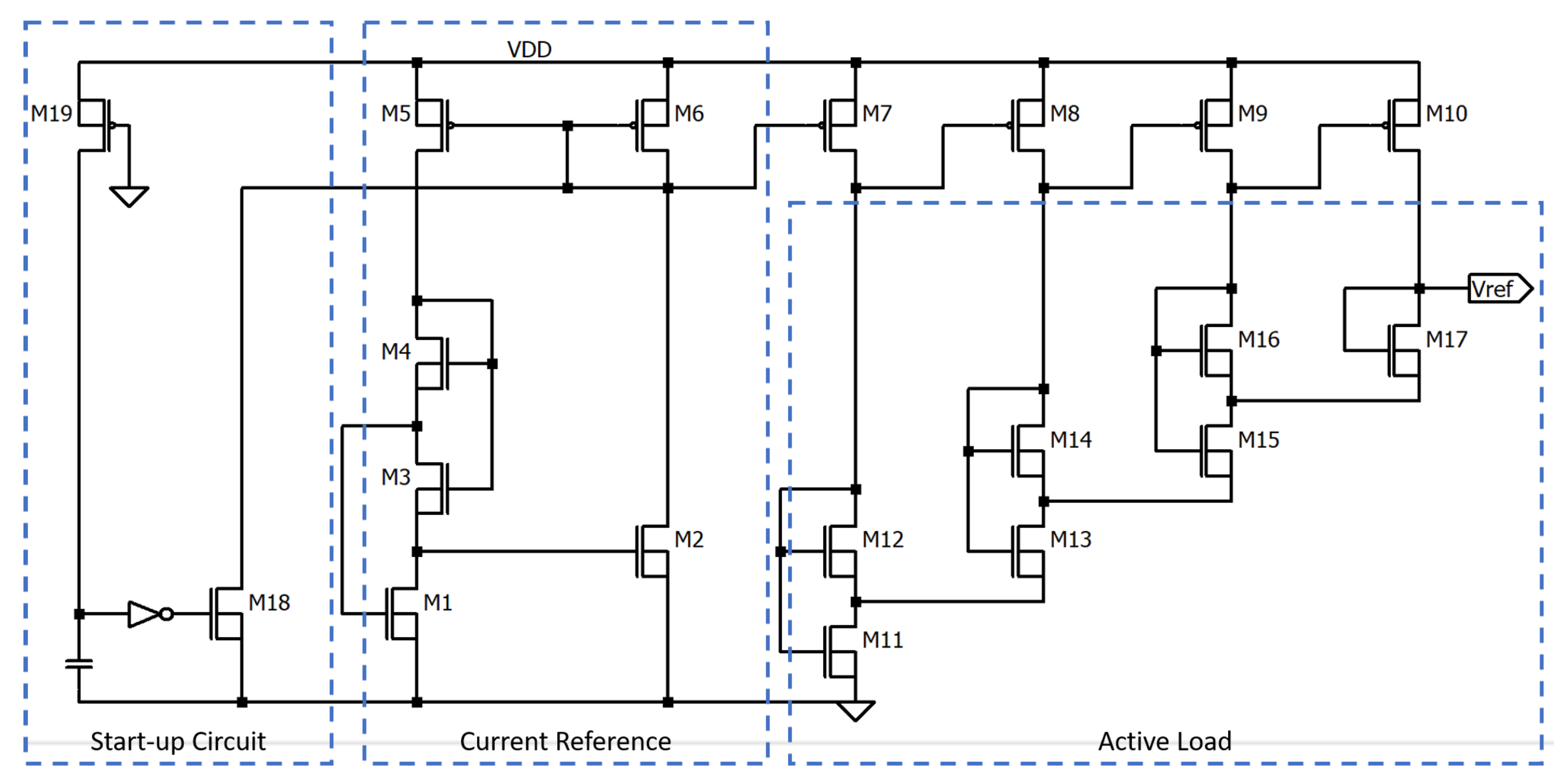

3.5. Voltage Reference

- The start-up circuit consists of the transistors M18, M19, and an inverter. This circuit prevents the operation at zero current of the self-biasing circuit.

- The triode-based Widlar current reference implements an accurate temperature compensation with temperature coefficient of 100 ppm/°C. This circuit consists of the transistors M1–M6. Functionally, it is a current reference that provides a reference current to the active load.

- The active load consists of transistors M11–M17 and provides the reference voltage, of ≈ 800 mV.

- is the subthreshold slope factor;

- = is the thermal voltage;

- is aspect ratio of transistor ;

- is width of transistors ;

- is length of transistors ;

- is the gate-source voltage of transistor ;

- is the carrier mobility of the n-type transistor;

- is the gate-oxide capacitance;

- is threshold voltage of the n-type transistor;

- is the Boltzman constant;

- T is the absolute temperature;

- q is the elementary charge.

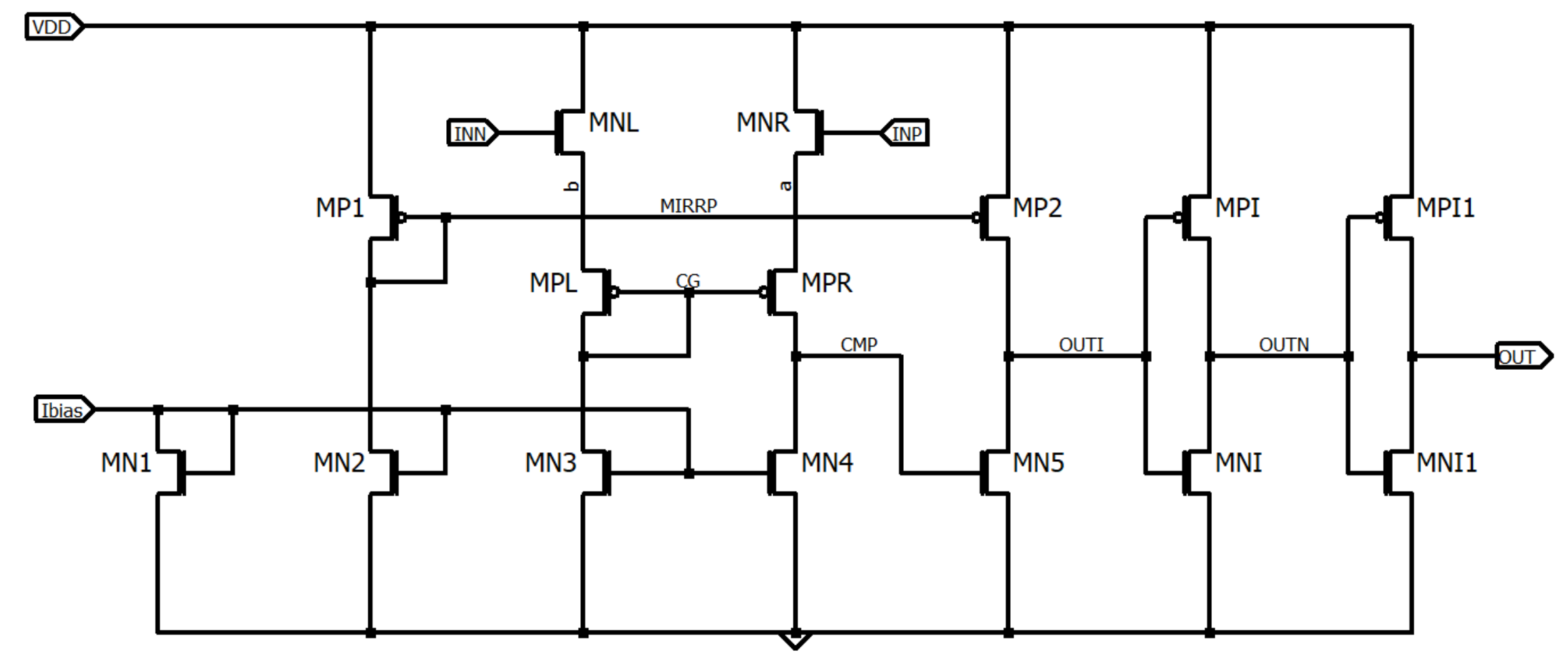

3.6. Voltage Comparator

3.7. Power Consumption Distribution

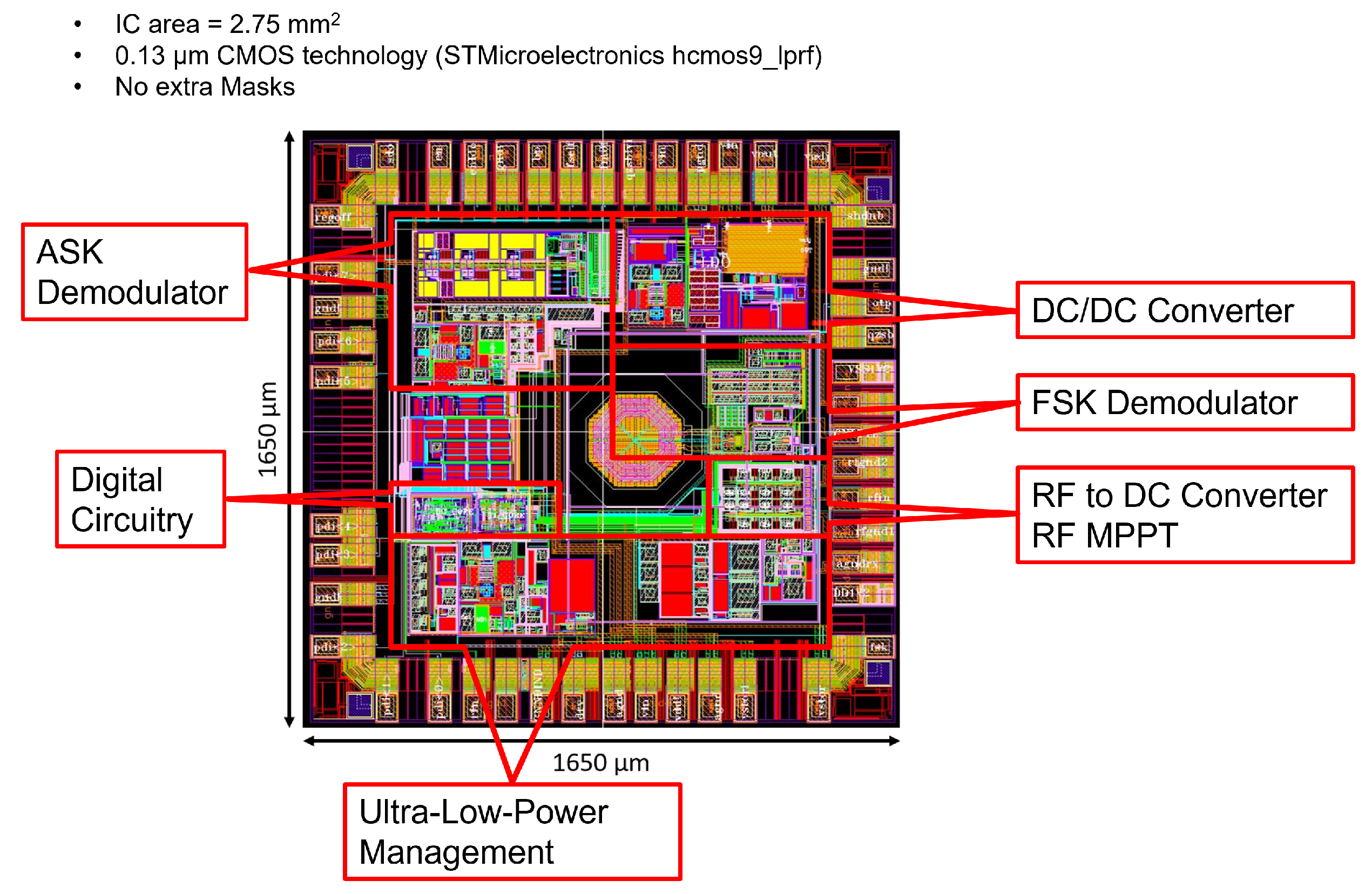

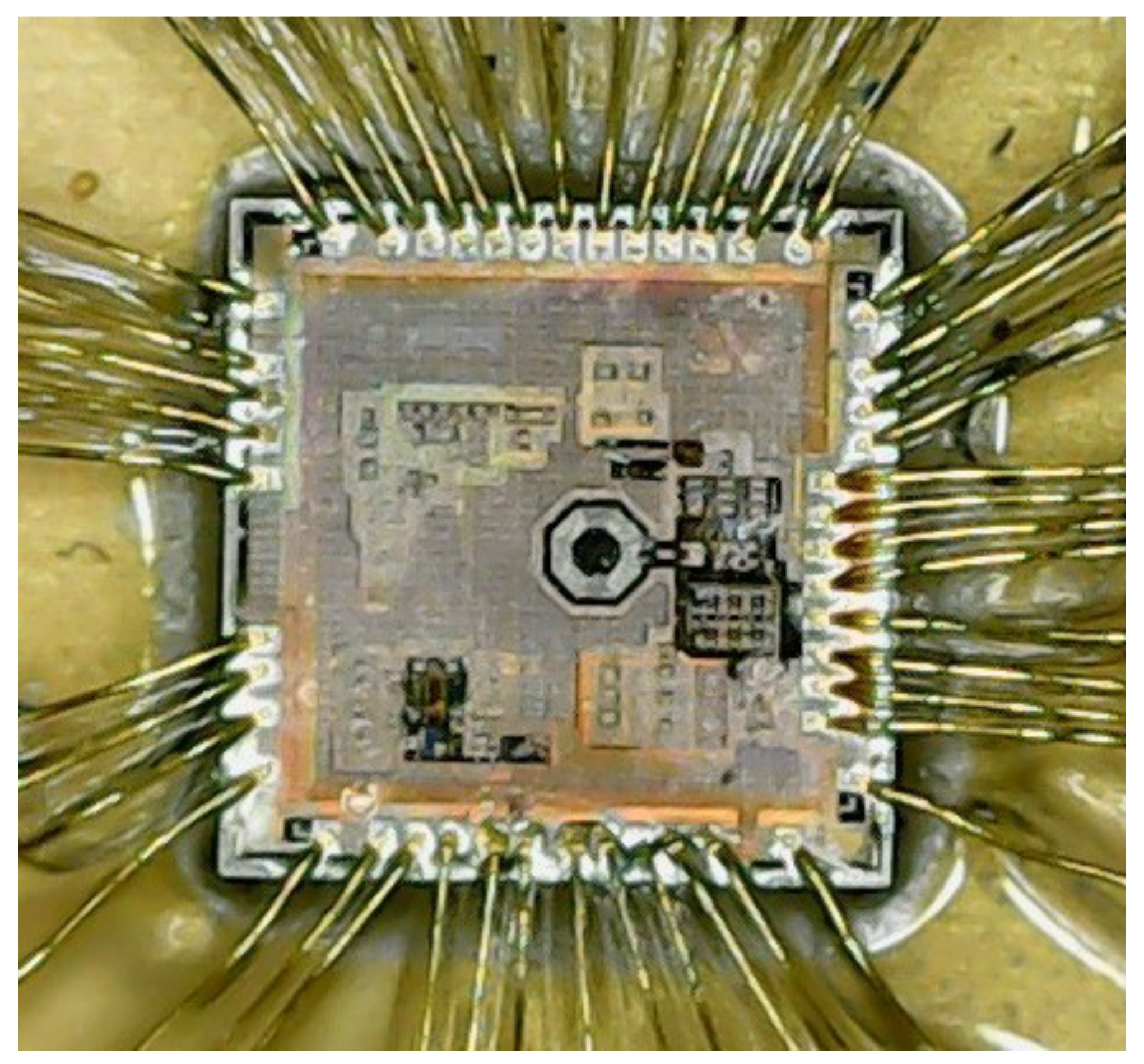

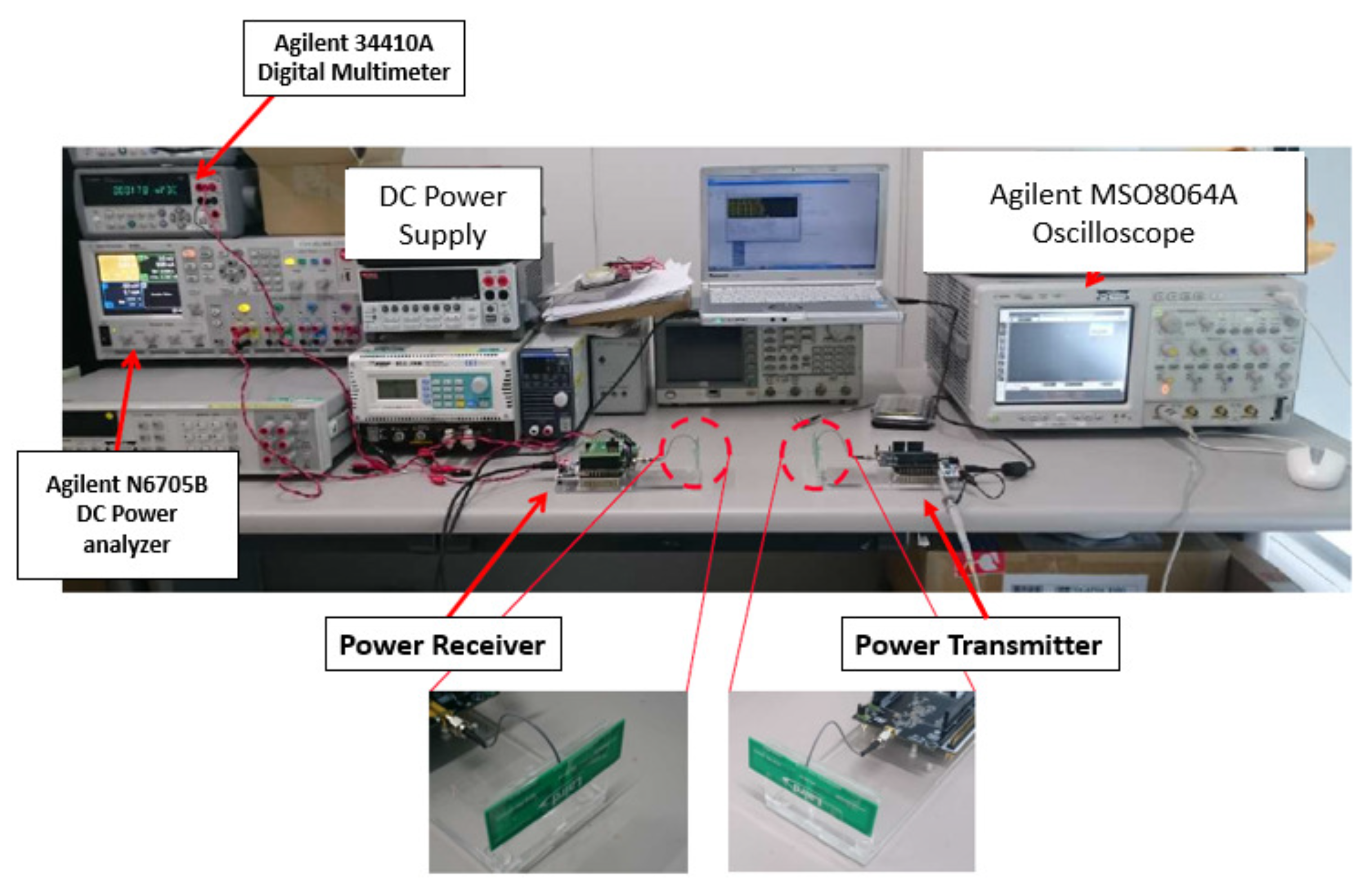

3.8. Measurement Setup and Results

4. Discussion

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| WSN | Wireless Sensor Network |

| WPT | Wireless Power Transfer |

| EH | Energy Harvesting |

| RF | Radio Frequency |

| PCE | Power Conversion Efficiency |

| MPPT | Maximum Power Point Tracking |

| MN | Matching Network |

| SoC | System on Chip |

| FSM | Finite State Machine |

| POR | Power On Reset |

| ASK | Amplitude Shift Keying |

| FSK | Frequency Shift Keying |

| FSPL | Free Space Path Loss |

References

- Habibzadeh, H.; Qin, Z.; Soyata, T.; Kantarci, B. Large-scale distributed dedicated-and non-dedicated smart city sensing systems. IEEE Sens. J. 2017, 17, 7649–7658. [Google Scholar] [CrossRef]

- Martinez, B.; Monton, M.; Vilajosana, I.; Prades, J.D. The power of models: Modeling power consumption for IoT devices. IEEE Sens. J. 2015, 15, 5777–5789. [Google Scholar] [CrossRef]

- La Rosa, R.; Livreri, P.; Trigona, C.; Di Donato, L.; Sorbello, G. Strategies and techniques for powering wireless sensor nodes through energy harvesting and wireless power transfer. Sensors 2019, 19, 2660. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Vyas, R.; Bito, J.; Niotaki, K.; Collado, A.; Georgiadis, A.; Tentzeris, M.M. Ambient RF energy-harvesting technologies for self-sustainable standalone wireless sensor platforms. Proc. IEEE 2014, 102, 1649–1666. [Google Scholar] [CrossRef]

- Dekimpe, R.; Xu, P.; Schramme, M.; Gérard, P.; Flandre, D.; Bol, D. A battery-less BLE smart sensor for room occupancy tracking supplied by 2.45-GHz wireless power transfer. Integration 2019, 67, 8–18. [Google Scholar] [CrossRef]

- La Rosa, R.; Dehollain, C.; Livreri, P. Advanced Monitoring Systems Based on Battery-Less Asset Tracking Modules Energized through RF Wireless Power Transfer. Sensors 2020, 20, 3020. [Google Scholar] [CrossRef]

- Hashemi, S.S.; Sawan, M.; Savaria, Y. A high-efficiency low-voltage CMOS rectifier for harvesting energy in implantable devices. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 326–335. [Google Scholar] [CrossRef]

- Hsieh, P.H.; Chou, C.H.; Chiang, T. An RF energy harvester with 44.1% PCE at input available power of −12 dBm. IEEE Trans. Circuits Syst. Regul. Pap. 2015, 62, 1528–1537. [Google Scholar] [CrossRef]

- Stoopman, M.; Keyrouz, S.; Visser, H.J.; Philips, K.; Serdijn, W.A. Co-design of a CMOS rectifier and small loop antenna for highly sensitive RF energy harvesters. IEEE J. Solid-State Circuits 2014, 49, 622–634. [Google Scholar] [CrossRef]

- Lu, Y.; Dai, H.; Huang, M.; Law, M.K.; Sin, S.W.; Seng-Pan, U.; Martins, R.P. A wide input range dual-path CMOS rectifier for RF energy harvesting. IEEE Trans. Circuits Syst. II Express Briefs 2016, 64, 166–170. [Google Scholar] [CrossRef]

- Saffari, P.; Basaligheh, A.; Moez, K. An RF-to-DC rectifier with high efficiency over wide input power range for RF energy harvesting applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 4862–4875. [Google Scholar] [CrossRef]

- Papotto, G.; Carrara, F.; Palmisano, G. A 90-nm CMOS threshold-compensated RF energy harvester. IEEE J. Solid-State Circuits 2011, 46, 1985–1997. [Google Scholar] [CrossRef]

- Noghabaei, S.M.; Radin, R.L.; Savaria, Y.; Sawan, M. A High-Sensitivity Wide Input-Power-Range Ultra-Low-Power RF Energy Harvester for IoT Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 69, 440–451. [Google Scholar] [CrossRef]

- Choo, A.; Ramiah, H.; Churchill, K.K.P.; Chen, Y.; Mekhilef, S.; Mak, P.I.; Martins, R.P. A High-Performance Dual-Topology CMOS Rectifier With 19.5-dB Power Dynamic Range for RF-Based Hybrid Energy Harvesting. IEEE Trans. Very Large Scale Integr. (VLSI) Systems 2023, 31, 1253–1257. [Google Scholar] [CrossRef]

- La Rosa, R.; Dehollain, C.; Pellitteri, F.; Miceli, R.; Livreri, P. An RF Wireless Power Transfer system to power battery-free devices for asset tracking. In Proceedings of the 26th IEEE International Conference on Electronics Circuits and Systems (ICECS), Genoa, Italy, 27–29 November 2019; pp. 1–4. [Google Scholar]

- Abouzied, M.A.; Ravichandran, K.; Sánchez-Sinencio, E. A fully integrated reconfigurable self-startup RF energy-harvesting system with storage capability. IEEE J. Solid-State Circuits 2016, 52, 704–719. [Google Scholar] [CrossRef]

- Kim, S.Y.; Abbasizadeh, H.; Rikan, B.S.; Oh, S.J.; Jang, B.G.; Park, Y.J.; Khan, D.; Nga, T.T.K.; Kang, K.T.; Pu, Y.G.; et al. A −20 to 30 dBm input power range wireless power system with a MPPT-based reconfigurable 48% efficient RF energy harvester and 82% efficient A4WP wireless power receiver with open-loop delay compensation. IEEE Trans. Power Electron. 2018, 34, 6803–6817. [Google Scholar] [CrossRef]

- Khan, D.; Oh, S.J.; Shehzad, K.; Basim, M.; Verma, D.; Pu, Y.G.; Lee, M.; Hwang, K.C.; Yang, Y.; Lee, K.Y. An efficient reconfigurable RF-DC converter with wide input power range for RF energy harvesting. IEEE Access 2020, 8, 79310–79318. [Google Scholar] [CrossRef]

- Zeng, Z.; Estrada-López, J.J.; Abouzied, M.A.; Sánchez-Sinencio, E. A reconfigurable rectifier with optimal loading point determination for RF energy harvesting from −22 dBm to −2 dBm. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 87–91. [Google Scholar] [CrossRef]

- Saini, G.; Somappa, L.; Baghini, M.S. A 500-nW-to-1-mW input power inductive boost converter with MPPT for RF energy harvesting system. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 5261–5271. [Google Scholar] [CrossRef]

- Choo, A.; Ramiah, H.; Churchill, K.K.P.; Chen, Y.; Mekhilef, S.; Mak, P.I.; Martins, R.P. A Reconfigurable CMOS Rectifier With 14-dB Power Dynamic Range Achieving> 36-dB/mm 2 FoM for RF-Based Hybrid Energy Harvesting. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022, 30, 1533–1537. [Google Scholar] [CrossRef]

- Oguey, H.J.; Aebischer, D. CMOS current reference without resistance. IEEE J. Solid-State Circuits 1997, 32, 1132–1135. [Google Scholar] [CrossRef]

- Ueno, K.; Hirose, T.; Asai, T.; Amemiya, Y. A 300 nW, 15 ppm/°C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. IEEE J. Solid-State Circuits 2009, 44, 2047–2054. [Google Scholar] [CrossRef]

- Parisi, A.; Finocchiaro, A.; Papotto, G.; Palmisano, G. Nano-power CMOS voltage reference for RF-powered systems. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1425–1429. [Google Scholar] [CrossRef]

- Matsumoto, K.; Hirose, T.; Asano, H.; Tsuji, Y.; Nakazawa, Y.; Kuroki, N.; Numa, M. An ultra-low power active diode using a hysteresis common gate comparator for low-voltage and low-power energy harvesting systems. In Proceedings of the 2018 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Verona, Italy, 8–10 October 2018; pp. 196–200. [Google Scholar]

- Guerra, R.; Finocchiaro, A.; Papotto, G.; Messina, B.; Grasso, L.; La Rosa, R.; Zoppi, G.; Notarangelo, G.; Palmisano, G. An RF-powered FSK/ASK receiver for remotely controlled systems. In Proceedings of the Radio Frequency Integrated Circuits Symposium (RFIC), 2016 IEEE, San Francisco, CA, USA, 22–24 May 2016; pp. 226–229. [Google Scholar]

- STMicroelectronics. SPIRIT1 Low data rate, low power sub-1GHz transceiver. In Proceedings of the Datasheet; STMicroelectronics: Geneva, Switzerland, 2021; Available online: https://www.st.com/en/wireless-connectivity/spirit1.html (accessed on 15 October 2022).

- lairdtech. Available online: https://www.lairdtech.com/datasheet-revie-pro-0618pdf (accessed on 3 March 2024).

| d_NoS[5:0] | Topology | |

|---|---|---|

| 000000 | 6 | 6-stage rectifier |

| 011010 | 4 | 4-stage rectifier |

| 101101 | 3 | 3-stage rectifier |

| Voltage Reference | Voltage Comparator | Power Monitoring RF-to-DC Converter | |

|---|---|---|---|

| Power Consumption | 100 nW | 40 nW | 50 nW |

| Relative Power Consumption to = 6 µW (−22 dBm) | 1.7% | 0.66% | 1% |

| Relative Power Consumption to = 2.4 µW | 4.2% | 1.7% | 2% |

| Reference | [18] | [13] | [21] | [14] | This Work | This Work |

|---|---|---|---|---|---|---|

| CMOS Technology | 180 nm | 130 nm | 130 nm | 130 nm | 130 nm | 130 nm |

| Operating Frequency (MHz) | 1000 | 915 | 900 | 900 | 868 | 868 |

| PCE max (%) | 33 @ −8 dBm | 42.4 @ −16 dBm | 34.93 @ −10 dBm | 78.4 @ −16 dBm | 55 @ −12.5 dBm | 45 @ −20 dBm |

| Sensitivity (dBm) | −20.2 | −25.5 | −21.7 | −18 | −22 | −22 |

| Reconfigurable RF-to-DC Rectifier | Yes | No | Yes | No | Yes | No |

| MPPT | No | No | No | No | Yes | No |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

La Rosa, R.; Demarchi, D.; Carrara, S.; Dehollain, C. High-Efficiency Reconfigurable CMOS RF-to-DC Converter System for Ultra-Low-Power Wireless Sensor Nodes with Efficient MPPT Circuitry. Chips 2024, 3, 49-68. https://doi.org/10.3390/chips3010003

La Rosa R, Demarchi D, Carrara S, Dehollain C. High-Efficiency Reconfigurable CMOS RF-to-DC Converter System for Ultra-Low-Power Wireless Sensor Nodes with Efficient MPPT Circuitry. Chips. 2024; 3(1):49-68. https://doi.org/10.3390/chips3010003

Chicago/Turabian StyleLa Rosa, Roberto, Danilo Demarchi, Sandro Carrara, and Catherine Dehollain. 2024. "High-Efficiency Reconfigurable CMOS RF-to-DC Converter System for Ultra-Low-Power Wireless Sensor Nodes with Efficient MPPT Circuitry" Chips 3, no. 1: 49-68. https://doi.org/10.3390/chips3010003

APA StyleLa Rosa, R., Demarchi, D., Carrara, S., & Dehollain, C. (2024). High-Efficiency Reconfigurable CMOS RF-to-DC Converter System for Ultra-Low-Power Wireless Sensor Nodes with Efficient MPPT Circuitry. Chips, 3(1), 49-68. https://doi.org/10.3390/chips3010003