A Low-Power, Fast Transient Response Low-Dropout Regulator Featuring Bi-Directional Level Shifting for Sensor Applications †

Abstract

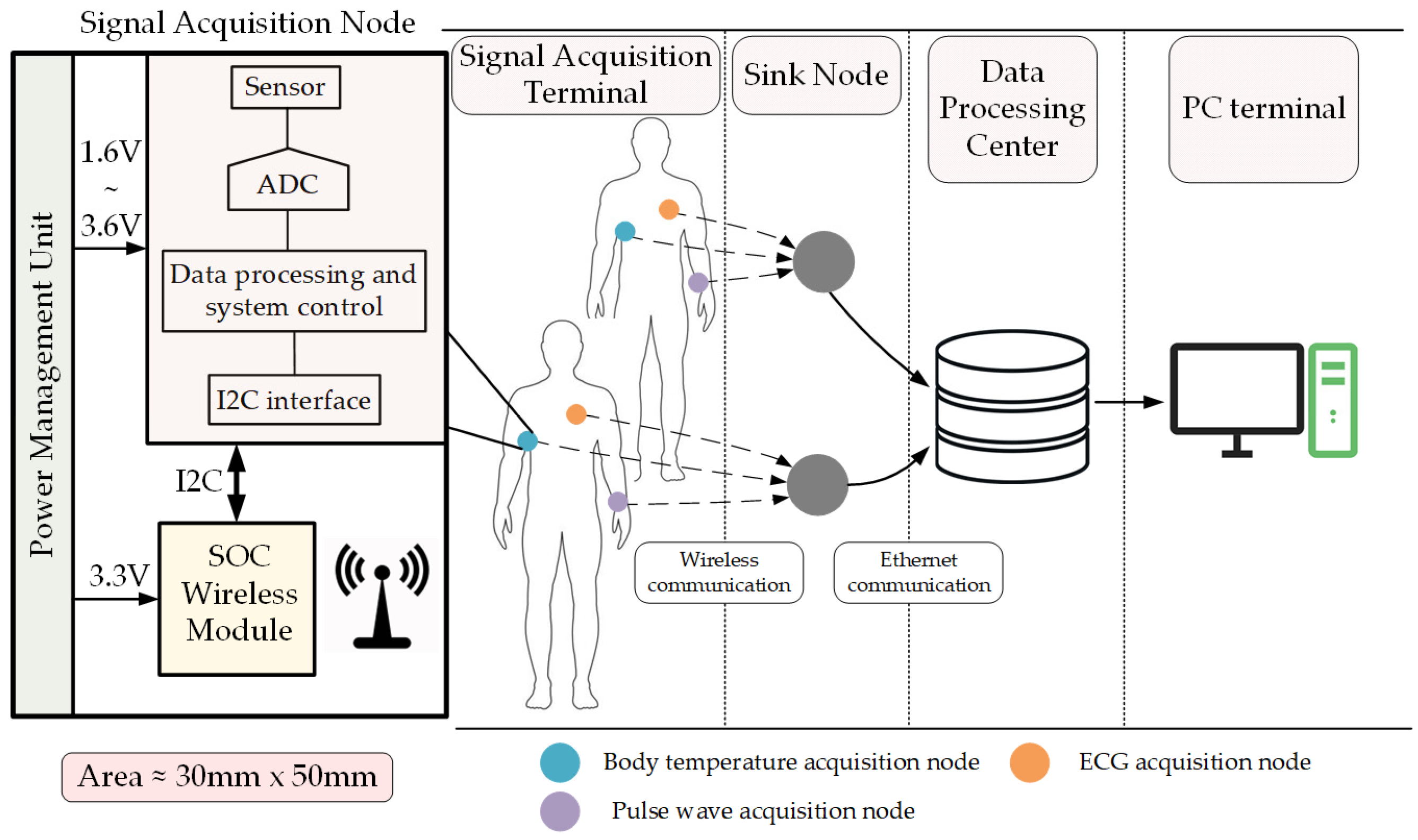

1. Introduction

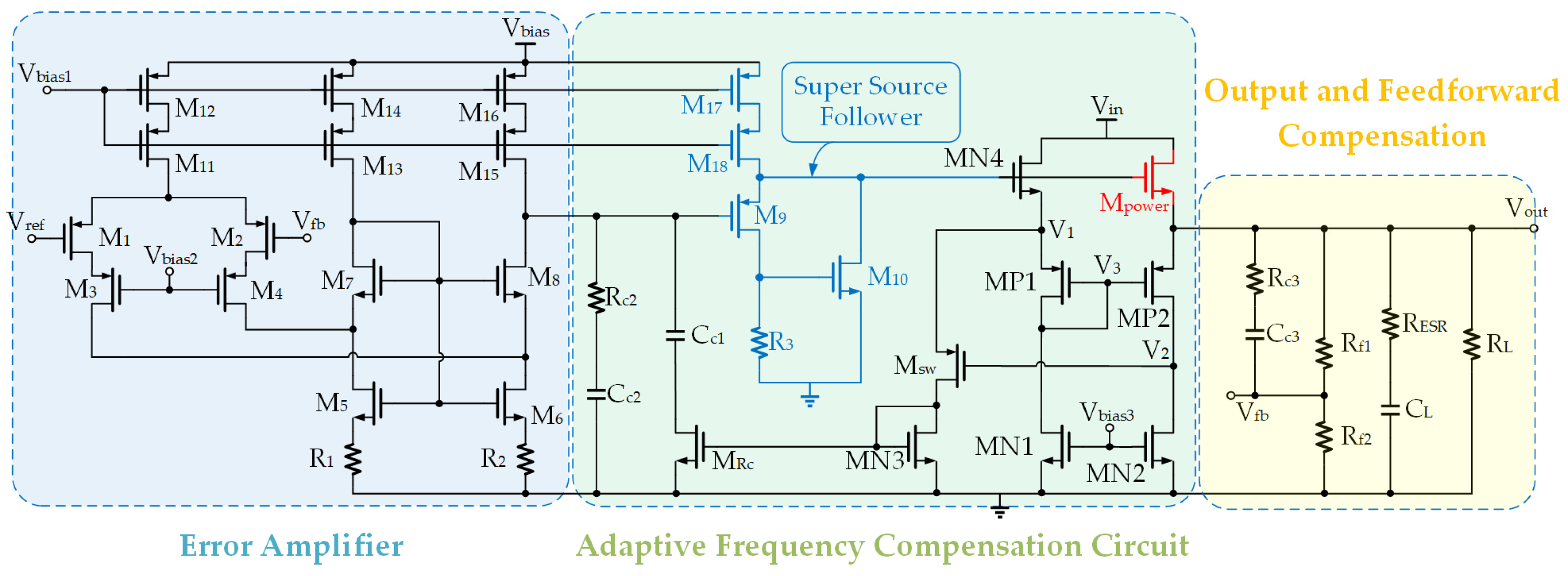

2. Design of the Proposed Low-Dropout Regulator

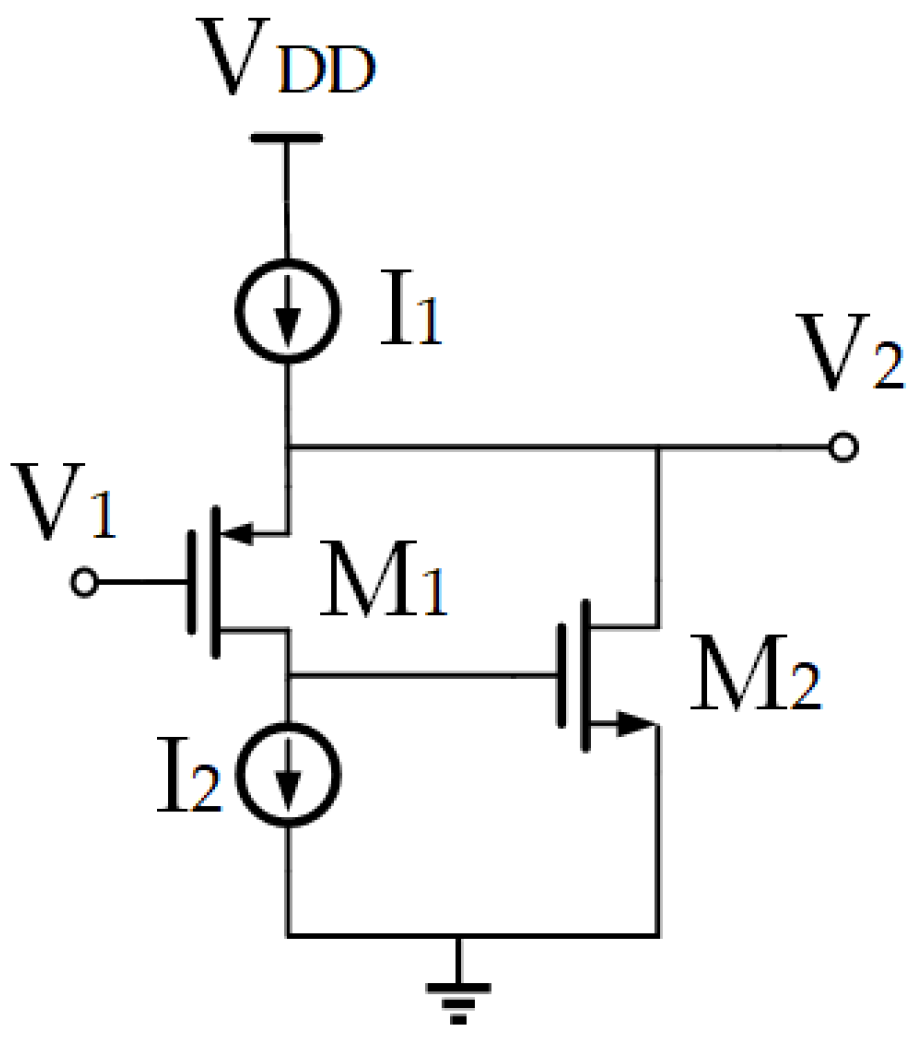

2.1. Super Source Follower

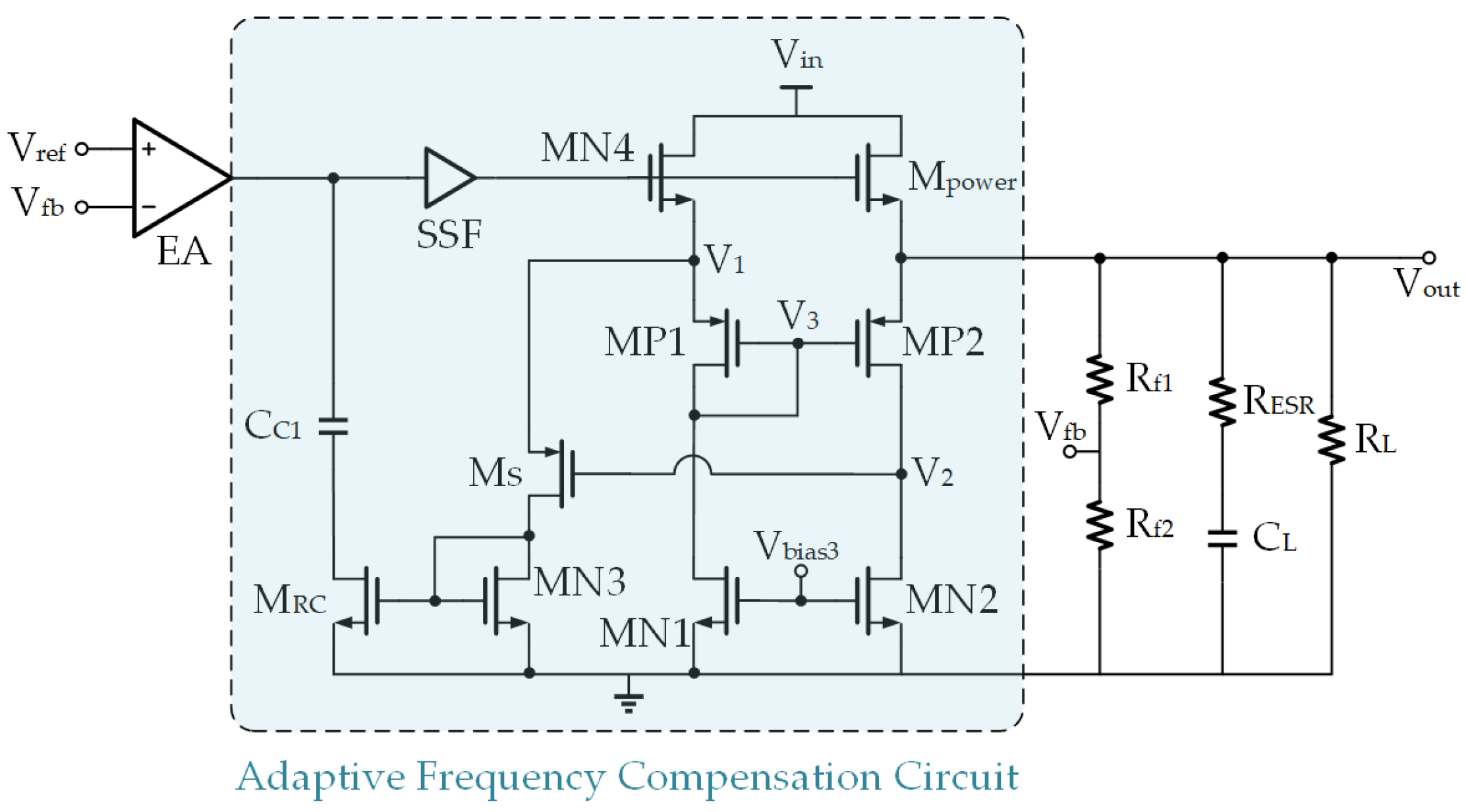

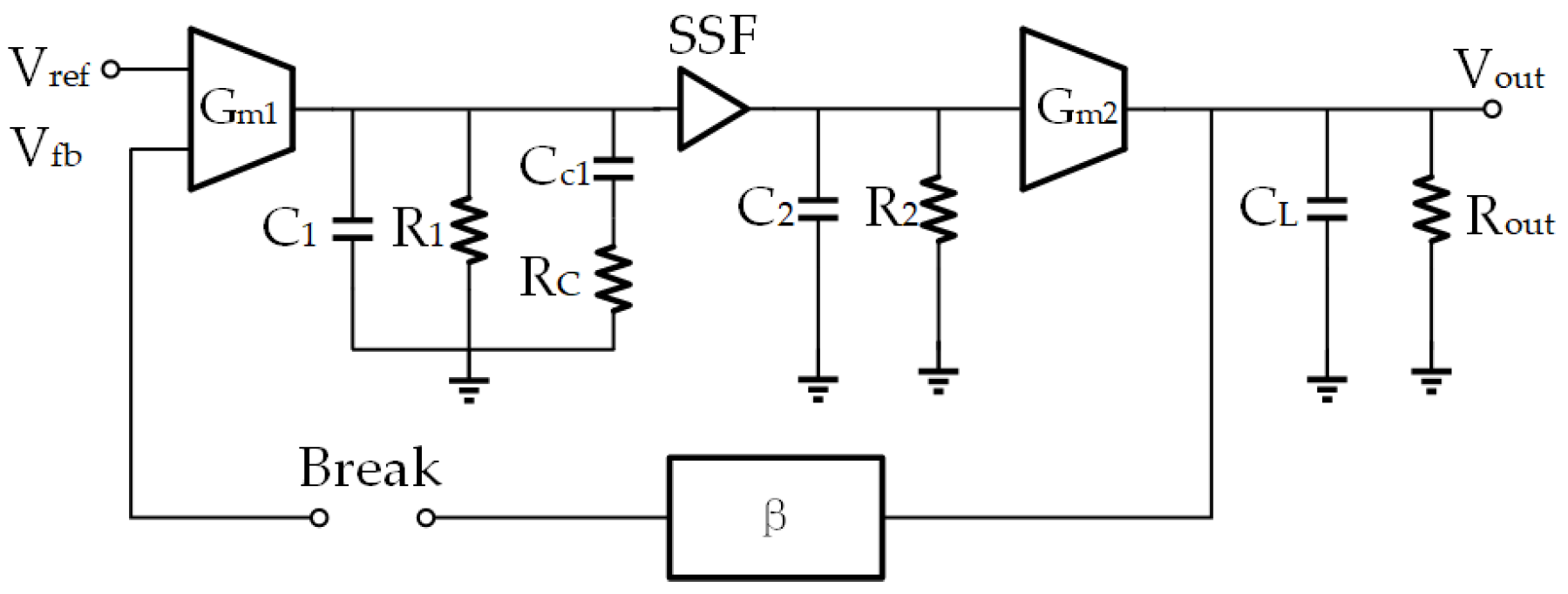

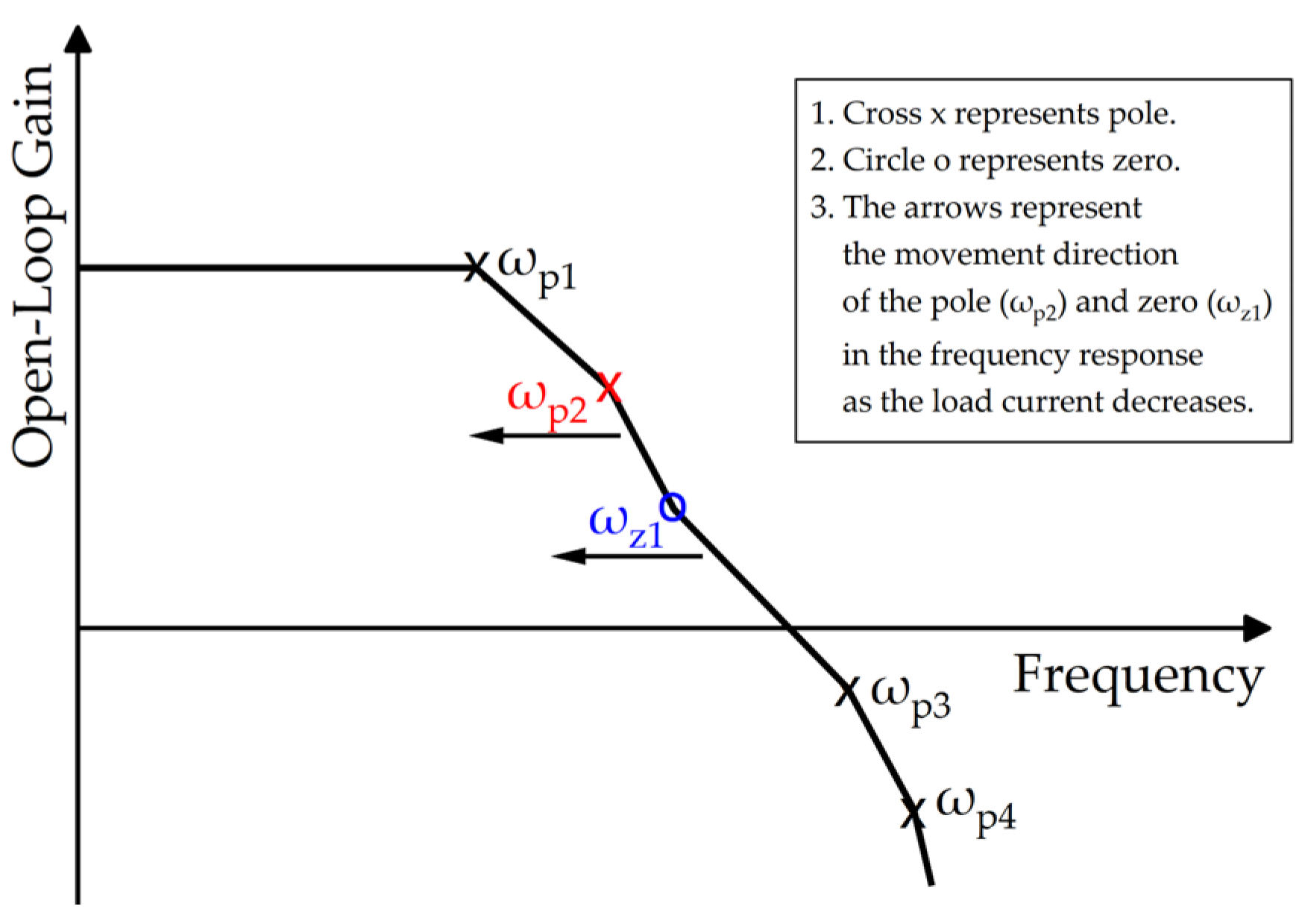

2.2. Adaptive Frequency Compensation

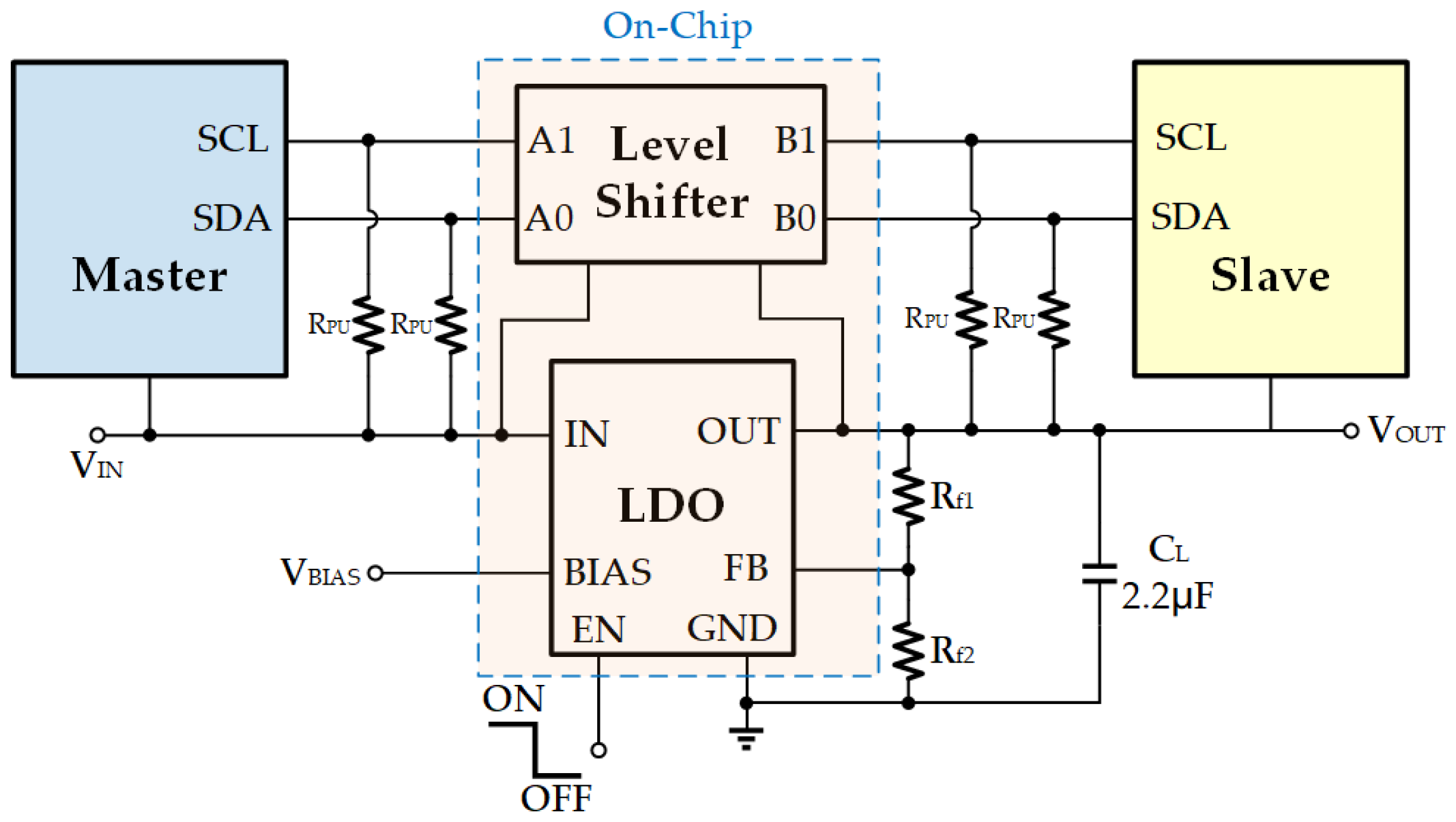

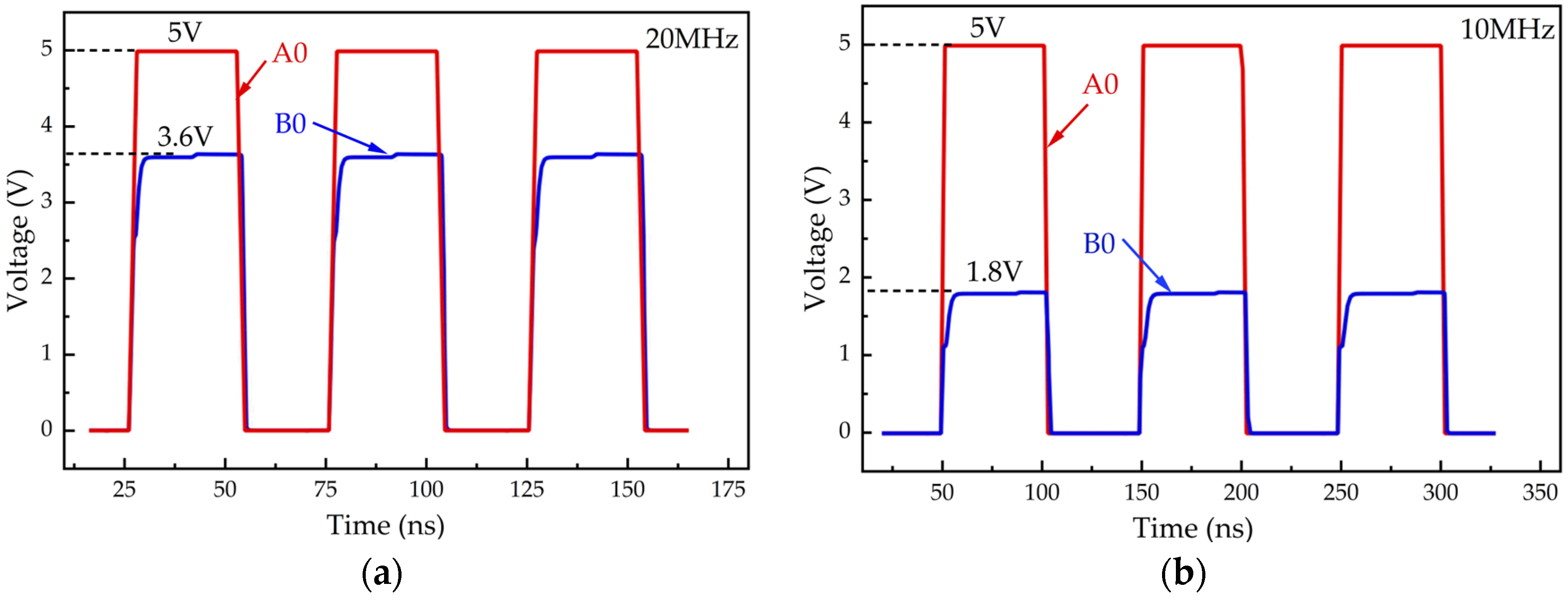

2.3. Integrated LDO and Level Shifter

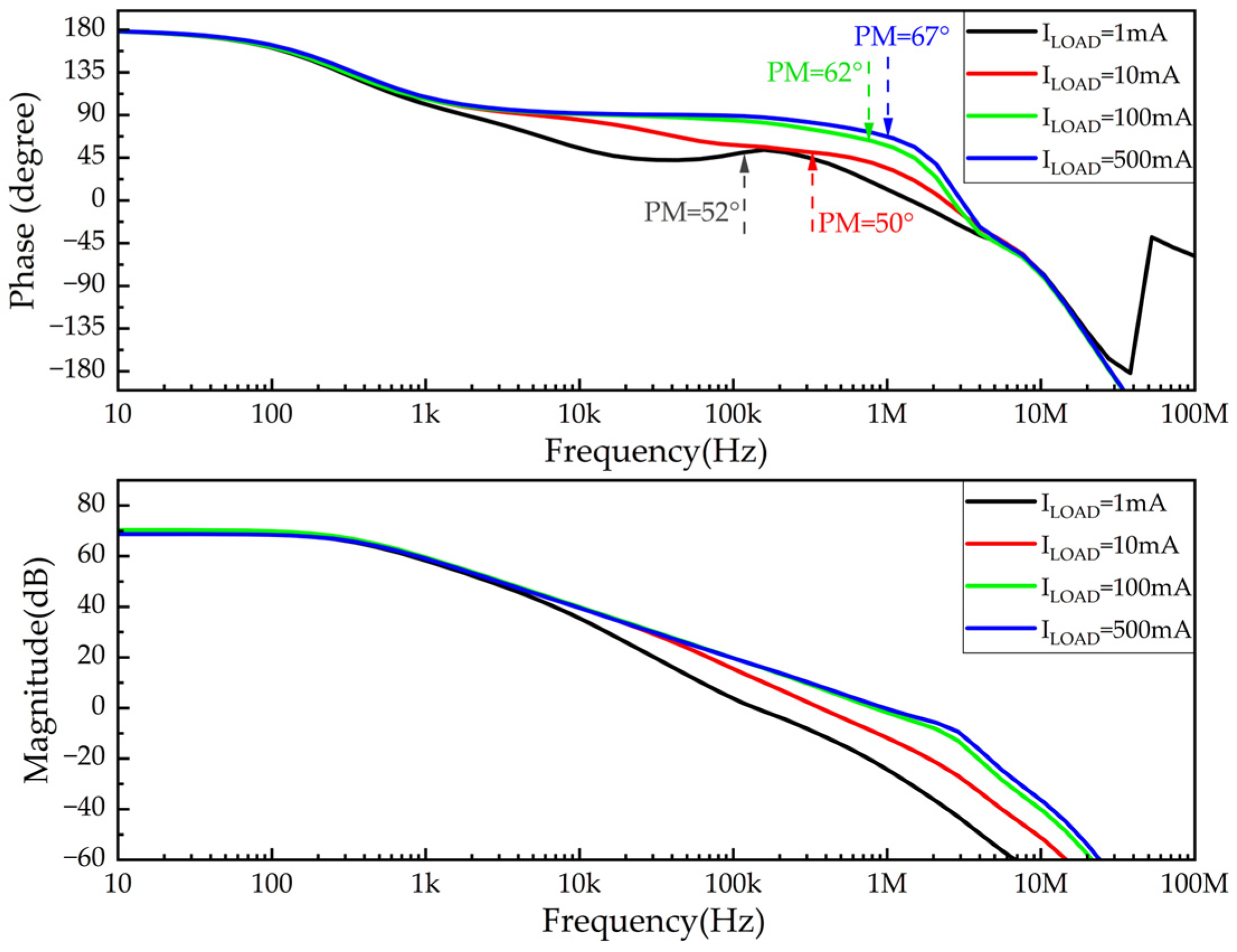

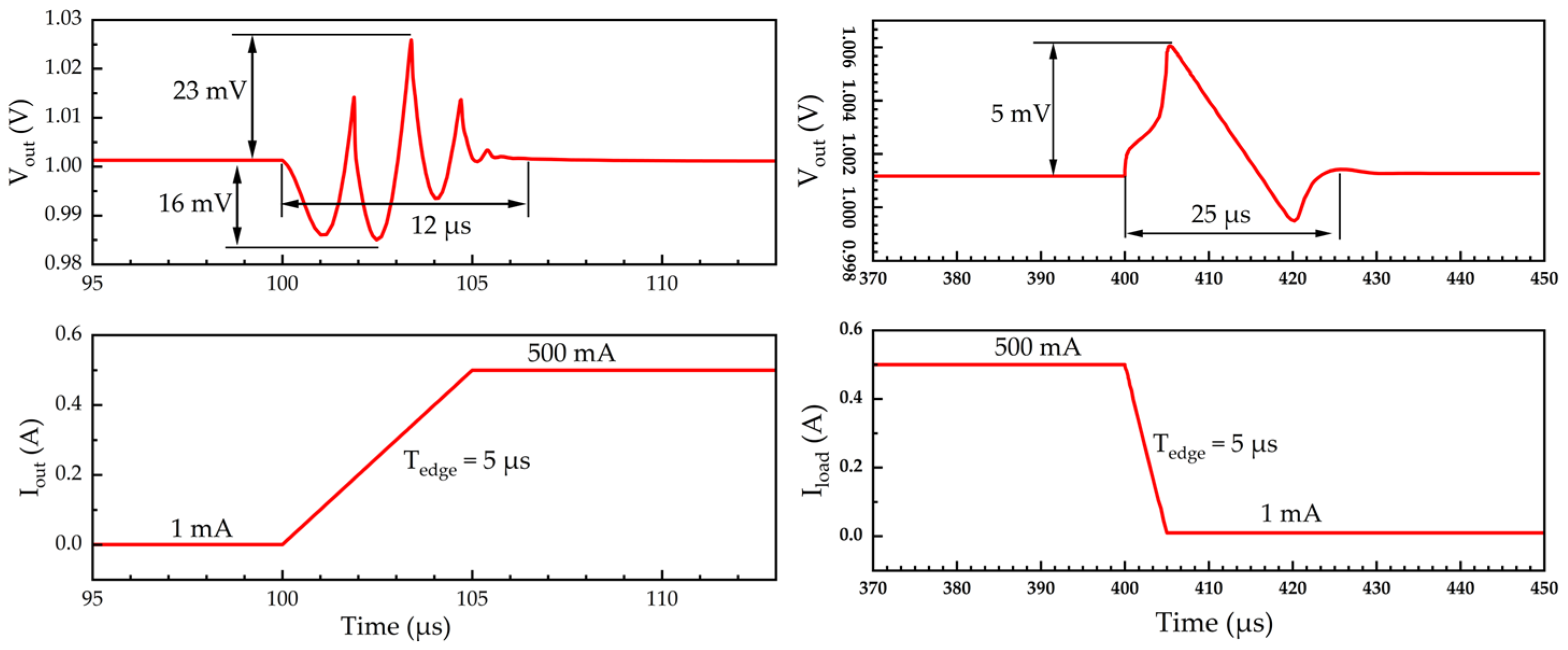

3. Simulation Results and Discussion

| Parameter | [8] | [9] | [10] | [11] | This Work |

|---|---|---|---|---|---|

| Published date (year) | 2020 | 2020 | 2024 | 2024 | 2024 |

| Technology (nm) | 180 | 180 | 600 | 110 | 180 |

| Vin (V) | 1.4–1.8 | 5.5 | 2.2–5.5 | 4–4.5 | 0.8–5.5 |

| Vout (V) | 1.2 | 1.5–5.25 | 1.8–3.3 | 1.85 | 0.8–3.6 |

| ΔVout (mV) | 20 | 36 | 38.6 | 271 | 23 |

| Cout (μF) | 4.7 | 2.2 | 1 | 1 | 2.2 |

| Iq (μA) | 13.5 | 5.6–35.6 | 9.6 | 57 | 42 |

| Iload, max (mA) | 150 | 250 | 150 | 300 | 500 |

| Iload, min (mA) | 0.1 | NA | NA | NA | 1 |

| Line reg (mV/V) | 7.785 | 10.20 | 1 | 1 | 0.62 |

| Load reg (mV/mA) | 0.0750 | 0.1120 | 0.06 | 0.00267 | 0.0018 |

| Vin PSR @ freq(dB) | −30 dB @100 Hz | −70 dB @1 MHz | −71 dB @1 KHz | −22 dB @1 MHz | −91 dB @1 KHz |

| Vbias PSR @ freq(dB) | NA | NA | NA | NA | −83@1 KHz |

| FOM 1 (ps) | 104 | 7.10 | 16.47 | 171 | 8.5 |

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Conflicts of Interest

References

- Chen, S.-L.; Lee, H.-Y.; Chen, C.-A.; Huang, H.-Y.; Luo, C.-H. Wireless Body Sensor Network With Adaptive Low-Power Design for Biometrics and Healthcare Applications. IEEE Systems Journal 2009, 3, 398–409. [Google Scholar] [CrossRef]

- Hao, Y.; Foster, R. Wireless Body Sensor Networks for Health-Monitoring Applications. Physiol. Meas. 2008, 29, R27–R56. [Google Scholar] [CrossRef]

- Gweon, S.; Lee, J.; Kim, K.; Yoo, H.-J. 93.8% Current Efficiency and 0.672 Ns Transient Response Reconfigurable LDO for Wireless Sensor Network Systems. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar]

- Mii, K.; Nagahama, A.; Watanabe, H. Ultra-Low Quiescent Current LDO with FVF-Based Load Transient Enhanced Circuit. IEICE Trans. Electron. 2020, E103.C, 466–471. [Google Scholar] [CrossRef]

- Lim, Y.; Lee, J.; Park, S.; Jo, Y.; Choi, J. An External Capacitorless Low-Dropout Regulator With High PSR at All Frequencies From 10 kHz to 1 GHz Using an Adaptive Supply-Ripple Cancellation Technique. IEEE J. Solid-State Circuits 2018, 53, 2675–2685. [Google Scholar] [CrossRef]

- Gao, J.; Wang, X.; Chen, B.; Liu, H.; Li, X.; Guo, P. A High-Input-Voltage Wide-Load LDO with Improved Load-Dependent Zero Mobile Compensation. In Proceedings of the 2022 IEEE 65th International Midwest Symposium on Circuits and Systems (MWSCAS), Fukuoka, Japan, 7–10 August 2022; pp. 1–5. [Google Scholar]

- Hazucha, P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-Efficient Linear Regulator with Ultra-Fast Load Regulation. IEEE J. Solid-State Circuit 2005, 40, 933–940. [Google Scholar] [CrossRef]

- Ming, X.; Liang, H.; Zhang, Z.-W.; Xin, Y.-L.; Qin, Y.; Wang, Z. A High-Efficiency and Fast-Transient Low-Dropout Regulator With Adaptive Pole Tracking Frequency Compensation Technique. IEEE Trans. Power Electron. 2020, 35, 12401–12415. [Google Scholar] [CrossRef]

- Joshi, K.; Manandhar, S.; Bakkaloglu, B. A 5.6 μ A Wide Bandwidth, High Power Supply Rejection Linear Low-Dropout Regulator With 68 dB of PSR Up To 2 MHz. IEEE J. Solid-State Circuit 2020, 55, 2151–2160. [Google Scholar] [CrossRef]

- Fan, H.; Feng, L.; Diao, X.; Xie, X.; Wang, C.; Li, G.; Wei, Q.; Qiao, F.; Feng, Q.; Bonizzoni, E. A Fast Transient LDO Regulator Featuring High PSRR Over 100-kHz Frequency Range With Adaptive, Dynamic Biasing, and Current Mode Feed-Forward Amplifier. IEEE Trans. Circuits Syst. II-Express Briefs 2024, 71, 1764–1768. [Google Scholar] [CrossRef]

- Tang, J.; Fan, B.; Liu, H.; Li, M.; Qin, K. Multi-Zero Pole Dynamically Compensated LDO with Low Quiescent Current. AEU Int. J. Electron. Commun. 2024, 184, 155423. [Google Scholar] [CrossRef]

| Parameter | Equation |

|---|---|

| ωp1 | 1/R1Cc1 |

| ωp2 | 1/RoutCL |

| ωp3 | 1/RcC1 |

| ωp4 | 1/R2C2 |

| ωz1 | 1/RcCc1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, H.; Cui, J. A Low-Power, Fast Transient Response Low-Dropout Regulator Featuring Bi-Directional Level Shifting for Sensor Applications. Eng. Proc. 2024, 82, 53. https://doi.org/10.3390/ecsa-11-20349

Huang H, Cui J. A Low-Power, Fast Transient Response Low-Dropout Regulator Featuring Bi-Directional Level Shifting for Sensor Applications. Engineering Proceedings. 2024; 82(1):53. https://doi.org/10.3390/ecsa-11-20349

Chicago/Turabian StyleHuang, Hao, and Jie Cui. 2024. "A Low-Power, Fast Transient Response Low-Dropout Regulator Featuring Bi-Directional Level Shifting for Sensor Applications" Engineering Proceedings 82, no. 1: 53. https://doi.org/10.3390/ecsa-11-20349

APA StyleHuang, H., & Cui, J. (2024). A Low-Power, Fast Transient Response Low-Dropout Regulator Featuring Bi-Directional Level Shifting for Sensor Applications. Engineering Proceedings, 82(1), 53. https://doi.org/10.3390/ecsa-11-20349