Functional Converter for Intelligent Sensor and Its Layout Design †

Abstract

:1. Introduction

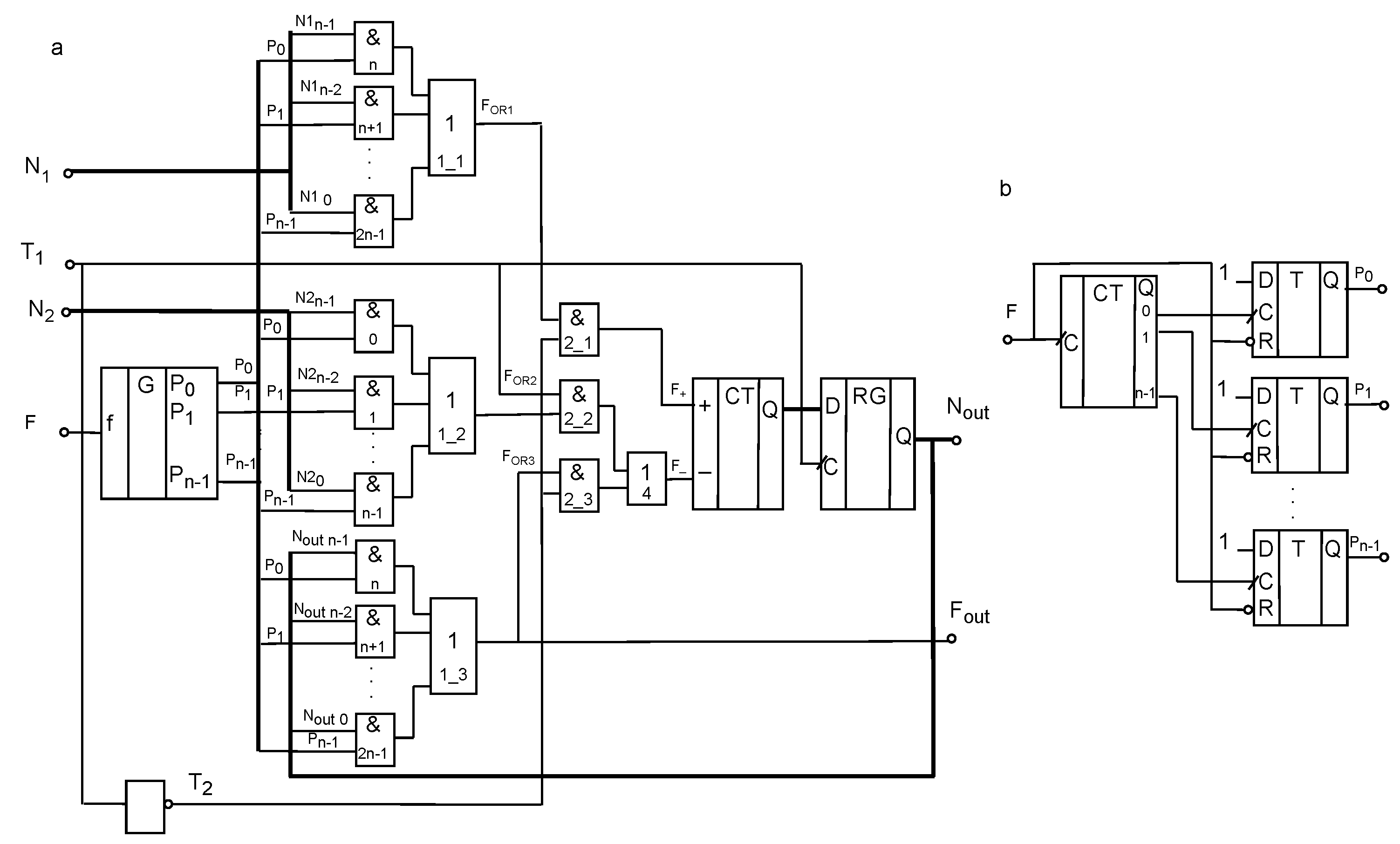

2. Design of the Converter

2.1. Implementation Based on Traditional Calculations

2.2. Implementation Based on the Method of Small Increments

3. Converter Implementation

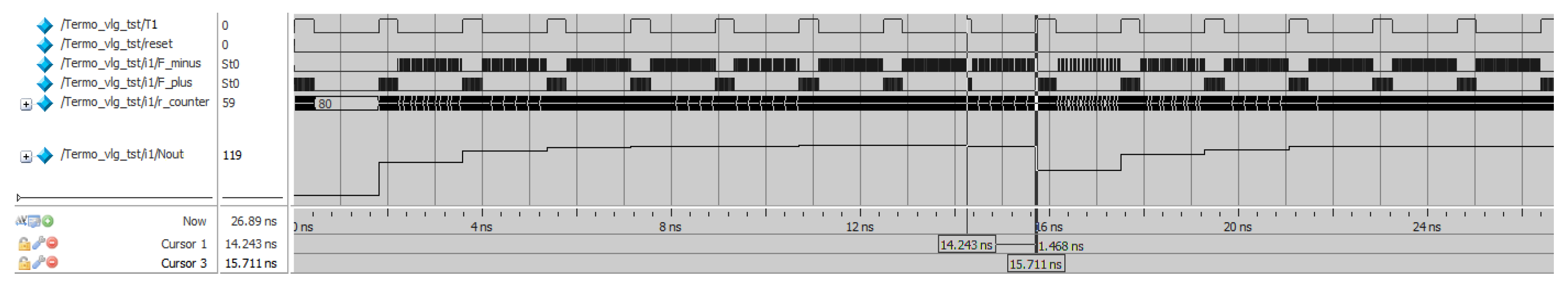

3.1. Simulation of the Converter

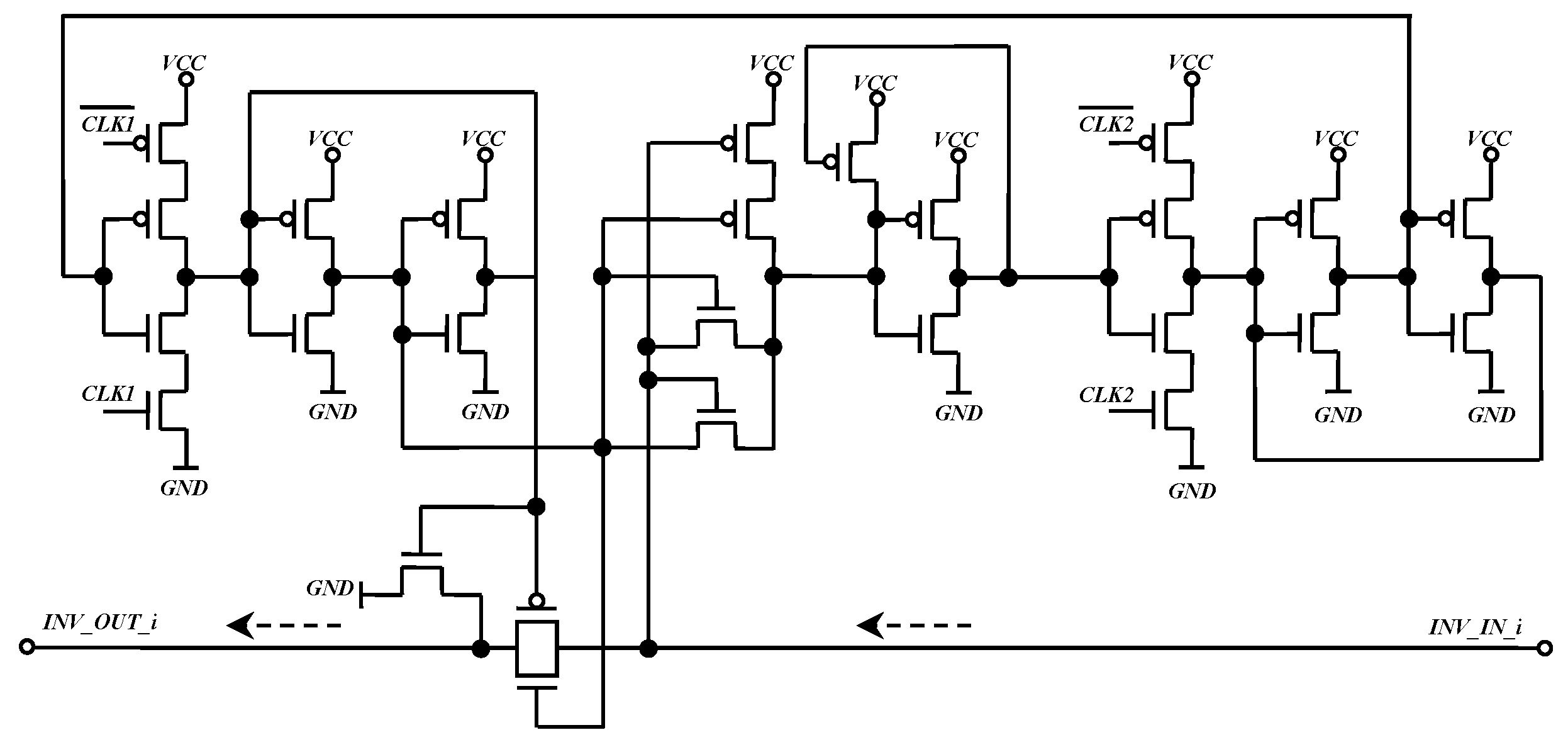

3.2. Custom Circuit Design

4. Conclusions

- Energy efficiency of the presence of pauses between pulses, which reduces the average power consumption;

- High reliability of information transmission by a stream of pulses, since the loss of one pulse when transmitting a number of pulses is equivalent to the loss of one low-order bit of the binary code, while the loss of a pulse when transmitting a binary code, even in sequential format, is equivalent to the loss of a value with the weight , where k is a bit number in the binary code.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Jain, R.; Tata, S. Cloud to Edge: Distributed Deployment of Process-Aware IoT Applications. In Proceedings of the 2017 IEEE International Conference on Edge Computing (EDGE), Honolulu, HI, USA, 25–30 June 2017; pp. 182–189. [Google Scholar]

- Singh, S. Optimize cloud computations using edge computing. In Proceedings of the 017 International Conference on Big Data, IoT and Data Science (BID), Pune, India, 20–22 December 2017; pp. 49–53. [Google Scholar]

- Feichi, Z.; Yang, C. Near-sensor and in-sensor computing. Nat. Electron. 2020, 3, 664–671. [Google Scholar]

- Yang, C. In-sensor computing for machine vision. Nature 2020, 579, 32–33. [Google Scholar]

- Ueno, K.; Asai, T.; Amemiya, Y. Temperature-to-frequency converter consisting of subthreshold mosfet circuits for smart temperature-sensor LSIs. In Proceedings of the TRANSDUCERS 2009-2009 International Solid-State Sensors, Actuators and Microsystems Conference, Denver, CO, USA, 21–25 June 2009; pp. 2433–2436. [Google Scholar]

- Beshliu, V.S.; Kantser, V.G.; Beldiman, L.N.; Beshliu, V.V.; Coban, R.A. Integral gauge pressure sensor with frequency output signal. In Proceedings of the CAS ’99 Proceedings. 1999 International Semiconductor Conference (Cat. No.99TH8389), Sinaia, Romania, 5–9 October 1999; pp. 491–494. [Google Scholar]

- Darwish, H.; Reig, C.; Cubells-Beltrán, M.D.; Leger, G.; De Marcellis, A. CMOS Capacitance-to-Time Converter-Based Interface for Differential Capacitive Sensors. In Proceedings of the 2020 Global Congress on Electrical Engineering (GC-ElecEng), Valencia, Spain, 4–6 September 2020; pp. 61–64. [Google Scholar]

- Kokolanski, Z.; Gavrovski, C.; Dimcev, V.; Makraduli, M. Simple Interface for Resistive Sensors Based on Pulse Width Modulation. Trans. Instrum. Meas. 2013, 62, 2983–2992. [Google Scholar] [CrossRef]

- Arbet, D.; Kováč, M.; Stopjaková, V.; Potočný, M. Voltage-to-Frequency Converter for Ultra-Low-Voltage Applications. In Proceedings of the 2019 42nd International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), Opatija, Croatia, 20–24 May 2019; pp. 53–58. [Google Scholar]

- Areekath, L.; George, B.; Reverter, F. An Auto-Balancing Capacitance-to-Pulse-Width Converter for Capacitive Sensors. IEEE Sens. J. 2021, 21, 765–775. [Google Scholar] [CrossRef]

- Safyannikov, N.; Bureneva, O. Bit-Stream Functional Converters for Decentralized Sensor Systems. In Proceedings of the 2020 9th Mediterranean Conference on Embedded Computing (MECO), Budva, Montenegro, 8–11 June 2020; pp. 1–4. [Google Scholar]

- Santos, E.J.P.; Silva, L.B.M. FPGA-based smart sensor implementation with precise frequency to digital converter for flow measurement. In Proceedings of the 2010 VI Southern Programmable Logic Conference (SPL), Ipojuca, Brazil, 24–26 March 2010; pp. 21–26. [Google Scholar]

- Tirupathi, R.; Kar, S.K. On-Chip Implementable Autocalibration of Sensor Offset for Differential Capacitive Sensor Interfaces. IEEE Trans. Instrum. Meas. 2021, 70, 1–9. [Google Scholar] [CrossRef]

- Yoshii, Y.; Nakajo, A.; Abe, H.; Nimomiya, K.; Miyashita, H.; Sakurai, N.; Kosuge, M.; Hao, S. 1 chip integrated software calibrated CMOS pressure sensor with MCU, A/D convertor, D/A convertor, digital communication port, signal conditioning circuit and temperature sensor. In Proceedings of the International Solid State Sensors and Actuators Conference (Transducers ’97), Chicago, IL, USA, 19 June 1997; pp. 1485–1488. [Google Scholar]

- Serial Digital Output Thermometers. Analog Device. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ (accessed on 10 October 2021).

- Reverter, F.; Jordana, J.; Pallas-Areny, R. Program-dependent uncertainty in period-to-code converters based on counters embedded in microcontrollers. In Proceedings of the 20th IEEE Instrumentation Technology Conference (Cat. No.03CH37412), Vail, CO, USA, 20–22 May 2003; pp. 977–980. [Google Scholar]

- Thakur, A.; Mehra, R. Power and speed efficient ripple counter design using 45 nm technology. In Proceedings of the 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–4. [Google Scholar]

- Putra, H.D.; Pratiwi, S.E.; Jamilah, W. The synthesis of counter circuit layout design based on CMOS technology 0.35 micro-m. In Proceedings of the 2017 Second International Conference on Informatics and Computing (ICIC), Jayapura, Indonesia, 1–3 November 2017; pp. 1–5. [Google Scholar]

- Mironov, S.E.; Zibarev, K.M. Management of Layout Matching of Objects of Complex Microelectronic Systems with Uncertainty of Design Rules. In Proceedings of the 2019 III International Conference on Control in Technical Systems (CTS), St. Petersburg, Russia, 30 October–1 November 2019; pp. 69–73. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bureneva, O.; Mironov, S.; Safyannikov, N.; Sukhinets, Z. Functional Converter for Intelligent Sensor and Its Layout Design. Eng. Proc. 2023, 33, 50. https://doi.org/10.3390/engproc2023033050

Bureneva O, Mironov S, Safyannikov N, Sukhinets Z. Functional Converter for Intelligent Sensor and Its Layout Design. Engineering Proceedings. 2023; 33(1):50. https://doi.org/10.3390/engproc2023033050

Chicago/Turabian StyleBureneva, Olga, Sergey Mironov, Nikolay Safyannikov, and Zhanna Sukhinets. 2023. "Functional Converter for Intelligent Sensor and Its Layout Design" Engineering Proceedings 33, no. 1: 50. https://doi.org/10.3390/engproc2023033050

APA StyleBureneva, O., Mironov, S., Safyannikov, N., & Sukhinets, Z. (2023). Functional Converter for Intelligent Sensor and Its Layout Design. Engineering Proceedings, 33(1), 50. https://doi.org/10.3390/engproc2023033050