Author Contributions

F.G.: theory, modelling, writing, numerical simulations, and editing; A.M.: writing, modelling, simulation, implementation, python programming, and results. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding author.

Conflicts of Interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Abbreviations

The following abbreviations are used in this manuscript:

| Abbreviations | Meaning |

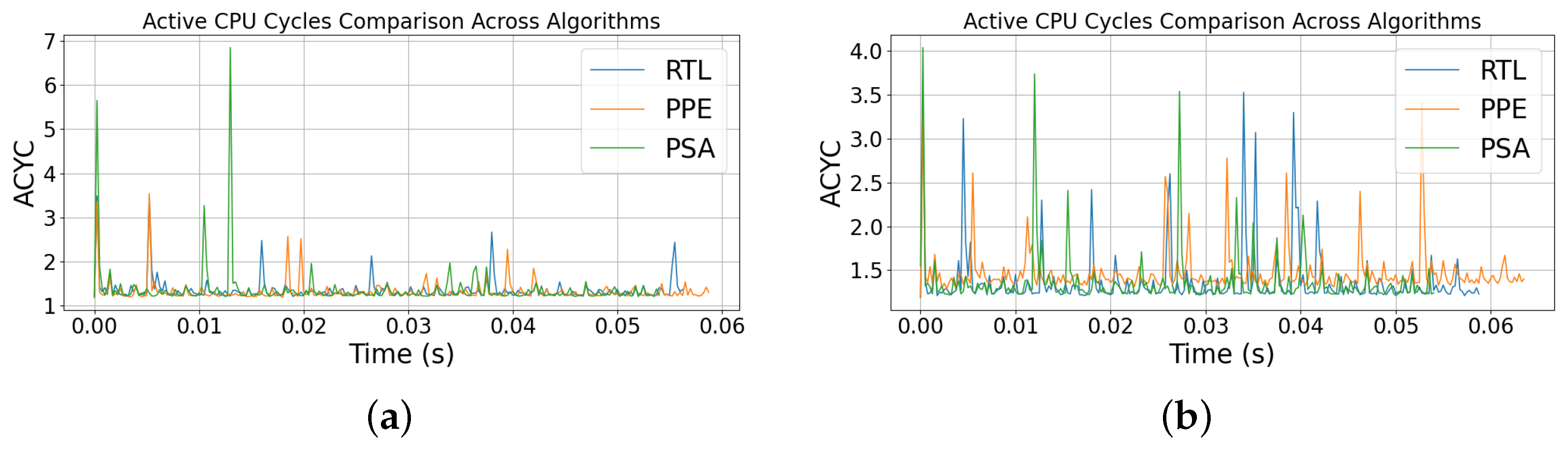

| ACYC | Active CPU Cycles |

| ALU | Arithmetic logic unit |

| CPA | Correlation Power Analysis (side-channel) |

| CPU | Central Processing Unit |

| CSV | Comma Separated Values |

| DPA | Differential power analysis (side-channel) |

| ECC | Elliptic curve cryptography |

| GPU | Graphic Processing Unit |

| HW | Hamming Weight |

| IDE | Integrated Development Environment |

| INST | Instructions Retired (used in Intel’s PCM) |

| IoT | Internet of things |

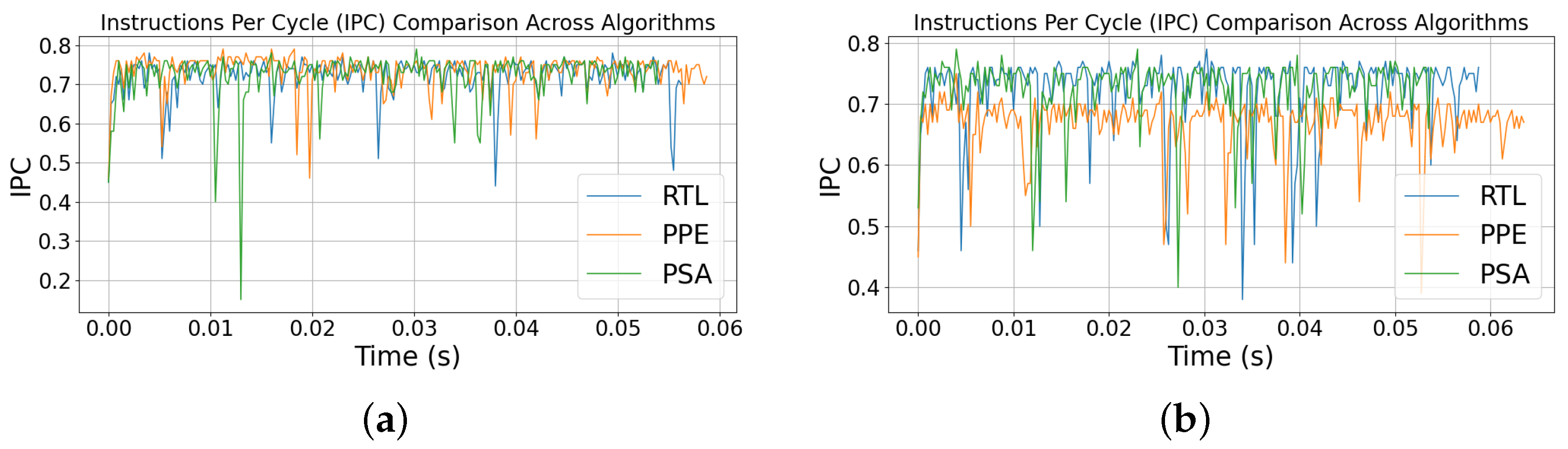

| IPC | Interprocess Communication |

| LSB | Least Significant Bit |

| LtR | Left-to-Right algorithm |

| L3MPI | Level 3 Cache Misses per instruction |

| L3MSS | Raw Level 3 Misses |

| L3 Cache | Level 3 cache |

| MSB | Most Significant Bit |

| NAF | Non-Adjacent Form |

| NIST | National institute of standards and technology |

| OS | Operating system |

| PCM | Performance Counter Monitor |

| PKI | Public key infrastructure |

| RAPL | Running Average Power Limit (used in Intel’s PCM) |

| RSA | Rivest-Shamir-Adleman |

| RtL | Right-to-Left algorithm |

| SCA | Side-channel attack |

| SPA | Simple power analysis (side-channel) |

| TVLA | Test Vector Leakage Assessment |

References

- Qiang, L. Research on Performance Optimization and Resource Allocation Strategy of Network Node Encryption Based on RSA Algorithm. J. Cyber Secur. Mobil. 2025, 14, 101–125. [Google Scholar] [CrossRef]

- Kolagatla, V.R.; Raveendran, A.; Desalphine, V. A Novel and Efficient SPI enabled RSA Crypto Accelerator for Real-Time applications. In Proceedings of the 2024 28th International Symposium on VLSI Design and Test (VDAT), Vellore, India, 1–3 September 2024. [Google Scholar]

- Navarro-Torrero, P.; Camacho-Ruiz, E.; Martinez-Rodriguez, M.C.; Brox, P. Design of a Karatsuba Multiplier to Accelerate Digital Signature Schemes on Embedded Systems. In Proceedings of the 2024 IEEE Nordic Circuits and Systems Conference (NorCAS), Lund, Sweden, 29–30 October 2024. [Google Scholar]

- Ibrahim, A.; Gebali, F. Symmetry-enabled resource-efficient systolic array design for Montgomery multiplication in resource-constrained MIoT endpoints. Symmetry 2024, 16, 715. [Google Scholar] [CrossRef]

- Ibrahim, A.; Gebali, F. Enhancing Security and Efficiency in IoT Assistive Technologies: A Novel Hybrid Systolic Array Multiplier for Cryptographic Algorithms. Appl. Sci. 2025, 15, 2660. [Google Scholar] [CrossRef]

- Cormen, T.H.; Leiserson, C.E.; Rivest, R.L.; Stein, C. Introduction to Algorithms, 3rd ed.; MIT Press and McGraw-Hill: Cambridge, MA, USA, 2009. [Google Scholar]

- Menezes, A.J.; Van Oorschot, P.C.; Vanstone, S.A. Handbook of Applied Cryptography; CRC Press: Boca Raton, FL, USA, 2018. [Google Scholar]

- Kocher, P.C. Timing attacks on implementations of Diffie-Hellman, RSA, DSS, and other systems. In Proceedings of the Advances in Cryptology—CRYPTO’96: 16th Annual International Cryptology Conference, Santa Barbara, CA, USA, 18–22 August 1996; Proceedings 16. Springer: Berlin/Heidelberg, Germany, 1996; pp. 104–113. [Google Scholar]

- Lou, X.; Zhang, T.; Jiang, J.; Zhang, Y. A survey of microarchitectural side-channel vulnerabilities, attacks, and defenses in cryptography. ACM Comput. Surv. (CSUR) 2021, 54, 1–37. [Google Scholar] [CrossRef]

- Liang, Y.; Bai, G. A randomized window-scanning RSA scheme resistant to power analysis. In Proceedings of the 2014 IEEE/ACIS 13th International Conference on Computer and Information Science (ICIS), Taiyuan, China, 4–6 June 2014. [Google Scholar]

- Yin, X.; Wu, K.; Li, H.; Xu, G. A randomized binary modular exponentiation based RSA algorithm against the comparative power analysis. In Proceedings of the 2012 IEEE International Conference on Intelligent Control, Automatic Detection and High-End Equipment, Beijing, China, 27–29 July 2012. [Google Scholar]

- Luo, C.; Fei, Y.; Kaeli, D. GPU Acceleration of RSA is Vulnerable to Side-channel Timing Attacks. In Proceedings of the 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Diego, CA, USA, 5–8 November 2018. [Google Scholar]

- Ors, K.A.B.B. Differential Power Analysis resistant hardware implementation of the RSA cryptosystem. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, 18–21 May 2008. [Google Scholar]

- Gulen, U.; Baktir, S. Side-Channel Resistant 2048-Bit RSA Implementation for Wireless Sensor Networks and Internet of Things. IEEE Access 2023, 11, 39531–39543. [Google Scholar] [CrossRef]

- Möller, B. Improved techniques for fast exponentiation. In Proceedings of the International Conference on Information Security and Cryptology, Seoul, Republic of Korea, 28–29 November 2002; Springer: Berlin/Heidelberg, Germany, 2002; pp. 298–312. [Google Scholar]

- Möller, B. Sliding Window Exponentiation. In Encyclopedia of Cryptography, Security and Privacy; Jajodia, S., Samarati, P., Yung, M., Eds.; Springer Nature Switzerland: Cham, Switzerland, 2025; pp. 2443–2445. [Google Scholar] [CrossRef]

- Joye, M. Highly regular m-ary powering ladders. In Proceedings of the Selected Areas in Cryptography: 16th Annual International Workshop, SAC 2009, Calgary, AB, Canada, 13–14 August 2009; Revised Selected Papers 16. Springer: Berlin/Heidelberg, Germany, 2009; pp. 350–363. [Google Scholar]

- Astriratma, R. A Study of Known Vulnerabilities and Exploit Patterns in Blockchain Smart Contracts. J. Curr. Res. Blockchain 2025, 2, 169–179. [Google Scholar] [CrossRef]

- Mendoza, C.P.T.; Tubice, N.G. Analyzing Historical Trends and Predicting Market Sentiment in Digital Currency Using Time Series Decomposition and ARIMA Models on Crypto Fear and Greed Index Data. J. Digit. Mark. Digit. Curr. 2025, 2, 270–297. [Google Scholar] [CrossRef]

- Intel Corporation. Intel/PCM. Available online: https://github.com/intel/pcm (accessed on 16 October 2025).

| Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).