Polysilicon-Channel Synaptic Transistors for Implementation of Short- and Long-Term Memory Characteristics

Abstract

1. Introduction

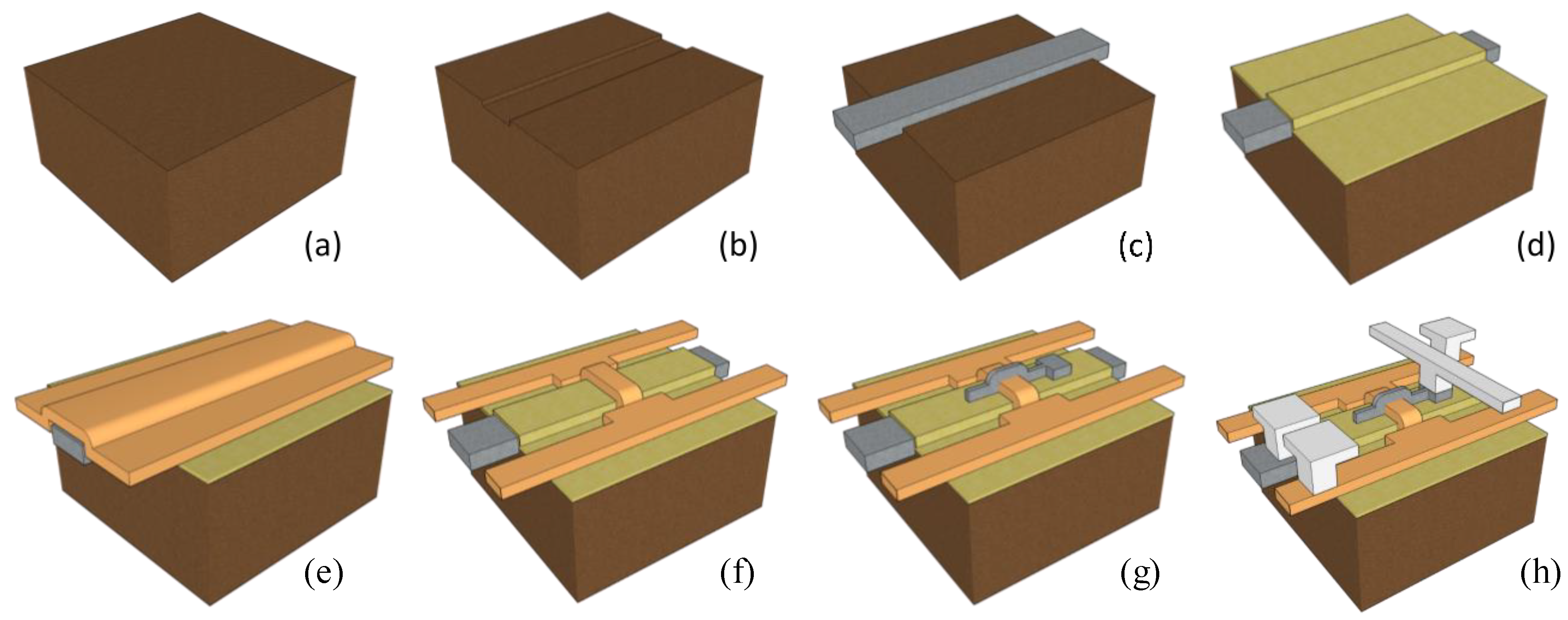

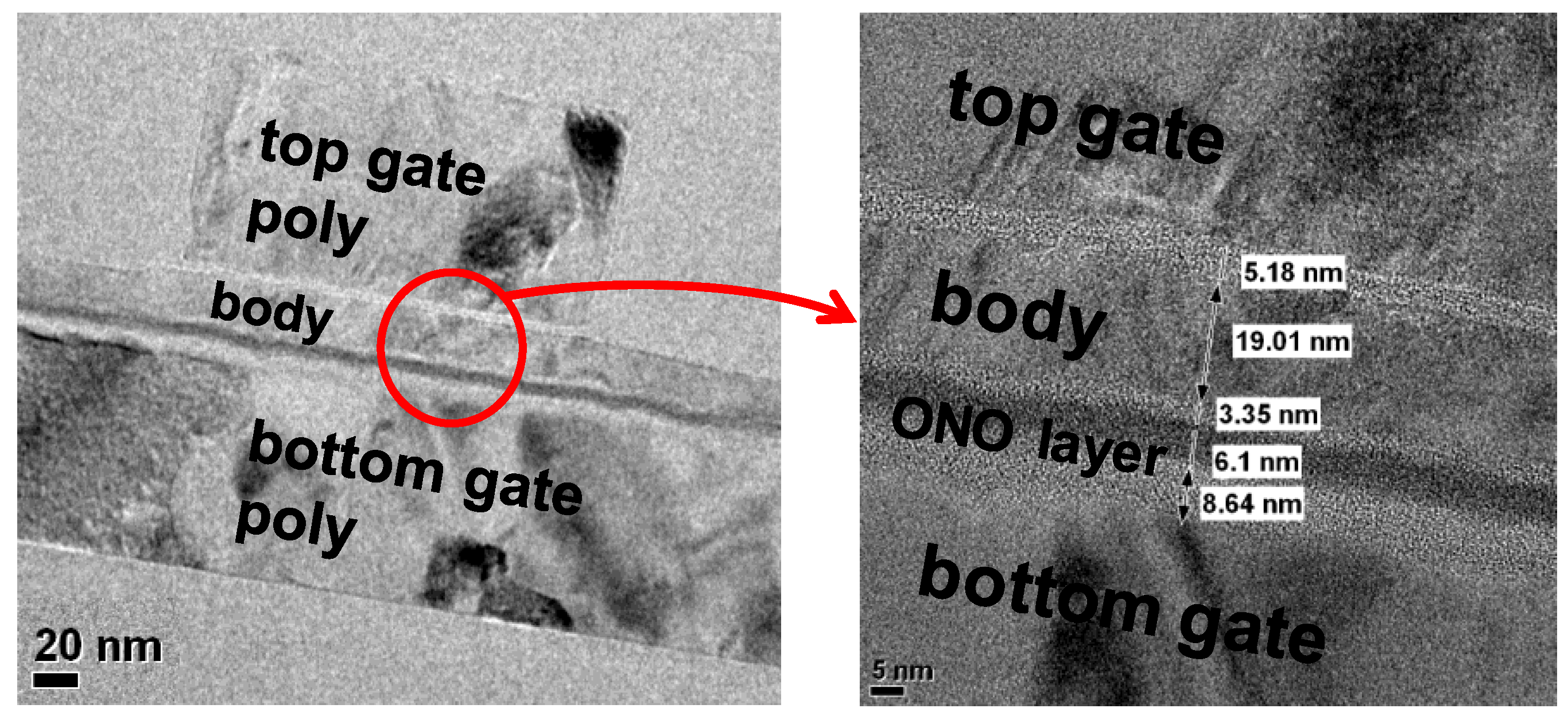

2. Materials and Methods

3. Results and Discussion

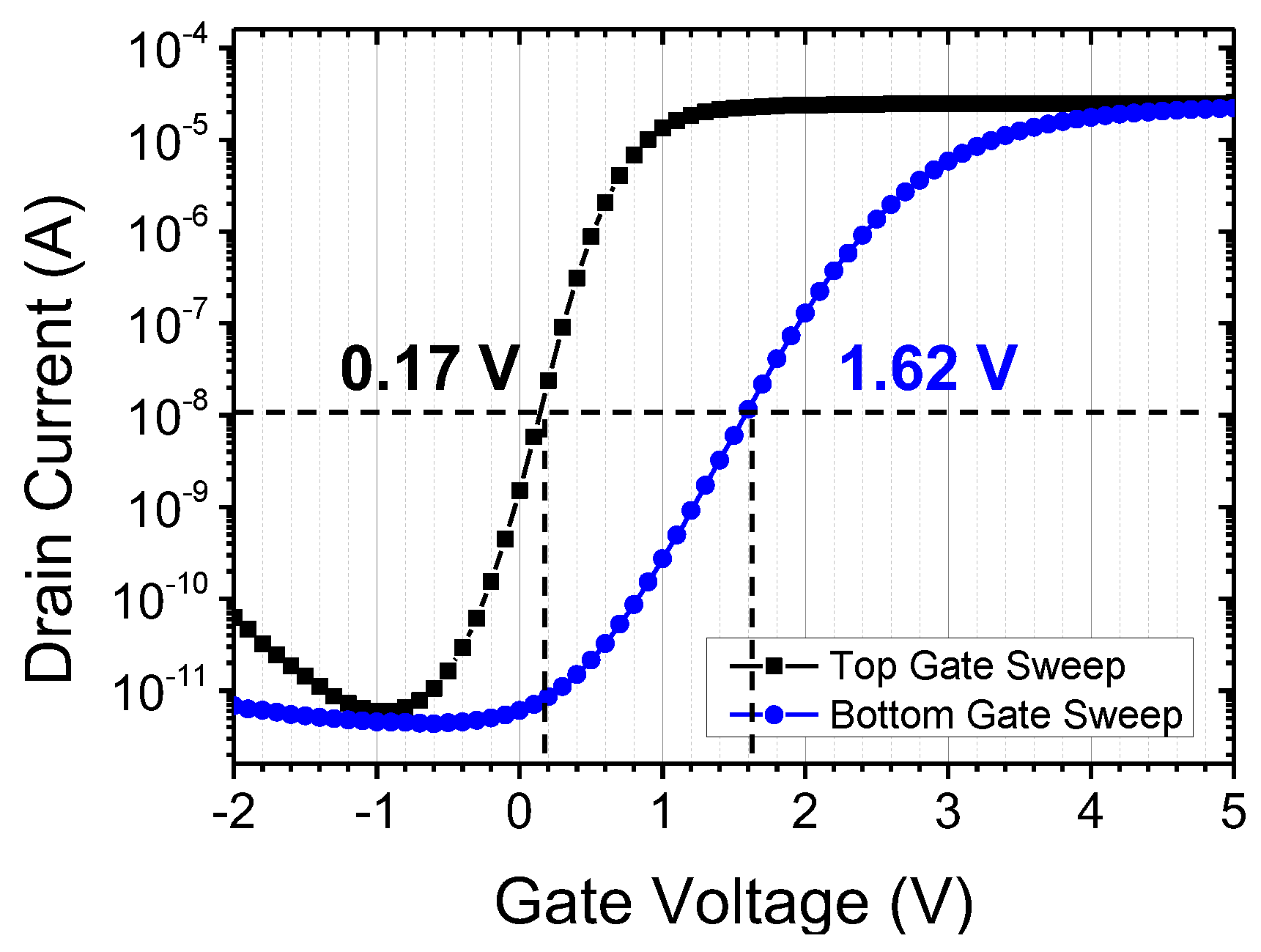

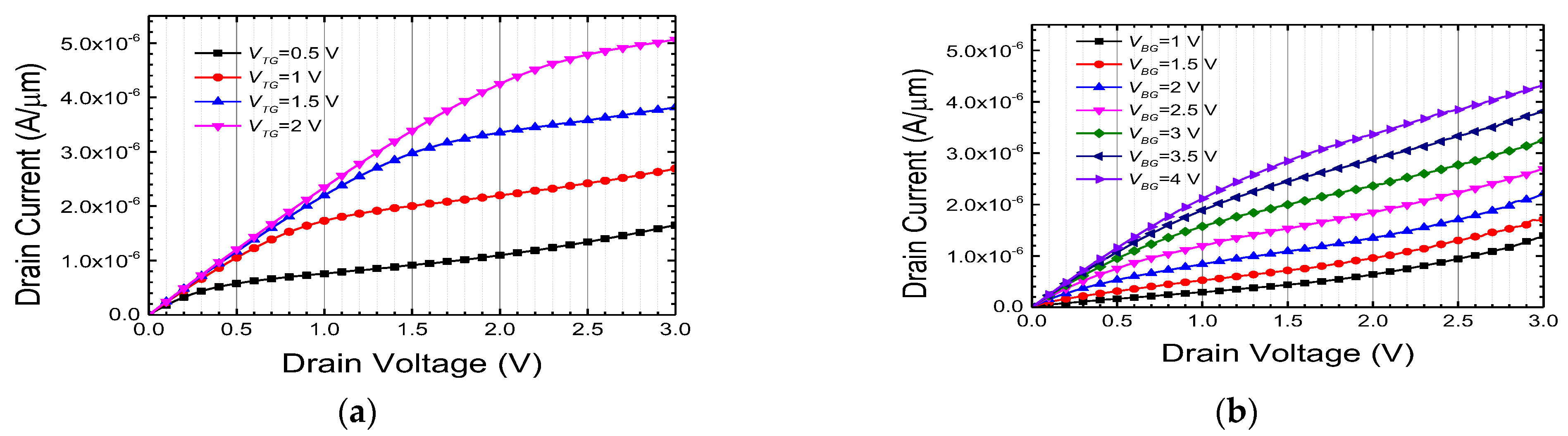

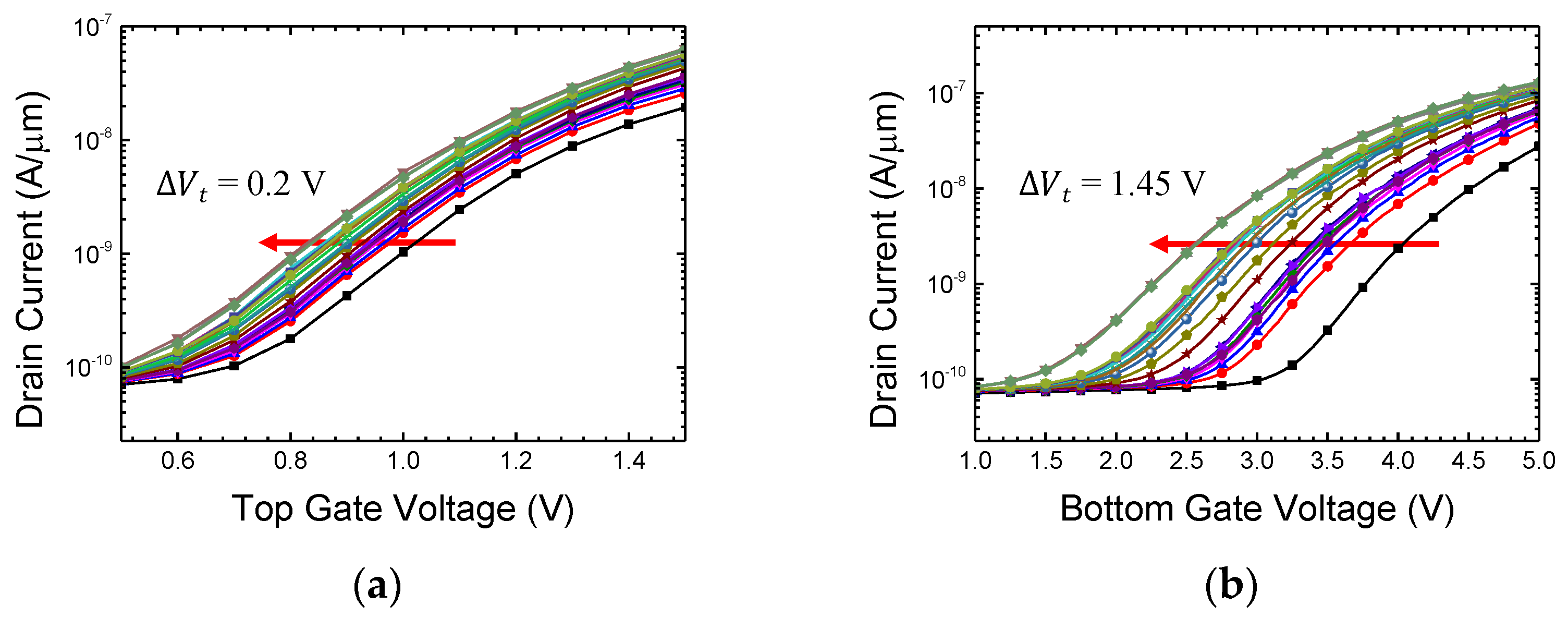

3.1. Basic Device Characteristics

3.2. Grain Boundary Induced Short-Term Memory Effect

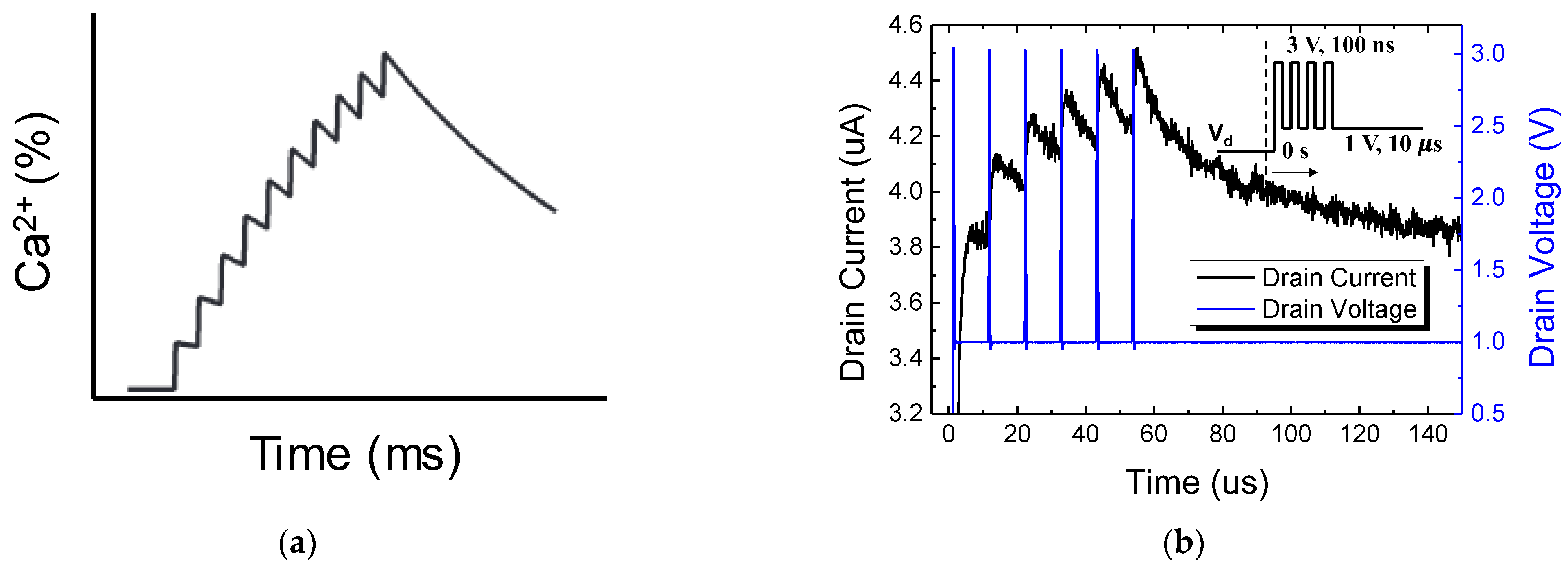

3.2.1. Synaptic Plasticity

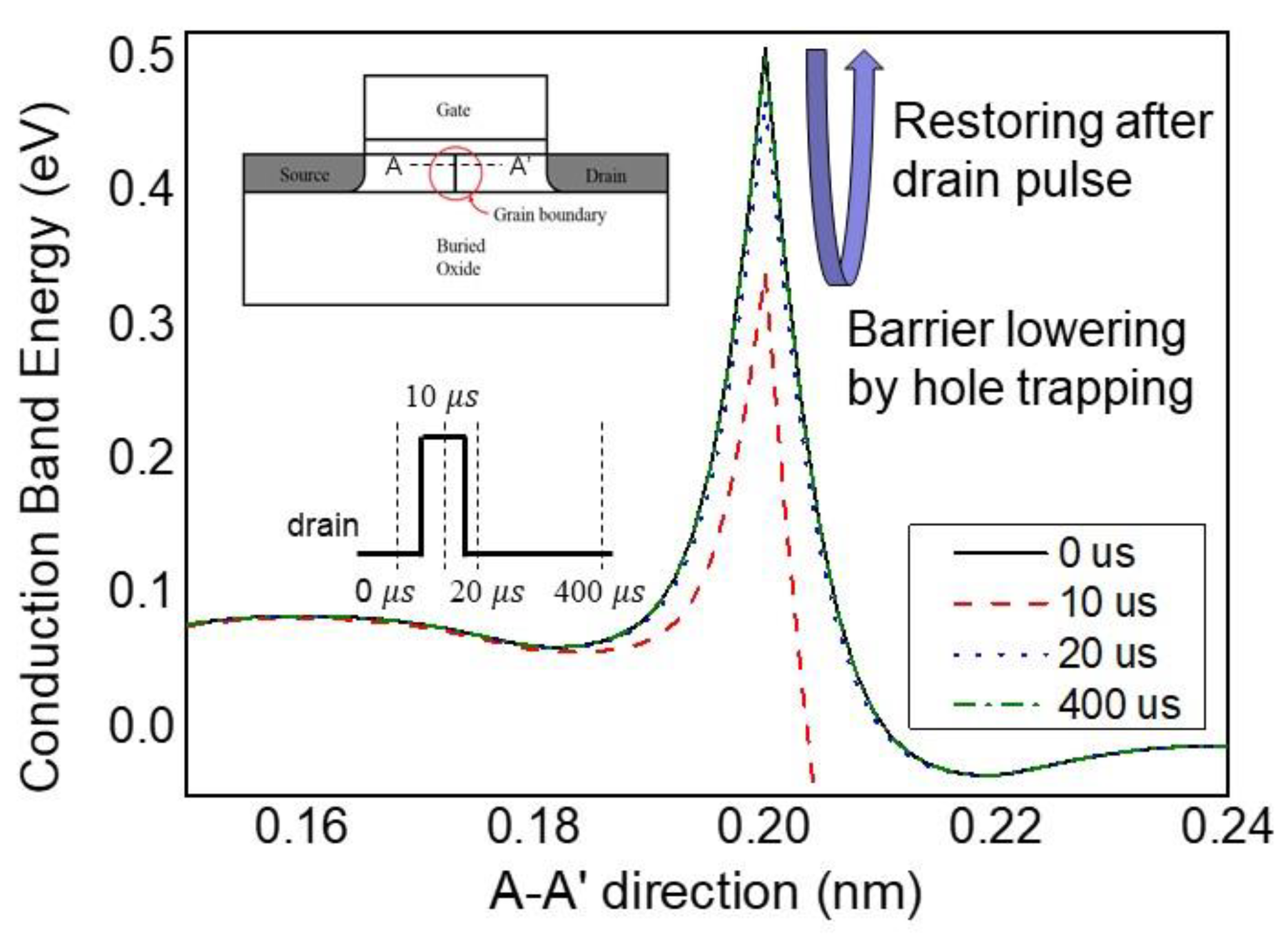

3.2.2. Charge Trapping Phenomenon at Polysilicon Grain Boundary

3.3. Long-Term Memory Property

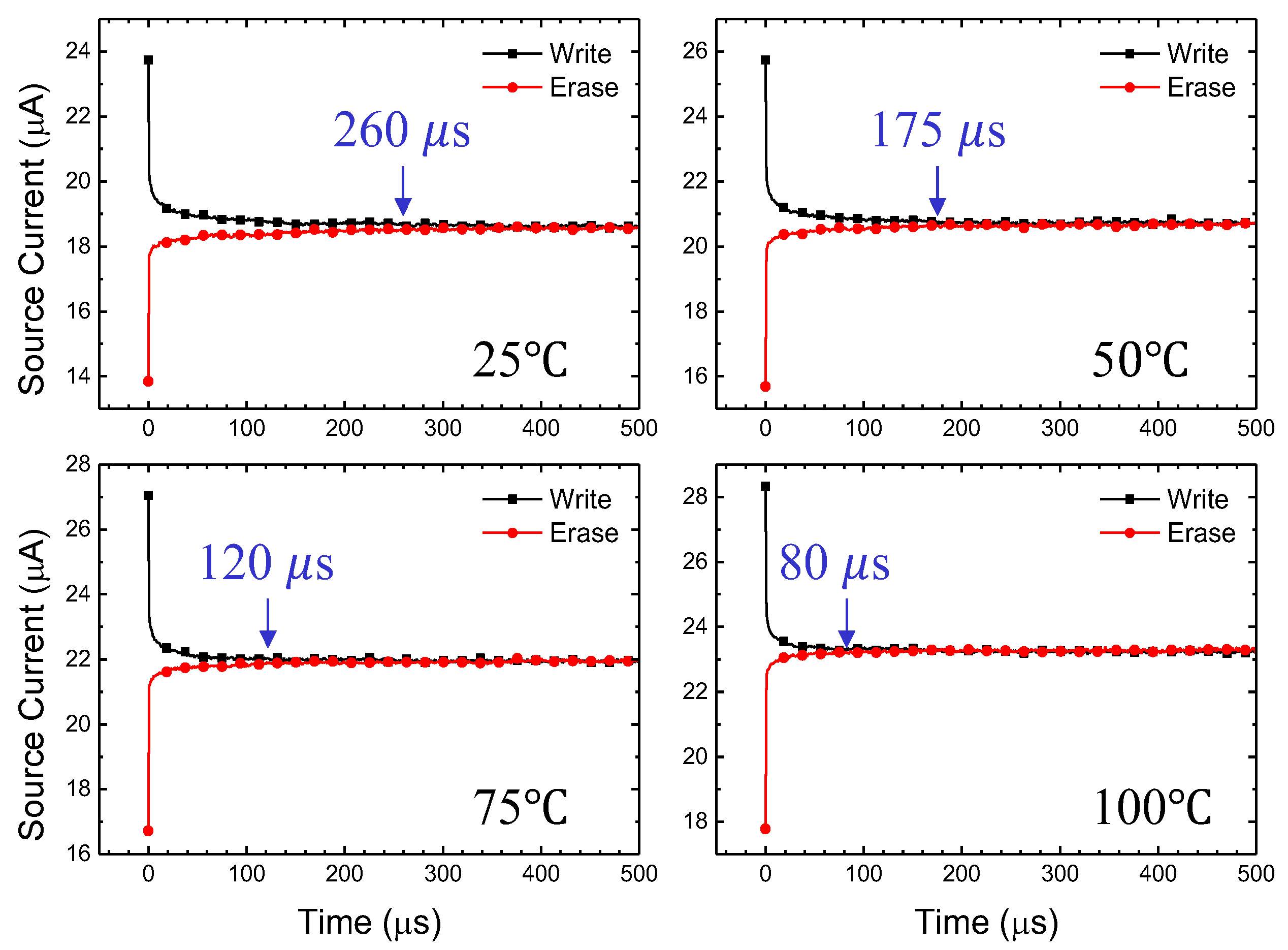

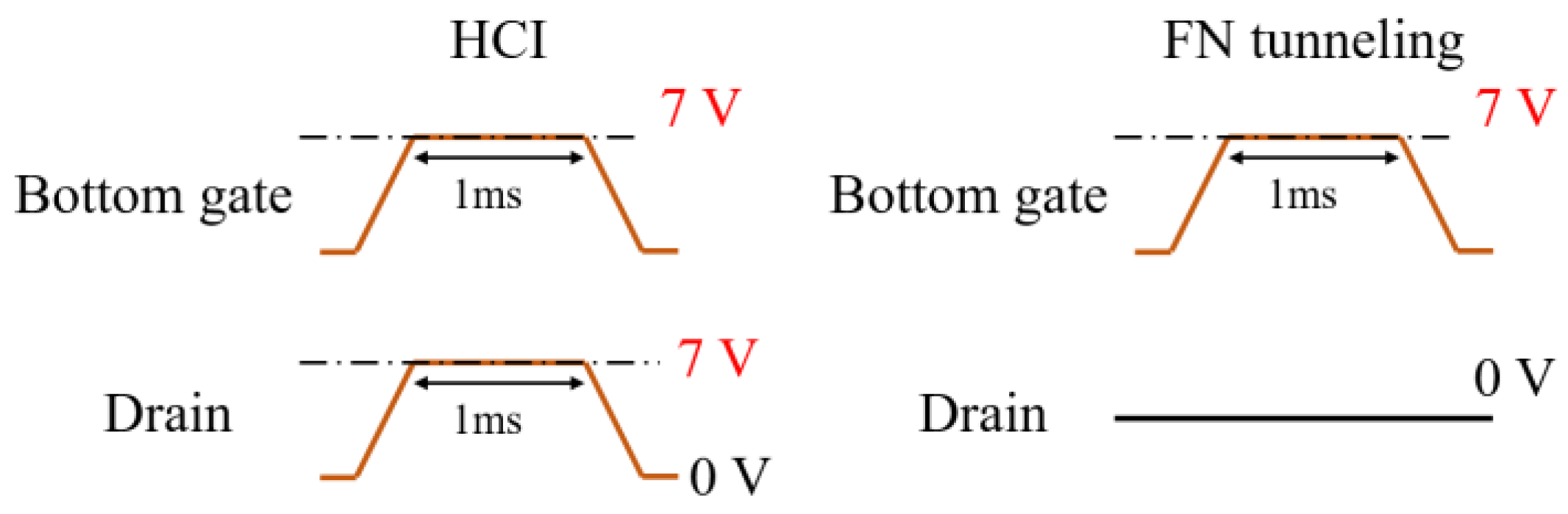

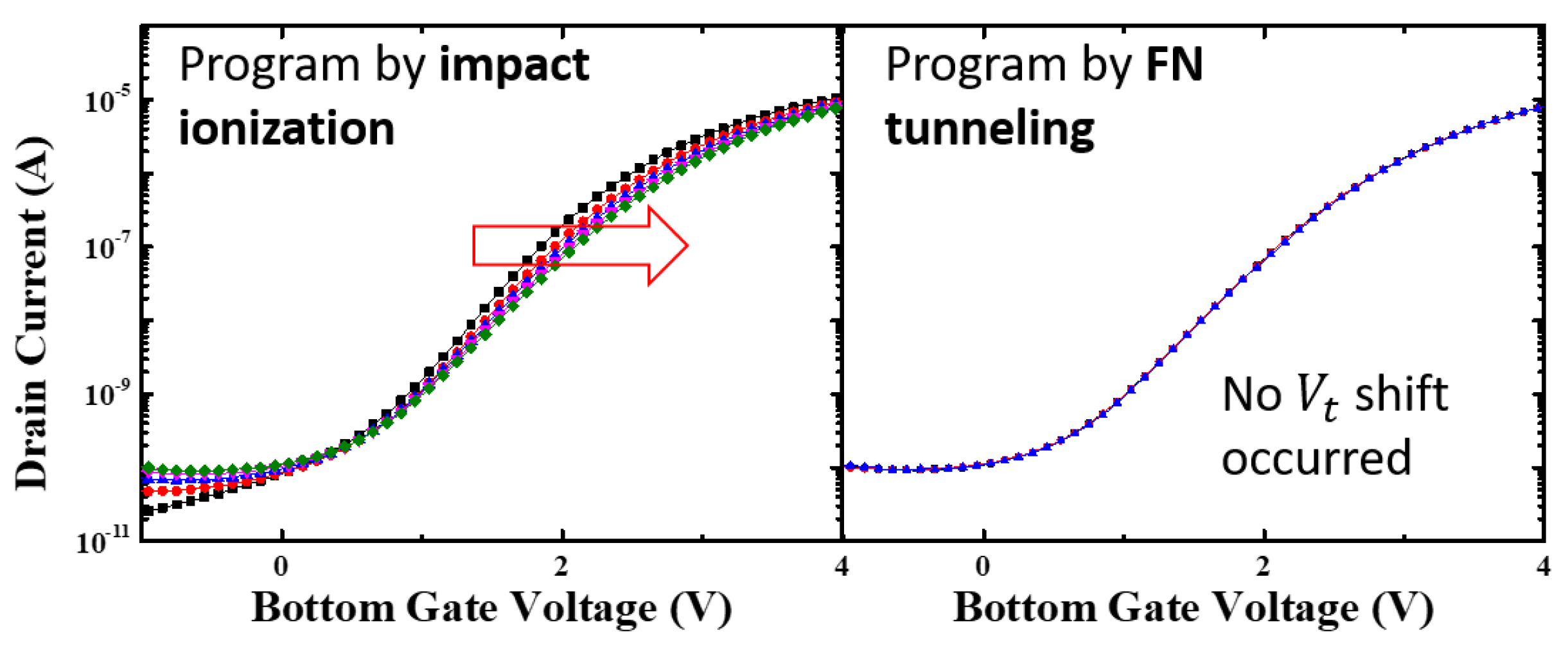

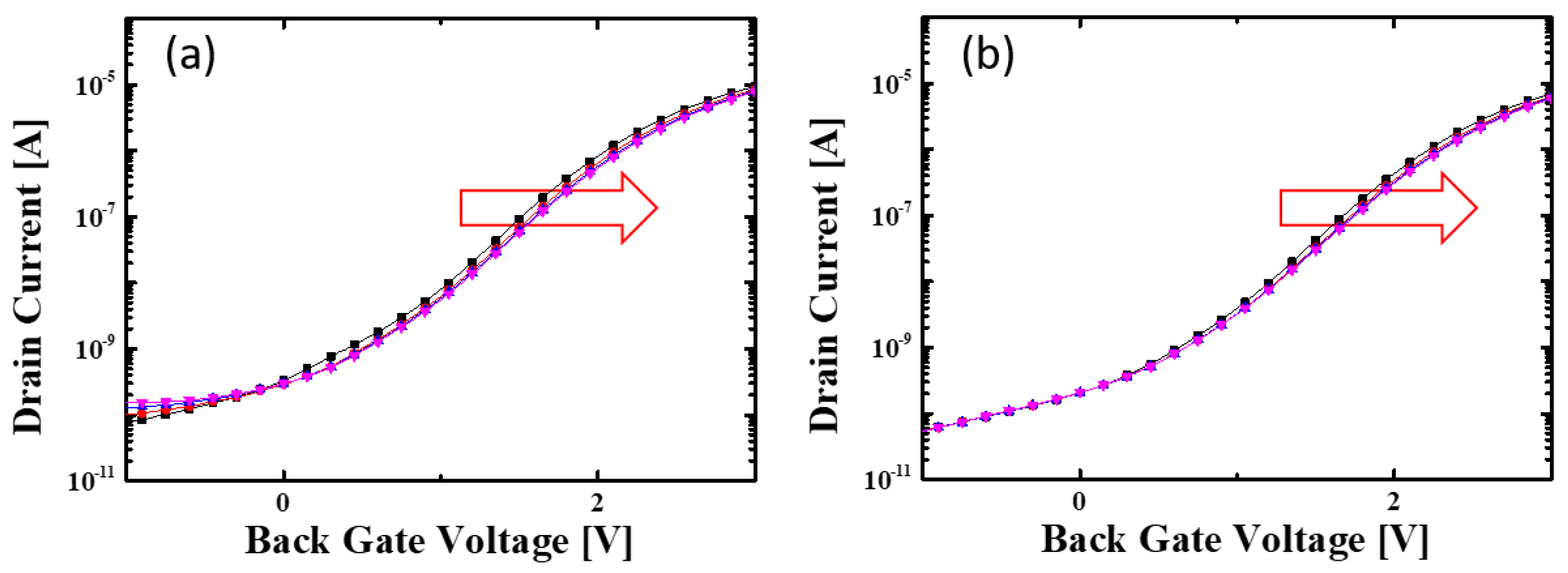

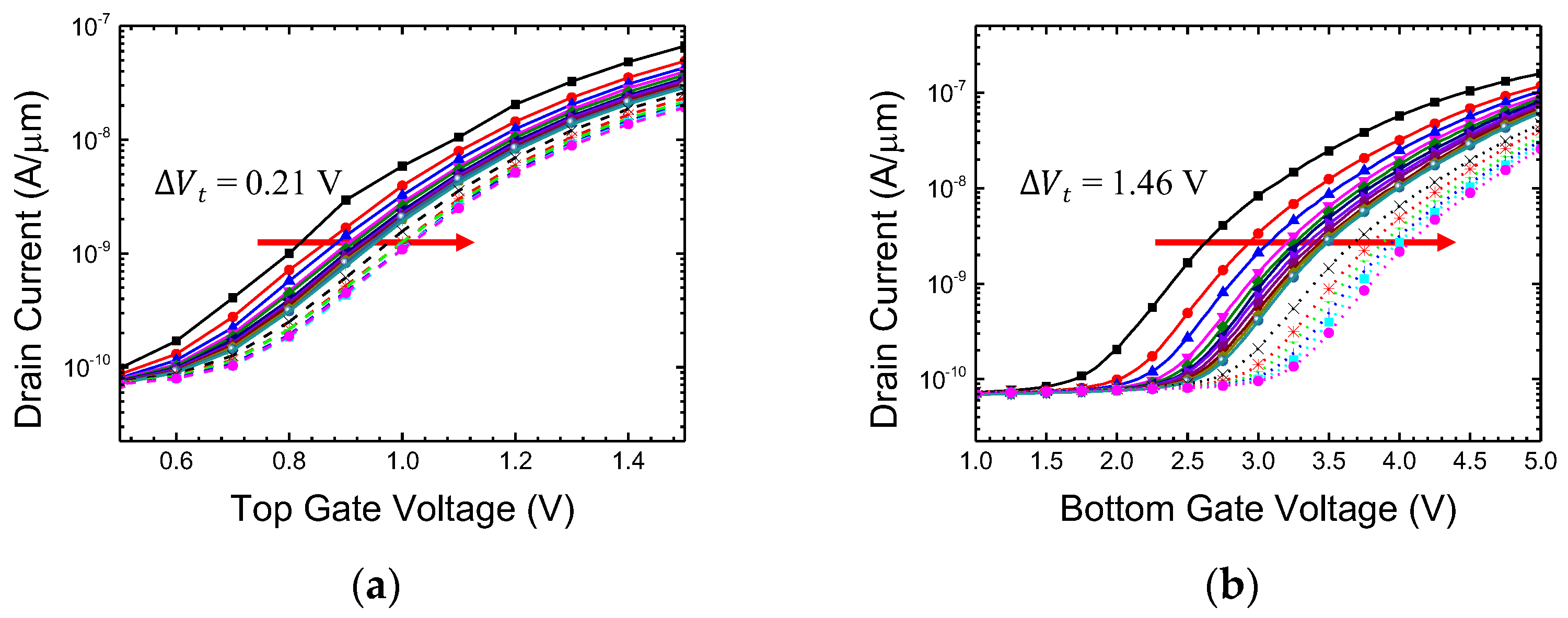

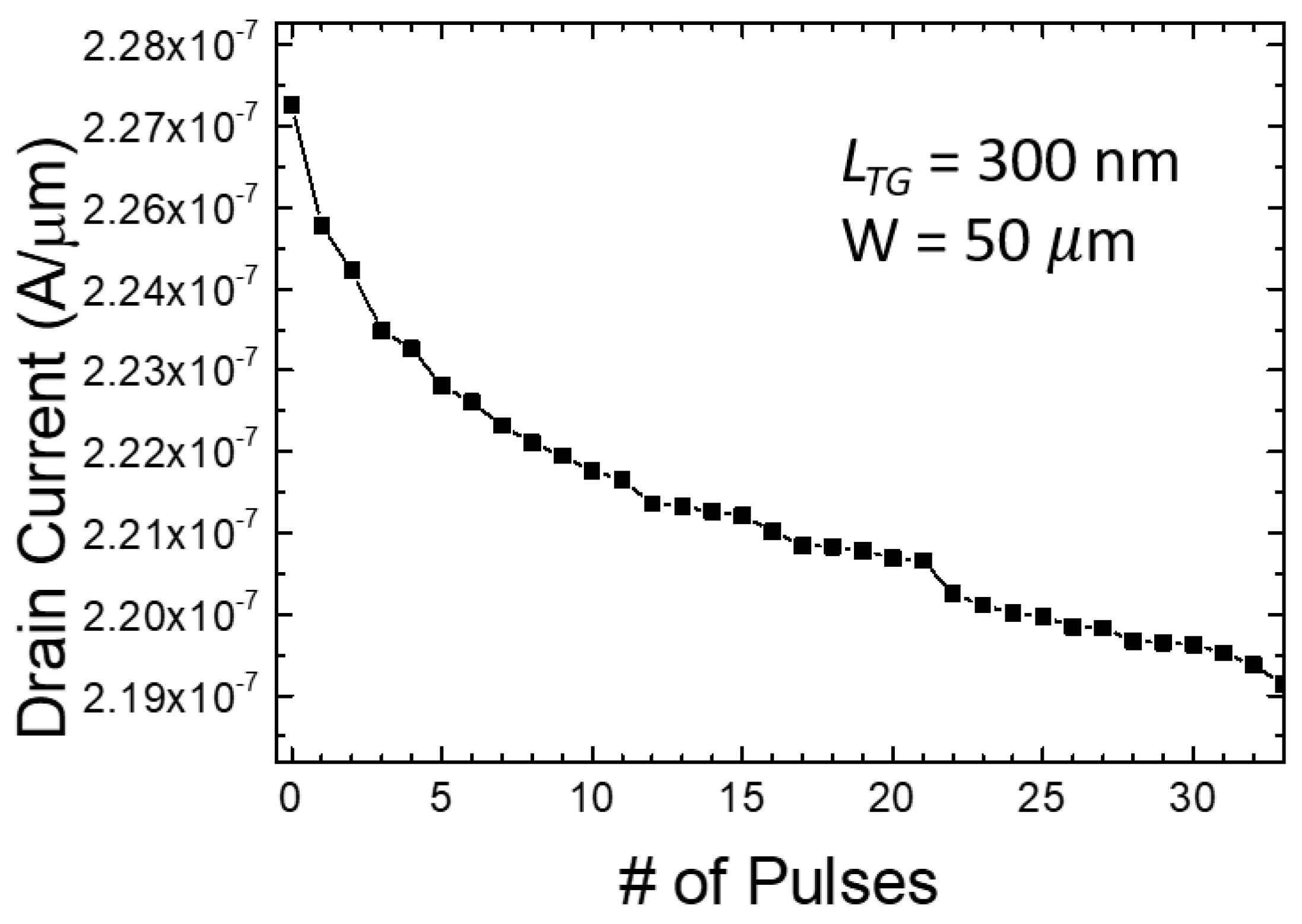

3.3.1. Synaptic Weight Update by Hot Carrier Injection

3.3.2. Synaptic Weight Update by Fowler–Nordheim Tunneling

3.4. Performance Benchmark

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Krizhevsky, A.; Sutskever, I.; Hinton, G.E. ImageNet classification with deep convolutional neural networks. In Proceedings of the Advances in Neural Information Processing Systems (NIPS) 25, Lake Tahoe, NV, USA, 3–6 December 2012; pp. 1097–1105. [Google Scholar]

- Kang, H.; Schuman, E. Long-lasting neurotrophin-induced enhancement of synaptic transmission in the adult hippocampus. Science 1995, 267, 1658–1662. [Google Scholar] [CrossRef] [PubMed]

- Veletic, M.; Balasingham, I. An information theory of neuro-transmission in multiple-access synaptic channels. IEEE Trans. Commun. 2020, 68, 841–853. [Google Scholar] [CrossRef]

- Yan, Z.; Rein, B. Mechanisms of synaptic transmission dysregulation in the prefrontal cortex: Pathophysiological implications. Mol. Psychiatry 2022, 27, 445–465. [Google Scholar] [CrossRef] [PubMed]

- Xie, R.-G.; Chu, W.-G.; Liu, D.-L.; Wang, X.; Ma, S.-B.; Wang, F.; Wang, F.-D.; Lin, Z.; Wu, W.-B.; Lu, N.; et al. Presynaptic NMDARs on spinal nociceptor terminals state-dependently modulate synaptic transmissions and pain. Nat. Commun. 2022, 13, 728. [Google Scholar] [CrossRef] [PubMed]

- Morozov, A.Y.; Abgaryan, K.K.; Reviznikov, D.L. Mathematical model of a neuromorphic network based on memristive elements. Chaos Solitons Fractals 2021, 143, 110548. [Google Scholar] [CrossRef]

- Werner, T.; Vianello, E.; Bichler, O.; Grossi, A.; Nowak, E.; Nodin, J.-F.; Yvert, B.; DeSalvo, B.; Perniola, L. Experimental demonstration of short and long term synaptic plasticity using OxRAM multi k-bit arrays for reliable detection in highly noisy input data. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 16.6.1–16.6.4. [Google Scholar]

- Wang, Z.Q.; Xu, H.Y.; Li, X.H.; Yu, H.; Liu, Y.C.; Zhu, X.J. Synaptic learning and memory functions achieved using oxygen ion migration/diffusion in an amorphous InGaZnO memristor. Adv. Funct. Mater. 2012, 22, 2759–2765. [Google Scholar] [CrossRef]

- Kim, T.-H.; Kim, S.; Hong, K.; Park, J.; Youn, S.; Lee, J.-H.; Park, B.-G.; Kim, H. Effect of program error in memristive neural network with weight quantization. IEEE Trans. Electron Devices 2022, 69, 3151–3157. [Google Scholar] [CrossRef]

- Oh, S.; Huang, Z.; Shi, Y.; Kuzum, D. The impact of resistance drift of phase change memory (PCM) synaptic devices on artificial neural network performance. IEEE Electron Device Lett. 2019, 40, 1325–1328. [Google Scholar] [CrossRef]

- Bianchi, S.; Munoz-Martin, I.; Hashemkhani, S.; Pedretti, G.; Ielmini, D. A bio-inspired recurrent neural network with self-adaptive neurons and PCM synapses for solving reinforcement learning tasks. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 10–21 October 2020; pp. 1–5. [Google Scholar]

- Kang, M.; Park, J. Peripheral circuit optimization with precharge technique of spin transfer torque MRAM synapse array. In Proceedings of the International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC), Jeju, South Korea, 25–28 June 2021; pp. 1–3. [Google Scholar]

- Feng, Y.; Huang, P.; Zhao, Y.; Shan, Y.; Zhang, Y.; Zhou, Z.; Liu, L.; Liu, X.; Kang, J. Improvement of state stability in multi-level resistive random-access memory (RRAM) array for neuromorphic computing. IEEE Electron Device Lett. 2021, 42, 1168–1171. [Google Scholar] [CrossRef]

- Kim, S.; Park, J.; Kim, T.-H.; Hong, K.; Hwang, Y.; Park, B.-G.; Kim, H. 4-bit multilevel operation in overshoot suppressed Al2O3/TiOx RRAM crossbar array. Adv. Intell. Syst. 2022, 4, 2100273. [Google Scholar] [CrossRef]

- Lee, G.H.; Kim, T.-H.; Song, M.S.; Park, J.; Kim, S.; Hong, K.; Kim, Y.; Park, B.-G.; Kim, H. Effect of weight overlap region on neuromorphic system with memristive synaptic devices. Chaos Solitons Fractals 2022, 157, 111999. [Google Scholar] [CrossRef]

- Li, Y.; Ang, K.-W. Hardware implementation of neuromorphic computing using large-scale memristor crossbar arrays. Adv. Intell. Syst. 2021, 3, 2000137. [Google Scholar] [CrossRef]

- Kim, T.-H.; Kim, S.; Hong, K.; Kim, H.; Park, B.-G. Enhanced current-voltage nonlinearity by controlling oxygen concentration of TiOx buffer layer for RRAM passive crossbar array. J. Semicond. Technol. Sci. 2022, 22, 417–425. [Google Scholar] [CrossRef]

- Jeon, K.; Kim, J.; Ryu, J.J.; Yoo, S.-J.; Song, C.; Yang, M.K.; Jeong, D.S.; Kim, G.H. Self-rectifying resistive memory in passive crossbar arrays. Nat. Commun. 2021, 12, 2968. [Google Scholar] [CrossRef]

- Kim, H.; Mahmoodi, M.; Nili, H.; Strukov, D.B. 4K-memristor analog-grade passive crossbar circuit. Nat. Commun. 2021, 12, 5198. [Google Scholar] [CrossRef] [PubMed]

- Hsieh, E.; Zheng, X.; Le, B.; Shih, Y.; Radway, R.; Nelson, M.; Mitra, S.; Wong, S. Four-bits-per-memory one-transistor-and-eight-resistive-random-access-memory (1T8R) array. IEEE Electron Device Lett. 2021, 42, 335–338. [Google Scholar] [CrossRef]

- Kim, T.-H.; Hong, K.; Kim, S.; Park, J.; Youn, S.; Lee, J.-H.; Park, B.-G.; Kim, H.; Choi, W.Y. Fuse devices for pruning in memristive neural network. IEEE Electron Device Lett. 2023, 44, 520–523. [Google Scholar] [CrossRef]

- Hwang, S.; Yu, J.; Lee, G.H.; Song, M.S.; Chang, J.; Min, K.K.; Jang, T.; Lee, J.-H.; Park, B.-G.; Kim, H. Capacitor-based synaptic devices for hardware spiking neural networks. IEEE Electron Device Lett. 2022, 43, 549–552. [Google Scholar] [CrossRef]

- Wang, Y.; Yin, L.; Huang, W.; Li, Y.; Huang, S.; Zhu, Y.; Yang, D.; Pi, X. Optoelectronic synaptic devices for neuromorphic computing. Adv. Intell. Syst. 2021, 3, 2000099. [Google Scholar] [CrossRef]

- Li, S.; Lyu, H.; Li, J.; He, Y.; Gao, X.; Wan, Q.; Shi, Y.; Pan, L. Multiterminal ionic synaptic transistor with artificial blink reflex function. IEEE Electron Device Lett. 2021, 42, 351–354. [Google Scholar] [CrossRef]

- Lee, S.-T.; Lim, S.; Choi, N.Y.; Bae, J.-H.; Kwon, D.; Park, B.-G.; Lee, J.-H. Operation scheme of multi-layer neural networks using nand flash memory as high-density synaptic devices. IEEE J. Electron Devices Soc. 2019, 7, 1085–1093. [Google Scholar] [CrossRef]

- Seo, Y.-T.; Kwon, D.; Noh, Y.; Lee, S.; Park, M.-K.; Woo, S.Y.; Park, B.-G.; Lee, J.-H. 3-D AND-type flash memory architecture with high-k gate dielectric for high-density synaptic devices. IEEE Trans. Electron Devices 2021, 68, 3801–3806. [Google Scholar] [CrossRef]

- Park, Y.J.; Kwon, H.T.; Kim, B.; Lee, W.J.; Wee, D.H.; Choi, H.-S.; Park, B.-G.; Lee, J.-H.; Kim, Y. 3-D stacked synapse array based on charge-trap flash memory for implementation of deep neural networks. IEEE Trans. Electron Devices 2018, 66, 420–427. [Google Scholar] [CrossRef]

- Lee, I.; Kim, D.H.; Kang, D.; Cho, I.H. Investigation of poly silicon channel variation in vertical 3D NAND flash memory. IEEE Access 2022, 10, 108067–108074. [Google Scholar] [CrossRef]

- Keithley Model 4200-SCS Semiconductor Characterization System User Manual. 4200-900-01 Rev. K. February 2017. Available online: https://download.tek.com/manual/4200-900-01K_Feb2017_User.pdf (accessed on 23 July 2023).

- Ho, V.M.; Lee, J.-A.; Martin, K.C. The cell biology of synaptic plasticity. Science 2011, 334, 623–628. [Google Scholar] [CrossRef] [PubMed]

- Regehr, W.G. Short-term presynaptic plasticity. Cold Spring Harb. Perspect. Biol. 2012, 4, a005702. [Google Scholar] [CrossRef]

- Habets, R.L.P.; Borst, J.G.G. An increase in calcium influx contributes to post-tetanic potentiation at the rat calyx of held synapse. J. Neurophysiol. 2006, 96, 2868–2876. [Google Scholar] [CrossRef]

- Fioravante, D.; Myoga, M.H.; Leitges, M.; Regehr, W.G. Adaptive regulation maintains posttetanic potentiation at cerebellar granule cell synapses in the absence of calcium-dependent PKC. J. Neurosci. 2012, 32, 13004–13009. [Google Scholar] [CrossRef][Green Version]

- Kim, J.; Rim, T.; Lee, J.; Baek, C.-K.; Meyyappan, M.; Lee, J.-S. Threshold voltage variations due to oblique single grain boundary in sub-50-nm polysilicon channel. IEEE Trans. Electron Devices 2014, 61, 2705–2710. [Google Scholar]

- Amit, I.; Englander, D.; Horvitz, D.; Sasson, Y.; Rosenwaks, Y. Density and energy distribution of interface states in the grain boundaries of polysilicon nanowire. Nano Lett. 2014, 14, 6190–6194. [Google Scholar] [CrossRef]

- Oh, H.; Kim, J.; Lee, J.; Rim, T.; Baek, C.-K.; Lee, J.-S. Effects of single grain boundary and random interface traps on electrical variations of sub-30-nm polysilicon nanowire structures. Microelectron. Eng. 2016, 149, 113–116. [Google Scholar] [CrossRef]

- Walker, P.M.; Mizuta, H.; Uno, S.; Furuta, Y.; Hasko, D.G. improved off-current and subthreshold slope in aggressively scaled poly-Si TFTs with a single grain boundary in the channel. IEEE Trans. Electron Devices 2004, 51, 212–219. [Google Scholar] [CrossRef]

- Wang, P.-Y.; Tsui, B.-Y. A Novel approach using discrete grain-boundary traps to study the variability of 3-D vertical-gate NAND flash memory cells. IEEE Trans. Electron Devices 2015, 62, 2488–2493. [Google Scholar] [CrossRef]

- Kimura, M.; Yoshino, T.; Harada, K. Complete extraction of trap densities in poly-Si thin-film transistors. IEEE Trans. Electron Devices 2010, 57, 3426–3433. [Google Scholar] [CrossRef]

- Grant, W.N. Electron and hole ionization rates in epitaxial silicon at high electric fields. Solid State Electron. 1973, 16, 1189–1203. [Google Scholar] [CrossRef]

- Massey, D.J.; David, J.P.R.; Rees, G.J. Temperature dependence of impact ionization in submicrometer silicon devices. IEEE Trans. Electron Devices 2006, 53, 2328–2334. [Google Scholar] [CrossRef]

- Pavan, P.; Bez, R.; Olivo, P.; Zanoni, E. Flash memory cells-an overview. Proc. IEEE 1997, 85, 1248–1271. [Google Scholar] [CrossRef]

- Kim, H.; Park, J.; Kwon, M.-W.; Lee, J.-H.; Park, B.-G. Silicon-based floating-body synaptic transistor with frequency-dependent short- and long-term memories. IEEE Electron Device Lett. 2016, 37, 249–252. [Google Scholar] [CrossRef]

- Micheloni, R.; Crippa, L.; Marelli, A. Inside NAND Flash Memories, 1st ed.; Springer: New York, NY, USA, 2010; pp. 55–88. [Google Scholar]

- Suh, K.-D.; Suh, B.-H.; Lim, Y.-H.; Kim, J.-K.; Choi, Y.-J.; Koh, Y.-N.; Lee, S.-S.; Kwon, S.-C.; Choi, B.-S.; Yum, J.-S.; et al. A 3.3 V 32 Mb NAND flash memory with incremental step pulse programming scheme. IEEE J. Solid-State Circuits 1995, 30, 1149–1156. [Google Scholar]

- Kim, D.-H.; Cho, S.; Li, D.H.; Yun, J.-G.; Lee, J.H.; Lee, G.S.; Kim, Y.; Shim, W.B.; Park, S.H.; Kim, W.; et al. Program/erase model of nitride-based NAND-type charge trap flash memories. Jpn. J. Appl. Phys. 2010, 59, 084301. [Google Scholar] [CrossRef]

- Jeon, S.; Han, J.H.; Lee, J.H.; Choi, S.; Hwang, H.; Kim, C. High work-function metal gate and high-k dielectrics for charge trap flash memory devices applications. IEEE Trans. Electron Devices 2005, 52, 2654–2659. [Google Scholar] [CrossRef]

- Jeon, S.; Han, J.H.; Lee, J.; Choi, S.; Hwang., H.; Kim, C. Impact of metal work function on memory properties of charge-trap flash memory devices using Fowler-Nordheim P/E mode. IEEE Electron Device Lett. 2006, 27, 486–488. [Google Scholar] [CrossRef]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit cost scalable technology with punch and plug process for ultra high density flash memory. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15. [Google Scholar]

- Kim, S.S.; Yong, S.K.; Kim, W.; Kang, S.; Park, H.W.; Yoon, K.J.; Sheen, D.S.; Lee, S.; Hwang, C.S. Review of semiconductor flash memory devices for material and process issues. Adv. Mater. 2022, 2200659. [Google Scholar] [CrossRef] [PubMed]

- Wu, W.; Wu, H.; Gao, B.; Yao, P.; Zhang, X.; Peng, X.; Yu, S.; Qian, H. A Methodology to improve linearity of analog RRAM for neuromorphic computing. In Proceedings of the IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 103–104. [Google Scholar]

- Kim, W.; Bruce, R.L.; Masuda, T.; Fraczak, G.W.; Gong, N.; Adusumilli, P.; Ambrogio, S.; Tsai, H.; Bruley, J.; Han, J.-P.; et al. Confined PCM-based analog synaptic devices offering low resistance-drift and 1000 programmable states for deep learning. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T66–T67. [Google Scholar]

| Device Type | ReRAM (ETML/HfOx) [51] | PCM (GST) [52] | Polysilicon Flash (ONO) [26] | This Work |

|---|---|---|---|---|

| RON | ||||

| On/Off ratio | 10 | 12.5 | 62.2 | ~106 |

| Number of multi-level weight states | 7 bit | 10 bit | 4 bit | 5 bit |

| Area | 21.17 mm2 | 22.18 mm2 | 33.27 mm2 | 55.45 mm2 |

| Operating voltage | 1.6 V | ~2 V | 3 V | 1 V |

| Power consumption | W | W | 16.8 nW | W |

| SET pulse | 50 ns | 100 ns | s | 1 ms |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Baek, M.-H.; Kim, H. Polysilicon-Channel Synaptic Transistors for Implementation of Short- and Long-Term Memory Characteristics. Biomimetics 2023, 8, 368. https://doi.org/10.3390/biomimetics8040368

Baek M-H, Kim H. Polysilicon-Channel Synaptic Transistors for Implementation of Short- and Long-Term Memory Characteristics. Biomimetics. 2023; 8(4):368. https://doi.org/10.3390/biomimetics8040368

Chicago/Turabian StyleBaek, Myung-Hyun, and Hyungjin Kim. 2023. "Polysilicon-Channel Synaptic Transistors for Implementation of Short- and Long-Term Memory Characteristics" Biomimetics 8, no. 4: 368. https://doi.org/10.3390/biomimetics8040368

APA StyleBaek, M.-H., & Kim, H. (2023). Polysilicon-Channel Synaptic Transistors for Implementation of Short- and Long-Term Memory Characteristics. Biomimetics, 8(4), 368. https://doi.org/10.3390/biomimetics8040368