Digital System Performance Enhancement of a Tent Map-Based ADC for Monitoring Photovoltaic Systems

Abstract

:1. Introduction

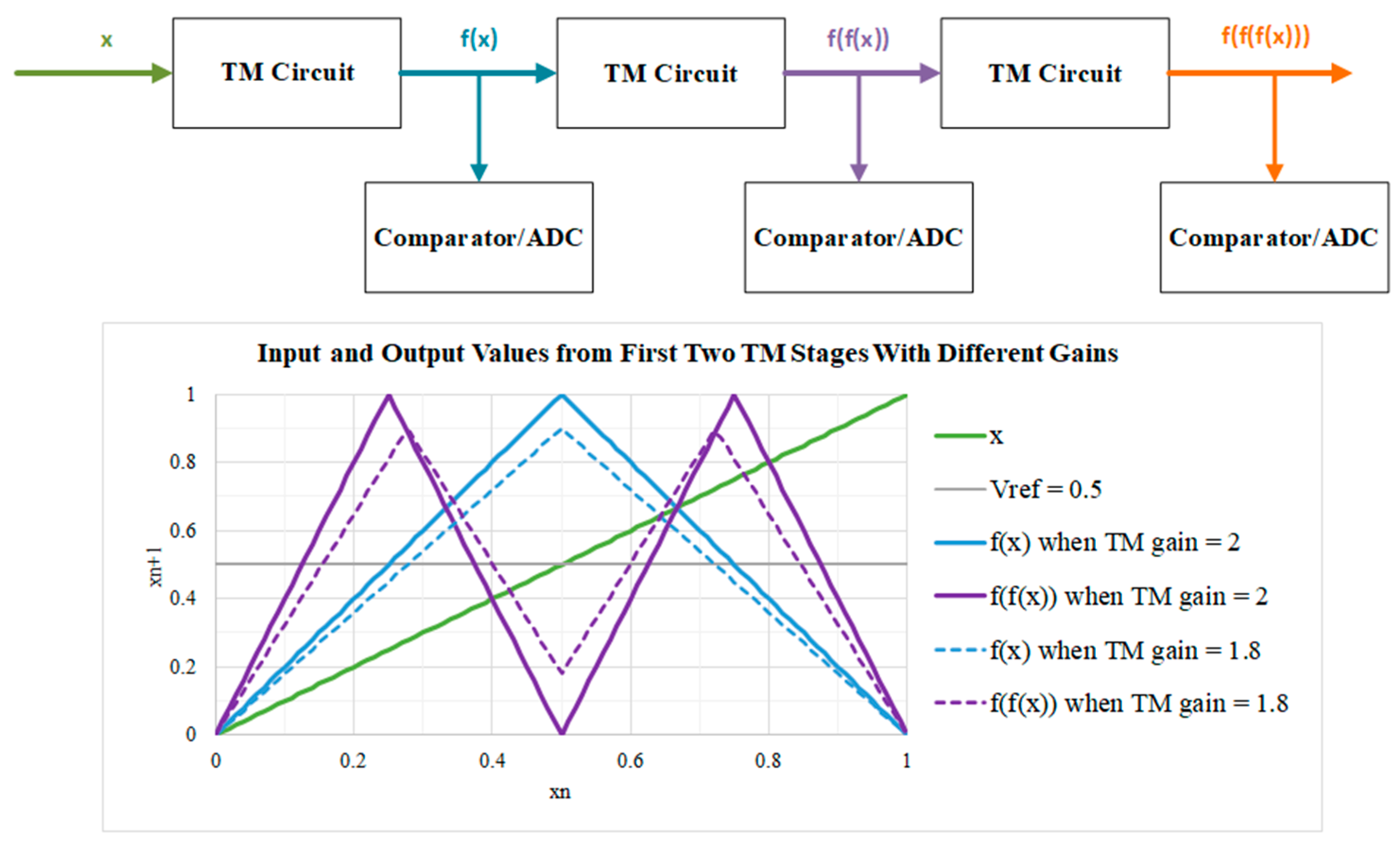

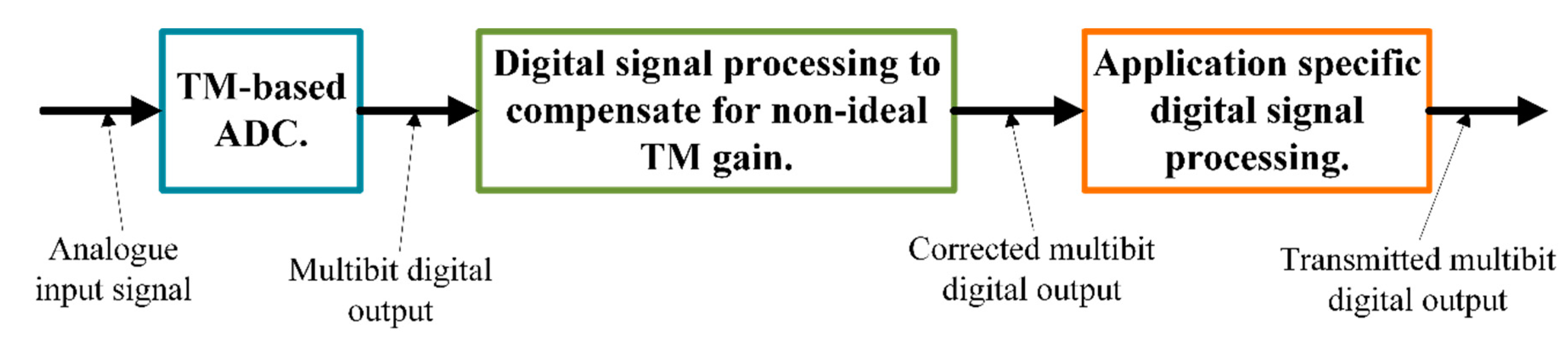

2. Materials and Methods

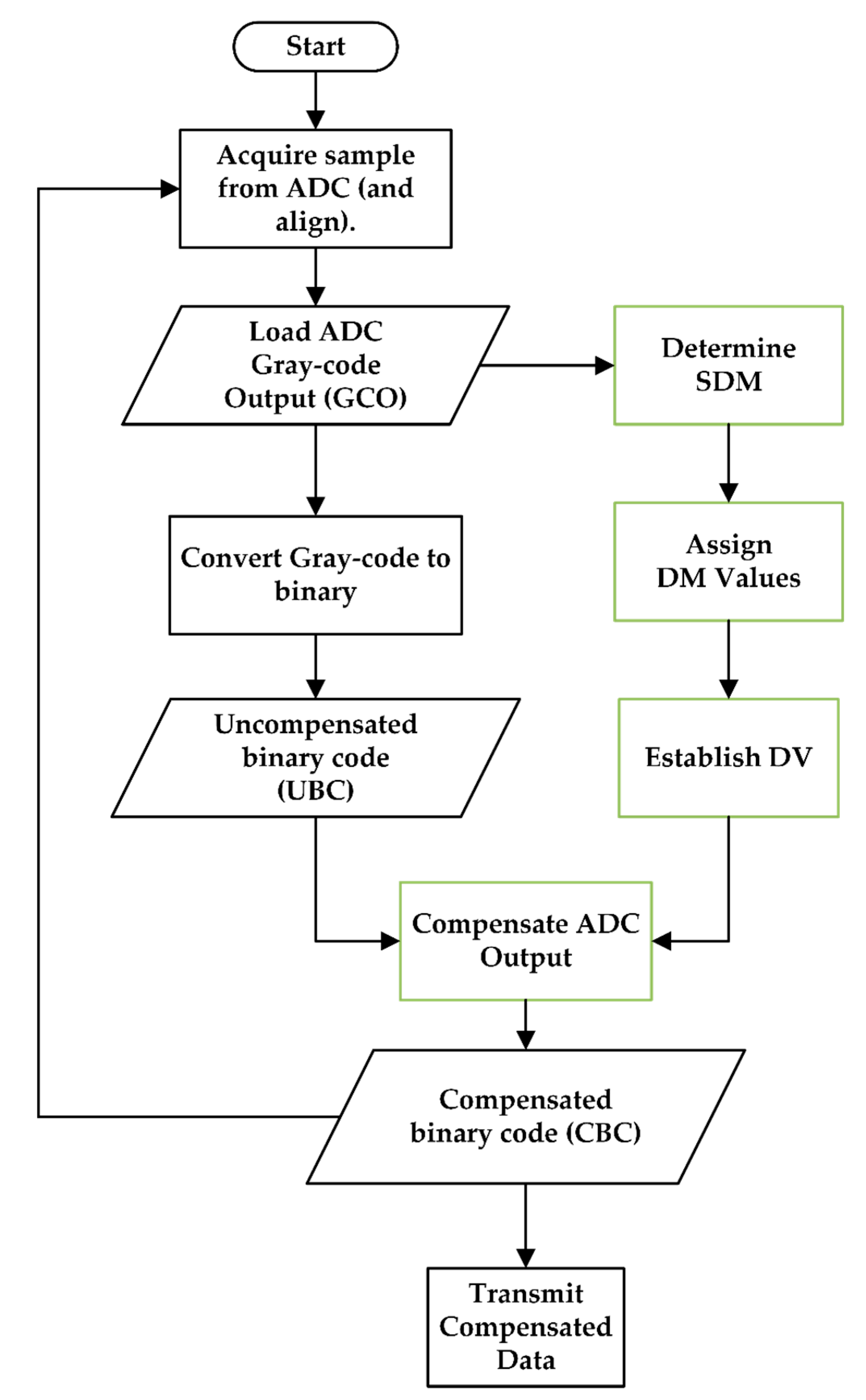

2.1. The Compensation Algorithm

- Determine the sign for difference measure (SDM) to establish the direction of difference between the ideal output and that due to the non-ideal gain for each TM stage.

- Calculate the difference measure (DM) to determine the magnitude of difference between the ideal output and that due to the non-ideal gain for each TM stage.

- Compute the difference value (DV), which provides the overall magnitude and direction of the cumulative difference between the non-ideal gain of the TM based ADC output and the ideal.

- Compensate the ADC output.

2.2. Methodology

2.2.1. Analysis of the Algorithm

2.2.2. FPGA Implementation

2.2.3. Comparison with Basu et al.’s Method

2.2.4. Approximation of Difference Values

2.2.5. Sensitivity Analysis of Algorithm

3. Results

3.1. Analysis of the Algorithm

3.2. FPGA Implementation

3.3. Comparison with Basu et al.’s Method

3.4. Approximation of Difference Values.

3.5. Sensitivity Analysis of Algorithm

4. Discussion and Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Appendix A. List of Acronyms and Symbols

| Acronyms and Symbols | Meaning |

|---|---|

| ADC | Analogue-to-Digital Converter. A device that samples an analogue signal and digitizes the acquired data [23]. |

| BESS | Battery Energy Storage System. Enables excess electrical energy from a PV system to be stored. When the PV system is unable to generate enough energy to supply connected loads, then the stored energy can be released to meet the demand [3]. |

| CBC | Compensated Binary Code. |

| DAQ | Data Acquisition. This is a process where electrical signals, representing real world physical phenomena, are measured and digitize for further processing [24]. |

| DM | Difference Measure |

| DV | Difference Value |

| FPGA | Field Programmable Gate Array. A two-dimensional array of logic cells which can be configured to produce highly complex digital electronic circuits [25]. |

| GCO | Gray Code Output. |

| LSB | Least Significant Bit [26]. |

| MSB | Most Significant Bit [26]. |

| n stage | Number of TM stages employed. |

| PV | Photovoltaic [27]. |

| SDM | Sign for Difference Measure. |

| SoC | State of Charge. The percentage of charge being stored by a battery relative to its capacity [4]. |

| TM | Tent Map. A type of one-dimensional, discrete chaotic map [9]. |

| UBC | Uncompensated Binary Code. |

| Vcc | In the context of this paper, it is the maximum of the valid input voltage range for the TM-based ADC. |

| Vee | In the context of this paper, it is the minimum of the valid input voltage range for the TM-based ADC. |

| VHDL | Very high speed integrated circuits Hardware Description Language. This language enables digital electronic systems to be described [28]. |

| xn | In the context of this paper, it is the input value supplied to a TM. |

| xn+1 | In the context of this paper, it is the output value given by a TM. |

| µ | In the context of this paper, it is the TM gain. |

| µADC | The TM gain of the TM-based ADC. |

| µc | Referring to the Scalar Approximation Method (Section 2.2.4), it is the actual TM gain of the TM circuit. |

| µo | Referring to the Scalar Approximation Method (Section 2.2.4), it is the TM gain used to calculate the DM values suing Equation (2). |

| Term | Meaning |

|---|---|

| Initial Conditions | The initial state of a chaotic system (e.g., control parameters and input values) [9]. |

| Straight-Line and Error Approximation Method | A method proposed (see Section 2.2.4) in this paper to approximate the DM values employed by the algorithm. |

| Scalar Approximation Method | A method proposed (see Section 2.2.4) in this paper to approximate the DM values employed by the algorithm. |

References

- Bashir, S.; Ali, S.; Ahmed, S.; Kakkar, V. Analog-to-digital converters: A comparative study and performance analysis. In Proceedings of the 2016 International Conference on Computing, Communication and Automation (ICCCA), Noida, India, 29–30 April 2016; pp. 999–1001. [Google Scholar]

- Çikan, N.N.; Aksoy, M. Analog to Digital Converters Performance Evaluation Using Figure of Merits in Industrial Applications. In Proceedings of the 2016 European Modelling Symposium (EMS), Pisa, Italy, 28–30 November 2016; pp. 205–209. [Google Scholar]

- Zhao, B.; Wang, C.; Zhang, X. Chapter 2 Techniques of Distributed Photovoltaic Generation. In Grid-Integrated and Standalone Photovoltaic Distributed Generation Systems: Analysis, Design, and Control; John Wiley & Sons: Incorporated, NJ, USA, 2017; pp. 17–42. [Google Scholar]

- Hesse, H.C.; Schimpe, M.; Kucevic, D.; Jossen, A. Lithium-Ion Battery Storage for the Grid—A Review of Stationary Battery Storage System Design Tailored for Applications in Modern Power Grids. Energies 2017, 10, 2107. [Google Scholar] [CrossRef] [Green Version]

- Karthikeyan, R.; Parvathy, A.K. Peak Load reduction in micro Smart Grid using Non-Intrusive Load monitoring and Hierarchical Load scheduling. In Proceedings of the 2015 International Conference on Smart Sensors and Systems (IC-SSS), Bangalore, India, 21–23 December 2015; pp. 1–6. [Google Scholar]

- Sangwine, S. Integrated circuits 3. In Electronic Components and Technology, 3rd ed.; CRC Press: Boca Raton, FL, USA, 2007; pp. 31–52. [Google Scholar]

- Berberkic, S. Measurement of Small Signal Variations Using One-Dimensional Chaotic Maps. Ph.D. Thesis, University of Huddersfield, Huddersfield, UK, 2014. [Google Scholar]

- Upton, D.W.; Haigh, R.P.; Mather, P.J.; Lazaridis, P.I.; Mistry, K.; Zaharis, Z.D.; Tachtatzis, C.; Atkinson, R.C. Gated Pipelined Folding ADC based Low Power Sensor for Large-Scale Radiometric Partial Discharge Monitoring. IEEE Sens. J. 2020, 20, 7826–7836. [Google Scholar] [CrossRef] [Green Version]

- Baker, G.L.; Gollub, J.P. Chaotic Dynamics: An Introduction, 2nd ed.; Cambridge University Press: Cambridge, UK, 1996; p. 256. [Google Scholar]

- Liu, J.; Zhang, X.; Li, Z.; Li, X. A tent map based A/D conversion circuit for robot tactile sensor. J. Sens. 2013, 2013, 624981. [Google Scholar] [CrossRef] [Green Version]

- Hazell, P.; Mather, P.; Longstaff, A.; Fletcher, S. A Non-linear Tent Map-Based ADC Design for Sensitive Condition Monitoring Measurement Systems. In COMADEM 2019; Ball, A., Gelman, L., Rao, B.K.N., Eds.; Springer International Publishing: Huddersfield, UK, 2020; pp. 893–902. [Google Scholar]

- Ren, Y.; Lin, H.; Ma, Z.; Shan, X. Performance analysis in general cyclic ADCs. Int. J. Bifurc. Chaos Appl. Sci. Eng. 2003, 13, 2369–2376. [Google Scholar] [CrossRef]

- Ndjountche, T. Nyquist Analog-to-Digital Converters. In CMOS Analog Integrated Circuits: High-Speed and Power-Efficient Design; CRC Press Taylor & Francis Group: Baton Rouge, LA, USA, 2011; pp. 573–650. [Google Scholar]

- Analog Devices Inc. Chapter 9: Hardware Design Techniques. In Data Conversion Handbook, 1st ed.; Kester, W., Ed.; Elsevier Science & Technology: Boston, MA, USA, 2005; pp. 709–894. [Google Scholar]

- Dutta, D.; Basu, R.; Banerjee, S.; Holmes, V.; Mather, P. Parameter estimation for 1D PWL chaotic maps using noisy dynamics. Nonlinear Dyn. 2018, 94, 2979–2993. [Google Scholar] [CrossRef] [Green Version]

- Dinu, A.; Vlad, A. The compound tent map and the connection between gray codes and the initial condition recovery. UPB Sci. Bull. Ser. A Appl. Math. Phys. 2014, 76, 17–28. [Google Scholar]

- Luengo, D.; Santamaría, I. Asymptotically optimal estimators for chaotic digital communications. In Chaotic Signals in Digital Communications, 1st ed.; Eisencraft, M., Romis Attux, R., Suyama, R., Eds.; CRC Press Taylor & Francis Group: Baton Rouge, LA, USA, 2013; Volume 26, pp. 297–324. [Google Scholar]

- Liu, L.; Hu, J.; He, Z.; Han, C.; Lu, C. Chaotic signal reconstruction with application to noise radar system. In Proceedings of the ISPACS 2010—2010 International Symposium on Intelligent Signal Processing and Communication Systems, Chengdu, China, 6–8 December 2010; p. 4. [Google Scholar]

- Xi, C.; Yong, G.; Yuan, Y. A novel method for the initial condition estimation of a tent map. Chin. Phys. Lett. 2009, 26, 078202. [Google Scholar] [CrossRef]

- Litovski, V.; Andrejević, M.; Nikolić, M. Chaos based analog-to-digital conversion of small signals. In Proceedings of the 8th Seminar on Neural Network Applications in Electrical Engineering, Belgrade, Serbia, 25–27 September 2006; pp. 173–176. [Google Scholar]

- Basu, R.; Dutta, D.; Banerjee, S.; Holmes, V.; Mather, P. An Algorithmic Approach for Signal Measurement Using Symbolic Dynamics of Tent Map. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2221–2231. [Google Scholar] [CrossRef]

- Basu, R. Estimation of Input Variable as Initial Condition of a Chaos Based Analogue to Digital Converter. Ph.D. Thesis, University of Huddersfield, Huddersfield, UK, 2018. [Google Scholar]

- Razavi, B. Introduction to Data Conversion and Processing. In Principles of Data Conversion System Design; Blicq, R.S., Eden, M., Etter, D.M., Hoffnagle, G.F., Hoyt, R.F., Irwin, J.D., Kartalopoulos, S.V., Aplante, P., Laub, A.J., et al., Eds.; IEEE Press: New York, NY, USA, 1995; pp. 1–6. [Google Scholar]

- Park, J.; Mackay, S. Introduction. In Practical Data Acquisition for Instrumentation and Control Systems; Elsevier Science & Technology: London, UK, 2003; pp. 1–12. [Google Scholar]

- Storey, N. Implementing Digital Systems. In Electronics: A Systems Approach, 5th ed.; Pearson Education Limited: Harlow, UK, 2013; pp. 687–746. [Google Scholar]

- Bolton, W. 3.1 The Binary System. In Programmable Logic Controllers, 5th ed.; Elsevier: Oxford, UK, 2009; p. 60. [Google Scholar]

- Zhao, B.; Wang, C.; Zhang, X. Chapter 1 Overview. In Grid-Integrated and Standalone Photovoltaic Distributed Generation Systems: Analysis, Design, and Control; John Wiley & Sons: Incorporated, NJ, USA, 2017; pp. 1–16. [Google Scholar]

- Ashenden, P.J. The Student’s Guide to VHDL, 2nd ed.; Morgan Kaufmann/Elsevier: Amsterdam, The Netherlands, 2008. [Google Scholar]

| TM Gain | Difference (Step-Size 1) | Effective Resolution (Nearest Bit) |

|---|---|---|

| 1.9 | ±1543 | 4 |

| 1.99 | ±162 | 7 |

| 2 | ±1 | 15 |

| TM Gain = 2 | TM Gain = 1.8 | |||||

|---|---|---|---|---|---|---|

| x | b2 | b1 | b0 | b2 | b1 | b0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0.1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0.2 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0.3 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0.4 | 0 | 1 | 0 | 0 | 1 | 1 |

| 0.5 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0.6 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0.7 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0.8 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0.9 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hazell, P.; Mather, P.; Longstaff, A.; Fletcher, S. Digital System Performance Enhancement of a Tent Map-Based ADC for Monitoring Photovoltaic Systems. Electronics 2020, 9, 1554. https://doi.org/10.3390/electronics9091554

Hazell P, Mather P, Longstaff A, Fletcher S. Digital System Performance Enhancement of a Tent Map-Based ADC for Monitoring Photovoltaic Systems. Electronics. 2020; 9(9):1554. https://doi.org/10.3390/electronics9091554

Chicago/Turabian StyleHazell, Philippa, Peter Mather, Andrew Longstaff, and Simon Fletcher. 2020. "Digital System Performance Enhancement of a Tent Map-Based ADC for Monitoring Photovoltaic Systems" Electronics 9, no. 9: 1554. https://doi.org/10.3390/electronics9091554

APA StyleHazell, P., Mather, P., Longstaff, A., & Fletcher, S. (2020). Digital System Performance Enhancement of a Tent Map-Based ADC for Monitoring Photovoltaic Systems. Electronics, 9(9), 1554. https://doi.org/10.3390/electronics9091554