10-GHz Fully Differential Sallen–Key Lowpass Biquad Filters in 55nm SiGe BiCMOS Technology

Abstract

:1. Introduction

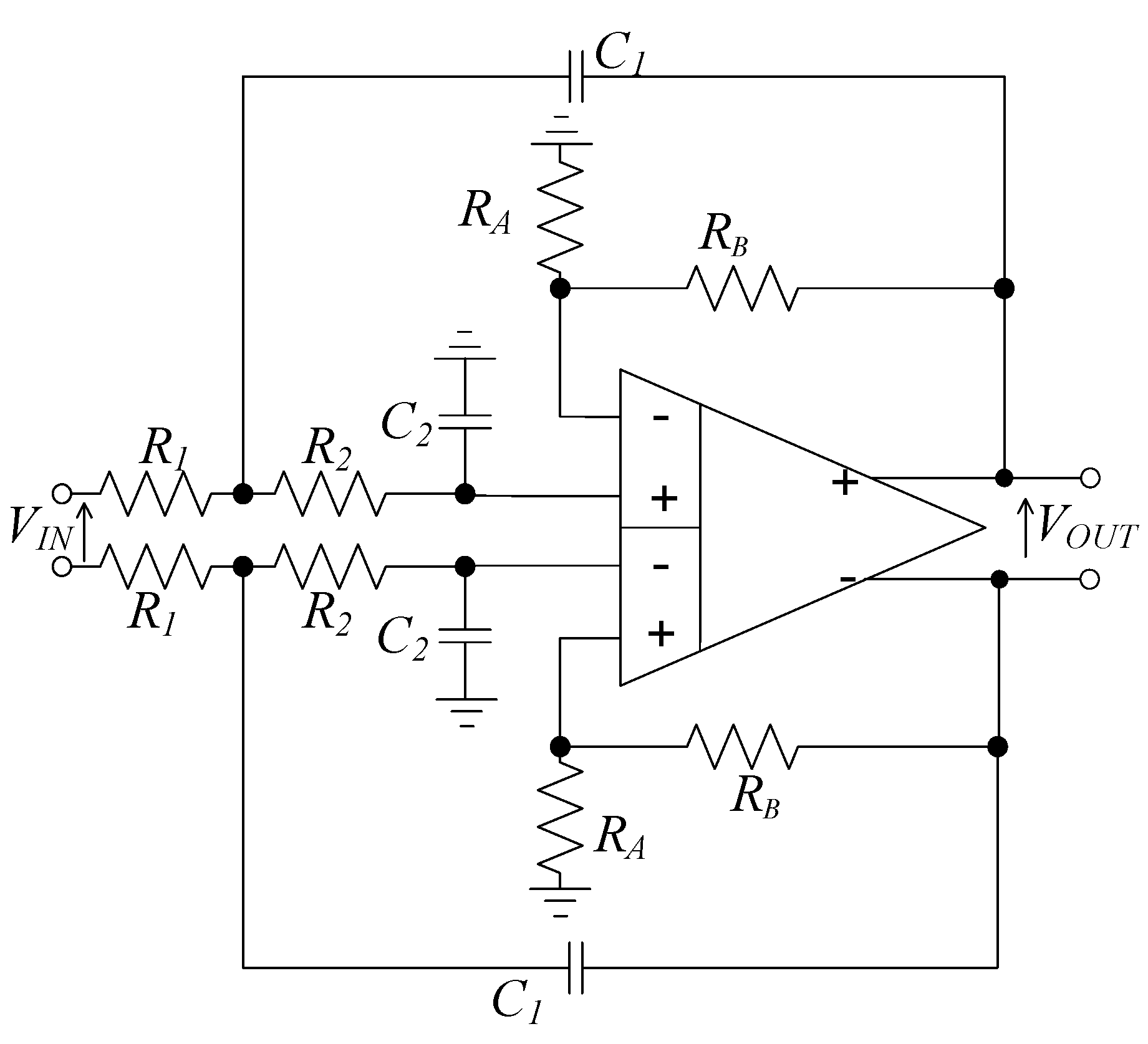

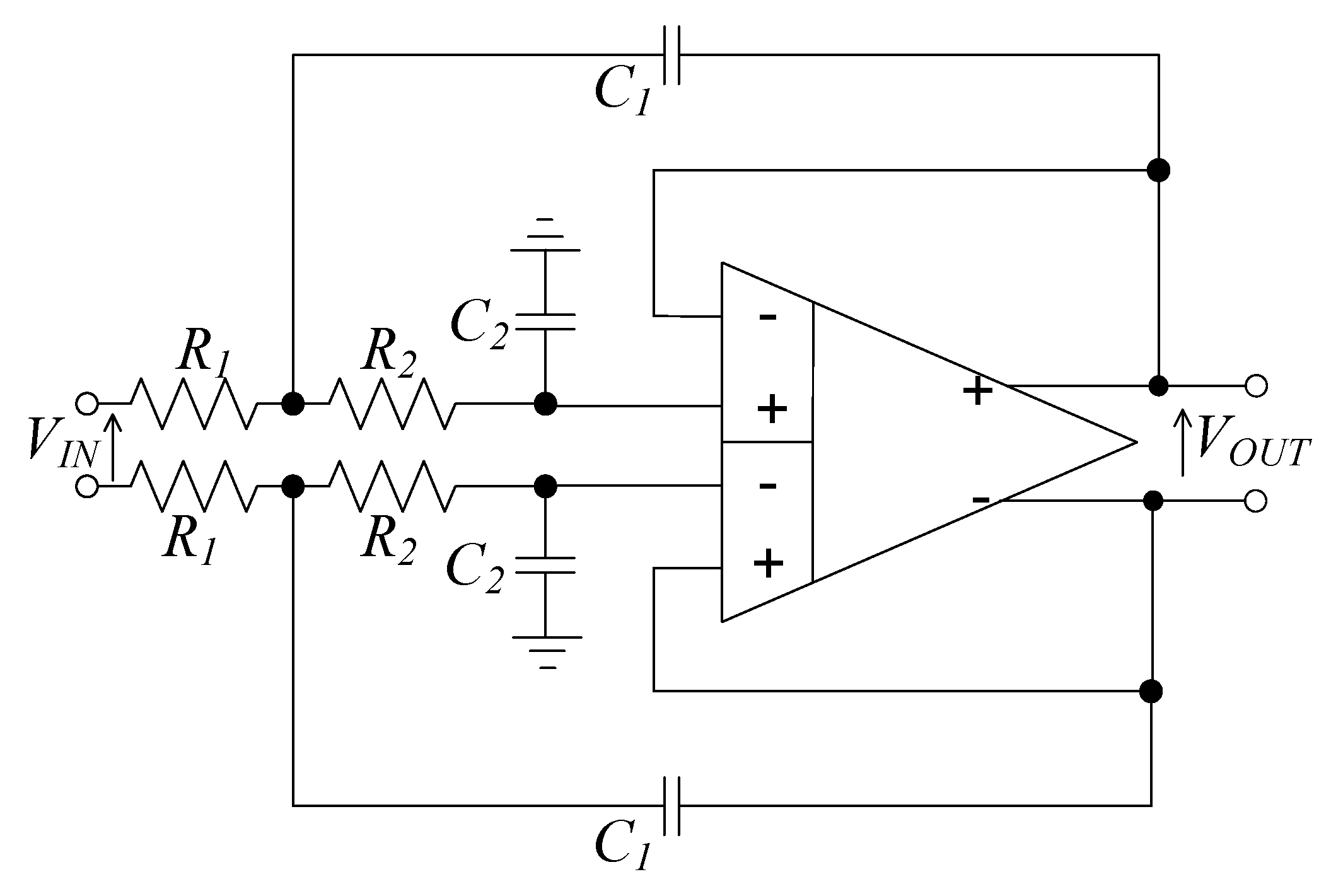

2. Proposed Biquad Architecture

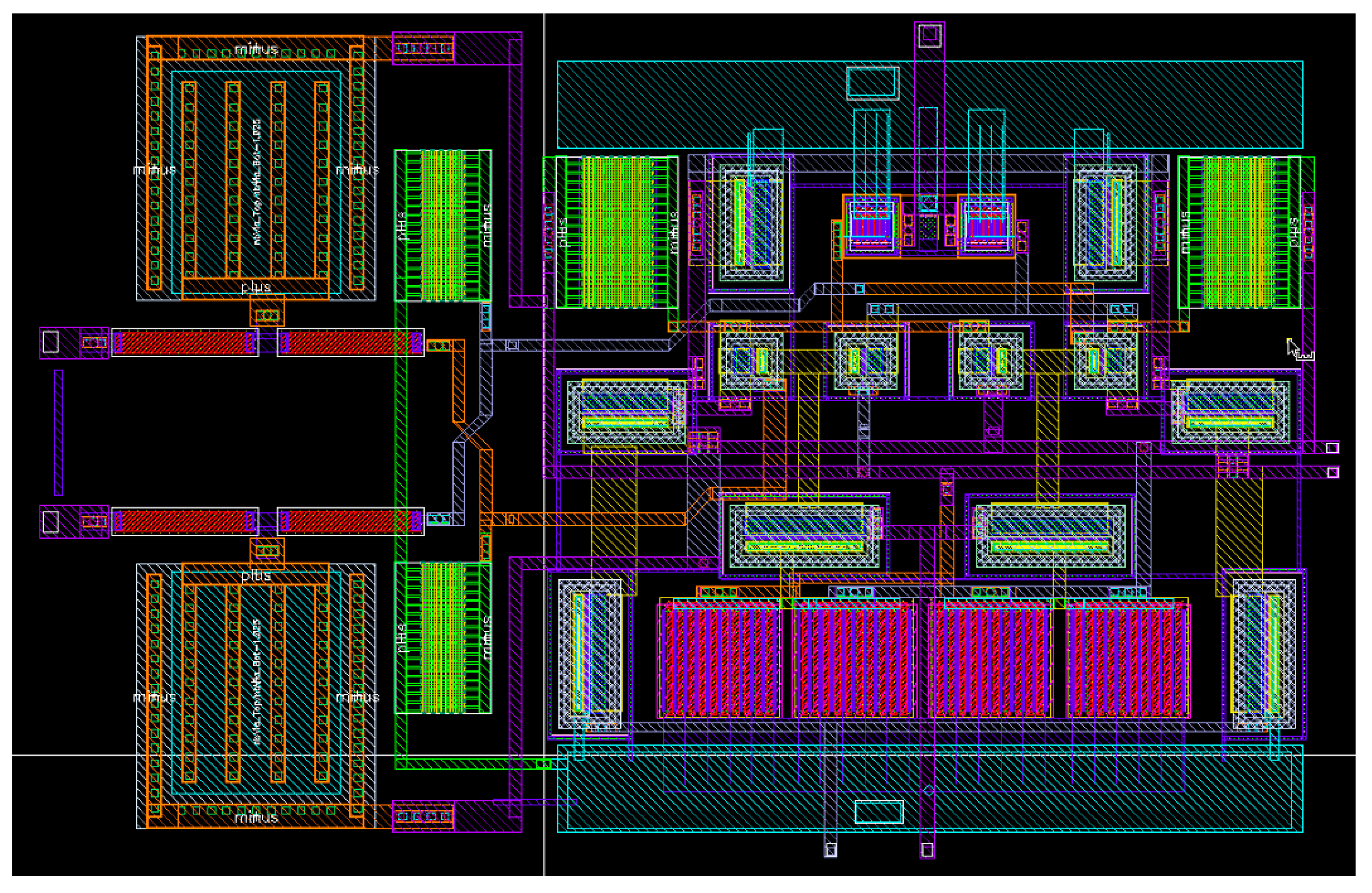

3. Proposed Topology for the DDA amplifier

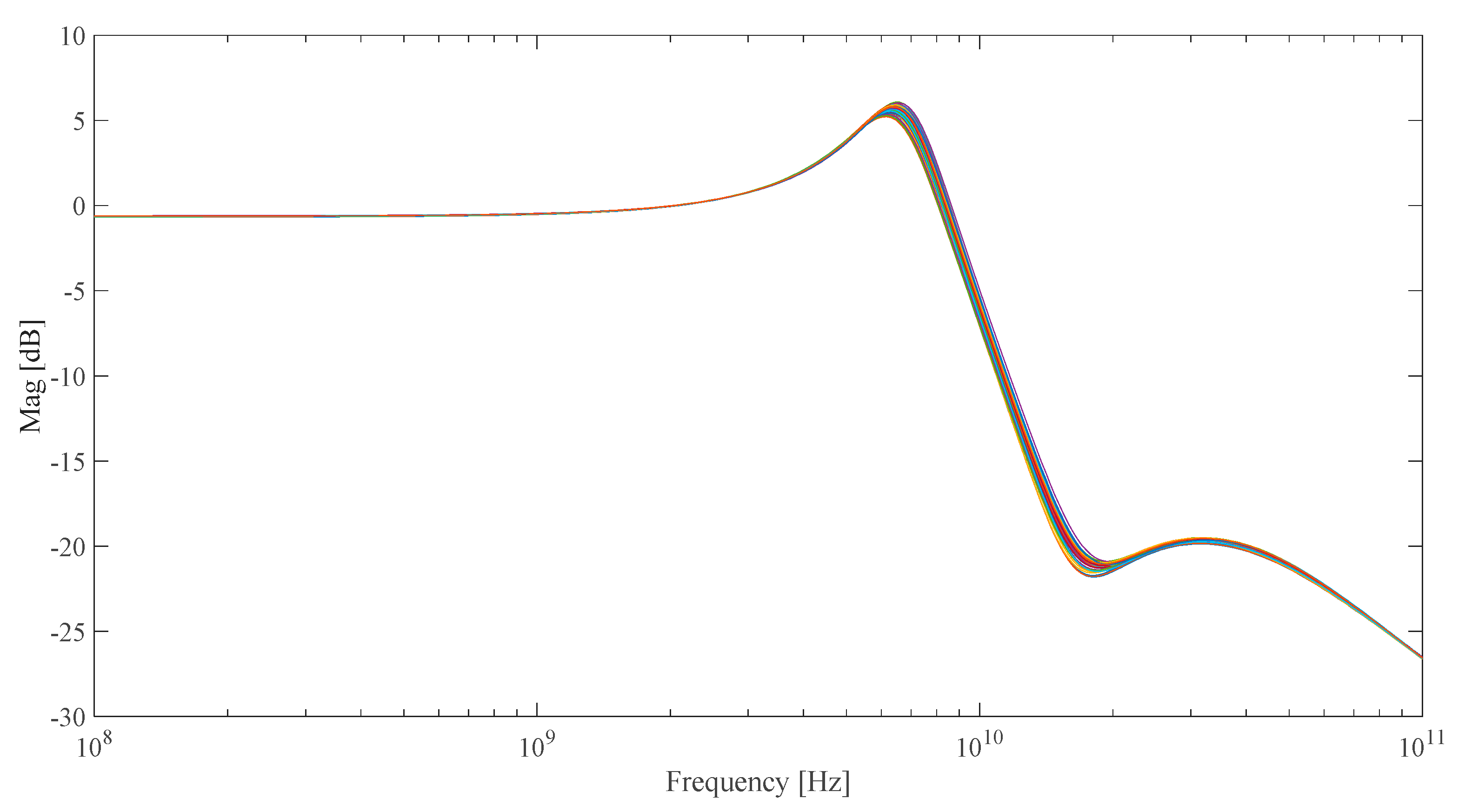

3.1. DDA Amplifier

3.2. Common Mode Feedback Loop

4. Filter Design

5. Simulation Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kim, S.-N.; Kim, W.-C.; Seo, M.-J.; Ryu, S.-T. A 65-nm CMOS 6-Bit 20 GS/s Time-Interleaved DAC With Full-Binary Sub-DACs. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1154–1158. [Google Scholar] [CrossRef]

- Zandieh, A.; Schvan, P.; Voinigescu, S.P. Design of a 55-nm SiGe BiCMOS 5-bit Time-Interleaved Flash ADC for 64-Gbd 16-QAM Fiberoptics Applications. IEEE J. Solid-State Circuits 2019, 54, 2375–2387. [Google Scholar] [CrossRef]

- Sun, K.; Wang, G.; Zhang, Q.; Elahmadi, S.; Gui, P. A 56-GS/s 8-bit Time-Interleaved ADC With ENOB and BW Enhancement Techniques in 28-nm CMOS. IEEE J. Solid-State Circuits 2018, 54, 821–833. [Google Scholar] [CrossRef]

- Monsurrò, P.; Trifiletti, A.; Angrisani, L.; D’Arco, M. Streamline calibration modelling for a comprehensive design of ATI-based digitizers. Measurement 2018, 125, 386–393. [Google Scholar] [CrossRef]

- Monsurrò, P.; Trifiletti, A.; Angrisani, L.; D’Arco, M. Two novel architectures for 4-channel mixing/filtering/processing digitizers. Measurement 2019, 142, 138–147. [Google Scholar] [CrossRef]

- Chen, Y.; Mak, P.-I.; Wang, Y.; Zhang, L.; Qian, H. 0.013 mm2, kHz-to-GHz-bandwidth, third-order all-pole lowpass filter with 0.52-to-1.11 pW/pole/Hz efficiency. Electron. Lett. 2013, 49, 1340–1342. [Google Scholar] [CrossRef]

- Wambacq, P.; Giannini, V.; Scheir, K.; Van Thillo, W.; Rolain, Y. A fifth-order 880MHz/1.76GHz active lowpass filter for 60GHz communications in 40nm digital CMOS. In Proceedings of the ESSCIRC 2010—36th European Solid State Circuits Conference, Seville, Spain, 14–19 September 2010; pp. 350–353. [Google Scholar]

- Wu, C.-D.; Hsieh, J.-Y.; Wu, C.-H.; Cheng, Y.-S.; Wu, C.-C.; Lu, S.-S. An 1.1 v 0.1–1.6 GHz tunable-bandwidth elliptic filter with 6 dB linearity improvement by precise zero location control in 40 nm CMOS technology for 5G applications. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Salem, S.B.; Fakhfakh, M.; Masmoudi, D.S.; Loulou, M.; Loumeau, P.; Masmoudi, N. A high performances CMOS CCII and high frequency applications. Analog. Integr. Circuits Signal Process. 2006, 49, 71–78. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High performance voltage output filter realizations using second generation voltage conveyor. Int. J. RF Microw. Comput. Eng. 2018, 28, e21534. [Google Scholar] [CrossRef]

- Lu, Y.; Krithivasan, R.; Kuo, W.-M.L.; Li, X.; Cressler, J.D.; Gustat, H.; Heinemann, B. A 70 MHz–4.1 GHz 5th-order elliptic gm-C low-pass filter in complementary SiGe technology. In Proceedings of the 2006 Bipolar/BiCMOS Circuits and Technology Meeting, Maastricht, The Netherlands, 8–10 October 2006. [Google Scholar]

- Houfaf, F.; Egot, M.; Kaiser, A.; Cathelin, A.; Nauta, B. A 65nm CMOS 1-to-10GHz tunable continuous-time low-pass filter for high-data-rate communications. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 362–363. [Google Scholar]

- Xiao, H.; Schaumann, R. Very-high-frequency lowpass filter based on a CMOS active inductor. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems, Phoenix-Scottsdale, AZ, USA, 26–29 May 2002. [Google Scholar]

- Centurelli, F.; Monsurrò, P.; Trifiletti, A. A 10 GHz inductorless active SiGe HBT lowpass filter. Int. J. RF Microw. Comput. Eng. 2018, 28, e21567. [Google Scholar] [CrossRef]

- Monsurrò, P.; Pennisi, S.; Scotti, G.; Trifiletti, A. Design strategy for biquad-based continuous-time low-pass filters. In Proceedings of the 20th European Conference on Circuit Theory and Design, Linkoping, Sweden, 29 August 2011; pp. 385–388. [Google Scholar]

- Monsurrò, P.; Pennisi, S.; Scotti, G.; Trifiletti, A. High-tuning-range CMOS band-pass IF filter based on a low-Qcascaded biquad optimization technique. Int. J. Circuit Theory Appl. 2014, 43, 1615–1636. [Google Scholar] [CrossRef]

- Chevalier, P.; Avenier, G.; Canderle, E.; Montagné, A.; Ribes, G.; Vu, V.T. Nanoscale SiGe BiCMOS technologies: From 55 nm reality to 14 nm opportunities and challenges. In Proceedings of the 2015 IEEE Bipolar/BiCMOS Circuits and Technology Meeting – BCTM, Boston, MA, USA, 26–28 October 2015. [Google Scholar]

- Sabatino, N.; Minoia, G.; Roche, M.; Baldi, D.; Temporiti, E.; Mazzanti, A. A 5th Order gm-C Low-Pass Filter with ±3% Cut-Off Frequency Accuracy and 220 MHz to 3.3 GHz Tuning-Range in 28nm LP CMOS. In Proceedings of the IEEE European Solid State Circuits Conference, ESSCIRC 2014, Venice Lido, Italy, 22–26 September 2014; pp. 351–354. [Google Scholar]

- Baranauskas, D.; Zelenin, D.; Bussmann, M.; Elahmadi, S.; Edwards, J.K.; Gill, C.A. A 1.6-3.2-GHz sixth-order +13.1-dBm OIP3 linear phase gm-C filter for fiber-optic EDC receivers. IEEE Trans Microw Theory Tech. 2010, 58, 1314–1322. [Google Scholar] [CrossRef]

| Device | Size | Bias Current |

|---|---|---|

| Q1, Q2, Q3, Q4 | IC = 1 mA | |

| Q5, Q6 | IC = 1 mA | |

| Q7, Q8,Q12 | IC = 1 mA | |

| Q9, Q10 | IC = 1 mA | |

| Q11 | IC = 1 mA | |

| M1, M2 | W/L = 6/0.06 | ID = 1 mA |

| M3,M4,M5,M6 | W/L = 20/0.25 | ID = 1 mA |

| Name | Value | Unit | Notes |

|---|---|---|---|

| 18 | mW | Power Dissipation | |

| 3 | V | Supply Voltage | |

| 6.45 | GHz | Resonant Frequency | |

| 9.55 | GHz | 3 dB Bandwidth | |

| −0.5 | dB | DC-Gain | |

| 5.8 | dB | Peak Gain | |

| 2.06 | - | Quality Factor | |

| SFDR | 64 | dB | @0.8Vpp differential,1 GHz |

| 1.36 | mVrms | Output Noise integrated between 1 Hz and 10 GHz | |

| SNR | 46.4 | [ | @0.8Vpp differential |

| 1 | 49.3 | dB | Dynamic Range |

| FOM1 | 9 | mW | |

| FOM2 | 0.94 | pW/Hz | |

| FOM3 | 0.0032 | mW/GHz |

| Name | Minimum | Maximum | Unit |

|---|---|---|---|

| −30 | 120 | °C | |

| 18.4 | 19.56 | mW | |

| 6.91 | 5.65 | GHz | |

| 10.2 | 8.2 | GHz | |

| 5.51 | 5.3 | dB | |

| −0.53 | −0.58 | dB | |

| 2 | 1.9 | - | |

| SFDR | 61 | 73 | dB |

| 1.12 | 1.51 | mV | |

| 1 | 49.4 | 51.6 | dB |

| Name | Value | Value | Unit |

|---|---|---|---|

| 2.85 | 3.15 | V | |

| 17.1 | 19.9 | mW | |

| 6.1 | 6.4 | GHz | |

| 8.9 | 9.6 | GHz | |

| 4.89 | 5.72 | dB | |

| −0.7 | −0.56 | dB | |

| 1.9 | 2 | - | |

| SFDR | 48 | 56 | dB |

| 1.26 | 1.26 | mV | |

| 1 | 44.3 | 47 | dB |

| Name | Unit | ||

|---|---|---|---|

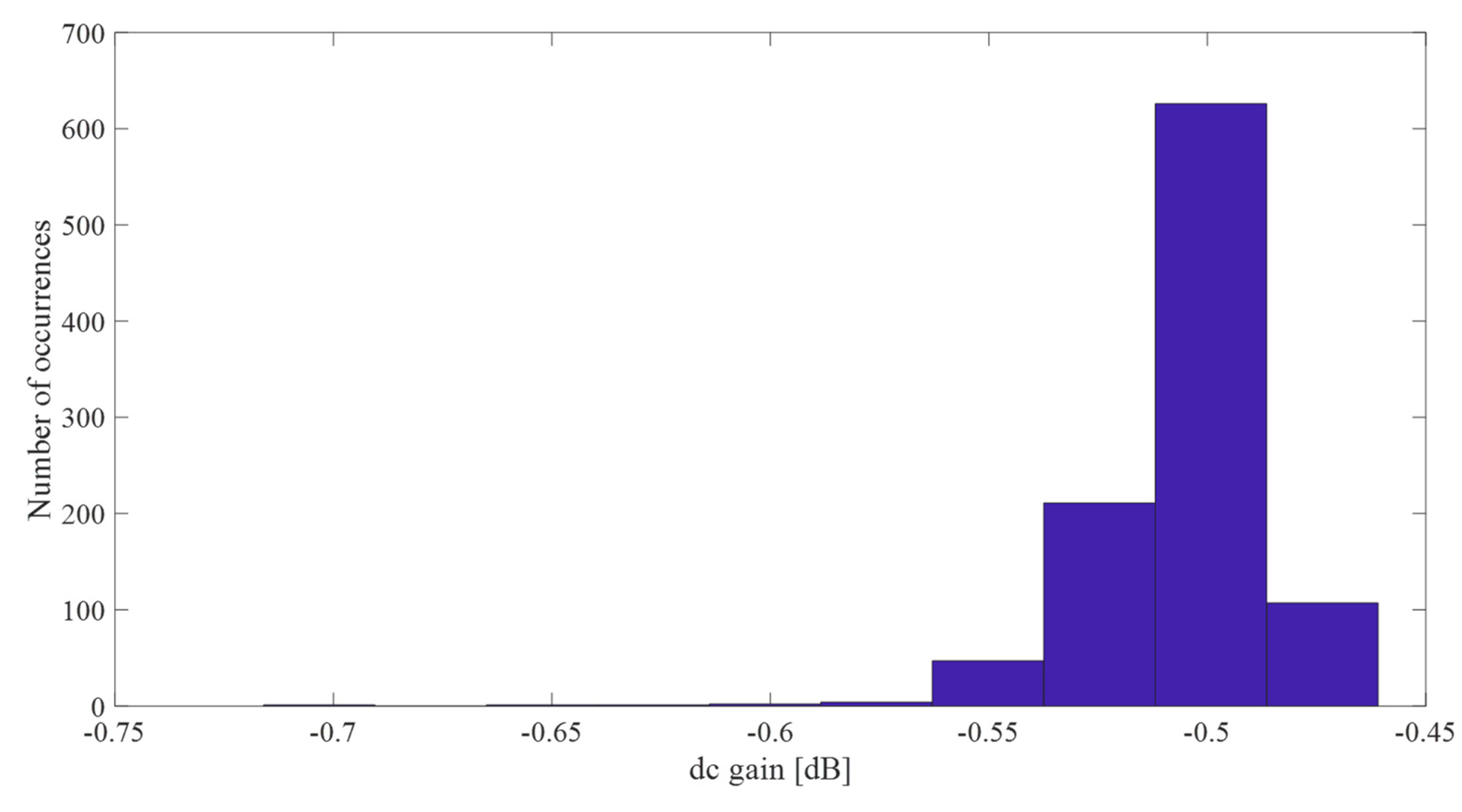

| −0.505 | 0.018 | dB | |

| 2.071 | 0.037 | - | |

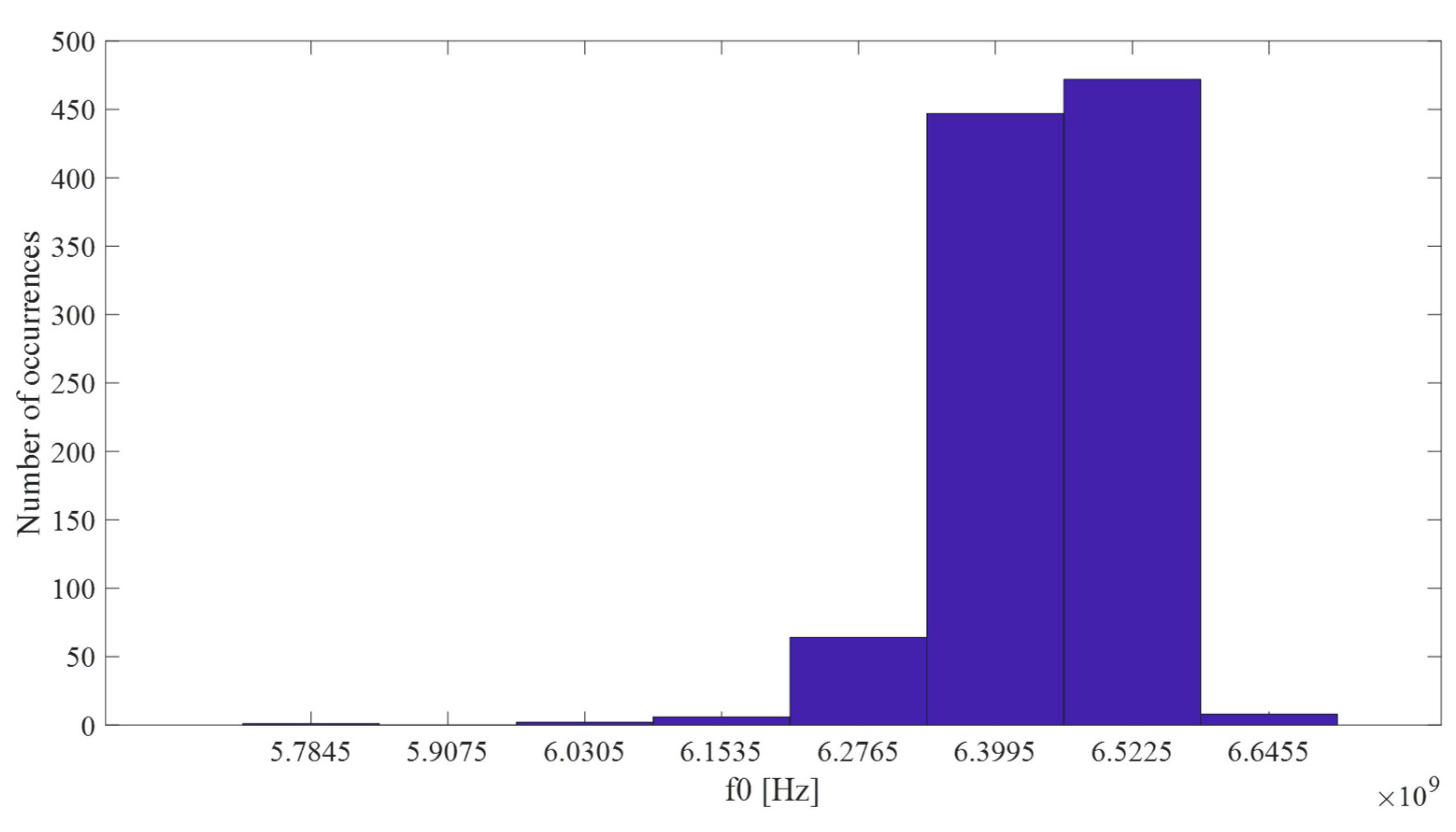

| 6.471 | 0.100 | GHz | |

| 9.588 | 0.126 | dB |

| This Work | [14] | [8] | [18] | [12] | [19] | [11] | [13] | |

|---|---|---|---|---|---|---|---|---|

| Year | 2020 | 2018 | 2017 | 2014 | 2012 | 2010 | 2006 | 2002 |

| Technology | BiCMOS 55 nm | BiCMOS 55 nm | CMOS 40 nm | CMOS 28 nm | CMOS 65 nm | BiCMOS 180 nm | BiCMOS 250 nm | CMOS 180 nm |

| Filter Type | SK | AL | TT | GMC | GMC | GMC | GMC | AL |

| Supply Voltage [ | 3 | 3 | 1.1 | 1.1 | 1.4 | 3.3 | 3.5 | 1.8 |

| [ | 18 | 13.7 | 17.6 | 30 | 140 | 300 | 99.8 | 1.6 |

| [ | 9.55 | 10.5 | 1.6 | 3.3 | 10 | 3.2 | 4.1 | 4.6 |

| SFDR [) | 64 | −51 | −46 | −40 | −45 | 40 | - | −57 |

| [ | 1.36 | 1.1 | 1.5 | - | 0.5 | - | - | - |

| SNR [ | 46.4 | 47.2 | 43.2 | 39 | 45 | - | - | - |

| 1 [ | 49.3 | 45.5 | 41.1 | 37 | 42 | - | 20.1 | - |

| Npole | 2 | 2 | 5 | 5 | 3 | 6 | 5 | 5 |

| FOM1 [ | 9 | 6.85 | 3.52 | 6 | 46.6 | 50 | 19,9 | 0.32 |

| FOM2 [ | 0.94 | 0.65 | 2.2 | 1.81 | 4.7 | 15.6 | 4,8 | 0.07 |

| FOM3[ | 0.0032 | 0.0035 | 0.019 | 0.025 | 0.037 | - | 0.47 | - |

| Area (mm2) | 0.0027 | 0.0056 | 0.12 | 0.091 | 0.01 | 0.17 | 0.82 | - |

| Measured | No | No | Yes | Yes | Yes | No | Yes | Yes |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Centurelli, F.; Monsurrò, P.; Scotti, G.; Tommasino, P.; Trifiletti, A. 10-GHz Fully Differential Sallen–Key Lowpass Biquad Filters in 55nm SiGe BiCMOS Technology. Electronics 2020, 9, 563. https://doi.org/10.3390/electronics9040563

Centurelli F, Monsurrò P, Scotti G, Tommasino P, Trifiletti A. 10-GHz Fully Differential Sallen–Key Lowpass Biquad Filters in 55nm SiGe BiCMOS Technology. Electronics. 2020; 9(4):563. https://doi.org/10.3390/electronics9040563

Chicago/Turabian StyleCenturelli, Francesco, Pietro Monsurrò, Giuseppe Scotti, Pasquale Tommasino, and Alessandro Trifiletti. 2020. "10-GHz Fully Differential Sallen–Key Lowpass Biquad Filters in 55nm SiGe BiCMOS Technology" Electronics 9, no. 4: 563. https://doi.org/10.3390/electronics9040563

APA StyleCenturelli, F., Monsurrò, P., Scotti, G., Tommasino, P., & Trifiletti, A. (2020). 10-GHz Fully Differential Sallen–Key Lowpass Biquad Filters in 55nm SiGe BiCMOS Technology. Electronics, 9(4), 563. https://doi.org/10.3390/electronics9040563