PA-LIRS: An Adaptive Page Replacement Algorithm for NAND Flash Memory

Abstract

1. Introduction

2. Related Works

3. PA-LIRS Algorithm

3.1. Background

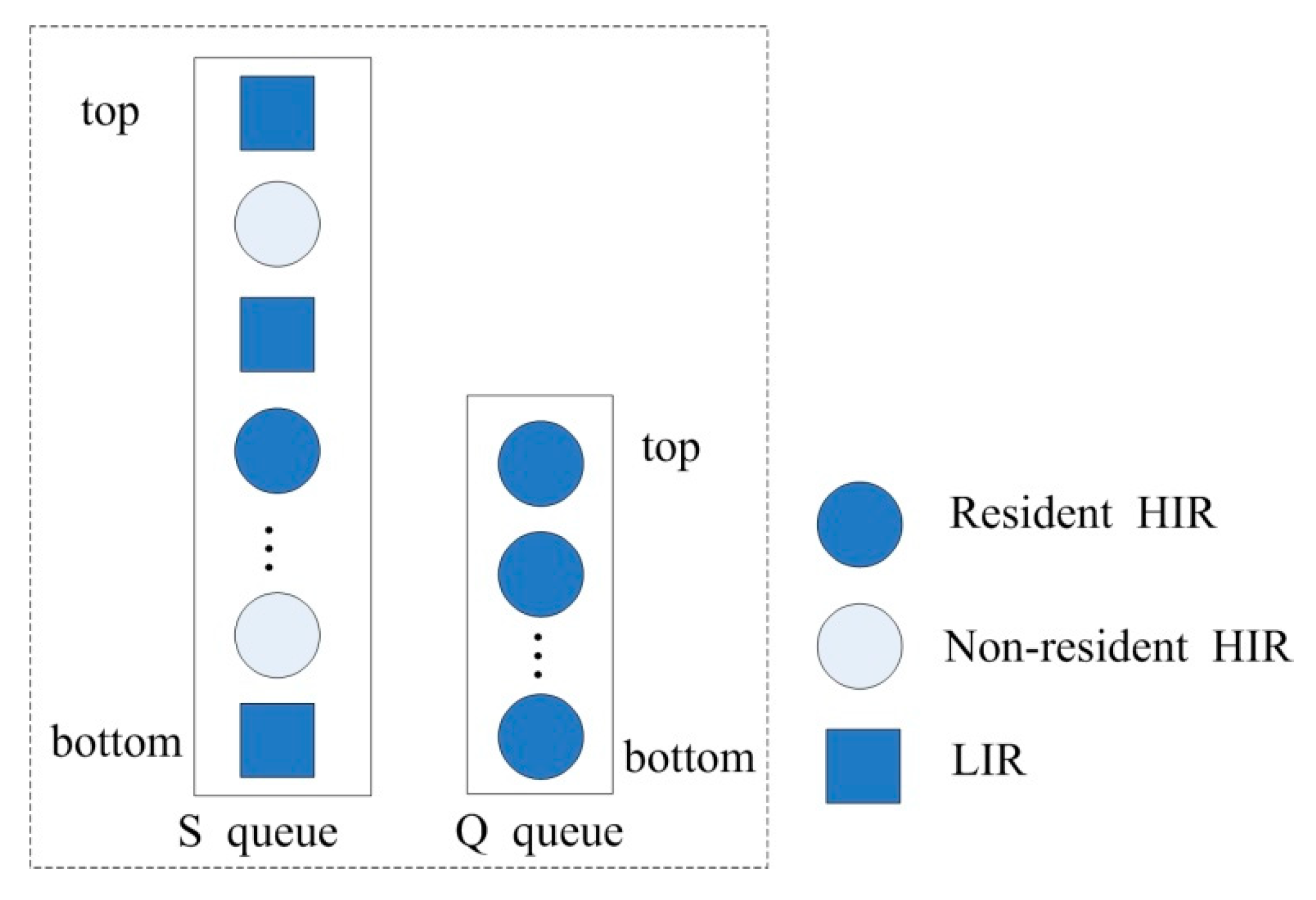

3.2. Base LIRS Policy

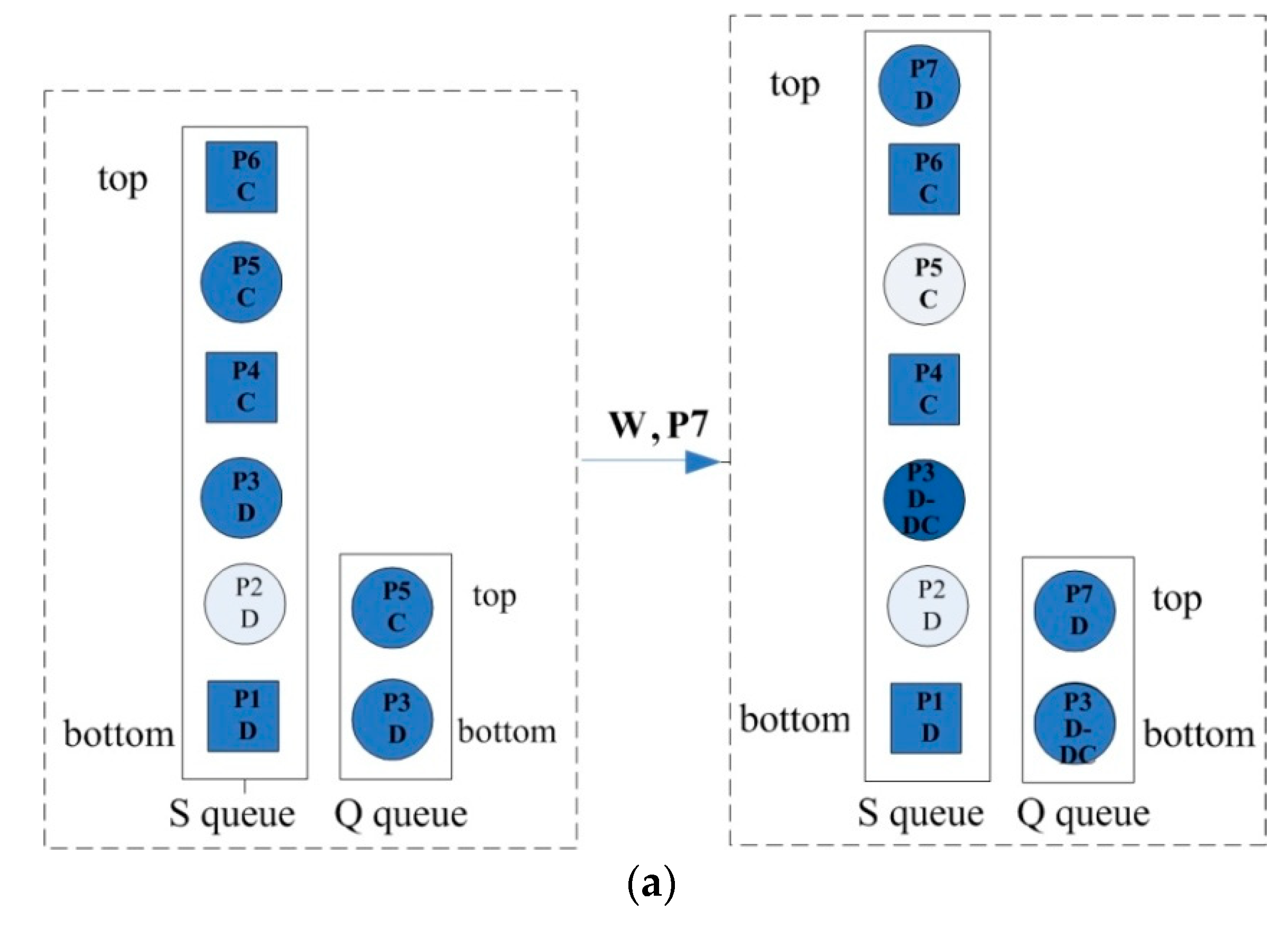

3.2.1. The Insertion Policy

3.2.2. The Promotion Policy

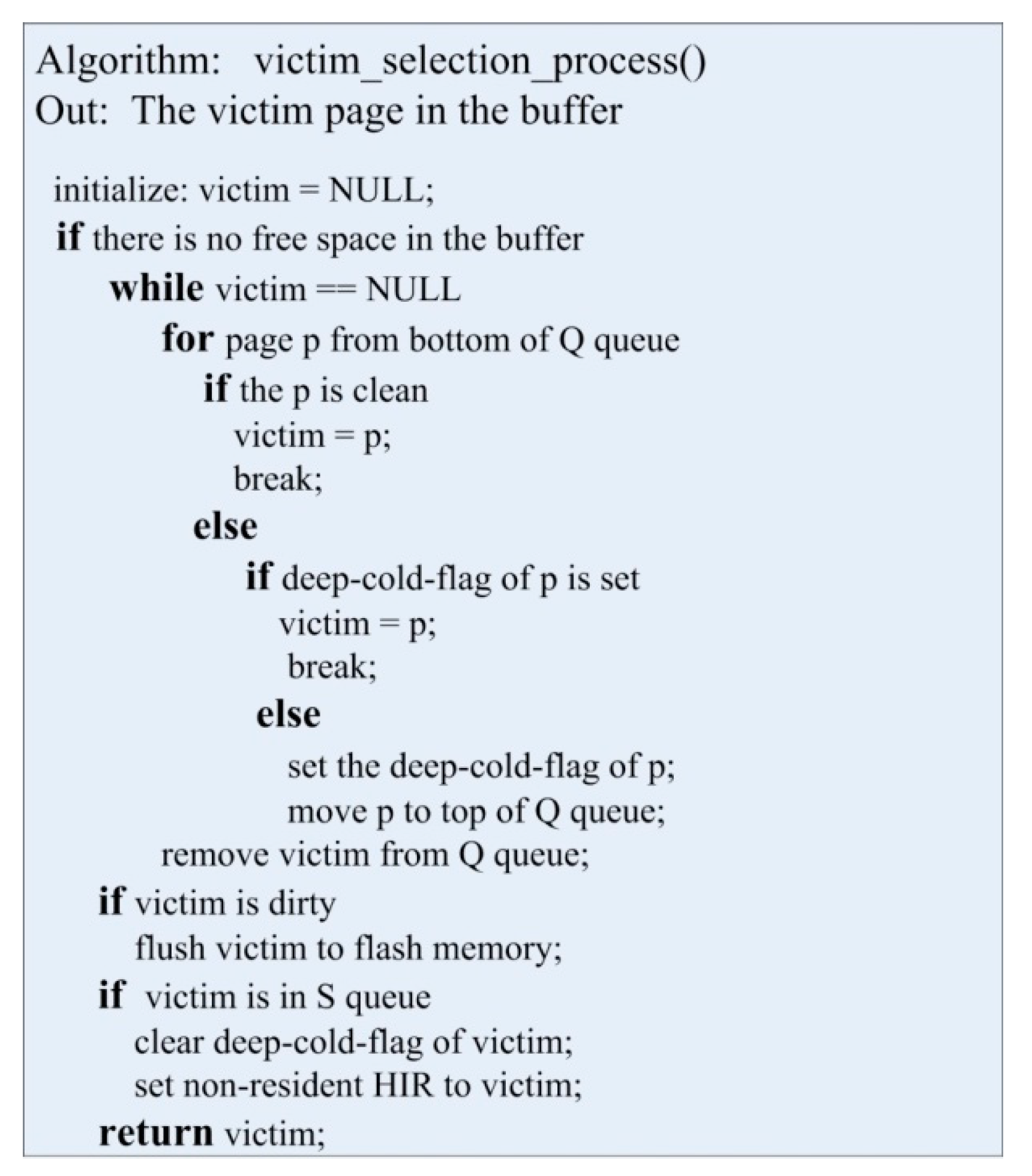

3.2.3. The Victim Selection Policy

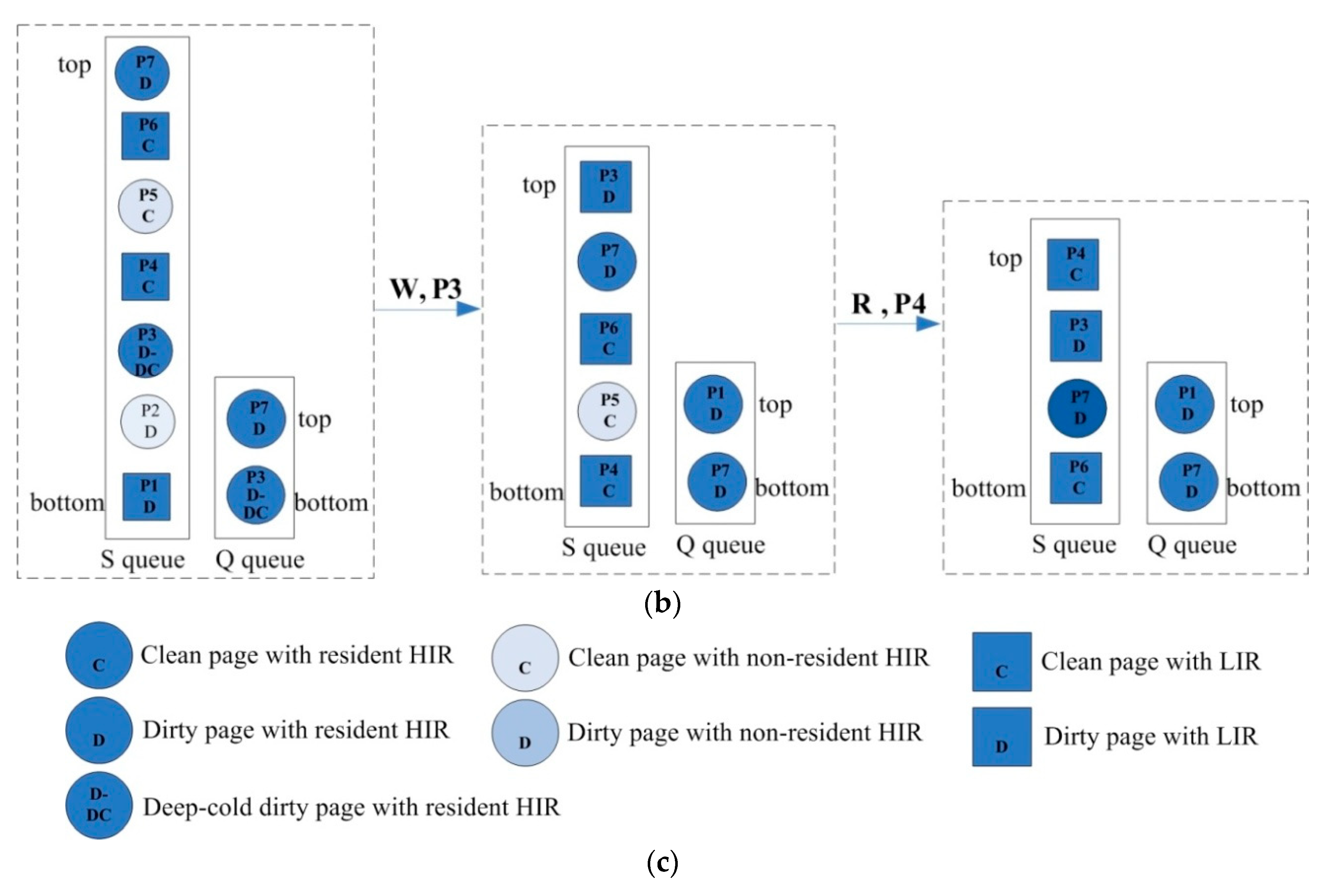

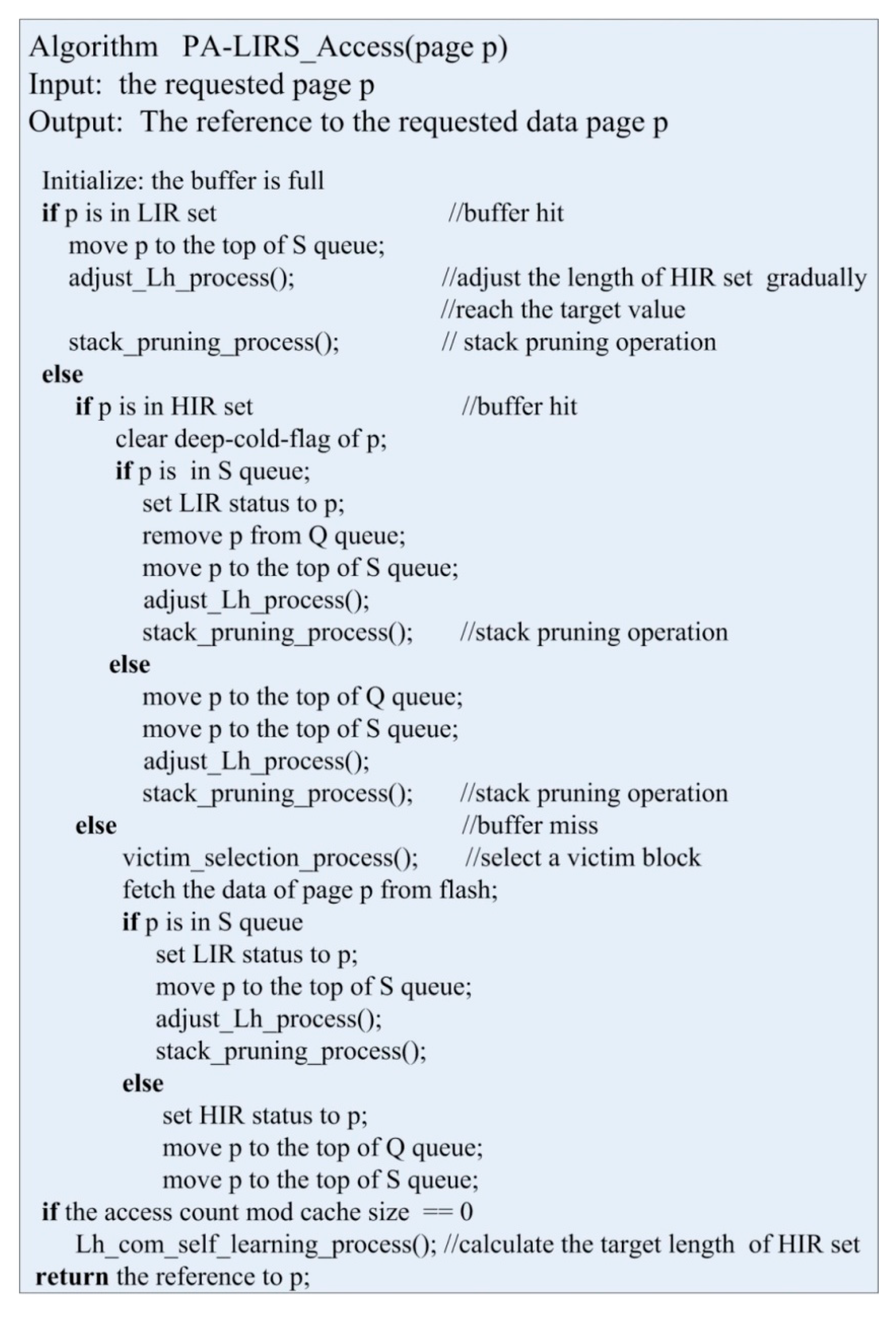

3.3. Proposed Policy

- Using deep-cold-detection policy to assign a deep-cold flag to the cold pages in the Q queue;

- Putting off evicting a dirty page that is considered as a non-deep-cold page.

4. Discussion

4.1. Experimental Environment

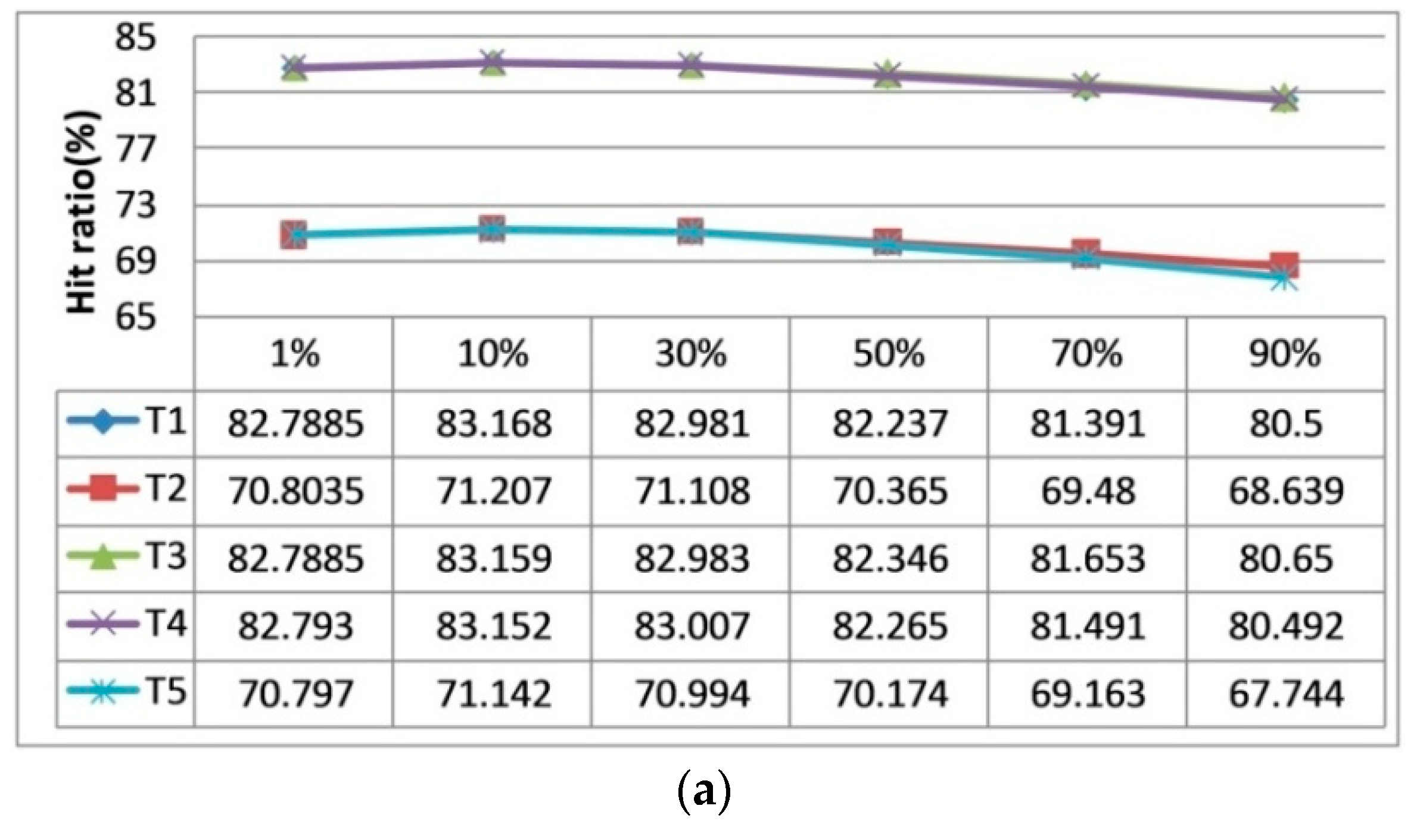

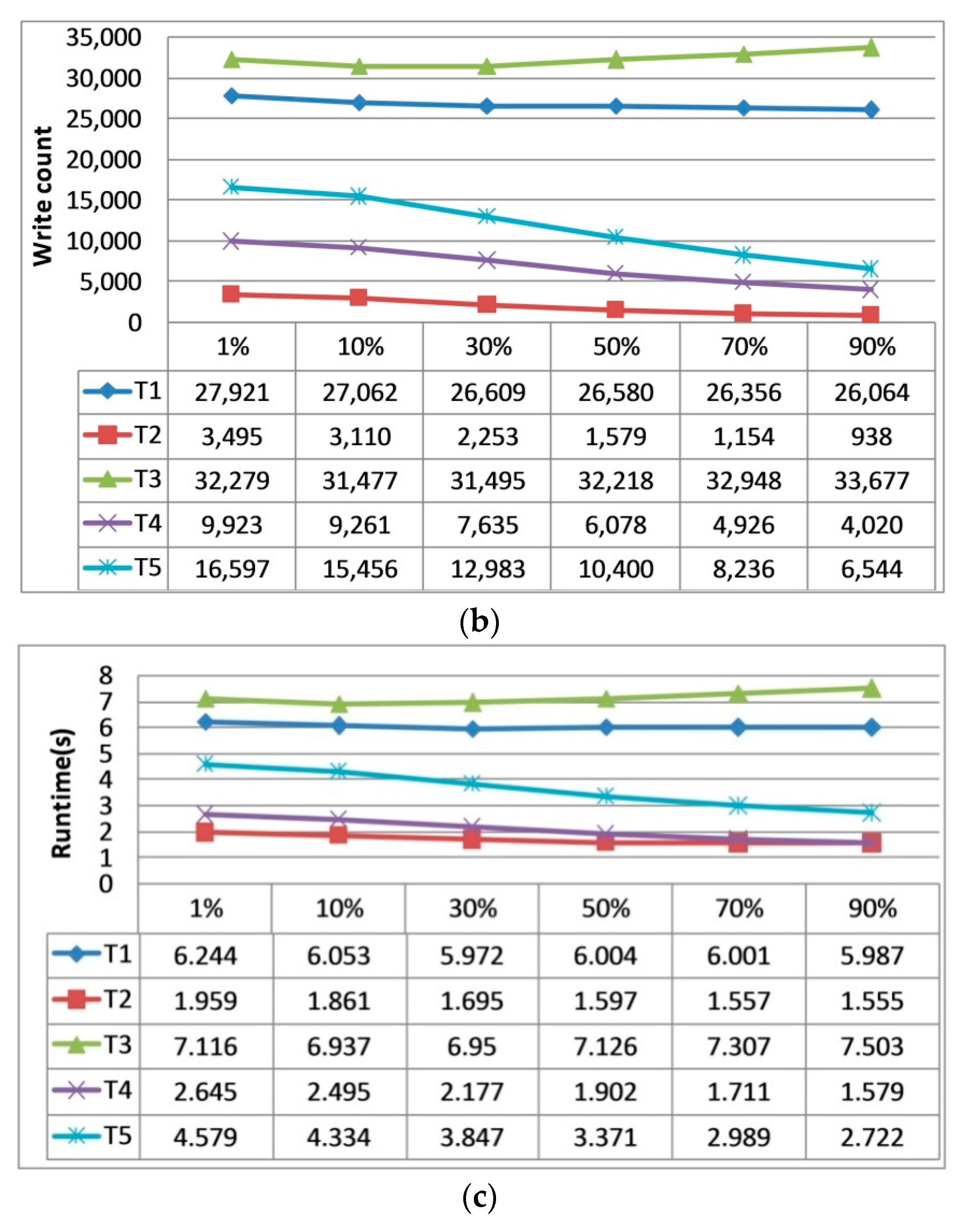

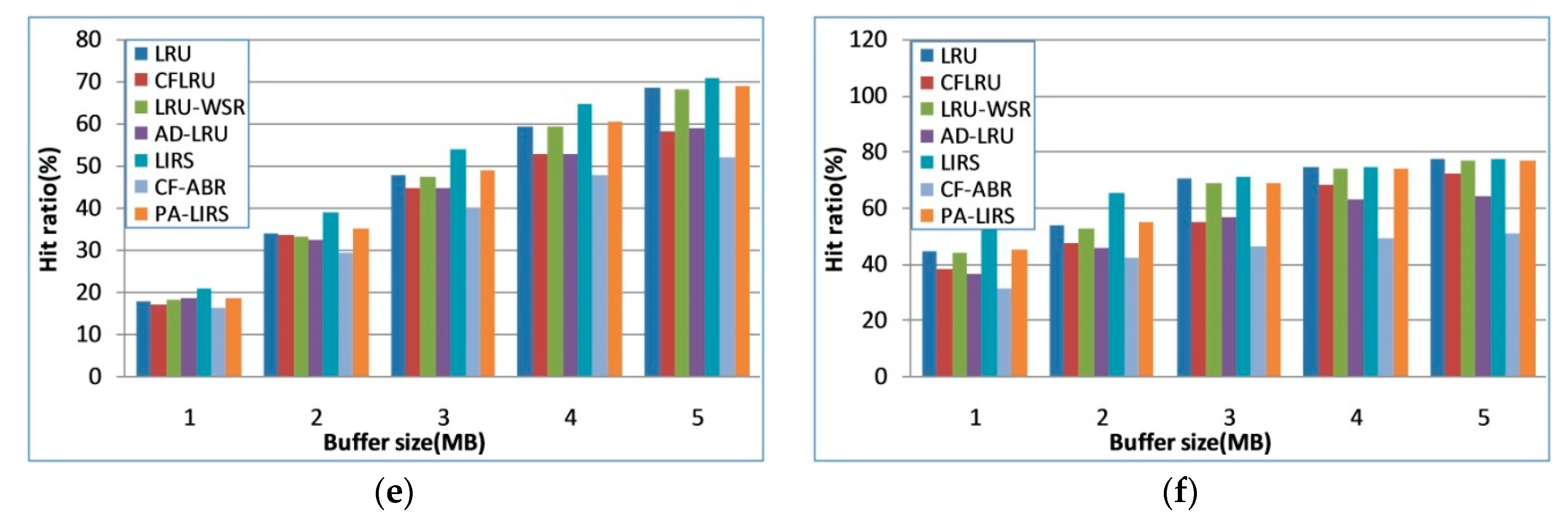

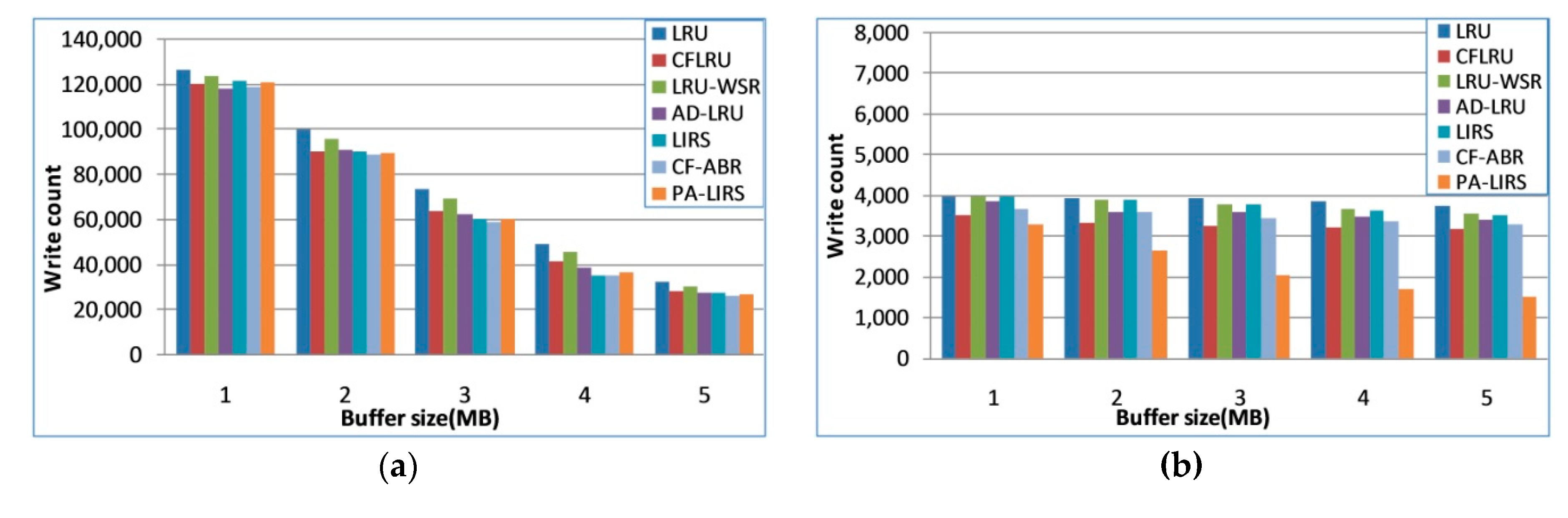

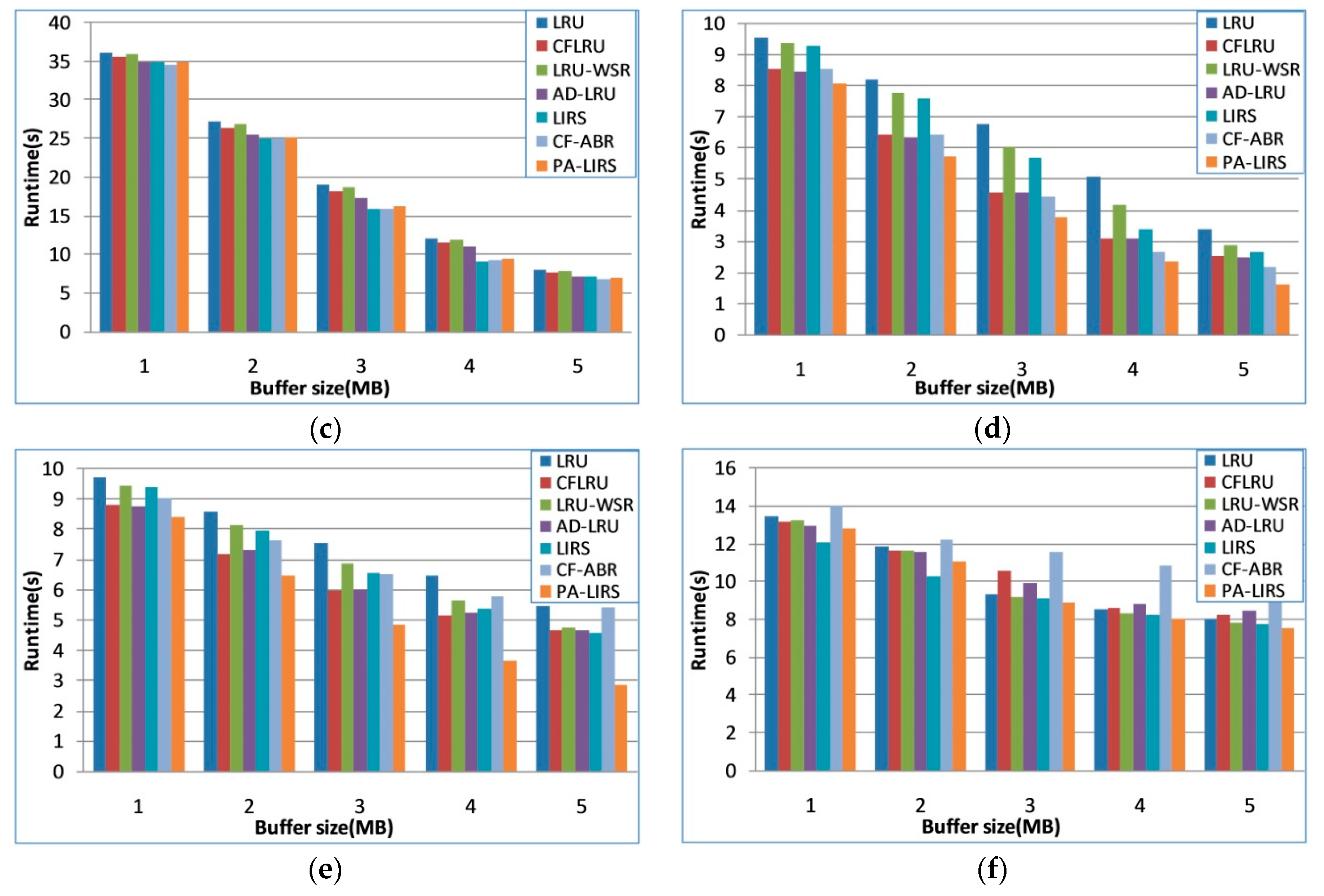

4.2. Experiment Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ahn, S.; Hyun, S.; Kim, T.; Bahn, H. A Compressed File System Manager for Flash Memory Based Consumer Electronics Devices. IEEE Trans. Consum. Electron. 2013, 59, 544–549. [Google Scholar] [CrossRef]

- AlinezhadChamazcoti, S.; Delavari, Z.; Ghassem, S.G.; Asadi, H. On Endurance and Performance of Erasure Codes in SSD-Based Storage Systems. Microelectron. Reliab. 2015, 55, 2453–2467. [Google Scholar] [CrossRef]

- Fukami, A.; Ghose, S.; Luo, Y.; Cai, Y.; Mutlu, O. Improving the Reliability of Chip-Off Forensic Analysis of NAND Flash Memory Devices. Digit. Investig. 2017, 20, S1–S11. [Google Scholar] [CrossRef]

- Xie, T.; Koshia, J. Boosting Random Write Performance for Enterprise Flash Storage Systems. In Proceedings of the IEEE 27th Symposium on Mass Storage Systems and Technologies (MSST), Denver, CO, USA, 23–27 May 2011; pp. 1–10. [Google Scholar]

- Du, C.; Yao, Y.; Zhou, J.; Xu, X. VBBMS: A Novel Buffer Management Strategy for NAND Flash Storage Devices. IEEE Trans. Consum. Electron. 2019, 65, 134–141. [Google Scholar] [CrossRef]

- Yao, Y.; Kong, X.; Zhou, J.; Xu, X.; Feng, W.; Liu, Z. An Advanced Adaptive Least Recently Used Buffer Management Algorithm for SSD. IEEE Access 2019, 7, 33494–33505. [Google Scholar] [CrossRef]

- Megiddo, N.; Modha, D.S. ARC: A Self-Tuning, Low Overhead Replacement Cache. In Proceedings of the USENIX File and Storage Technologies Conference (FAST), San Francisco, CA, USA, 31 March 2003; pp. 115–130. [Google Scholar]

- Bengar, D.A.; Ebrahimnejad, A.; Motameni, H.; Golsorkhtabaramiri, M. A page replacement algorithm based on a fuzzy approach to improve cache memory performance. Soft Comput. 2020, 24, 955–963. [Google Scholar] [CrossRef]

- Zanoon, N.; Abu-Taieh, E.; Abu-Hamatta, H.S. A Novel Approach to Improve LRU Page Replace Algorithm. J. Appl. Sci. Eng. 2018, 13, 478–483. [Google Scholar]

- Anwar, U.; Paik, J.Y.; Jin, R.; Chung, T.S. Log-buffer Aware Cache Replacement Policy for Flash Storage Devices. IEEE Trans. Consum. Electron. 2017, 63, 77–84. [Google Scholar] [CrossRef]

- Man, D.P.; Lu, Q.; Wang, Y.; Wu, Y.; Du, X.J.; Guizani, M. An Adaptive Cache Management Approach in ICN with Pre-filter. Queues. Comput. Commun. 2020, 153, 250–263. [Google Scholar] [CrossRef]

- Zheng, K.; Wang, J. Page Weight-Based Buffer Replacement Algorithm for Flash-Based Databases. In Proceedings of the 2018 International Computers, Signals and Systems Conference (ICOMSSC), Dalian, China, 28–30 September 2018; pp. 107–111. [Google Scholar]

- Thakare, A.O.; Deshpande, P.S. Probabilistic Page Replacement Policy in Buffer Cache Management for Flash-Based Cloud Databases. Comput. Inform. 2019, 38, 1237–1271. [Google Scholar] [CrossRef]

- Zhang, X.; Duan, X.N.; Yang, J.C.; Wang, J.Y. ARW: Efficient Replacement Policies for Phase Change Memory and NAND Flash. IEICE T. Inf. Syst. 2017, 100, 79–90. [Google Scholar] [CrossRef]

- Kim, J.J. Hot/Cold Based Replacement Algorithm for Flash Memory Buffer Management. J. Appl. Sci. Eng. 2019, 14, 5072–5077. [Google Scholar]

- Yuan, Y.; Shen, Y.; Li, W.; Yu, D.; Yan, L.; Wang, Y. PR-LRU: A Novel Buffer Placement Algorithm Based on the Probability of Reference for Flash Memory. IEEE Access 2017, 5, 12626–12634. [Google Scholar] [CrossRef]

- Liu, M.; Yao, Z.; Huang, T. F-LRU: An Efficient Buffer Replacement Algorithm for NAND Flash-Based Databases. Optik-Int. J. Light Electron. Opt. 2016, 127, 663–667. [Google Scholar]

- Li, C.; Feng, D.; Hua, Y.; Xia, W.; Wang, F. GASA: A New Page Replacement Algorithm for NAND Flash Memory. In Proceedings of the 2016 IEEE International Conference on Networking, Architecture and Storage (NAS), Long Beach, CA, USA, 8–10 August 2016; pp. 1–9. [Google Scholar]

- Park, S.Y.; Jung, D.; Kang, J.U.; Kim, J. CFLRU: A Replacement Algorithm for Flash Memory. In Proceedings of the 2006 International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), Seoul, Korea, 22–25 October 2006; pp. 234–241. [Google Scholar]

- Jung, H.; Yoon, K.; Shim, H.; Park, S.; Cha, J. LRU-WSR: Integration of LRU and Writes Sequence Reordering for Flash Memory. IEEE Trans. Consum. Electron. 2008, 54, 1215–1223. [Google Scholar] [CrossRef]

- Jin, P.; Ou, Y.; Harder, T.; Li, Z. AD-LRU: An Efficient Buffer Replacement Algorithm for Flash-Based Databases. Data Knowl. Eng. 2012, 72, 83–102. [Google Scholar] [CrossRef]

- Huang, Q.; Chen, R.; Lin, M.; Yang, C.; Li, X. Clean-First Adaptive Buffer Replacement Algorithm for NAND Flash-based Consumer Electronics. In Proceedings of the 17th IEEE International Symposium on Parallel and Distributed Processing with Applications (IEEE ISPA-2019), Xiamen, China, 16–19 December 2019; pp. 1217–1223. [Google Scholar]

- Jiang, S.; Zhang, X. LIRS: An Efficient Low Inter-reference Recency Set Replacement to Improve Buffer Cache Performance. In Proceedings of the International Conference on Measurements and Modeling of Computer Systems, SIGMETRICS 2002, Marina Del Rey, CA, USA, 15–19 June 2002; pp. 31–42. [Google Scholar]

- Chang, H.P.; Chiang, C.P.; Yu, Y.C. An Adaptive Buffer Cache Management Scheme. In Proceedings of the 2016 International Computer Symposium (ICS), Chiayi, Taiwan, 15–17 December 2016; pp. 124–127. [Google Scholar]

- Su, X.; Jin, P.; Xiang, X.; Cui, K.; Yue, L. Flash-DBSim: A Simulation Tool for Evaluating Flash-based Database Algorithms. In Proceedings of the 2009 2nd IEEE International Conference on Computer Science & Information Technology (ICCSIT), Beijing, China, 8–11 August 2009; pp. 185–189. [Google Scholar]

- UMass Trace Repository. Available online: http://traces.cs.umass.edu/index.php/Storage/Storage (accessed on 28 November 2020).

- Jung, H.; Yoon, K.; Shim, H.; Park, S.; Cha, J. LIRS-WSR: Integration of LIRS and Writes Sequence Reordering for Flash Memory. In Proceedings of the International Conference on Computational Science and Its Applications—ICCSA 2007, Kuala Lumpur, Malaysia, 26–29 August 2007; pp. 224–237. [Google Scholar]

| Parameter | Value |

|---|---|

| Page size | 2 KB |

| Block Size | 64 pages |

| Write latency | 200 /page |

| Read latency | 25 /page |

| Erase latency | 1.5 /block |

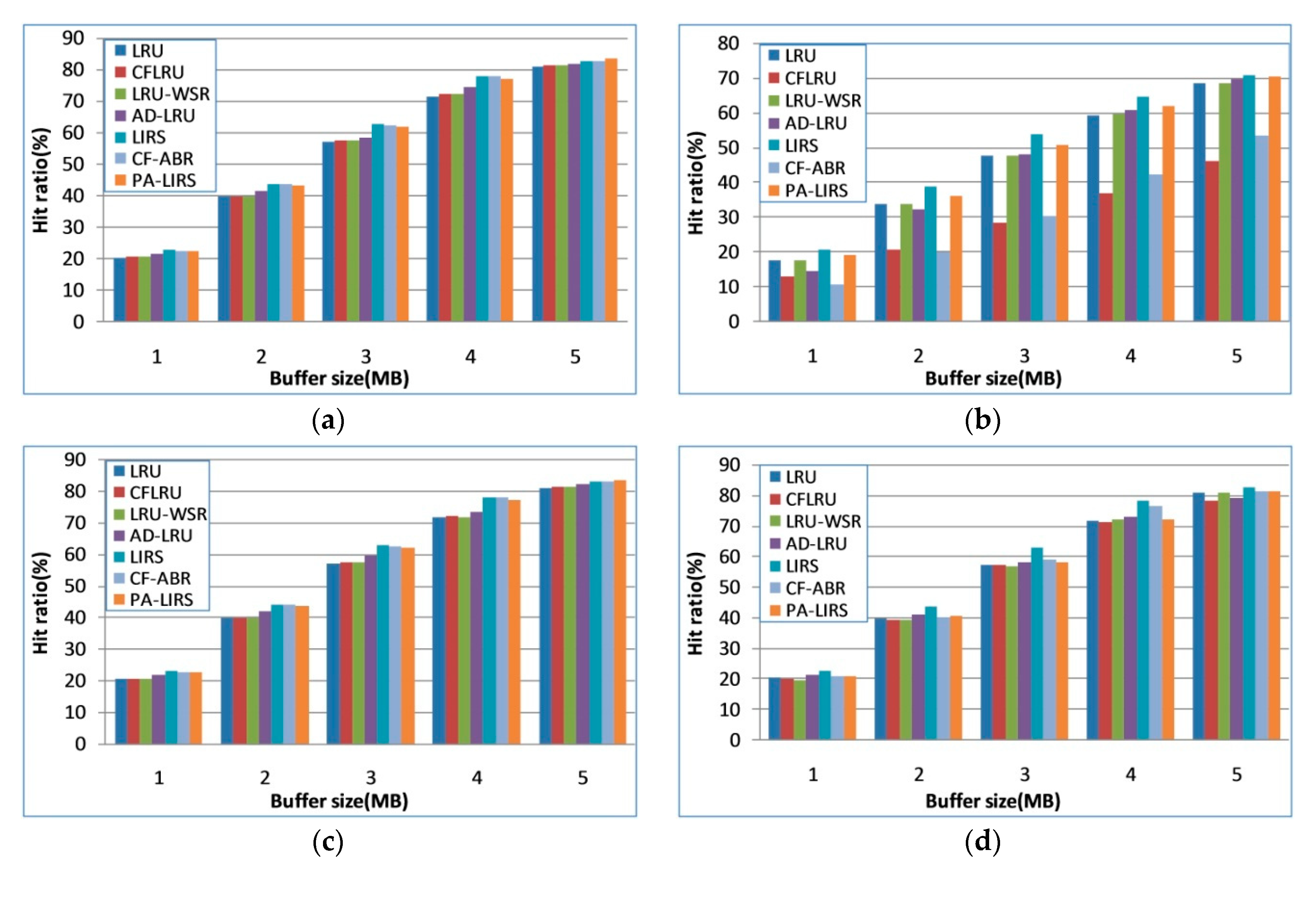

| Type | Total Buffer Requests | Unique Pages | Read/Write Ratio | Locality |

|---|---|---|---|---|

| T1 | 200,000 | 10,000 | 25%/75% | 80%/20% |

| T2 | 200,000 | 10,000 | 98%/2% | 60%/40% |

| T3 | 200,000 | 10,000 | 8%/92% | 80%/20% |

| T4 | 200,000 | 10,000 | 85%/15% | 80%/20% |

| T5 | 200,000 | 10,000 | 85%/15% | 60%/40% |

| Attribute | Value |

|---|---|

| Total buffer requests | 502,775 |

| Read/Write ratio | 87%/13% |

| Unique pages | 31,732 |

| Algorithm | Hit Ratio (%) | Write Count () | Runtime (s) |

|---|---|---|---|

| LRU | 68.34 | 20.49 | 5.47 |

| CFLRU | 57.9 | 13.8 | 4.67 |

| LRU-WSR | 67.89 | 17.43 | 4.74 |

| AD-LRU | 58.71 | 14.0 | 4.66 |

| LIRS | 70.81 | 16.67 | 4.59 |

| CF-ABR | 51.88 | 16.01 | 5.42 |

| PA-LIRS | 68.81 | 7.6 | 2.9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, F.; Jiang, X.; Huang, J.; Chen, F. PA-LIRS: An Adaptive Page Replacement Algorithm for NAND Flash Memory. Electronics 2020, 9, 2172. https://doi.org/10.3390/electronics9122172

Wang F, Jiang X, Huang J, Chen F. PA-LIRS: An Adaptive Page Replacement Algorithm for NAND Flash Memory. Electronics. 2020; 9(12):2172. https://doi.org/10.3390/electronics9122172

Chicago/Turabian StyleWang, Fangjun, Xianliang Jiang, Jifu Huang, and Fuguang Chen. 2020. "PA-LIRS: An Adaptive Page Replacement Algorithm for NAND Flash Memory" Electronics 9, no. 12: 2172. https://doi.org/10.3390/electronics9122172

APA StyleWang, F., Jiang, X., Huang, J., & Chen, F. (2020). PA-LIRS: An Adaptive Page Replacement Algorithm for NAND Flash Memory. Electronics, 9(12), 2172. https://doi.org/10.3390/electronics9122172