Automatic Generation Strategy for Standard Cell Layout in DTCO Process Based on Reinforcement Learning

Abstract

1. Introduction

2. Analysis of Standard Cell Layout

- The standard cell placement includes two rows of horizontal diffusion bars, P-type and N-type, with all PMOS transistors located on the P-type bars and NMOS transistors located on the N-type bars.

- A pair of PMOS and NMOS transistors with a common gate are vertically aligned and share a polycrystalline gate. This pair of PMOS and NMOS transistors is called a transistor pair, while a pair of PMOS and NMOS transistors with a non-common gate but that are vertically aligned are also called a transistor pair [22].

- If the source and drain regions of MOS transistors connected in a circuit are adjacent, they are connected by diffusion regions, which is called source–drain sharing. Multiple MOS transistors arranged continuously with source–drain sharing are called diffusion chains. Since MOS transistors are often arranged in pairs of P and N, diffusion chains are also called transistor pair chains [23].

- The power supply VSS/ground wire VDD are arranged in parallel outside the two rows of horizontal bars.

- The wire mesh outside of the power supply VSS/ground VDD is arranged between the P-type and N-type horizontal bars.

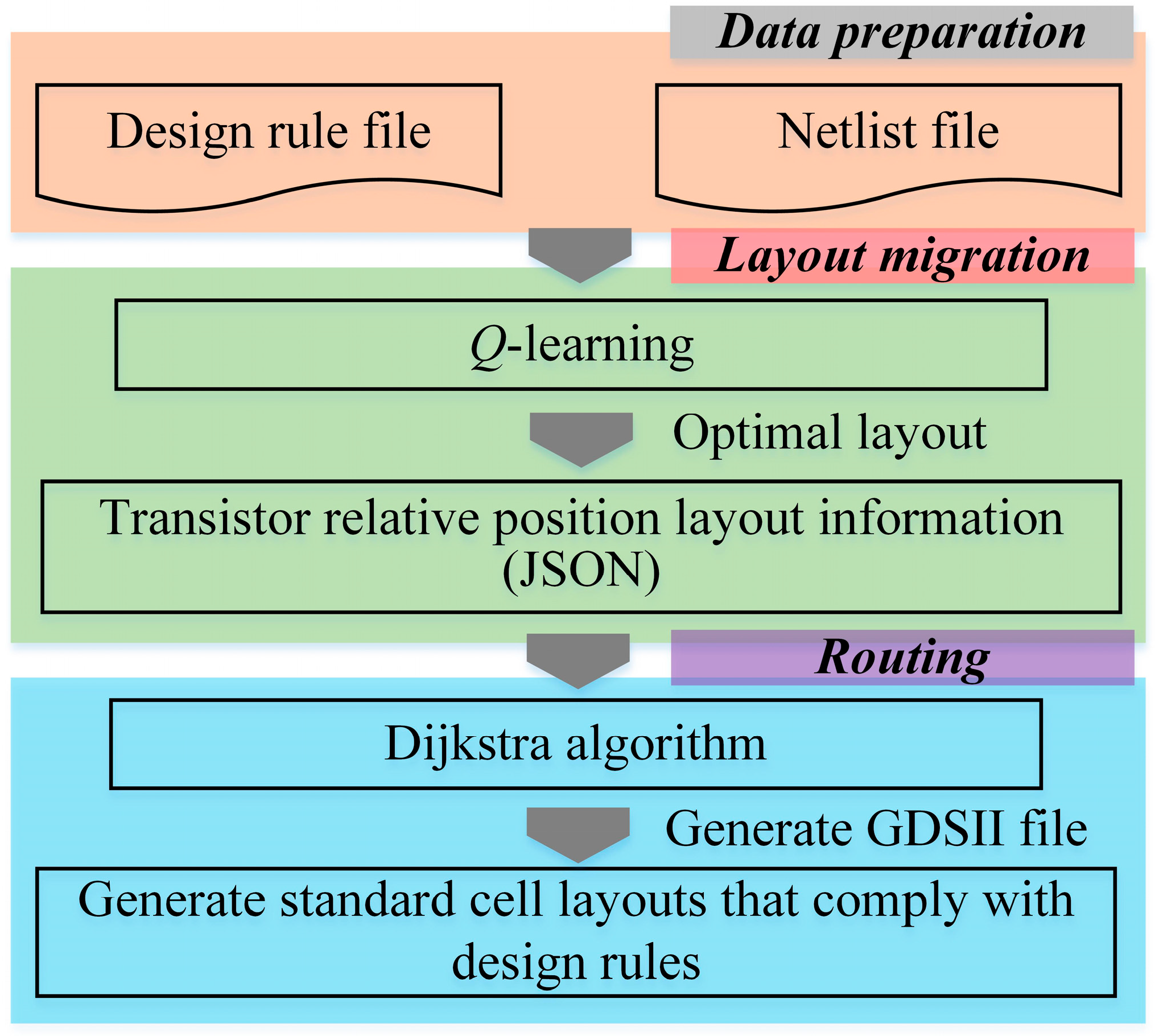

3. Algorithm Design

3.1. Placement Algorithm

- State space: When transistors act as intelligent agents moving in a scene, they will determine the next action to be executed based on the observed layout scene. The interaction between intelligent agents and layout scenarios is the foundation of and key to reinforcement learning for autonomous learning and training. Of these, the layout scenario refers to the transistor element pool environment in which the intelligent agent exists and interacts. Therefore, the state space observed by intelligent agents and the action strategies executed need to be designed and represented in a reasonable layout. The state space s observed by intelligent agents is defined as

- Action space design: The movement of the intelligent agent is a deterministic behavior, and purpose of the action space of the intelligent agent is mainly to exchange the source and drain under fixed gate conditions and search for sharing situations. For each transistor in the current group, check if its source is in the drain list of any transistor in the previous group.

- Reward function design: Create an array that includes the “source drain sharing” situation to count the maximum number of sources and drains shared and reward them. If the drain of the current transistor is the same as the source of the next transistor and their y-coordinates are the same and the x-coordinate of the current transistor plus 1 equals the x-coordinate of the next transistor, then these two transistors are considered “shared” with a reward value of rt + 1.

- Update the Q-value: Update the Q-value according to the Q-learning formula:

3.2. Routing Algorithm

- Initialization: Set the shortest path estimation value d[u] for all identical Net nodes to infinity (indicating that the actual path has not been found yet), except for the source point s, whose value is initialized to 0 (the distance from the source point to itself).

- Node selection: Select the node with the shortest distance from the source point as the current processing node u. This choice is based on a greedy strategy to ensure that each step processes the node with the shortest known path.

- Relaxation operation: Perform a relaxation operation on each adjacent unprocessed node, v, of the current processing node u, attempting to update the shortest path estimation of the adjacent nodes through the current node. The core of the relaxation operation is to check whether there is a shorter path to reach adjacent nodes. If , then . Among these values, represents the currently known shortest path length from the source point to node , and represents the weight of the edge from node to .

- Update operation: If the path length from node to node is less than the known path length from the source point to , then update to the path length from to . Repeat the above steps until all nodes have been processed, that is, the shortest path to all reachable nodes has been found.

4. Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Cheng, C.K.; Ho, C.T.; Holtz, C.; Lin, B. Design and system technology co-optimization sensitivity prediction for VLSI technology development using machine learning. In Proceedings of the 2021 ACM/IEEE International Workshop on System Level Interconnect Prediction (SLIP), Munich, Germany, 4 November 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 8–15. [Google Scholar]

- Vandewalle, B.; Chava, B.; Sakhare, S.; Ryckaert, J.; Dusa, M. Design technology co-optimization for a robust 10 nm Metal1 solution for Logic design and SRAM. In Proceedings of the Design-Process-Technology Co-optimization for Manufacturability VIII, San Jose, CA, USA, 23–27 February 2014; SPIE: Bellingham, WA, USA, 2014; Volume 9053, pp. 208–220. [Google Scholar]

- Rabaey, J.M.; Chandrakasan, A.; Nikolic, B. Digital Integrated Circuits; Prentice Hall: Englewood Cliffs, NJ, USA, 2002. [Google Scholar]

- Johansson, T. A Technology Agnostic Approach for Standard-Cell Layout Design Automation. 2019. Available online: https://ask.orkg.org/item/289968215/A-Technology-Agnostic-Approach-for-Standard-cell-Layout-Design-Automation (accessed on 1 December 2024).

- Guruswamy, M.; Maziasz, R.L.; Dulitz, D.; Raman, S.; Chiluvuri, V.; Fernandez, A.; Jones, L.G. CELLERITY: A fully automatic layout synthesis system for standard cell libraries. In Proceedings of the 34th annual Design Automation Conference, New York, NY, USA, 9–13 June 1997; pp. 327–332. [Google Scholar]

- Riepe, M.A.; Sakallah, K.A. Transistor placement for noncomplementary digital VLSI cell synthesis. ACM Trans. Des. Autom. Electron. Syst. (TODAES) 2003, 8, 81–107. [Google Scholar] [CrossRef]

- Hwang, C.Y.; Hsieh, Y.C.; Lin, Y.L.; Hsu, Y.C. An efficient layout style for 2-metal CMOS leaf cells and their automatic generation. In Proceedings of the 28th ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 17–21 June 1991; pp. 481–486. [Google Scholar]

- Phillips, S.; Hauck, S. Automatic layout of domain-specific reconfigurable subsystems for system-on-a-chip. In Proceedings of the 2002 ACM/SIGDA Tenth International Symposium on Field-Programmable Gate Arrays, Monterey, CA, USA, 24–26 February 2002; pp. 165–173. [Google Scholar]

- Ziesemer, A.M., Jr.; Reis, R. Physical design automation of transistor networks. Microelectron. Eng. 2015, 148, 122–128. [Google Scholar] [CrossRef]

- Ma, Q.; Wang, X. An Algorithm for Transistor Cell Layout Synthesis. J. Circuits Syst. 2004, 4, 121–124. [Google Scholar]

- Lazzari, C.; Santos, C.; Reis, R. A new transistor-level layout generation strategy for static CMOS circuits. In Proceedings of the 2006 13th IEEE International Conference on Electronics, Circuits and Systems, Nice, France, 10–13 December 2006; IEEE: Piscataway, NJ, USA, 2006; pp. 660–663. [Google Scholar]

- Ziesemer, A.; Reis, R.; Moreira, M.T.; Arendt, M.E.; Calazans, N.L. Automatic layout synthesis with ASTRAN applied to asynchronous cells. In Proceedings of the 2014 IEEE 5th Latin American Symposium on Circuits and Systems, Santiago, Chile, 25–28 February 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 1–4. [Google Scholar]

- Hao, R.; Cai, Y.; Zhou, Q.; Wang, R. DrPlace: A Deep Learning Based Routability-Driven VLSI Placement Algorithm. J. Comput. Aided Des. Comput. Graph. 2021, 33, 624–631. [Google Scholar] [CrossRef]

- Jo, K.; Ahn, S.; Do, J.; Song, T.; Kim, T.; Choi, K. Design Rule Evaluation Framework Using Automatic Cell Layout Generator for Design Technology Co-Optimization. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 1933–1946. [Google Scholar] [CrossRef]

- Lee, D.; Park, D.; Ho, C.T.; Kang, I.; Kim, H.; Gao, S.; Lin, B.; Cheng, C.K. SP&R: SMT-based Simultaneous Place-and-Route for Standard Cell Synthesis of Advanced Nodes. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2020, 40, 2142–2155. [Google Scholar]

- Gao, X.; Zhang, H.; Pan, Z.; Lin, Y.; Wang, R.; Huang, R. Migrating Standard Cells for Multiple Drive Strengths by Routing Imitation. In Proceedings of the 2024 2nd International Symposium of Electronics Design Automation (ISEDA), Xi’an, China, 10–13 May 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 5–10. [Google Scholar]

- Ren, H.; Fojtik, M. Invited-NVCell: Standard Cell Layout in Advanced Technology Nodes with Reinforcement Learning. In Proceedings of the 2021 58th ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 5–9 December 2021; pp. 1291–1294. [Google Scholar]

- Taylor, B.; Pileggi, L. Exact combinatorial optimization methods for physical design of regular logic bricks. In Proceedings of the 44th Annual Design Automation Conference, San Diego, CA, USA, 4–8 June 2007; pp. 344–349. [Google Scholar]

- Guruswamy, M.; Wong, D.F. Echelon: A multilayer detailed area router. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1996, 15, 1126–1136. [Google Scholar] [CrossRef][Green Version]

- Maziasz, R.L.; Hayes, J.P. Layout optimization of static CMOS functional cells. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1990, 9, 708–719. [Google Scholar] [CrossRef]

- Martins, R. Closing the Gap Between Electrical and Physical Design Steps with an Analog IC Placement Optimizer Enhanced with Machine-Learning-Based Post-Layout Performance Regressors. Electronics 2024, 13, 4360. [Google Scholar] [CrossRef]

- Kim, J.; Kang, S.M. An efficient transistor folding algorithm for row-based CMOS layout design. In Proceedings of the 34th Annual Design Automation Conference, Anaheim, CA, USA, 9–13 June 1997; pp. 456–459. [Google Scholar]

- Basaran, B.; Rutenbar, R.A. An O (n) algorithm for transistor stacking with performance constraints. In Proceedings of the 33rd Annual Design Automation Conference, Las Vegas, NV, USA, 3–7 June 1996; pp. 221–226. [Google Scholar]

- Mirhoseini, A.; Goldie, A.; Yazgan, M.; Jiang, J.; Songhori, E.; Wang, S.; Lee, Y.J.; Johnson, E.; Pathak, O.; Bae, S.; et al. Chip placement with deep reinforcement learning. arXiv 2020, arXiv:2004.10746. [Google Scholar]

| Cell | Cell Info | Area (μm2) | Design Time | Norm.Delay (ns) | Norm.Power (μW) | DRVs | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Num.T | Num.Nets | Manual | Ours | Manual | Ours | Manual | Ours | Manual | Ours | Manual | Ours | |

| AND | 6 | 9 | 1.40 | 1.40 | 10–15 min | 3–5 s | 0.542 | 0.538 | 0.053 | 0.52 | 0 | 0 |

| NAND | 8 | 12 | 1.40 | 140 | 10–15 min | 3–5 s | 0.538 | 0.535 | 0.056 | 0.054 | 0 | 0 |

| AO | 10 | 13 | 1.96 | 1.95 | 10–15 min | 3–5 s | 0.431 | 0.428 | 0.049 | 0.045 | 0 | 0 |

| DQH | 26 | 17 | 5.88 | 5.86 | 40–50 min | 5–10 s | 0.421 | 0.419 | 0.041 | 0.040 | 0 | 0 |

| CLK | 12 | 13 | 1.40 | 1.40 | 10–15 min | 3–5 s | 0.562 | 0.553 | 0.039 | 0.037 | 0 | 0 |

| INV | 2 | 6 | 0.84 | 0.82 | 10–15 min | 3–5 s | 0.521 | 0.518 | 0.036 | 0.035 | 0 | 0 |

| BUF | 4 | 7 | 1.12 | 1.10 | 10–15 min | 3–5 s | 0.481 | 0.465 | 0.032 | 0.029 | 0 | 0 |

| MUX | 12 | 12 | 3.08 | 3.06 | 10–15 min | 3–5 s | 0.461 | 0.458 | 0.025 | 0.023 | 0 | 0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, W.; Li, B.; Huang, S.; Lei, Z.; Liu, W.; Wu, Z.; Qin, C. Automatic Generation Strategy for Standard Cell Layout in DTCO Process Based on Reinforcement Learning. Electronics 2025, 14, 529. https://doi.org/10.3390/electronics14030529

Huang W, Li B, Huang S, Lei Z, Liu W, Wu Z, Qin C. Automatic Generation Strategy for Standard Cell Layout in DTCO Process Based on Reinforcement Learning. Electronics. 2025; 14(3):529. https://doi.org/10.3390/electronics14030529

Chicago/Turabian StyleHuang, Wenli, Bin Li, Songting Huang, Zonghan Lei, Wenchao Liu, Zhaohui Wu, and Chaozheng Qin. 2025. "Automatic Generation Strategy for Standard Cell Layout in DTCO Process Based on Reinforcement Learning" Electronics 14, no. 3: 529. https://doi.org/10.3390/electronics14030529

APA StyleHuang, W., Li, B., Huang, S., Lei, Z., Liu, W., Wu, Z., & Qin, C. (2025). Automatic Generation Strategy for Standard Cell Layout in DTCO Process Based on Reinforcement Learning. Electronics, 14(3), 529. https://doi.org/10.3390/electronics14030529