Review of Applications of Regression and Predictive Modeling in Wafer Manufacturing

Abstract

1. Introduction

1.1. Role of Regression and Predictive Modeling

- How do process conditions (e.g., etch time, temperature, pressure) influence wafer characteristics (e.g., film thickness, CD uniformity)? That is, how do we quantify complex relationships between inputs (recipes, tool settings, material properties) and outputs (film thickness, line width, yield) [4,14]?

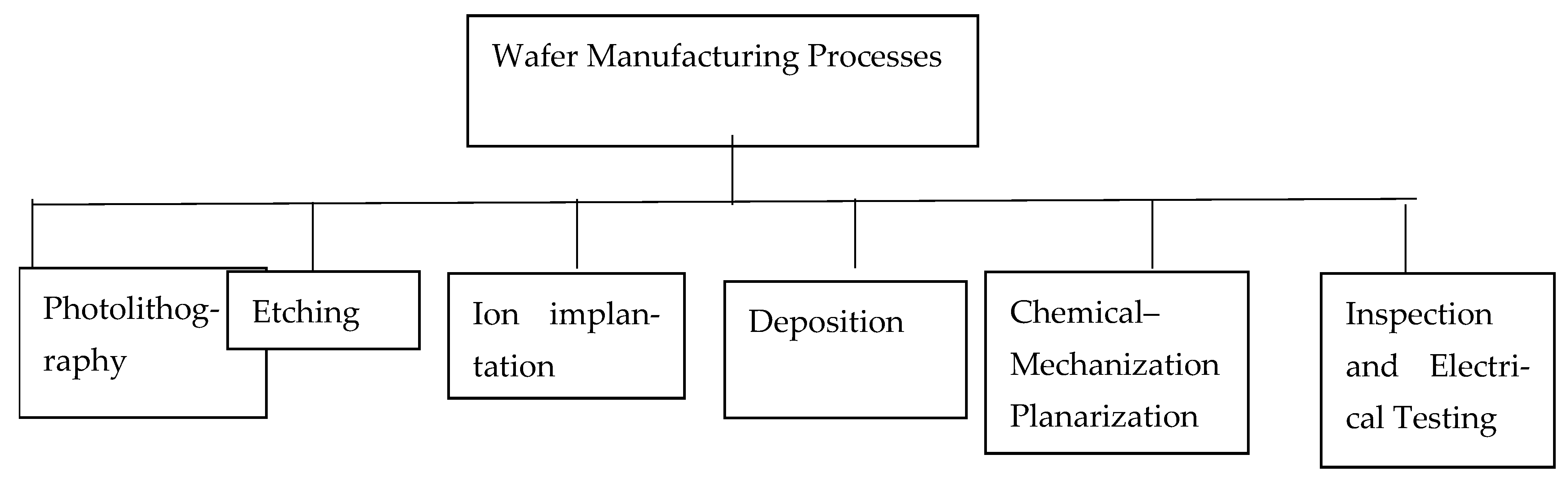

1.2. The Applications in the Process Steps of Wafer Manufacturing

- Chemical–Mechanical Polishing (CMP): Predicting the wafer material removal rate for semiconductor chemical–mechanical polishing is performed by a regression model [27]. Five regression models were proposed to predict the material removal of a wafer [28]. Yu et al. [29] used models to predict the material removal rate (MRR) in the chemical–mechanical planarization process, with the asperity radius and asperity density of the polishing pad as the responses.

- Metrology Data Correlation: Regression links in-line inspection data with final wafer yield [8]. Rana et al. [22] showed that predictive metrology and analytics, which rely on multivariate, nonlinear, and correlated data, are difficult to model mathematically but can be effectively learned by computing machines for process prediction and control.

- Electrical Test Data: Regression can be used for predicting die pass/fail before final test [30]. Skinner et al. [11] selected two traditional multivariate statistical methods—principal component methods and regression-based methods—and a classification and regression tree (CART) method to study the effects of the wafer fabrication process on the quality or yield of the wafers.

1.3. Benefits of Regression and Predictive Modeling

1.3.1. Early Yield Estimation: Predicts Outcomes Before Wafers Reach the Testing Stage

1.3.2. Process Optimization: Identifies Critical Parameters with the Most Significant Impact

1.3.3. Cost Reduction: Reduces Metrology Steps and Wafer Scrap and Enables Predictive Maintenance and Fewer Reworks

1.3.4. Improved Reliability: Detects Subtle Drifts Before They Cause Widespread Failures

1.3.5. Shorter Ramp-Up: Accelerates Development of New Technology Nodes and Accelerates Learning Cycles for New Nodes

1.3.6. Higher Yield: Early Detection of Yield Excursions

1.3.7. Reduced Scrap: Predict Failing Wafers Before Packaging

1.4. Data Landscape in Wafer Manufacturing

2. The Application of Regression in Wafer Manufacturing

2.1. Process–Parameter Relationship Modeling

2.2. Metrology Correlation

2.3. Fault Detection and Excursion Analysis

3. The Application of Predictive Modeling in Wafer Manufacturing

3.1. Yield Prediction

3.2. Equipment Health Monitoring and Predictive Maintenance

3.3. Defect Density and Pattern Prediction

3.4. Process Control and Run-to-Run Optimization

3.5. Reliability and Lifetime Forecasting

3.6. Virtual Fabrication and Digital Twin

3.7. Design–Technology Co-Optimization (DTCO)

4. Regression Methods in Wafer Manufacturing

4.1. Regression Models

4.1.1. Linear Regression

4.1.2. Multiple Regression

4.1.3. Polynomial Regression

4.1.4. Logistic Regression

4.1.5. Nonlinear Regression

4.1.6. Principal Component Regression (PCR)

4.1.7. Partial Least Squares Regression (PLSR)

4.1.8. Regularized Regression (Ridge, Lasso, Elastic Net)

4.1.9. Hierarchical and Mixed-Effect Regression

4.2. Generalization of the Regression Model

4.3. Demonstration of the Regression Methods

4.3.1. Virtual Metrology

4.3.2. Yield Prediction

4.3.3. Excursion Detection

5. Predictive Modeling in Wafer Manufacturing

5.1. Virtual Metrology (VM) Models

5.2. Yield Prediction Models

5.3. Fault Detection and Classification (FDC) Models

5.4. Time-Series Predictive Models

5.5. Hybrid Models

6. Integration with Machine Learning

6.1. Support Vector Regression (SVR)

6.2. Random Forests/Gradient Boosting

6.3. Neural Networks

6.4. Deep Learning (CNNs, LSTMs)

7. Challenges of Regression and Predictive Modeling

7.1. Regression

7.1.1. Multicollinearity

7.1.2. Nonlinear and Dynamic Processes

7.1.3. High-Dimensional Data

7.1.4. Concept Drift

7.1.5. Interpretability vs. Accuracy

7.2. Predictive

7.2.1. Data Quality and Integration

7.2.2. Model Interpretability

7.2.3. Tool-to-Tool Variation

7.2.4. Computational Efficiency

7.2.5. Imbalanced Data

8. Future Trends

8.1. Hybrid Physics–ML Models

8.2. Real-Time Predictive Analytics

8.3. Digital Twins

8.4. Explainable AI

8.5. Edge AI Deployment

9. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Conflicts of Interest

References

- Chen, Q.; Wei, Q.; Xu, H. A multimodal hierarchical learning approach for virtual metrology in semiconductor manufacturing. J. Manuf. Syst. 2025, 80, 194–205. [Google Scholar] [CrossRef]

- Hargrove, M.; Wen, S.; Yim, D.; Ruegger, K.E.; Nanja, P.; Sarkar, S.; Lowe, B.; Vincent, B.; Ervin, J.; Fried, D. Review of virtual wafer process modeling and metrology for advanced technology development. J. Micro/Nanopatterning Mater. Metrol. 2023, 22, 31209. [Google Scholar] [CrossRef]

- Kang, P.; Lee, H.J.; Cho, S.; Kim, D.; Park, J.; Park, C.K.; Doh, S. A virtual metrology system for semiconductor manufacturing. Expert Syst. Appl. 2009, 36, 12554–12561. [Google Scholar] [CrossRef]

- Melhem, M.; Ananou, B.; Ouladsine, M.; Pinaton, J. Regression methods for predicting the product’s quality in the semiconductor manufacturing process. IFAC-PapersOnLine 2016, 49, 83–88. [Google Scholar] [CrossRef]

- Morsy, M.; Znid, F.; Farraj, A. A critical review on improving and moving beyond the 2 nm horizon: Future directions and impacts in next-generation integrated circuit technologies. Mater. Sci. Semicond. Proc. 2025, 190, 109376. [Google Scholar] [CrossRef]

- Zeng, D. Statistical Methods for Enhanced Metrology in Semiconductor/Photovoltaic Manufacturing. Ph.D. Thesis, UC Berkeley, Berkeley, CA, USA, 2012. [Google Scholar]

- Suthar, K.; Shah, D.; Wang, J.; He, Q.P. Next-generation virtual metrology for semiconductor manufacturing: A feature-based framework. Comput. Chem. Eng. 2019, 127, 140–149. [Google Scholar] [CrossRef]

- Scheibelhofer, P.; Gleispach, D.; Hayderer, G.; Stadlober, E. A methodology for predictive maintenance in semiconductor manufacturing. Austrian J. Stat. 2012, 41, 161–173. [Google Scholar] [CrossRef]

- Zhang, J.; Jiang, Y.; Luo, H.; Yin, S. Prediction of material removal rate in chemical mechanical polishing via residual convolutional neural network. Comput. Chem. Eng. 2021, 107, 104673. [Google Scholar] [CrossRef]

- Flechsig, C.; Lohmer, J.; Lasch, R.; Zettler, B.; Schneider, G.; Eberts, D. Streamlining semiconductor manufacturing of 200 mm and 300 mm wafers: A longitudinal case study on the lot-to-order-matching process. IEEE Trans. Semicond. Manuf. 2022, 35, 397–404. [Google Scholar] [CrossRef]

- Skinner, K.R.; Montgomery, D.C.; Runger, G.C.; Fowler, J.W.; McCarville, D.R.; Rhoads, T.R.; Stanley, J.D. Multivariate statistical methods for modeling and analysis of wafer probe test data. IEEE Trans. Semicond. Manuf. 2002, 15, 523–530. [Google Scholar] [CrossRef]

- Kim, K.; Oh, S.; Bae, K.; Oh, H.S. Prediction of wafer performance: Use of functional outlier detection and regression. IEEE Access 2025, 13, 3544244. [Google Scholar] [CrossRef]

- Purwins, H.; Barak, B.; Nagi, A.; Engel, R.; Höckele, U.; Kyek, A.; Cherla, S.; Lenz, B.; Pfeifer, G.; Weinzierl, K. Regression methods for virtual metrology of layer thickness in chemical vapor deposition. IEEE/ASME Trans. Mechatron. 2013, 19, 1–8. [Google Scholar] [CrossRef]

- Wan, J.; Pampuri, S.; O’Hara, P.G.; Johnston, A.B.; McLoone, S. On regression methods for virtual metrology in semiconductor manufacturing. In Proceedings of the 25th IET Irish Signals & Systems Conference 2014 and 2014 China-Ireland International Conference on Information and Communications Technologies (ISSC 2014/CIICT 2014), Limerick, Ireland, 26–27 June 2014; IET: Stevenage, UK, 2014; pp. 380–385. [Google Scholar]

- Zhai, W.; Han, Q.; Chen, L.; Shi, X. Explainable AutoML (xAutoML) with adaptive modeling for yield enhancement in semiconductor smart manufacturing. In Proceedings of the 2024 2nd International Conference on Artificial Intelligence and Automation Control (AIAC), Guangzhou, China, 20–22 December 2024; pp. 162–171. [Google Scholar]

- Maitra, V.; Su, Y.; Shi, J. Virtual metrology in semiconductor manufacturing: Current status and prospects. Expert Syst. Appl. 2024, 249, 123559. [Google Scholar] [CrossRef]

- Dreyfus, P.A.; Psarommatis, F.; May, G.; Kiritsis, D. Virtual metrology as an approach for product quality estimation in Industry 4.0: A systematic review and integrative conceptual framework. Int. J. Prod. Res. 2022, 60, 742–765. [Google Scholar] [CrossRef]

- Nam, W.S.; Kim, S.B. A prediction of wafer yield using product fabrication virtual metrology process parameters in semiconductor manufacturing. J. Korean Inst. Ind. Eng. 2015, 41, 572–578. [Google Scholar] [CrossRef]

- Kumar, M.G.V.; Krishna, V.R.; Chinthamu, N.; Gupta, A.; Venkatakiran, S. IoT sensor data-driven programming approach for predictive maintenance of wafer stick machines. In Technological Applications for Smart Sensors; Apple Academic Press: Palm Bay, FL, USA, 2025; pp. 447–464. [Google Scholar]

- Lenz, B.; Barak, B. Data mining and support vector regression machine learning in semiconductor manufacturing to improve virtual metrology. In Proceedings of the 2013 46th Hawaii International Conference on System Sciences, Wailea, HI, USA, 7–10 January 2013; pp. 3447–3456. [Google Scholar]

- Deenen, P.C.; Middelhuis, J.; Akcay, A.; Adan, I.J. Data-driven aggregate modeling of a semiconductor wafer fab to predict WIP levels and cycle time distributions. Flex. Serv. Manuf. J. 2024, 36, 567–596. [Google Scholar] [CrossRef]

- Rana, N.; Zhang, Y.; Wall, D.; Dirahoui, B. Predictive data analytics and machine learning enabling metrology and process control for advanced node IC fabrication. In Proceedings of the 2015 26th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 3–6 May 2015; pp. 313–319. [Google Scholar]

- Kang, S. Joint modeling of classification and regression for improving faulty wafer detection in semiconductor manufacturing. J. Intell. Manuf. 2020, 31, 319–326. [Google Scholar] [CrossRef]

- Ahmad, J. Using ML to Model and Optimize Chip Geometry for Improved Lithography. Master’s Thesis, The University of South Bohemia in České Budějovice, Branišovská, České Budějovice, Czech Republic, 2023. [Google Scholar]

- Chien, K.C.; Chang, C.H.; Djurdjanovic, D. Virtual metrology modeling of reactive ion etching based on statistics-based and dynamics-inspired spectral features. J. Vac. Sci. Technol. B 2021, 39, 064003. [Google Scholar] [CrossRef]

- Guo, J.; Geng, M.; Ren, K.; Ni, D.; Gao, D. Optimizing plasma etching: Integrating precise three-dimensional etching simulation and machine learning for multi-objective optimization. IEEE Access 2024, 12, 127065–127073. [Google Scholar] [CrossRef]

- Liu, C.L.; Tseng, C.J.; Hsaio, W.H.; Wu, S.H.; Lu, S.R. Predicting the wafer material removal rate for semiconductor chemical mechanical polishing using a fusion network. Appl. Sci. 2022, 12, 11478. [Google Scholar] [CrossRef]

- Zhao, G.; Wei, Z.; Wang, W.; Feng, D.; Xu, A.; Liu, W.; Song, Z. Review on modeling and application of chemical mechanical polishing. Nanotechnol. Rev. 2020, 9, 182–189. [Google Scholar] [CrossRef]

- Yu, T.; Li, Z.; Wu, D. Predictive modeling of material removal rate in chemical mechanical planarization with physics-informed machine learning. Wear 2019, 426, 1430–1438. [Google Scholar] [CrossRef]

- Dimaculangan, R.V.; de Luna, R.G.; Rosales, M.A.; Magsumbol, J.A.V.; Tubola, O.D. Semiconductor manufacturing final test yield prediction using regression with genetic algorithm-based feature selection. In Proceedings of the International Conference on Intelligent Computing & Optimization, Phnom Penh, Cambodia, 27–28 October 2023; Springer Nature: Cham, Switzerland, 2023; pp. 108–117. [Google Scholar]

- Wang, H.; Li, B.; Tong, S.H.; Chang, I.K.; Wang, K. A discrete spatial model for wafer yield prediction. Qual. Eng. 2018, 30, 169–182. [Google Scholar] [CrossRef]

- Ahmadi, A.; Stratigopoulos, H.G.; Huang, K.; Nahar, A.; Orr, B.; Pas, M.; Carulli, J.M., Jr.; Makris, Y. Yield forecasting across semiconductor fabrication plants and design generations. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2017, 36, 2120–2133. [Google Scholar] [CrossRef]

- Kumar, N.; Kennedy, K.; Gildersleeve, K.; Abelson, R.; Mastrangelo, C.M.; Montgomery, D.C. A review of yield modelling techniques for semiconductor manufacturing. Int. J. Prod. Res. 2006, 44, 5019–5036. [Google Scholar] [CrossRef]

- Kim, J.S.; Jang, S.J.; Kim, T.W.; Lee, H.J.; Lee, J.B. A productivity-oriented wafer map optimization using yield model based on machine learning. IEEE Trans. Semicond. Manuf. 2018, 32, 39–47. [Google Scholar] [CrossRef]

- Pfitzner, L.; Benesch, N.; Öchsner, R.; Schmidt, C.; Schneider, C.; Tschaftary, T.; Trunk, R.; Dudenhausen, H.M. Cost reduction strategies for wafer expenditure. Microelectron. Eng. 2001, 56, 61–71. [Google Scholar] [CrossRef]

- Kuo, W.; Kim, T. An overview of manufacturing yield and reliability modeling for semiconductor products. Proc. IEEE 1999, 87, 1329–1344. [Google Scholar] [CrossRef]

- Chou, P.H.; Chiang, K.N.; Liang, S.Y. Reliability assessment of wafer level package using artificial neural network regression model. J. Mech. 2019, 35, 829–837. [Google Scholar] [CrossRef]

- Xu, H.W.; Zhang, Q.H.; Sun, Y.N.; Chen, Q.L.; Qin, W.; Lv, Y.L.; Zhang, J. A fast ramp-up framework for wafer yield improvement in semiconductor manufacturing systems. J. Manuf. Syst. 2024, 76, 222–233. [Google Scholar] [CrossRef]

- Tirkel, I. Cycle time prediction in wafer fabrication line by applying data mining methods. In Proceedings of the 2011 IEEE/SEMI Advanced Semiconductor Manufacturing Conference, San Francisco, CA, USA, 16–18 May 2011; pp. 1–5. [Google Scholar]

- Dong, H.; Chen, N.; Wang, K. Wafer yield prediction using derived spatial variables. Qual. Reliab. Eng. Int. 2017, 33, 2327–2342. [Google Scholar] [CrossRef]

- PDF Solutions Semiconductor Manufacturing Data 101—An Introduction. Available online: https://www.pdf.com/semiconductor-manufacturing-data-101-an-introduction/?utm_source=chatgpt.com/ (accessed on 31 August 2025).

- Ma, J.; Zhang, T.; Yang, C.; Cao, Y.; Xie, L.; Tian, H.; Li, X. Review of wafer surface defect detection methods. Electronics 2023, 12, 1787. [Google Scholar] [CrossRef]

- Amato, U.; Antoniadis, A.; De Feis, I.; Doinychko, A.; Gijbels, I.; La Magna, A.; Pagano, D.; Piccinini, F.; Suviseshamuthu, E.S.; Severgnini, C.; et al. Detecting important features and predicting yield from defects detected by SEM in semiconductor production. Sensors 2025, 25, 4218. [Google Scholar] [CrossRef]

- Chen, C.H.; Zhao, W.D.; Pang, T.; Lin, Y.Z. Virtual metrology of semiconductor PVD process based on combination of tree-based ensemble model. ISA Trans. 2020, 103, 192–202. [Google Scholar] [CrossRef]

- Kenney, J.; Valcore, J.; Riggs, S.; Rietman, E. Deep learning regression of VLSI plasma etch metrology. arXiv 2019, arXiv:1910.10067. [Google Scholar] [CrossRef]

- Qin, F.; Zhang, L.; Chen, P.; An, T.; Dai, Y.; Gong, Y.; Yi, Z.; Wang, H. In situ wireless measurement of grinding force in silicon wafer self-rotating grinding process. Mech. Syst. Signal Process. 2021, 154, 107550. [Google Scholar] [CrossRef]

- Chien, C.F.; Chen, C.C. Adaptive parametric yield enhancement via collinear multivariate analytics for semiconductor intelligent manufacturing. Appl. Soft Comput. 2021, 108, 107385. [Google Scholar] [CrossRef]

- Pan, J.C.H.; Tai, D.H. Implementing virtual metrology for in-line quality control in semiconductor manufacturing. Int. J. Syst. Sci. 2009, 40, 461–470. [Google Scholar] [CrossRef]

- Krueger, D.C.; Montgomery, D.C.; Mastrangelo, C.M. Application of generalized linear models to predict semiconductor yield using defect metrology data. IEEE Trans. Semicond. Manuf. 2010, 24, 44–58. [Google Scholar] [CrossRef]

- Caglayan, C.; Sertel, K. Experimental analysis of repeatability and calibration residuals in on-wafer non-contact probing. IEEE Trans. Microw. Theory Tech. 2017, 65, 2185–2191. [Google Scholar] [CrossRef]

- Lee, T.; Kim, C.O. Statistical comparison of fault detection models for semiconductor manufacturing processes. IEEE Trans. Semicond. Manuf. 2014, 28, 80–91. [Google Scholar] [CrossRef]

- Chen, Y.J.; Wang, B.C.; Wu, J.Z.; Wu, Y.C.; Chien, C.F. Big data analytic for multivariate fault detection and classification in semiconductor manufacturing. In Proceedings of the 2017 13th IEEE Conference on Automation Science and Engineering (CASE), Xi’an, China, 20–23 August 2017; pp. 731–736. [Google Scholar]

- Jiang, D.; Lin, W.; Raghavan, N. A Gaussian mixture model clustering ensemble regressor for semiconductor manufacturing final test yield prediction. IEEE Access 2021, 9, 22253–22263. [Google Scholar] [CrossRef]

- Arnold, N.N.A. Wafer Defect Prediction with Statistical Machine Learning. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, 2016. [Google Scholar]

- Liu, Y. Predictive Modeling for Intelligent Maintenance in Complex Semiconductor Manufacturing Processes. Ph.D. Thesis, University of Michigan, Ann Arbor, MI, USA, 2008. [Google Scholar]

- Iskandar, J.; Moyne, J.; Subrahmanyam, K.; Hawkins, P.; Armacost, M. Predictive maintenance in semiconductor manufacturing. In Proceedings of the 2015 26th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 3–6 May 2015; pp. 384–389. [Google Scholar]

- Zhu, L.; Chen, J.; Chen, C.I. Prognostics of tool failing behavior based on autoassociative Gaussian process regression for semiconductor manufacturing. In Proceedings of the 2020 IEEE International Conference on Industrial Technology (ICIT), Buenos Aires, Argentina, 26–28 February 2020; pp. 316–321. [Google Scholar]

- Zhu, L.; Chen, J.; Chen, C.I. Prognostics for semiconductor sustainability: Tool failure behavior prediction in fabrication processes. IEEE Trans. Syst. Man Cybern. Syst. 2024, 54, 3450–3460. [Google Scholar] [CrossRef]

- Kim, T.; Behdinan, K. Advances in machine learning and deep learning applications towards wafer map defect recognition and classification: A review. J. Intell. Manuf. 2023, 34, 3215–3247. [Google Scholar] [CrossRef]

- Munirathinam, S.; Ramadoss, B. Predictive models for equipment fault detection in the semiconductor manufacturing process. IACSIT Int. J. Eng. Technol. Innov. 2016, 8, 273–285. [Google Scholar][Green Version]

- Del Castillo, E.; Hurwitz, A.M. Run-to-run process control: Literature review and extensions. J. Qual. Technol. 1997, 29, 184–196. [Google Scholar] [CrossRef]

- Chemali, C.E.; Freudenberg, J.; Hankinson, M.; Bendik, J.J. Run-to-run critical dimension and sidewall angle lithography control using the PROLITH simulator. IEEE Trans. Semicond. Manuf. 2004, 17, 388–401. [Google Scholar] [CrossRef]

- Wan, J.; McLoone, S. Gaussian process regression for virtual metrology-enabled run-to-run control in semiconductor manufacturing. IEEE Trans. Semicond. Manuf. 2017, 31, 12–21. [Google Scholar] [CrossRef]

- Martin, A.; Vollertsen, R.P. An introduction to fast wafer level reliability monitoring for integrated circuit mass production. Microelectron. Reliab. 2007, 44, 1209–1231. [Google Scholar] [CrossRef]

- Bensoussan, A. Microelectronic reliability models for more than Moore nanotechnology products. Facta Univ. Ser. Electron. Energ. 2016, 30, 1–25. [Google Scholar] [CrossRef]

- Su, Q.H.; Chiang, K.N. Predicting wafer-level package reliability life using mixed supervised and unsupervised machine learning algorithms. Materials 2022, 15, 3897. [Google Scholar] [CrossRef] [PubMed]

- Kim, K.O.; Oh, H.S. Reliability functions estimated from commonly used yield models. Microelectron. Reliab. 2008, 48, 481–489. [Google Scholar] [CrossRef]

- Amrouch, H. Techniques for Aging, Soft Errors and Temperature to Increase the Reliability of Embedded On-Chip Systems. Ph.D. Thesis, Karlsruher Institut für Technologie (KIT), Karlsruhe, Germany, 2015. [Google Scholar]

- Lenhard, P.; Kovalenko, A.; Lenhard, R. Die level predictive modeling to reduce latent reliability defect escapes. Microelectron. Reliab. 2023, 148, 115139. [Google Scholar] [CrossRef]

- Behrendt, S.; Altenmüller, T.; May, M.C.; Kuhnle, A.; Lanza, G. Real-to-sim: Automatic simulation model generation for a digital twin in semiconductor manufacturing. J. Intell. Manuf. 2025, 1–20. [Google Scholar] [CrossRef]

- Cale, T.S.; Merchant, T.P.; Borucki, L.J.; Labun, A.H. Topography simulation for the virtual wafer fab. Thin Solid Film. 2000, 365, 152–175. [Google Scholar] [CrossRef]

- Sheng, C.; Dong, X.; Zhu, Y.; Wang, X.; Chen, X.; Xia, Y.; Xu, Z.; Zhou, P.; Wang, J.; Bao, W. Two-dimensional semiconductors: From device processing to circuit integration. Adv. Funct. Mater. 2023, 33, 2304778. [Google Scholar] [CrossRef]

- Nguyen, P.H.; Bär, E.; Lorenz, J.; Ryssel, H. Modeling of chemical–mechanical polishing on patterned wafers as part of integrated topography process simulation. Microelectron. Eng. 2004, 76, 89–94. [Google Scholar] [CrossRef]

- Graves, D.B.; Labelle, C.B.; Kushner, M.J.; Aydil, E.S.; Donnelly, V.M.; Chang, J.P.; Mayer, P.; Overzet, L.; Shannon, S.; Rauf, S.; et al. Science challenges and research opportunities for plasma applications in microelectronics. J. Vac. Sci. Technol. B 2024, 42, 042202. [Google Scholar] [CrossRef]

- Yao, A. Design-Technology Co-Optimization for Sub-2 nm Technology Node Based on 2D Materials. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, 2025. [Google Scholar]

- Sturtevant, J.; Capodieci, L. Design for manufacturing and design process technology co-optimization. In Microlithography; CRC Press: Boca Raton, FL, USA, 2020; pp. 293–326. [Google Scholar]

- Zhu, Y.; Tang, H.; Pan, Y.; Ouyang, P.; Ma, Y.; Xu, K. Meta-optimized LDMOS process–device co-optimization: Extrapolation-enhanced modeling with wafer-level validation. IEEE Trans. Electron Devices 2025, 72, 5089–5096. [Google Scholar] [CrossRef]

- Chen, S.N.; Chen, S.H. Application of generative adversarial networks for virtual silicon data generation and design-technology co-optimization: A study on WAT and CP. IEEE Access 2024, 12, 6532–6545. [Google Scholar] [CrossRef]

- Purwins, H.; Nagi, A.; Barak, B.; Höckele, U.; Kyek, A.; Lenz, B.; Pfeifer, G.; Weinzierl, K. Regression methods for prediction of PECVD Silicon Nitride layer thickness. In Proceedings of the 2011 IEEE International Conference on Automation Science and Engineering, Trieste, Italy, 24–27 August 2011; pp. 387–392. [Google Scholar]

- Zhang, Q.; Poolla, K.; Spanos, C.J. Across wafer critical dimension uniformity enhancement through lithography and etch process sequence: Concept, approach, modeling, and experiment. IEEE Trans. Semicond. Manuf. 2007, 20, 488–505. [Google Scholar] [CrossRef]

- Forsberg, M. Effect of process parameters on material removal rate in chemical mechanical polishing of Si (100). Microelectron. Eng. 2005, 77, 319–326. [Google Scholar] [CrossRef]

- Mahandran, C.J.; Fatah, A.Y.A.; Bani, N.A.; Kaidi, H.M.; Muhtazaruddin, M.B.; Amran, M.E. Thermal oxidation improvement in semiconductor wafer fabrication. Int. J. Power Electron. Drive Syst. 2019, 10, 1141–1147. [Google Scholar] [CrossRef]

- Shumate, D.A.; Montgomery, D.C. Development of a TiW plasma etch process using a mixture experiment and response surface optimization. IEEE Trans. Semicond. Manuf. 1996, 9, 335–343. [Google Scholar] [CrossRef]

- Liu, X.; Liu, Y.; Liang, Y.; Liu, H.; Hu, Y.; Gao, B. Optimization of slurry components for a copper chemical mechanical polishing at low down pressure using response surface methodology. Microelectron. Eng. 2011, 88, 99–104. [Google Scholar] [CrossRef]

- Shi, H.; Fang, Z.; Yang, D. Mechanism study of ion implantation on photoresist shrinkage. In Advances in Patterning Materials and Processes XXXV; SPIE: Bellingham, WA, USA, 2018; pp. 189–197. [Google Scholar]

- Jankovič, D.; Pipan, M.; Šimic, M.; Herakovič, N. Polynomial regression-based predictive expert system for enhancing hydraulic press performance over a 5G network. Appl. Sci. 2024, 14, 12016. [Google Scholar] [CrossRef]

- Mack, C.A.; Byers, J.D. Improved model for focus-exposure data analysis. In Metrology, Inspection, and Process Control for Microlithography XVII; SPIE: Bellingham, WA, USA, 2003; pp. 396–405. [Google Scholar]

- George, P.; Meng, J.; Jaluria, Y. Optimization of gallium nitride metalorganic chemical vapor deposition process. J. Heat Transf. 2015, 137, 061007. [Google Scholar] [CrossRef]

- Bae, S.J.; Hwang, J.Y.; Kuo, W. Yield prediction via spatial modeling of clustered defect counts across a wafer map. IIE Trans. 2007, 39, 1073–1083. [Google Scholar] [CrossRef]

- Jizat, J.A.M.; Majeed, A.P.A.; Nasir, A.F.A.; Taha, Z.; Yuen, E. Evaluation of the machine learning classifier in wafer defects classification. ICT Express 2021, 7, 535–539. [Google Scholar] [CrossRef]

- Lynn, S. Virtual Metrology for Plasma Etch Processes. Ph.D. Thesis, National University of Ireland, Maynooth, Ireland, 2011. [Google Scholar]

- Gonzalez Debs, M.; Kuech, T.F. Phenomenological modeling of diffusion profiles: Sn in GaAs. J. Appl. Phys. 2006, 99, 123710. [Google Scholar] [CrossRef]

- Jia, X.; Di, Y.; Feng, J.; Yang, Q.; Dai, H.; Lee, J. Adaptive virtual metrology for semiconductor chemical mechanical planarization process using GMDH-type polynomial neural networks. J. Process Control 2018, 62, 44–54. [Google Scholar] [CrossRef]

- Nami, Z.; Misman, O.; Erbil, A.; May, G.S. Semi-empirical neural network modeling of metal-organic chemical vapor deposition. IEEE Trans. Semicond. Manuf. 1997, 10, 288–294. [Google Scholar] [CrossRef]

- Huang, Y.; Rosakis, A.J. Extension of Stoney’s formula to non-uniform temperature distributions in thin film/substrate systems. The case of radial symmetry. J. Mech. Phys. Solids 2005, 53, 2483–2500. [Google Scholar] [CrossRef]

- Iwakoshi, T.; Hirota, K.; Mori, M.; Tanaka, J.I.; Itabashi, N. Prediction of etching results and etching stabilization by applying principal component regression to emission spectra during in-situ cleaning. Thin Solid Film. 2008, 516, 3464–3468. [Google Scholar] [CrossRef]

- Phatak, U.; Bukkapatnam, S.; Kong, Z.; Komanduri, R. Sensor-based modeling of slurry chemistry effects on the material removal rate (MRR) in copper-CMP process. Int. J. Mach. Tools Manuf. 2009, 49, 171–181. [Google Scholar] [CrossRef]

- Jeong, Y.S.; Hwang, S.; Ko, Y.D. Quantitative analysis for plasma etch modeling using optical emission spectroscopy: Prediction of plasma etch responses. Ind. Eng. Manag. Syst. 2015, 14, 392–400. [Google Scholar] [CrossRef][Green Version]

- Hong, S.J.; May, G.S.; Park, D.C. Neural network modeling of reactive ion etching using optical emission spectroscopy data. IEEE Trans. Semicond. Manuf. 2003, 16, 598–608. [Google Scholar] [CrossRef]

- Pan, C.C.; Bai, J.; Yang, G.K.; Wong, D.S.H.; Jang, S.S. An inferential modeling method using enumerative PLS based nonnegative garrote regression. J. Process Control 2012, 22, 1637–1646. [Google Scholar] [CrossRef]

- Khan, A.A.; Moyne, J.R.; Tilbury, D.M. Virtual metrology and feedback control for semiconductor manufacturing processes using recursive partial least squares. J. Process Control 2008, 18, 961–974. [Google Scholar] [CrossRef]

- Melhem, M.; Ananou, B.; Ouladsine, M.; Pinaton, J. Regularized regression models to predict the product quality in multistep manufacturing. In Proceedings of the 2016 5th International Conference on Systems and Control (ICSC), Marrakesh, Morocco, 25–27 May 2016; pp. 31–36. [Google Scholar]

- Durowoju, E.S.; Olowonigba, J.K. Machine learning-driven process optimization in semiconductor manufacturing: A new framework for yield enhancement and defect reduction. Int. J. Adv. Res. Publ. Rev. 2024, 1, 110–130. [Google Scholar] [CrossRef]

- Park, C.; Kim, S.B. Virtual metrology modeling of time-dependent spectroscopic signals by a fused lasso algorithm. J. Process Control 2016, 42, 51–58. [Google Scholar] [CrossRef]

- Choi, J.; Son, Y.; Kang, J. Group-exclusive feature group Lasso and applications to automatic sensor selection for virtual metrology in semiconductor manufacturing. IEEE Trans. Semicond. Manuf. 2024, 37, 505–517. [Google Scholar] [CrossRef]

- Chen, H.; Leclair, J. Optimizing etching process recipe based on kernel ridge regression. J. Manuf. Process 2021, 61, 454–460. [Google Scholar] [CrossRef]

- Lee, G.; Wang, T.; Kim, D.; Jeong, M.K. Sparse group principal component analysis using elastic-net regularisation and its application to virtual metrology in semiconductor manufacturing. Int. J. Prod. Res. 2025, 63, 865–881. [Google Scholar] [CrossRef]

- Bao, L.; Wang, K.; Jin, R. A hierarchical model for characterising spatial wafer variations. Int. J. Prod. Res. 2014, 52, 1827–1842. [Google Scholar] [CrossRef]

- Krueger, D.C.; Montgomery, D.C. Modeling and analyzing semiconductor yield with generalized linear mixed models. Appl. Stoch. Models Bus. Ind. 2014, 30, 691–707. [Google Scholar] [CrossRef]

- Yuan, T.; Ramadan, S.Z.; Bae, S.J. Yield prediction for integrated circuits manufacturing through hierarchical Bayesian modeling of spatial defects. IEEE Trans. Reliab. 2011, 60, 729–741. [Google Scholar] [CrossRef]

- Liu, J.P.; Jin, R.; Kong, Z.J. Wafer quality monitoring using spatial Dirichlet process based mixed-effect profile modeling scheme. J. Manuf. Syst. 2018, 48, 21–32. [Google Scholar] [CrossRef]

- Miyaguchi, K.; Joko, M.; Sheraw, R.; Idé, T. Wafer defect root cause analysis with partial trajectory regression DM: Big data management and machine learning. In Proceedings of the 36th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 5–8 May 2025; pp. 1–6. [Google Scholar]

- Orji, N.G.; Obeng, Y.S.; Beitia, C.; Mashiro, S.; Moyne, J. Virtual metrology white paper—International roadmap for devices and systems (IRDS). In International Roadmap for Devices and Systems (IRDS); IEEE: Piscataway, NJ, USA, 2018. [Google Scholar]

- Kim, D.; Kang, S. Effect of irrelevant variables on faulty wafer detection in semiconductor manufacturing. Energies 2019, 12, 2530. [Google Scholar] [CrossRef]

- Ishikawa, Y.; Otsuka, M.; Nagai, T.; Utsumi, T.; Takeda, M. Recursive partial least squares for process drift com pensation in plasma etch virtual metrology. IEEE Trans. Semicond. Manuf. 2010, 23, 310–319. [Google Scholar]

- Lee, H.; Kim, T.; Choi, B. Locally weighted PLS modeling for adaptive virtual metrology in plasma etching pro cesses. J. Process Control 2017, 58, 49–60. [Google Scholar]

- Lee, Y.; Roh, Y. An expandable yield prediction framework using explainable artificial intelligence for semiconductor manufacturing. Appl. Sci. 2023, 13, 2660. [Google Scholar] [CrossRef]

- Puggini, L.; McLoone, S. An enhanced variable selection and isolation forest-based methodology for anomaly detection with OES data. Eng. Appl. Artif. Intell. 2018, 67, 126–135. [Google Scholar] [CrossRef]

- Kazemi, P.; Masoumian, A.; Martin, P. Fault detection and isolation for time-varying processes using neural-based principal component analysis. Processes 2024, 12, 1218. [Google Scholar] [CrossRef]

- Lynn, S.A.; Ringwood, J.; MacGearailt, N. Global and local virtual metrology models for a plasma etch process. IEEE Trans. Semicond. Manuf. 2011, 25, 94–103. [Google Scholar] [CrossRef]

- Pate, K.; Safier, P. Chemical metrology methods for CMP quality. In Advances in Chemical Mechanical Planarization (CMP); Woodhead Publishing: Cambridge, UK, 2022; pp. 355–383. [Google Scholar]

- Deivendran, B.; Masampally, V.S.; Nadimpalli, N.R.V.; Runkana, V. Virtual metrology for chemical mechanical planarization of semiconductor wafers. J. Intell. Manuf. 2025, 36, 1923–1942. [Google Scholar] [CrossRef]

- Jiang, D.; Lin, W.; Raghavan, N. Semiconductor manufacturing final test yield optimization and wafer acceptance test parameter inverse design using multi-objective optimization algorithms. IEEE Access 2021, 9, 137655–137666. [Google Scholar] [CrossRef]

- Miller, R.B.; Riordan, W.C. Unit level predicted yield: A method of identifying high defect density die at wafer sort. In Proceedings of the International Test Conference 2001 (Cat. No. 01CH37260), Baltimore, MD, USA, 1 November 2001; pp. 1118–1127. [Google Scholar]

- Leite, D.; Andrade, E.; Rativa, D.; Maciel, A.M. Fault detection and diagnosis in industry 4.0: A review on challenges and opportunities. Sensors 2024, 25, 60. [Google Scholar] [CrossRef]

- Park, H.; Choi, J.E.; Kim, D.; Hong, S.J. Artificial immune system for fault detection and classification of semiconductor equipment. Electronics 2021, 10, 944. [Google Scholar] [CrossRef]

- Goodlin, B.E.; Boning, D.S.; Sawin, H.H.; Wise, B.M. Simultaneous fault detection and classification for semiconductor manufacturing tools. J. Electrochem. Soc. 2003, 150, G778–G784. [Google Scholar] [CrossRef]

- Kim, D.; Kang, P.; Cho, S.; Lee, H.J.; Doh, S. Machine learning-based novelty detection for faulty wafer detection in semiconductor manufacturing. Expert Syst. Appl. 2012, 39, 4075–4083. [Google Scholar] [CrossRef]

- Fan, S.K.S.; Hsu, C.Y.; Tsai, D.M.; He, F.; Cheng, C.C. Data-driven approach for fault detection and diagnostic in semiconductor manufacturing. IEEE Trans. Autom. Sci. Eng. 2020, 17, 1925–1936. [Google Scholar] [CrossRef]

- Ren, J.; Ni, D. A real-time monitoring framework for wafer fabrication processes with run-to-run variations. IEEE Trans. Semicond. Manuf. 2021, 34, 483–492. [Google Scholar] [CrossRef]

- Chen, J.H.; Kuo, T.W.; Lee, A.C. Run-by-run process control of metal sputter deposition: Combining time series and extended Kalman filter. IEEE Trans. Semicond. Manuf. 2007, 20, 278–285. [Google Scholar] [CrossRef]

- Chen, A.; Blue, J. Recipe-independent indicator for tool health diagnosis and predictive maintenance. IEEE Trans. Semicond. Manuf. 2009, 22, 522–535. [Google Scholar] [CrossRef]

- Blue, J.; Gleispach, D.; Roussy, A.; Scheibelhofer, P. Tool condition diagnosis with a recipe-independent hierarchical monitoring scheme. IEEE Trans. Semicond. Manuf. 2012, 26, 82–91. [Google Scholar] [CrossRef]

- Kasilingam, S.; Yang, R.; Singh, S.K.; Farahani, M.A.; Rai, R.; Wuest, T. Physics-based and data-driven hybrid modeling in manufacturing: A review. Prod. Manuf. Res. 2024, 12, 2305358. [Google Scholar] [CrossRef]

- Wang, J.; Li, Y.; Gao, R.X.; Zhang, F. Hybrid physics-based and data-driven models for smart manufacturing: Modelling, simulation, and explainability. J. Manuf. Syst. 2022, 63, 381–391. [Google Scholar] [CrossRef]

- Liu, Y.J.; Ni, D.; Shao, X.; Gong, D.L.; Li, J.J. A hierarchical model-based method for wafer level virtual metrology under process information deficiency. Qual. Eng. 2024, 36, 534–547. [Google Scholar] [CrossRef]

- Jeong, M.K.; Choi, J.; Son, Y.; Kang, J. Deep learning based virtual metrology and yield prediction in semiconductor manufacturing processes. In Proceedings of the PHM Society Asia-Pacific Conference, Jeju, Republic of Korea, 14 July 2017; Volume 1. [Google Scholar]

- Baly, R.; Hajj, H. Wafer classification using support vector machines. IEEE Trans. Semicond. Manuf. 2012, 25, 373–383. [Google Scholar] [CrossRef]

- Taha, K. Observational and experimental insights into machine learning-based defect classification in wafers. J. Intell. Manuf. 2025, 1–51. [Google Scholar] [CrossRef]

- Huang, A.C.; Meng, S.H.; Huang, T.J. A survey on machine and deep learning in semiconductor industry: Methods, opportunities, and challenges. Clust. Comput. 2023, 26, 3437–3472. [Google Scholar] [CrossRef]

- Shih, D.H.; Yang, C.Y.; Wu, T.W.; Shih, M.H. Investigating a machine learning approach to predicting white pixel defects in wafers—A case study of wafer fabrication plant F. Sensors 2024, 24, 3144. [Google Scholar] [CrossRef]

- Choi, J.; Suh, D.; Otto, M.O. Boosted stacking ensemble machine learning method for wafer map pattern classification. Comput. Mater. Contin. 2023, 74, 2945–2966. [Google Scholar] [CrossRef]

- Jeong, I.; Lee, S.Y.; Park, K.; Kim, I.; Huh, H.; Lee, S. Wafer map failure pattern classification using geometric transformation-invariant convolutional neural network. Sci. Rep. 2023, 13, 8127. [Google Scholar] [CrossRef]

- Rahman, M.W.; Vogl, G.W.; Jia, X.; Qu, Y. Physics-informed multi-task learning for material removal rate prediction in semiconductor chemical mechanical planarization. In Proceedings of the 2024 IEEE International Conference on Prognostics and Health Management (ICPHM), Denver, CO, USA, 10–13 June 2024; pp. 385–392. [Google Scholar]

- Yang, Y.; Liu, K.; Gao, Y.; Wang, C.; Cao, L. Advancements and challenges in inverse lithography technology: A review of artificial intelligence-based approaches. Light Sci. Appl. 2025, 14, 250. [Google Scholar] [CrossRef]

- Zhao, X.; Zheng, H.; Zhao, Z.; Cheng, M.; Li, W.; Wan, G.; Jia, Y. Warpage prediction of fan-out wafer-level package based on coupled deep learning and finite element simulation. Microelectron. Reliab. 2025, 170, 115759. [Google Scholar] [CrossRef]

- Kota, P.R. Real-Time Plasma Etch Rate Optimization Using Machine Learning-Based Neural Network Surrogate Models. 2025; Authorea Preprints. [Google Scholar]

- Kwon, J.W.; Ryu, S.; Park, J.; Lee, H.; Jang, Y.; Park, S.; Kim, G.H. Development of virtual metrology using plasma information variables to predict Si etch profile processed by SF6/O2/Ar capacitively coupled plasma. Materials 2021, 14, 3005. [Google Scholar] [CrossRef]

- Dailey, R.; Bertelson, S.; Kim, J.; Djurdjanovic, D. Virtual metrology of critical dimensions in plasma etch processes using entire optical emission spectrum. IEEE Trans. Semicond. Manuf. 2024, 37, 363–372. [Google Scholar] [CrossRef]

- Kang, P.; Kim, D.; Cho, S. Semi-supervised support vector regression based on self-training with label uncertainty: An application to virtual metrology in semiconductor manufacturing. Expert Syst. Appl. 2016, 51, 85–106. [Google Scholar] [CrossRef]

- Mamun, K.M.; Pala, N.; Shawkat, M.S.A. A comprehensive review of machine learning approaches for semiconductor device modeling and simulation. IEEE Access 2025, 13, 3605856. [Google Scholar] [CrossRef]

- Katari, M.; Shanmugam, L.; Malaiyappan, J.N.A. Integration of AI and machine learning in semiconductor manufacturing for defect detection and yield improvement. Int. J. Artif. Intell. Gen. Sci. 2024, 3, 418–431. [Google Scholar] [CrossRef]

- Soorya, K.; Michael, G. Prediction of yields in semiconductor using XGBoost classifier in comparison with random forest classifier. In Information Visualization for Intelligent Systems; Wiley Online Library: New York, NY, USA, 2025; Chapter 9; pp. 95–104. [Google Scholar]

- Mohammed, H.U.H. A data-driven framework for predicting defect density in semiconductor wafer fabrication using ensemble learning. Int. J. Intell. Syst. Appl. Eng. 2021, 9, 429–437. [Google Scholar]

- Kalir, A.A.; Lo, S.K.; Goldberg, G.; Zingerman-Koladko, I.; Ohana, A.; Revah, Y.; Chimol, T.B.; Honig, G. Leveraging machine learning for capacity and cost on a complex toolset: A case study. IEEE Trans. Semicond. Manuf. 2023, 36, 611–618. [Google Scholar] [CrossRef]

- Puthanveettil Madathil, A.; Luo, X.; Liu, Q.; Walker, C.; Madarkar, R.; Qin, Y. A review of explainable artificial intelligence in smart manufacturing. Int. J. Prod. Res. 2025, 1–44. [Google Scholar] [CrossRef]

- Choi, J.; Zhu, M.; Kang, J.; Jeong, M.K. Convolutional neural network based multi-input multi-output model for multi-sensor multivariate virtual metrology in semiconductor manufacturing. Ann. Oper. Res. 2024, 339, 185–201. [Google Scholar] [CrossRef]

- Bao, Y.Y.; Li, E.C.; Yang, H.Q.; Jia, B.B. Wafer map defect classification using autoencoder-based data augmentation and convolutional neural network. arXiv 2024, arXiv:2411.11029. [Google Scholar] [CrossRef]

- Kim, M.; Tak, J.; Shin, J. A deep learning model for wafer defect map classification: Perspective on classification performance and computational volume. Phys. Stat. Sol. 2024, 261, 2300113. [Google Scholar] [CrossRef]

- Tsai, T.H.; Lee, Y.C. A light-weight neural network for wafer map classification based on data augmentation. IEEE Trans. Semicond. Manuf. 2020, 33, 663–672. [Google Scholar] [CrossRef]

- Yoon, S.; Kang, S. Semi-automatic wafer map pattern classification with convolutional neural networks. Comput. Ind. Eng. 2022, 166, 107977. [Google Scholar] [CrossRef]

- Kim, D.; Kim, M.; Kim, W. Wafer edge yield prediction using a combined long short-term memory and feed-forward neural network model for semiconductor manufacturing. IEEE Access 2020, 8, 215125–215132. [Google Scholar] [CrossRef]

- Chang, Y.C.; Mastrangelo, C. Addressing multicollinearity in semiconductor manufacturing. Qual. Reliab. Eng. Int. 2011, 27, 843–854. [Google Scholar] [CrossRef]

- Magklaras, A.; Gogos, C.; Alefragis, P.; Birbas, A. Enhancing parameters tuning of overlay models with ridge regression: Addressing multicollinearity in high-dimensional data. Mathematics 2024, 12, 3179. [Google Scholar] [CrossRef]

- Li, Y.; Du, J.; Jiang, W. Reinforcement learning for process control with application in semiconductor manufacturing. IISE Trans. 2024, 56, 585–599. [Google Scholar] [CrossRef]

- Wu, X.; Chen, J.; Xie, L.; Chan, L.L.T.; Chen, C.I. Development of convolutional neural network based Gaussian process regression to construct a novel probabilistic virtual metrology in multi-stage semiconductor processes. Control Eng. Pract. 2020, 96, 104262. [Google Scholar] [CrossRef]

- Chan, L.L.T.; Wu, X.; Chen, J.; Xie, L.; Chen, C.I. Just-in-time modeling with variable shrinkage based on Gaussian processes for semiconductor manufacturing. IEEE Trans. Semicond. Manuf. 2018, 31, 335–342. [Google Scholar] [CrossRef]

- Zhou, L.; Chen, J.; Song, Z. Recursive Gaussian process regression model for adaptive quality monitoring in batch processes. Math. Probl. Eng. 2015, 761280. [Google Scholar] [CrossRef]

- Hosseinpour, F.; Ahmed, I.; Baraldi, P.; Zio, E.; Behzad, M.; Lewitschnig, H. A novel methodology based on long short-term memory stacked autoencoders for unsupervised detection of abnormal working conditions in semiconductor manufacturing systems. Proc. Inst. Mech. Eng. Part O J. Risk Reliab. 2024, 239, 1115–1133. [Google Scholar] [CrossRef]

- Xie, Y. Enhancing Efficiency and Accuracy in Virtual Metrology for Semiconductors with Innovative Sparse Dimensionality Reduction and Advanced Ensemble Learning for Multi-Source Data Analysis. Ph.D. Thesis, The State University of New Jersey, Rutgers, New Brunswick, NJ, USA, 2024. [Google Scholar]

- Serani, A.; Diez, M. A survey on design-space dimensionality reduction methods for shape optimization. arXiv 2024, arXiv:2405.13944. [Google Scholar] [CrossRef]

- Ghojogh, B.; Ghodsi, A.; Karray, F.; Crowley, M. Sufficient dimension reduction for high-dimensional regression and low-dimensional embedding: Tutorial and survey. arXiv 2021, arXiv:2110.09620. [Google Scholar]

- Ajana, S.; Acar, N.; Bretillon, L.; Hejblum, B.P.; Jacqmin-Gadda, H.; Delcourt, C. Benefits of dimension reduction in penalized regression methods for high-dimensional grouped data: A case study in low sample size. Bioinformatics 2019, 35, 3628–3634. [Google Scholar] [CrossRef]

- Lima, M.; Neto, M.; Silva Filho, T.; Fagundes, R.A.D.A. Learning under concept drift for regression—A systematic literature review. IEEE Access 2022, 10, 45410–45429. [Google Scholar] [CrossRef]

- Igual, J.; Gomes, H.M.; Pfahringer, B.; Bifet, A. Linear adaptive filtering for regression in data streams. Int. J. Data Sci. Anal. 2025, 50, 5017–5032. [Google Scholar] [CrossRef]

- Samuel, K.M.; Ahmed, F. Continual learning strategies for 3D engineering regression problems: A benchmarking study. J. Comput. Inf. Sci. Eng. 2025, 25, 101003. [Google Scholar] [CrossRef]

- Ou, F.; Suherman, J.; Zhang, C.; Wang, H.; Bom, S.; Davis, J.F.; Christofides, P.D. Industrial multi-machine data aggregation, AI-ready data preparation, and machine learning for virtual metrology in semiconductor wafer and slider production. Digit. Chem. Eng. 2025, 15, 100242. [Google Scholar] [CrossRef]

- Alangari, N.; El Bachir Menai, M.; Mathkour, H.; Almosallam, I. Exploring evaluation methods for interpretable machine learning: A survey. Information 2023, 14, 469. [Google Scholar] [CrossRef]

- Muckley, E.S.; Saal, J.E.; Meredig, B.; Roper, C.S.; Martin, J.H. Interpretable models for extrapolation in scientific machine learning. Digit. Discov. 2023, 2, 1425–1435. [Google Scholar] [CrossRef]

- Nazir, Z.; Kaldykhanov, D.; Tolep, K.K.; Park, J.G. A machine learning model selection considering tradeoffs between accuracy and interpretability. In Proceedings of the 2021 13th International Conference on Information Technology and Electrical Engineering (ICITEE), Chiang Mai, Thailand, 14–15 October 2021; pp. 63–68. [Google Scholar]

- Lang, C.I. Applications of Probabilistic Machine Learning Models to Semiconductor Fabrication. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, 2022. [Google Scholar]

- Teh, H.Y.; Kempa-Liehr, A.W.; Wang, K.I.K. Sensor data quality: A systematic review. J. Big Data 2020, 7, 11. [Google Scholar] [CrossRef]

- Siang, L.C.; Elnawawi, S.; Rippon, L.D.; O’Connor, D.L.; Gopaluni, R.B. Data quality over quantity: Pitfalls and guidelines for process analytics. IFAC-PapersOnLine 2023, 56, 7992–7999. [Google Scholar] [CrossRef]

- Halder, P.; Mojumder, S. Physics-guided denoiser network for enhanced additive manufacturing data quality. arXiv 2025, arXiv:2508.02712. [Google Scholar]

- Sofianidis, G.; Rožanec, J.M.; Mladenic, D.; Kyriazis, D. A review of explainable artificial intelligence in manufacturing. In Trusted Artificial Intelligence in Manufacturing: A Review of the Emerging Wave of Ethical and Human Centric AI Technologies for Smart Production; Now Publishers: Norwell, MA, USA, 2021; pp. 93–113. [Google Scholar]

- Lisboa, P.J.; Saralajew, S.; Vellido, A.; Fernández-Domenech, R.; Villmann, T. The coming of age of interpretable and explainable machine learning models. Neurocomputing 2023, 535, 25–39. [Google Scholar] [CrossRef]

- Kusiak, A. Predictive models in digital manufacturing: Research, applications, and future outlook. Int. J. Prod. Res. 2023, 61, 6052–6062. [Google Scholar] [CrossRef]

- Davis, J.C.; Mozumder, P.K.; Burch, R.; Fernando, C.; Apte, P.P.; Saxena, S.; Rao, S.; Vasanth, K. Automatic synthesis of equipment recipes from specified wafer-state transitions. IEEE Trans. Semicond. Manuf. 2002, 11, 527–536. [Google Scholar] [CrossRef]

- Shim, J.; Cho, S.; Kum, E.; Jeong, S. Adaptive fault detection framework for recipe transition in semiconductor manufacturing. Comput. Ind. Eng. 2021, 161, 107632. [Google Scholar] [CrossRef]

- Chien, C.F.; Hung, W.T.; Liao, E.T.Y. Redefining monitoring rules for intelligent fault detection and classification via CNN transfer learning for smart manufacturing. IEEE Trans. Semicond. Manuf. 2022, 35, 158–165. [Google Scholar] [CrossRef]

- Li, Z.; Cai, R.; Ng, H.W.; Winslett, M.; Fu, T.Z.; Xu, B.; Yang, X.; Zhang, Z. Causal mechanism transfer network for time series domain adaptation in mechanical systems. ACM Trans. Intell. Syst. Technol. 2021, 12, 1–21. [Google Scholar] [CrossRef]

- Thavarajah, M. Real time inferencing of semiconductor wafer probing process using Machine Learning. In Proceedings of the 2024 IEEE 40th International Electronics Manufacturing Technology (IEMT), Penang, Malaysia, 16–18 October 2024; pp. 1–6. [Google Scholar]

- Horr, A.M. Real-time modeling for design and control of material additive manufacturing processes. Metals 2024, 14, 1273. [Google Scholar] [CrossRef]

- Horr, A.M.; Drexler, H. Real-time models for manufacturing processes: How to build predictive reduced models. Processes 2025, 13, 252. [Google Scholar] [CrossRef]

- Chen, Y.P.; Karkaria, V.; Tsai, Y.K.; Rolark, F.; Quispe, D.; Gao, R.X.; Cao, J.; Chen, W. Real-time decision-making for Digital Twin in additive manufacturing with Model Predictive Control using time-series deep neural networks. J. Manuf. Syst. 2025, 80, 412–424. [Google Scholar] [CrossRef]

- Kim, E.S.; Choi, S.H.; Lee, D.H.; Kim, K.J.; Bae, Y.M.; Oh, Y.C. An oversampling method for wafer map defect pattern classification considering small and imbalanced data. Comput. Ind. Eng. 2021, 162, 107767. [Google Scholar] [CrossRef]

- Han, T.; Taheri, Z.; Ko, H. Physics-informed neural networks For semiconductor film deposition: A Review. arXiv 2025, arXiv:2507.10983. [Google Scholar] [CrossRef]

- Di Cairano, S.; Kolmanovsky, I.V. Real-time optimization and model predictive control for aerospace and automotive applications. In Proceedings of the 2018 annual American control conference (ACC), Milwaukee, WI, USA, 27–29 June 2018; pp. 2392–2409. [Google Scholar]

- Singgih, I.K. Production flow analysis in a semiconductor fab using machine learning techniques. Processes 2021, 9, 407. [Google Scholar] [CrossRef]

- Leray, P.; De Gendt, S. Exploring machine learning for semiconductor process optimization: A systematic review. IEEE Trans. Artif. Intell 2024, 5, 5949–5989. [Google Scholar]

- Karkaria, V.; Goeckner, A.; Zha, R.; Chen, J.; Zhang, J.; Zhu, Q.; Cao, J.; Gao, R.X.; Chen, W. Towards a digital twin framework in additive manufacturing: Machine learning and bayesian optimization for time series process optimization. J. Manuf. Syst. 2024, 75, 322–332. [Google Scholar] [CrossRef]

- Liu, N.; Li, X.; Rajanna, M.R.; Reutzel, E.W.; Sawyer, B.; Rao, P.; Lua, J.; Phan, N.; Yu, Y. Deep neural operator enabled digital twin modeling for additive manufacturing. arXiv 2024, arXiv:2405.09572. [Google Scholar] [CrossRef]

- Senoner, J.; Netland, T.; Feuerriegel, S. Using explainable artificial intelligence to improve process quality: Evidence from semiconductor manufacturing. Manag. Sci. 2022, 68, 5704–5723. [Google Scholar] [CrossRef]

- INFICON. Edge AI: A Semiconductor Process Control Revolution (INFICON, 2025). Available online: https://www.inficon.com/en/news/edge-ai-a-semiconductor-process-control-revolution (accessed on 26 August 2025).

- Chen, M.; Wei, Z.; Li, L.; Zhang, K. Edge computing-based proactive control method for industrial product manufacturing quality prediction. Sci. Rep. 2024, 14, 1288. [Google Scholar] [CrossRef]

- SemiEngineering. When and Where to Implement AI/ML in Fabs. (SemiEngineering, 2023). Available online: https://semiengineering.com/when-and-where-to-implement-ai-ml-in-fabs/?utm_source=chatgpt.com (accessed on 28 August 2025).

| Aspect | Regression | Predictive Modeling |

|---|---|---|

| Focus | Explains and quantifies relationships between process variables and outputs [2,4,14] | Anticipates outcomes and future states such as yield, defect density, and equipment health [15,18,22] |

| Methods | Linear, multiple, logistic, partial least squares (PLS) regression [3,4,8] | Regression extended with machine learning: random forests (RF), support vector machines (SVM), deep learning (DL), Bayesian models [20,21,22] |

| Applications | Identifying parameter correlations, yield drivers, process window optimization, and virtual metrology (VM) [2,5,14] | Yield forecasting, fault detection and classification (FDC), tool health prediction, digital twins, real-time anomaly detection [15,18,20,23] |

| Strength | High interpretability, intense statistical rigor, practical for hypothesis testing [4,8,14] | High predictive accuracy, adaptability to nonlinear, high-dimensional, and noisy data streams [20,21,22] |

| Limitation | Less effective with highly nonlinear interactions, limited scalability to big data [3,14] | May lose interpretability, requires large datasets and high computing power [20,21,22] |

| Application Area | Description and Role of Regression | Examples/Methods | References |

|---|---|---|---|

| 2.1. Process–parameter relationship modeling | Quantifies mathematical relationships between process variables (etch time, plasma power, deposition rate, temperature) and wafer-level metrics (oxide thickness, line width, dopant concentration). Identifies critical parameters driving process performance. | Multiple linear regression to predict film thickness variation from tool settings. | [11,13,47] |

| 2.2. Metrology correlation | Relates inline metrology (critical dimension, overlay, film thickness) with end-of-line electrical test results. This system enables virtual metrology, rapid feedback, and proactive process control. This process improves yield, reduces cycle time, and enhances tool monitoring. | PLS regression to link scatterometry spectra with CD; regression to connect process parameters, metrology readings, and product quality; GLM on defect metrology for yield prediction and data integration strategies. | [6,11,14,48,49] |

| 2.3. Fault detection and excursion analysis | Uses regression residuals to reveal deviations between expected vs. actual performance. This system supports excursion analysis, fault detection, and identification of root causes of low yield and process drifts. | Regression residuals for chamber drift detection; data-driven diagnostic approaches for low yield; FD models with feature extraction, selection, and classification; two-stage frameworks with LASSO and random forest for FDC parameter ranking. | [50,51,52] |

| Application Area | Description and Role | Methods/Examples | References |

|---|---|---|---|

| 3.1. Yield prediction | Identifies variables most affecting yield and supports real-time monitoring. Predicts wafer/die yield from defect density, metrology, and test parameters. This process enables early detection of low-yield wafers to optimize cost and quality. | Logistic regression to classify wafers as pass/fail; GMM clustering + weighted ensemble regressor for FT yield prediction using WF data. | [33,53,54] |

| 3.2. Equipment health monitoring and predictive maintenance | The system anticipates tool failures using sensor logs, RF power, endpoint drift, vibration signals, and maintenance records. Enables condition-based maintenance, prevents downtime, and ensures process stability. | Predict chamber clean frequency; ML models (ANN, SVR, MLP, RF, ARIMA) tested on fab data; degradation pattern recognition; PdM frameworks. | [55,56,57,58] |

| 3.3. Defect density and pattern prediction | Predicts defect sources, spatial patterns, and recurring defect signatures using inspection and wafer map data. Supports rapid root cause analysis and implementation of corrective actions. | Machine learning classifiers; spatial predictive models; wafer defect maps from lithography, CMP, etch; correlation of tool/process data with yield impact. | [23,59,60] |

| 3.4. Process control and run-to-run (R2R) optimization | Maintains process stability and reduces variability via predictive modeling integrated into APC systems. Dynamically adjusts recipes using metrology and tool data. | VM-enabled R2R control with GPR models; metrology delay analysis; drift compensation; batch-to-batch optimization. | [61,62,63] |

| 3.5. Reliability and lifetime forecasting | Forecasts equipment wear, process drift, and product degradation. Supports DfR strategies and predictive maintenance to minimize downtime. | Survival/Weibull models; ML for TDDB, BTI, EM; wafer inline defect screening (prediction engine + clustering); RF + FEM for WLP reliability lifecycle. | [64,65,66,67,68,69] |

| 3.6. Virtual fabrication and digital twin | Creates high-fidelity digital replicas of processes, tools, and wafers. Integrates physics + ML to simulate recipes, yield outcomes, and “what-if” scenarios. | FEOL/BEOL transistor prediction; 3D CMP simulation (pad deformation, pressure); plasma–tool digital twins for reactor control/maintenance. | [2,70,71,72,73,74] |

| 3.7. Design–Technology Co-Optimization (DTCO) | Aligns chip design with process constraints to optimize performance, power, cost, and yield. ML accelerates prediction of manufacturability and design-yield trade-offs. | Layout-aware variability models; GANs for WAT/CP data generation; virtual wafer data for co-optimization of process + design. | [75,76,77,78] |

| Regression Method | Purpose/Description | Advantages in Wafer Manufacturing | Limitations/Challenges | Literature |

|---|---|---|---|---|

| Linear Regression (OLS) | Models a dependent variable as a linear combination of predictors (e.g., oxide thickness vs. process parameters). | Simple, interpretable; helpful for DOE and first-order process understanding. | Sensitive to multicollinearity and heteroscedasticity; poor for nonlinear effects. | [49,79] |

| Multiple Regression | This method extends OLS by modeling multiple inputs simultaneously to capture multi-factor interactions. | Captures interdependencies between process variables; supports DOE and RSM optimization. | Requires careful factor selection; collinearity can inflate variance. | [82,84] |

| Polynomial Regression | Fits nonlinear relationships using polynomial terms of predictors (e.g., quadratic, cubic). | This approach captures nonlinear behavior in etch, CMP, and CVD processes, improving accuracy over linear models. | Risk of overfitting and instability; requires cross-validation. | [84,88] |

| Logistic Regression | Predicts categorical or binary outcomes (e.g., pass/fail, defect/no defect). | This tool enables yield risk estimation, defect prediction, and quality classification. | Limited to binary/categorical outcomes; nonlinear decision boundaries. | [89,90] |

| Nonlinear Regression | Models nonlinear relationships between variables and outputs (e.g., etch rate, stress, yield). | Captures complex process behaviors (e.g., diffusion, plasma chemistry); supports virtual metrology. | Computationally intensive; may converge to local minima. | [93,94,95] |

| Principal Component Regression (PCR) | This method reduces multicollinearity by transforming correlated predictors into orthogonal principal components. | Effective for high-dimensional tool data (sensor signals, spectra); enhances model stability. | Principal components may lack direct physical meaning; may exclude minor but important factors. | [97,98] |

| Partial Least Squares Regression (PLSR) | Extracts latent variables that maximize covariance between predictors and outputs. | Robust for spectral and plasma data; enables real-time VM and R2R control. | Model interpretation is complex; it requires latent variable tuning. | [100,101] |

| Regularized Regression (Ridge, Lasso, Elastic Net) | Adds penalty terms to reduce overfitting and stabilize high-dimensional models. | This approach handles multicollinearity, identifies key process variables, and enhances generalization. | Requires hyperparameter tuning; interpretability may be reduced. | [106,107] |

| Hierarchical/Mixed-Effect Regression | Models multi-level data structures (e.g., wafer → lot → tool) with fixed and random effects. | Accounts for lot-to-lot and tool-to-tool differences; improves yield and defect prediction. | Complex parameter estimation; computational cost for large datasets. | [31,110,111] |

| Model/ Approach | Role and Application | Methods/Examples | References |

|---|---|---|---|

| Support Vector Regression (SVR) | This method captures nonlinear CD variation and maps process variables into higher-dimensional spaces. This supports VM, process optimization, and reduced inspection costs. | SVR for CD prediction [3,20,25]; Dailey et al. [149] used SVD-based OES + SVR for plasma etch VM; Kang et al. [150] proposed SS-SVR with PLR models, improving accuracy (+8%) and reducing training time. | [3,20,25,149,150] |

| Random Forests/Gradient Boosting | Handle noisy, high-dimensional fab data. Capture nonlinearities, rank features, and support yield prediction, defect classification, and root cause analysis. | Shih et al. [141] classified CMOS wafer defects with RF (~97% accuracy); Choi et al. [142] stacked models with XGBoost for wafer defect patterns; Mohammed et al. [154] integrated RF, XGBoost, LightGBM, and stacking for defect density; Kalir et al. [155] applied RF + LSTM for predictive maintenance; Lee et al. [158] used gradient boosting + SHAP for feature interpretation. | [138,139,141,142,151,152,153,154,155] |

| Neural Networks (NNs) | Model nonlinear input–output relations for yield, defects, and CD. Enable VM, predictive maintenance, anomaly detection, and decision optimization. | Choi et al. [157]: CNN for multivariate VM; Bao et al. [158]: CNN + autoencoder for noisy defect data; Jeong et al. [143]: CNN with radon transform and kernel flipping for geometric invariance. | [45,103,143,156,157,158] |

| Deep Learning (CNNs, LSTMs) | CNNs classify wafer map defect patterns; LSTMs capture time-series fab data for tool drift, yield forecasting, and predictive control. | Tsai et al. [160]: compact CNN for defect recognition; Yoon et al. [161]: CNN + EIL for wafer images; Kim et al. [159]: CNN with inception + skip connection for fast defect classification; Kim et al. [162]: LSTM + FFNN for edge yield trends. | [139,140,143,151,159,160,161,162] |

| Hybrid/Ensemble ML | Combine regression + ML for interpretable yet robust predictions. Effective on limited, imbalanced, or noisy data. | Choi et al. [142] used a stacked ensemble with boosting; Mohammed et al. [154] integrated RF/XGBoost/LightGBM; hybrid regression + DL models balance interpretability and accuracy [139]. | [139,142,154] |

| Category | Challenge | Description | Representative Studies |

|---|---|---|---|

| 7.1 Regression | 7.1.1 Multicollinearity | Strong correlations among tool/process parameters inflate the variance of estimates; wafer datasets are high-dimensional and interdependent. Methods include variable elimination, PCA, ridge regression, and PLS. | [12,163,164] |

| 7.1.2 Nonlinear and dynamic processes | Semiconductor processes are nonlinear, time-varying, and nonstationary. Linear regression struggles; advanced models (CNNs, Gaussian processes, recursive updates) improve predictions and uncertainty handling. | [166,167,168] | |

| 7.1.3 High-dimensional data | Sensors produce thousands of signals per wafer, creating overfitting risks. Requires dimensionality reduction (PCA, PLS, autoencoders, SDR, penalized regression). | [171,172,173] | |

| 7.1.4 Concept drift | Regression coefficients evolve as tools age, recipes shift, or fab conditions drift. Models must adapt via online learning, adaptive filtering, ensembling, or continuous learning strategies. | [174,175,176] | |

| 7.1.5 Interpretability vs. accuracy | Engineers prefer transparent models (linear regression, GAMs), but AI/ML often yields higher accuracy—recent approaches balance interpretability (EBMs, SOC metrics) with performance. | [178,179,180] |

| Category | Challenge | Description | Representative Studies |

|---|---|---|---|

| 7.2 Predictive Modeling | 7.2.1 Data quality and integration | Sensor streams may be noisy, missing, or misaligned across fab tools. Requires preprocessing, error correction, and domain-knowledge integration (PINNs). | [182,183,184] |

| 7.2.2 Model interpretability | Black-box AI (DL, ensembles) undermines trust in high-stakes fabs. Explainable AI (XAI) and transparent models improve adoption and ethical decision-making. | [185,186,187] | |

| 7.2.3 Tool-to-tool variation | Models trained on one tool often fail on others due to recipe/equipment differences. Solutions include adaptive learning, CNN-based FDC, and causal mechanism transfer networks. | [189,190,191] | |

| 7.2.4 Computational efficiency | Real-time fab-scale inference demands lightweight models. Hybrid ROMs, digital twins, and surrogate models accelerate prediction and control. | [193,194,195] | |

| 7.2.5 Imbalanced data | Defect samples are rare compared to regular wafers. Synthetic oversampling, CAE-based augmentation, and ensemble classifiers mitigate imbalance. | [139,142,196] |

| Category | Future Trend | Description | Representative Studies |

|---|---|---|---|

| 8.1 Hybrid physics–ML models | Integration of physical models with AI/ML | Embeds domain physics into machine learning to enhance robustness, interpretability, and accuracy in wafer processes (e.g., CMP, deposition). Combines governing equations, contact mechanics, and data-driven regression. | [29,133,197] |

| 8.2 Real-time predictive analytics | Models embedded in fab control systems | Predictive models must run in real time for corrective actions. Digital twins and reduced-order models enable cycle-time prediction, yield optimization, and proactive scheduling. | [21,190,199] |

| 8.3 Digital twins | Virtual replicas of wafer fab processes | Combines physics-based simulators and ML regression models to replicate process behavior, optimize parameters, and reduce variability. Supports proactive process monitoring and control. | [70,201,202] |

| 8.4 Explainable AI (XAI) | Improving interpretability of predictive models | Use of SHAP, Trace Shapley Attribution, and interpretable frameworks to balance accuracy and transparency. This tool helps engineers identify key process drivers, root causes, and yield variations. | [117,154,203] |

| 8.5 Edge AI deployment | AI running on equipment controllers | Pushes predictive inference to the sensor/equipment level for low-latency feedback. This feature enables in-tool control, anomaly detection, and real-time quality monitoring. | [204,205,206] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, H.-Y.; Chen, C. Review of Applications of Regression and Predictive Modeling in Wafer Manufacturing. Electronics 2025, 14, 4083. https://doi.org/10.3390/electronics14204083

Chen H-Y, Chen C. Review of Applications of Regression and Predictive Modeling in Wafer Manufacturing. Electronics. 2025; 14(20):4083. https://doi.org/10.3390/electronics14204083

Chicago/Turabian StyleChen, Hsuan-Yu, and Chiachung Chen. 2025. "Review of Applications of Regression and Predictive Modeling in Wafer Manufacturing" Electronics 14, no. 20: 4083. https://doi.org/10.3390/electronics14204083

APA StyleChen, H.-Y., & Chen, C. (2025). Review of Applications of Regression and Predictive Modeling in Wafer Manufacturing. Electronics, 14(20), 4083. https://doi.org/10.3390/electronics14204083