Stability Analysis of a Receiving-End VSC-HVDC System with Parallel-Connected VSCs

Abstract

1. Introduction

- A small-signal model of dual-receiving-end VSC-HVDC system connected to asymmetric weak grids is established, clarifying the interactive coupling relationships between AC network, control system, and DC-link;

- The influence of control strategy, asymmetrical grid strength, power flow direction, and tie line on the small-signal stability is analyzed, and a feasible SCR region constrained by power and topology is formed, providing guidance for dynamic adjustment of system parameters;

- Based on various influencing factors, a variety of operating conditions are constructed to validate the effectiveness of the feasible SCR region.

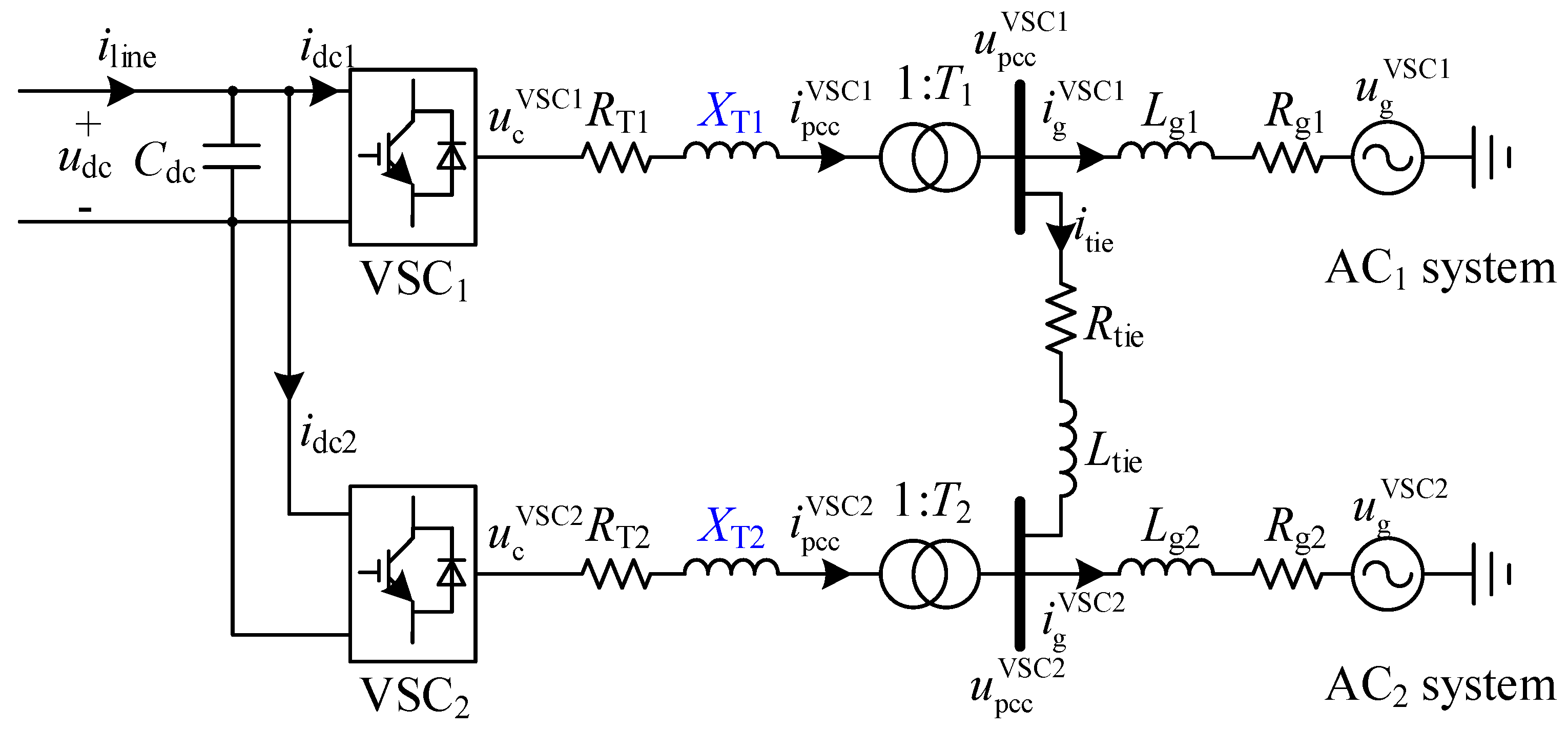

2. Structure and Controller of Dual-Receiving-End VSC-HVDC System

- The delays in the modulation process and sampling are neglected. This is because the modulation and sampling frequencies are typically much higher, mainly influencing the system’s high-frequency behavior, with limited effect on the 10–100 Hz frequency band that is the focus of this study [25];

- Since the power loss of the converter typically accounts for approximately 1% of its rated capacity, it is neglected in this study. Accordingly, the AC-side power of the VSC is assumed to be equal to its DC-side power [26];

- In the process of system modeling, the external characteristics of the receiving-end VSC-HVDC system serve as the main concern in this paper. As a result, its internal dynamic characteristics are neglected, and a two-level VSC is employed as a substitute for MMC [27].

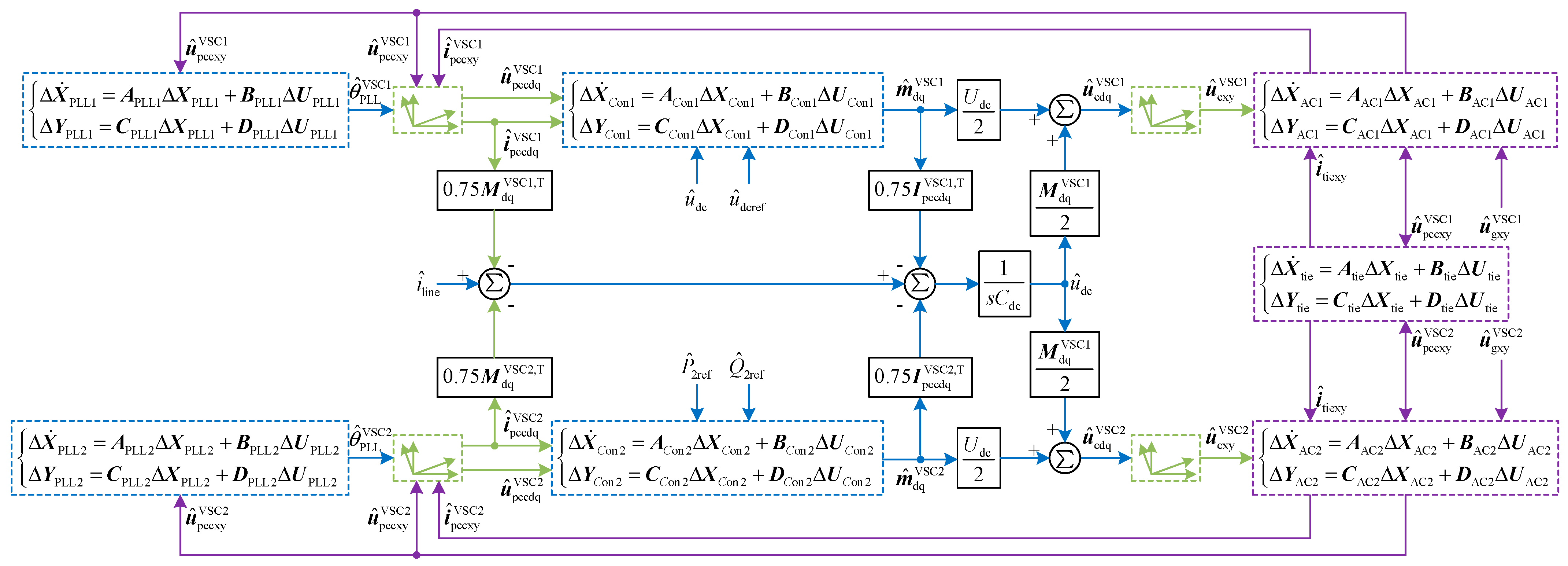

3. Small-Signal Modeling

3.1. Small-Signal Modeling of AC Network

3.2. Small-Signal Modeling of DC-Link

3.3. Small-Signal Modeling of Controller

3.4. Interconnection of Subsystem Models

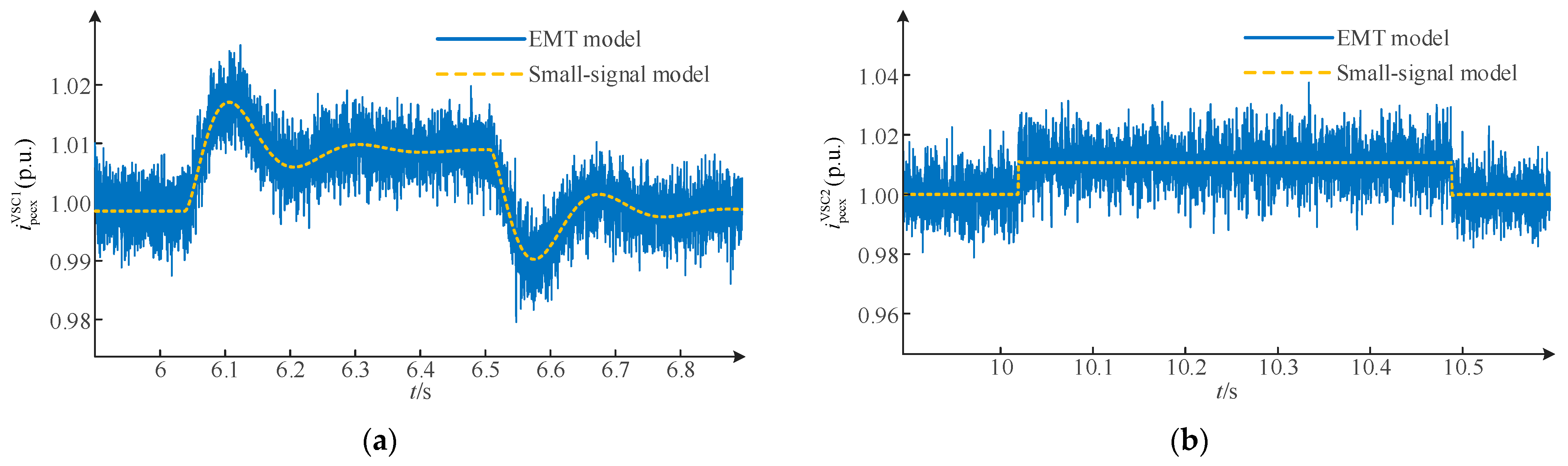

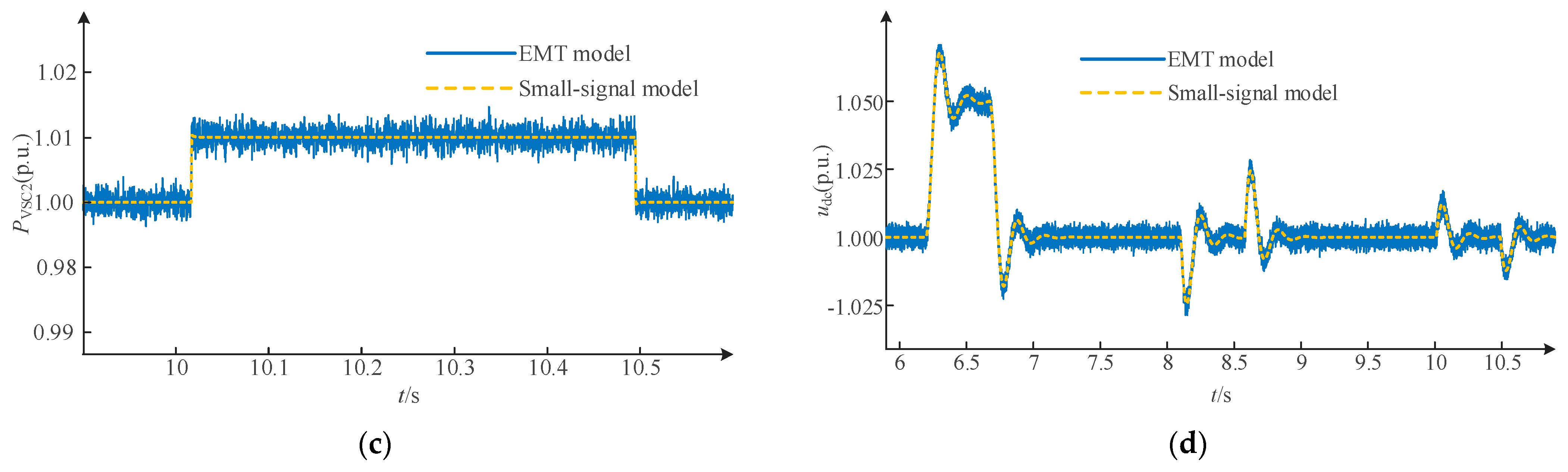

3.5. Model Validation

4. Construction of a Feasible SCR Region with Joint Power–Topology Constraints

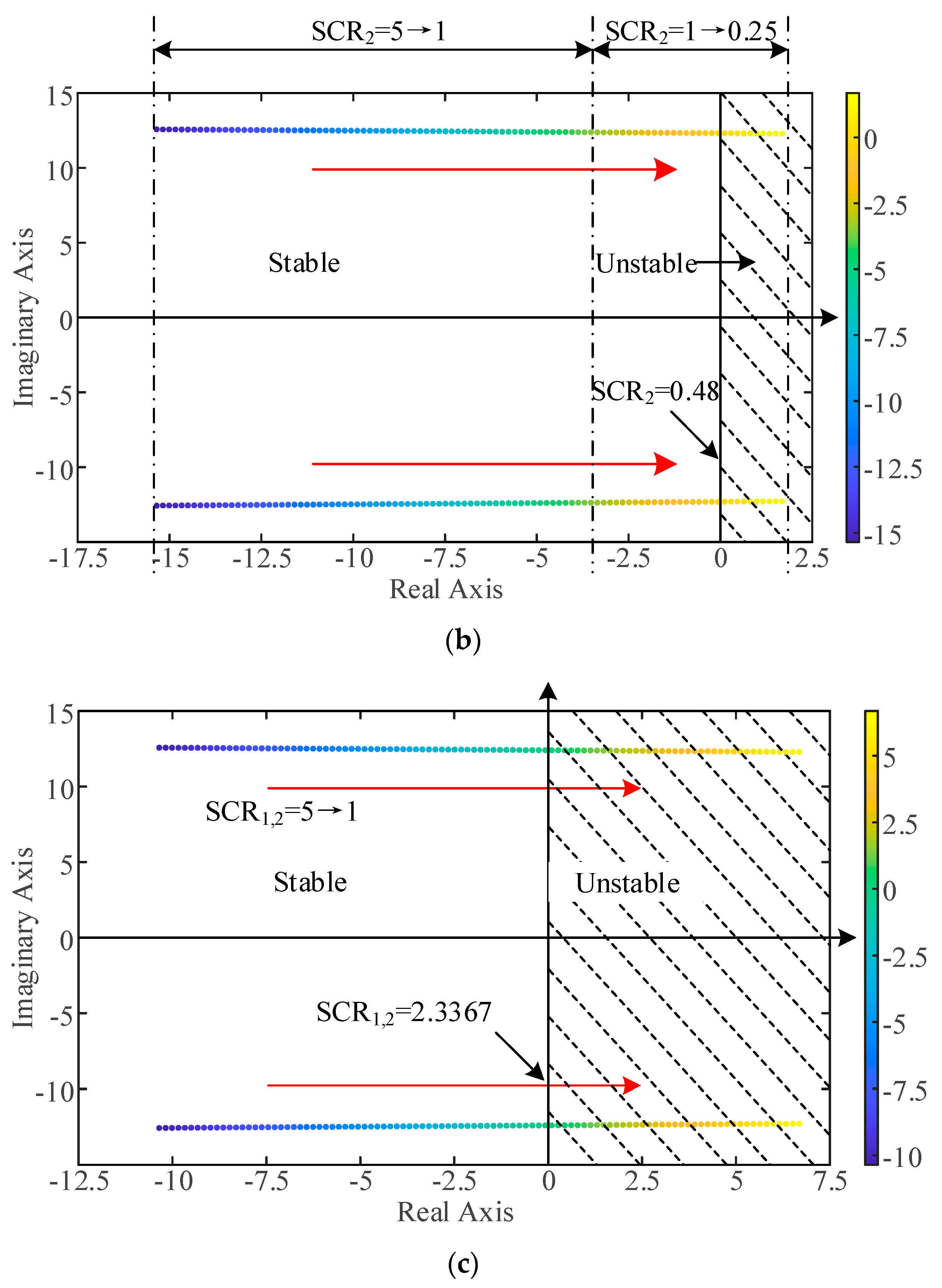

4.1. The Impact of AC System Strength

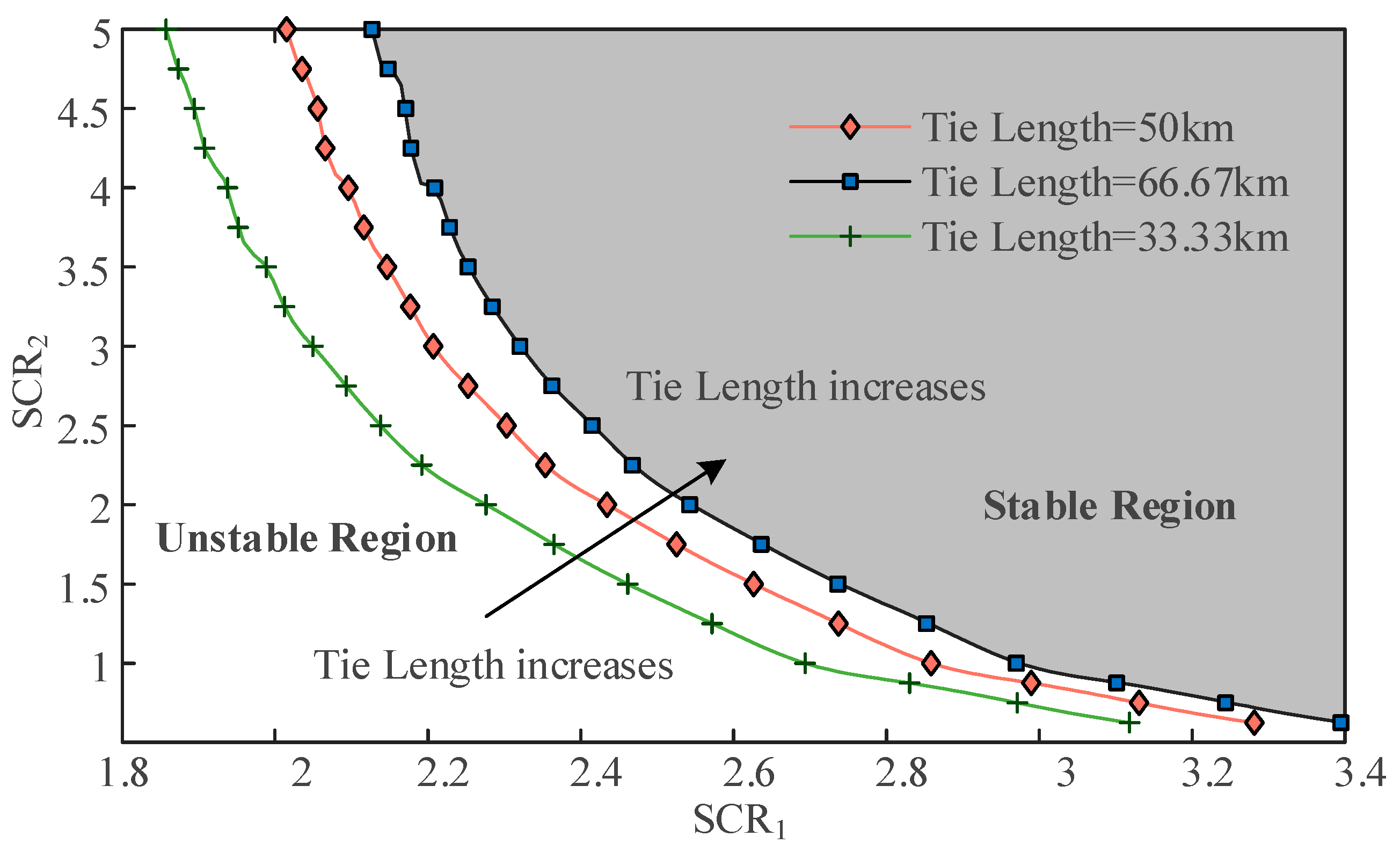

4.2. The Impact of Tie Line Length

4.3. The Impact of Power Condition for VSC2-HVDC

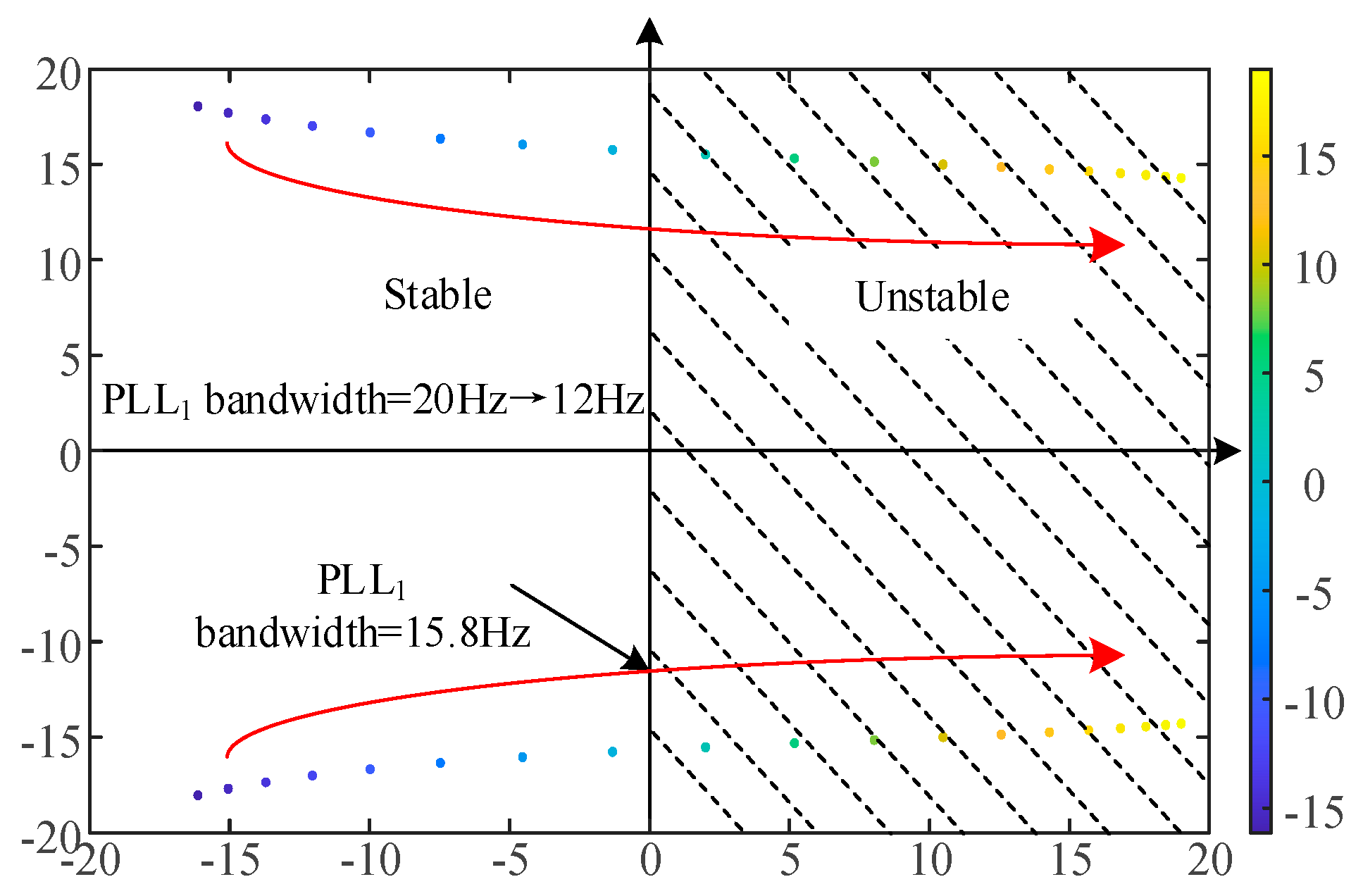

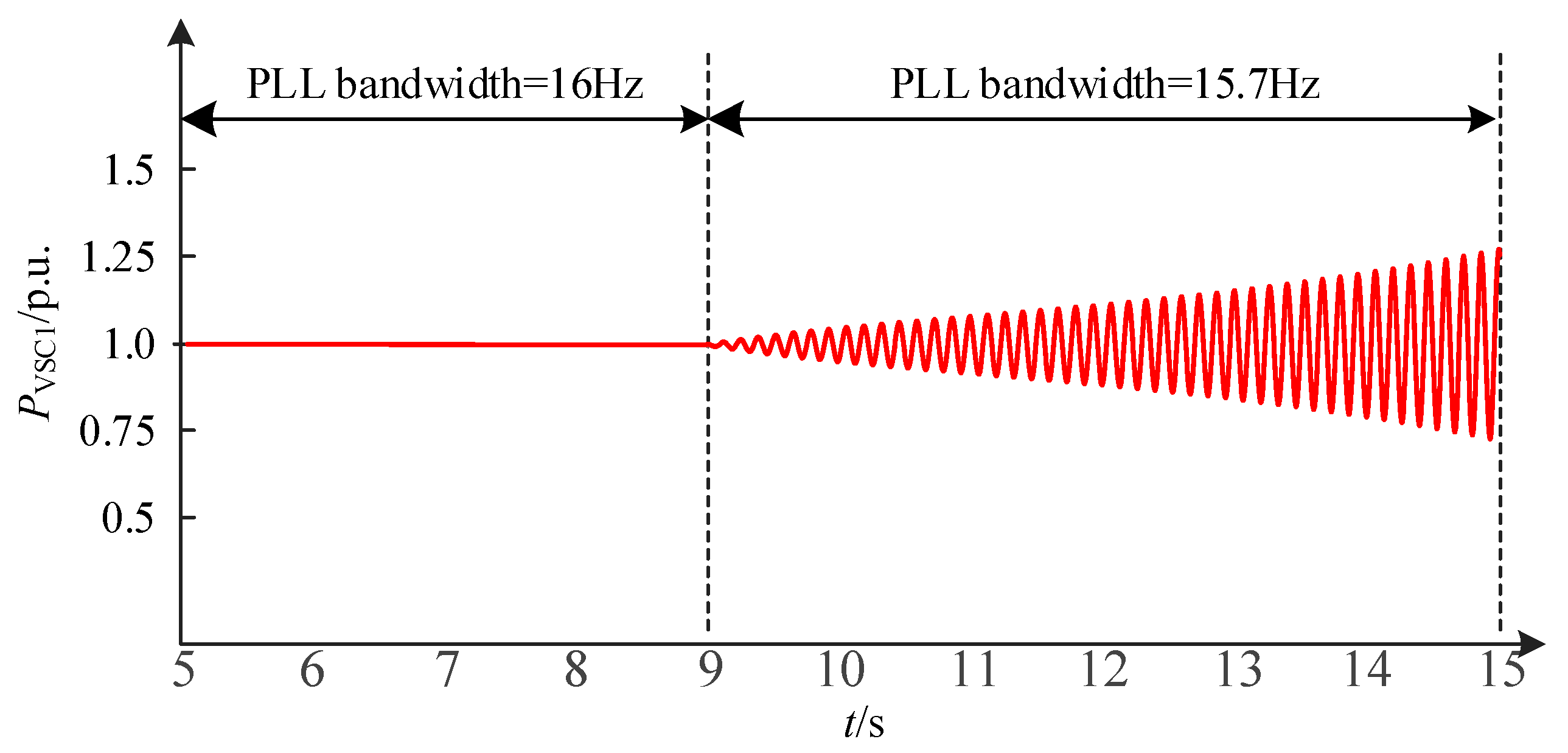

4.4. The Impact of PLL Bandwidth

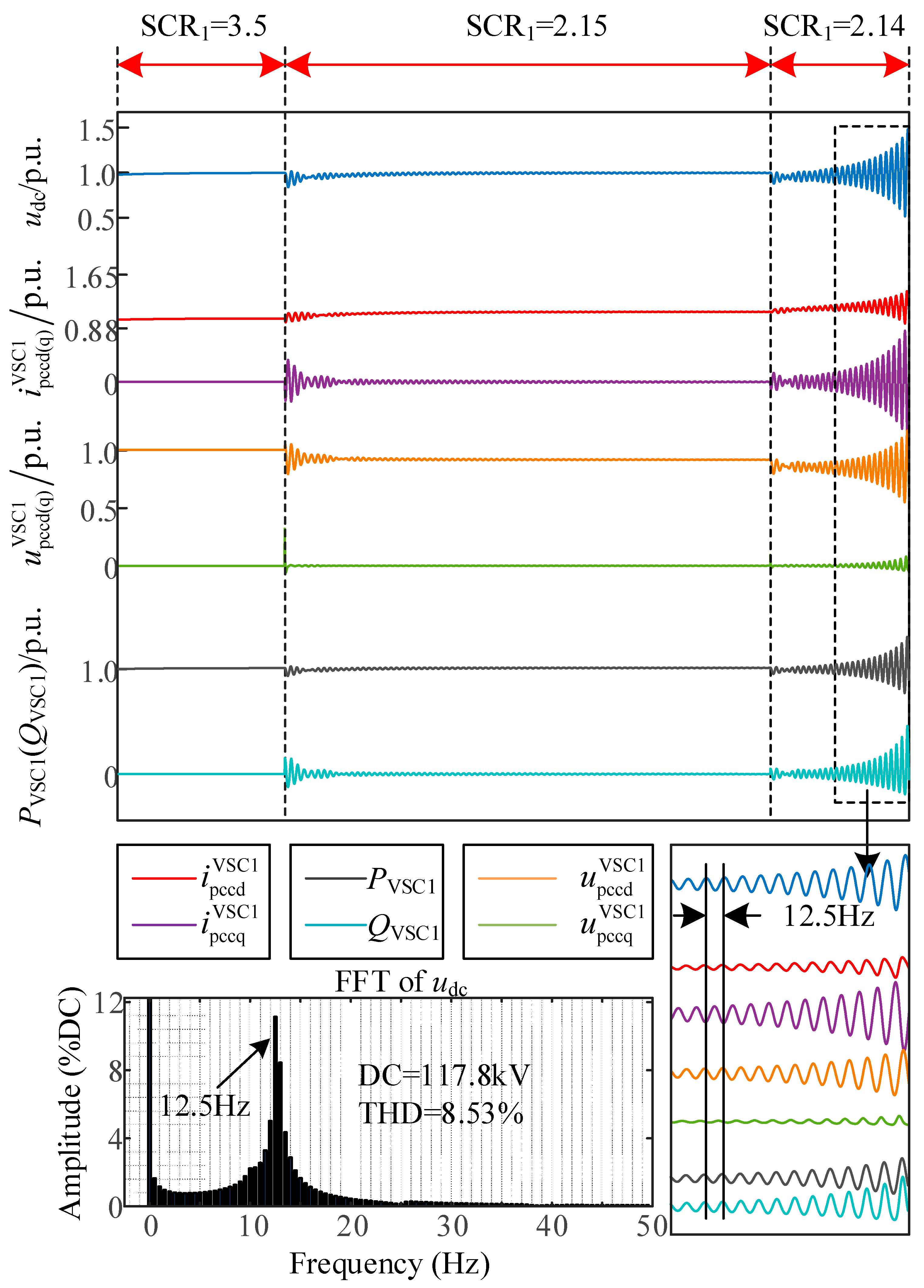

4.5. Simulation Verification

5. Conclusions

- Compared with the combined active/reactive power control strategy, DC voltage control strategy is more sensitive to changes in the power grid. Under conditions of the same rated power, it requires the configuration of a stronger AC system, and the state variable of DC voltage controller is the dominant factor causing this difference;

- An increase in the tie line length leads to a decrease in the area of the feasible SCR region, a reduction in the system’s stability margin, and an increase in the risk of instability. Moreover, the critical length is jointly determined by the outer loop control strategy and the asymmetric configuration of power grid;

- Compared with the combined active/reactive power control strategy, DC voltage control strategy exacerbates the influence of tie line length fluctuations on small-signal stability under weak grid conditions.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Nomenclatures

| Rgj, Lgj | Resistances and inductances of AC system (j = 1, 2) |

| RTj, XTj | Leakage resistance and Inductive inductance of transformer (j = 1, 2) |

| Rtie, Ltie | Resistance and inductance of tie line |

| Cdc | DC link capacitor |

| Voltage of AC system, PCC and VSC AC port (j = 1, 2) | |

| Current of AC system, VSC AC port and tie line (j = 1, 2) | |

| idcj | DC current of VSCj-HVDC (j = 1, 2) |

| udc | DC voltage |

| iline | Current of DC transmission line |

| xod1, xid1, xiq1 | State variables of controller for VSC1-HVDC |

| xod2, xod2, xid2, xiq2 | State variables of controller for VSC2-HVDC |

| ω0 | Rated angular frequency of AC system |

| State variables and output phase angles of PLL (j = 1, 2) |

References

- Ayaka, N.; Mikimasa, I.; Yasunobu, Y.; Naoto, K. Proposal of Emergency Operation and Active Power Dispatch Control Scheme for Bipolar VSC-MTDC System. IEEE Access. 2025, 13, 31590–31602. [Google Scholar]

- Li, D.; Wang, Z.; Gao, B.; Han, J.; Deng, F.; Li, Z. Improved Median Mode Decomposition Based Fault Detection Method in VSC Interfaced DC System. IEEE Trans. Instrum. Meas. 2025, 74, 1–10. [Google Scholar] [CrossRef]

- Zeng, Z.; Jiang, Z.; Liu, S.; Zhong, J.; Yan, Y.; Xie, Y. Corrective Security-Constrained Optimal Power Flow Considering Dynamic Thermal Line Rating and Fast Control of Battery Storage and VSC-HVDC. J. Energy Storage 2024, 100, 113705. [Google Scholar] [CrossRef]

- Jiang, H.; Zhou, Y.; Gao, Y.; Gao, S. Droop Frequency Limit Control and Its Parameter Optimization in VSC-HVDC Interconnected Power Grids. Energies 2024, 17, 3851. [Google Scholar] [CrossRef]

- Abdelaziz, Y.N.; Mansour, M.; Aboushady, A.A.; Alsokhiry, F.; Ahmed, K.H.; Abdel-khalik, A.S.; Al-Turki, Y. New Analysis of VSC-based Modular Multilevel DC-DC Converter with Low Interfacing Inductor for Hybrid LCC/VSC HVDC Network Interconnections. Alex. Eng. J. 2024, 95, 82–93. [Google Scholar] [CrossRef]

- Wu, X.; Yang, H.; Zheng, C.; Zou, Z. Model-Free Adaptive Control for Mitigation of SSO in PMSG Based Wind Farms with VSC-HVDC. IEEE Trans. Power Electron. 2025, 40, 3684–3696. [Google Scholar] [CrossRef]

- Xiang, F.; Liao, S.; Zhang, H.; Luo, L. Sub-synchronous Oscillation Phenomenon Analysis of Grid-connected Direct Drive-Doubly Fed Hybrid Wind Farms Via VSC-HVDC System. IEEE Access 2025, 13, 37966–37978. [Google Scholar] [CrossRef]

- Lu, X.; Wang, X.; Lin, W.; Wen, J. Comparative Study of Small-Signal Stability under Weak AC System Integration for Different VSCs. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 4482–4499. [Google Scholar] [CrossRef]

- Givaki, K.; Chen, D.; Xu, L. Current Error Based Compensations for VSC Current Control in Weak Grids for Wind Farm Applications. IEEE Trans. Sustain. Energy 2019, 10, 26–35. [Google Scholar] [CrossRef]

- Bakeer, A.; Chub, A.; Abid, A.; Zaid, S.A.; Alghamdi, T.A.H.; Salama, H.S. Enhancing Grid-Forming Converters Control in Hybrid AC/DC Microgrids Using Bidirectional Virtual Inertia Support. Processes 2024, 12, 139. [Google Scholar] [CrossRef]

- Guo, C.; Yang, S.; Liu, W.; Zhao, C.; Hu, J. Small-Signal Stability Enhancement Approach for VSC-HVDC System Under Weak AC Grid Conditions Based on Single-Input Single-Output Transfer Function Model. IEEE Trans. Power Del. 2021, 36, 1313–1323. [Google Scholar] [CrossRef]

- Morris, J.F.; Ahmed, K.H.; Alvarez, A.E. Analysis of Controller Bandwidth Interactions for Vector-Controlled VSC Connected to Very Weak AC Grids. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 7343–7354. [Google Scholar] [CrossRef]

- Gao, S.; Zhao, H.; Gui, Y.; Luo, J.; Blaabjerg, F. Impedance Analysis of Voltage Source Converter Using Direct Power Control. IEEE Trans. Energy Convers. 2021, 36, 831–840. [Google Scholar] [CrossRef]

- Zhang, Q.; McCalley, J.D.; Ajjarapu, V.; Renedo, J.; Elizondo, M.A.; Tbaileh, A.; Mohan, N. Primary Frequency Support Through North American Continental HVDC Interconnections with VSC-MTDC Systems. IEEE Trans. Power Syst. 2021, 36, 806–817. [Google Scholar] [CrossRef]

- Zhu, J.; Li, S.; Yu, L.; Bu, S.; Li, Y.; Wang, Y.; Deng, Z.; Liu, D.; Jia, H.; Wang, C. Coherence Analysis of System Characteristics and Control Parameters for Hybrid HVDC Transmission Systems Based on Small-Signal Modeling. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 7436–7446. [Google Scholar] [CrossRef]

- Guo, C.; Cui, P.; Zhao, C. Optimization and Configuration of Control Parameters to Enhance Small-signal Stability of Hybrid LCC-MMC HVDC System. J. Mod. Power Syst. Clean. Energy 2022, 10, 213–221. [Google Scholar] [CrossRef]

- Fu, Q.; Du, W.; Wang, H.; Ren, B.; Xiao, X. Small-Signal Stability Analysis of a VSC-MTDC System for Investigating DC Voltage Oscillation. IEEE Trans. Power Syst. 2021, 36, 5081–5091. [Google Scholar] [CrossRef]

- Pang, Y.; Egea-Alvarez, A.; Gonzalez-Torres, J.C.; Shinoda, K.; Perez, F.; Benchaib, A. DC Voltage Stability Analysis and Enhancement for Grid-Forming-Based MTDC Systems. IEEE Trans. Power Electron. 2024, 39, 12113–12117. [Google Scholar] [CrossRef]

- Zhou, Y.; Zhao, L.; Lee, W.-J. Robustness analysis of dynamic equivalent model of DFIG wind farm for stability study. In Proceedings of the 2018 IEEE/IAS 54th Industrial and Commercial Power Systems Technical Conference, Niagara Falls, ON, Canada, 7–10 May 2018. [Google Scholar]

- Ali, M.; Ilie, I.-S.; Milanovic, J.V.; Chicco, G. Wind farm model aggregation using probabilistic clustering. IEEE Trans. Power Syst. 2013, 28, 309–316. [Google Scholar] [CrossRef]

- Huang, L.; Xin, H.; Li, Z.; Ju, P.; Yuan, H.; Wang, G. Identification of generalized short-circuit ratio for on-line stability monitoring of wind farms. IEEE Trans. Power Syst. 2020, 35, 3282–3285. [Google Scholar] [CrossRef]

- Zhou, Y.; Zhao, L.; Lee, W.J. Robustness Analysis of Dynamic Equivalent Model of DFIG Wind Farm for Stability Study. IEEE Trans. Ind. Appl. 2018, 54, 5682–5690. [Google Scholar] [CrossRef]

- Dong, W.; Xin, H.; Wu, D.; Huang, L. Small Signal Stability Analysis of Multi-Infeed Power Electronic Systems Based on Grid Strength Assessment. IEEE Trans. Power Syst. 2019, 34, 1393–1403. [Google Scholar] [CrossRef]

- Meng, P.; Xiang, W.; Chi, Y.; Wang, Z.; Lin, W.; Wen, J. Resilient DC Voltage Control for Islanded Wind Farms Integration Using Cascaded Hybrid HVDC System. IEEE Trans. Power Syst. 2022, 37, 1054–1066. [Google Scholar] [CrossRef]

- Zhao, L.; Jin, Z.; Wang, X. Analysis and Damping of Low-Frequency Oscillation for DC-Link Voltage-Synchronized VSCs. IEEE Trans. Power Electron. 2023, 38, 8177–8189. [Google Scholar] [CrossRef]

- Chen, L.; Zhang, X.; Shi, Y.; Qi, L. A Novel Mixture-Devices-Based Submodule for MMC by Using Low on-State Voltage IGCT and High di/dt Ability IGBT. IEEE Trans. Ind. Electron. 2024, 71, 2375–2384. [Google Scholar] [CrossRef]

- Guo, Y.; Gao, H.; Wu, Q.; Zhao, H.; Østergaard, J.; Shahidehpour, M. Enhanced Voltage Control of VSC-HVDC-Connected Offshore Wind Farms Based on Model Predictive Control. IEEE Trans. Sustain. Energy 2017, 9, 474–487. [Google Scholar] [CrossRef]

- Fu, X.; Huang, M.; Pan, S.; Zha, X. Cascading Synchronization Instability in Multi-VSC Grid-Connected System. IEEE Trans. Power Electron. 2022, 37, 7572–7576. [Google Scholar] [CrossRef]

- Sun, P.; Yao, J.; Zhao, Y.; Fang, X.; Cao, J. Stability Assessment and Damping Optimization Control of Multiple Grid-connected Virtual Synchronous Generators. IEEE Trans. Energy Convers. 2021, 36, 3555–3567. [Google Scholar] [CrossRef]

- Xiao, H.; Li, Y. Multi-Infeed Voltage Interaction Factor: A Unified Measure of Inter-Inverter Interactions in Hybrid Multi-Infeed HVDC Systems. IEEE Trans. Power Del. 2019, 35, 2040–2048. [Google Scholar] [CrossRef]

- Kim, Y.K.; Lee, G.S.; Kim, C.K.; Moon, S.I. An Improved AC System Strength Measure for Evaluation of Power Stability and Temporary Overvoltage in Hybrid Multi-Infeed HVDC Systems. IEEE Trans. Power Del. 2022, 37, 638–649. [Google Scholar] [CrossRef]

- Xiao, H.; Li, Y.; Shi, D.; Chen, J.; Duan, X. Evaluation of Strength Measure for Static Voltage Stability Analysis of Hybrid Multi-Infeed DC Systems. IEEE Trans. Power Del. 2019, 34, 879–890. [Google Scholar] [CrossRef]

| Parameters | Values | |

|---|---|---|

| VSC1-HVDC subsystem | Rated DC voltage udc | 400 kV |

| Voltage of AC system | 525 kV | |

| SCR | 3.5 | |

| Rated active power | 1000 MW | |

| Transformer leakage impedance LT1/RT1 | 0.20 p.u./0.20 p.u. | |

| VSC2-HVDC subsystem | Voltage of AC system | 510.089 kV |

| SCR | 3.5 | |

| Rated DC voltage udc | 400 kV | |

| Rated active power | 1000 MW | |

| Transformer leakage impedance LT2/RT2 | 0.20 p.u./0.20 p.u. | |

| Tie line | Tie line length | 50 km |

| Tie line resistance Rtie | 28 mΩ/km | |

| Tie line inductance Ltie | 12.9 mH/km | |

| Parameters | Values |

|---|---|

| PLL bandwidth of VSC1-HVDC | 20 Hz |

| PLL bandwidth of VSC2-HVDC | 20 Hz |

| DVC parameters of VSC1-HVDC kpv/kiv | 5 × 10−7/0.1 |

| PQC parameters of VSC2-HVDC kpac/kiac | 7 × 10−6/7 × 10−5 |

| VCC parameters of VSC1-HVDC | 1.0/330 |

| VCC parameters of VSC2-HVDC | 0.5/300 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bin, Z.; Kong, X.; Zhao, K.; Wu, X.; Yuan, Y.; Ren, X. Stability Analysis of a Receiving-End VSC-HVDC System with Parallel-Connected VSCs. Electronics 2025, 14, 2178. https://doi.org/10.3390/electronics14112178

Bin Z, Kong X, Zhao K, Wu X, Yuan Y, Ren X. Stability Analysis of a Receiving-End VSC-HVDC System with Parallel-Connected VSCs. Electronics. 2025; 14(11):2178. https://doi.org/10.3390/electronics14112178

Chicago/Turabian StyleBin, Zijun, Xiangping Kong, Kai Zhao, Xi Wu, Yubo Yuan, and Xuchao Ren. 2025. "Stability Analysis of a Receiving-End VSC-HVDC System with Parallel-Connected VSCs" Electronics 14, no. 11: 2178. https://doi.org/10.3390/electronics14112178

APA StyleBin, Z., Kong, X., Zhao, K., Wu, X., Yuan, Y., & Ren, X. (2025). Stability Analysis of a Receiving-End VSC-HVDC System with Parallel-Connected VSCs. Electronics, 14(11), 2178. https://doi.org/10.3390/electronics14112178