T-Smade: A Two-Stage Smart Detector for Evasive Spectre Attacks Under Various Workloads

Abstract

1. Introduction

- (1)

- To design a well-generalized evasive Spectre attack detector, Spectre attack and non-attack datasets are used to train a detector capable of identifying evasive Spectre nop and evasive Spectre memory under the workloads of realistic application and stress test.

- (2)

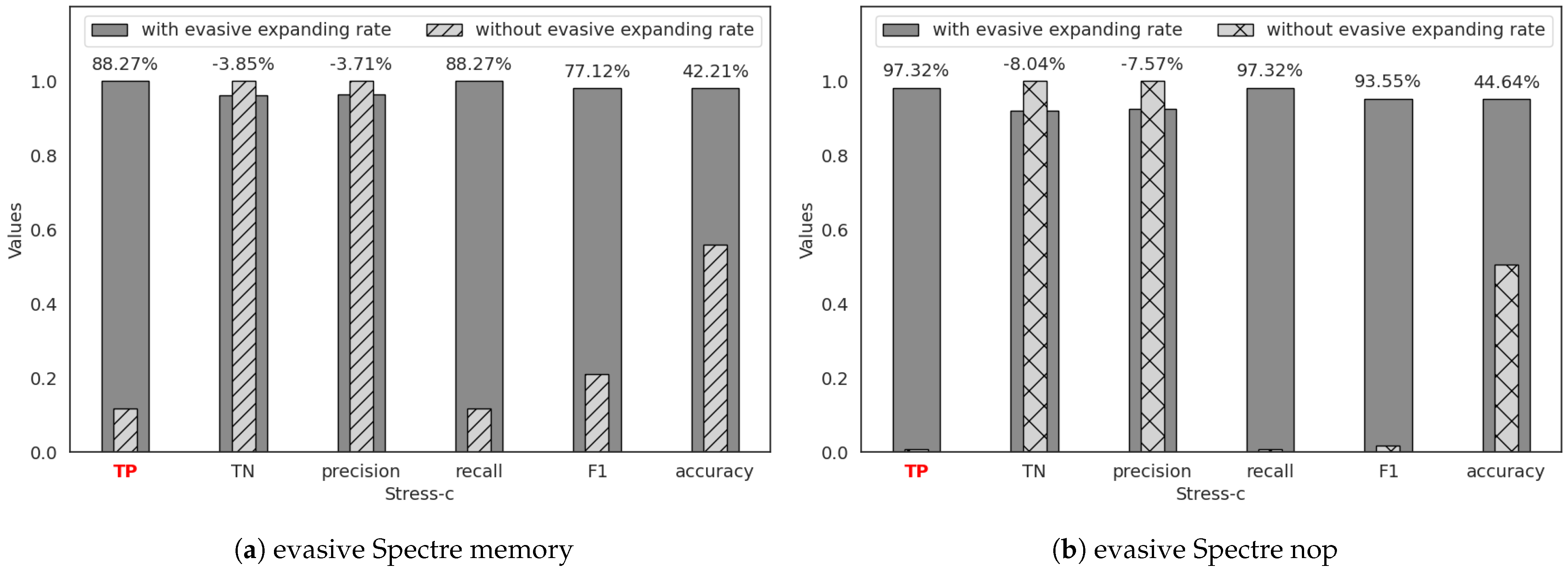

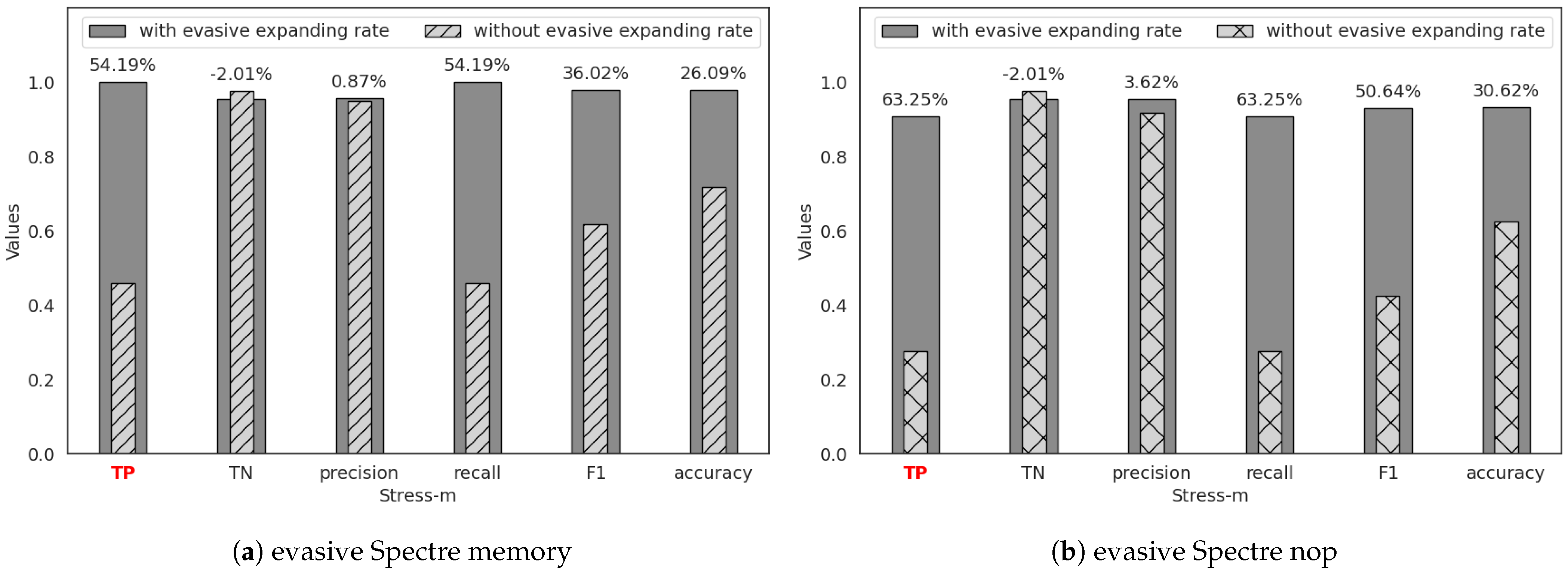

- To minimize extra performance overhead of HPC detector for evasive Spectre attacks, four existed HPC events are reused to further expands the features of evasive Spectre under different workloads. As a result, the average attack detection successful rate for evasive Spectre nop attacks returns from 27.52% to 95.42%, and that of evasive Spectre memory increases from 59.8% up to 100%.

- (3)

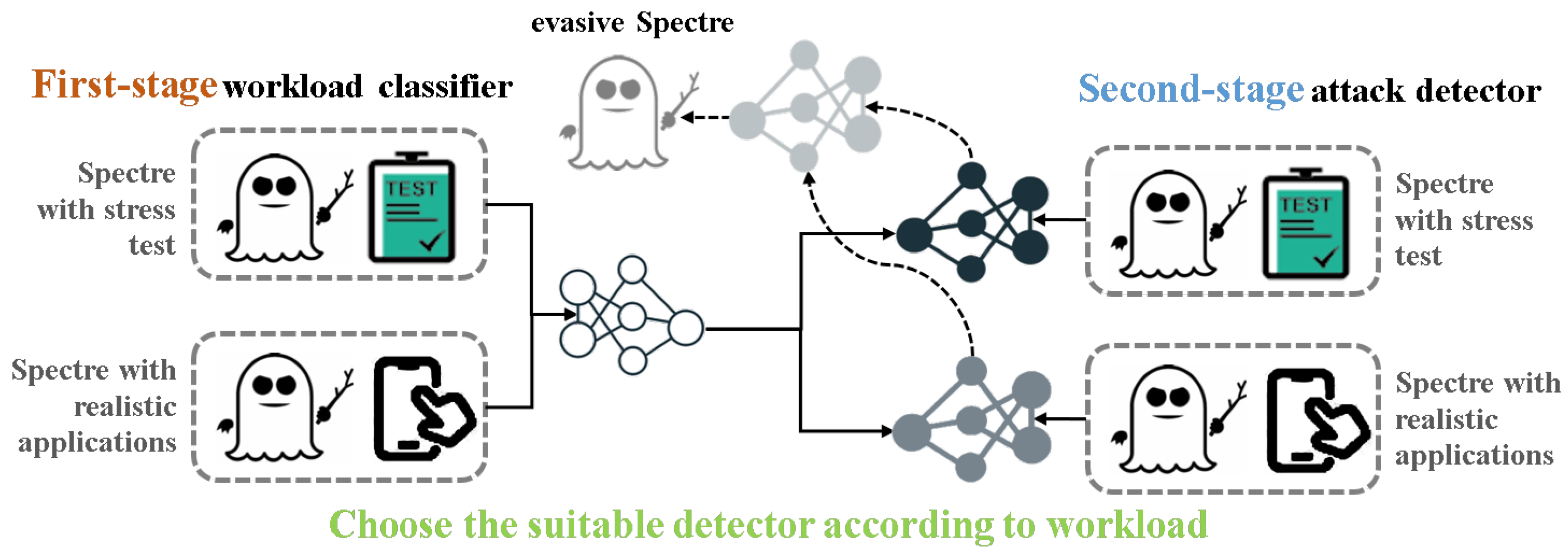

- To identify different workloads for more accurate attack detection, a unified two-stage smart detector is well designed. The first-stage is used to distinguish various workloads, while the second-stage focuses on attack detection. This ablation study show that the proposed approach only results in only 0.12% accuracy loss on average compared with solely separate detectors.

2. Background

2.1. Speculative Execution and Cache Side Channels for Microarchitecture Attack

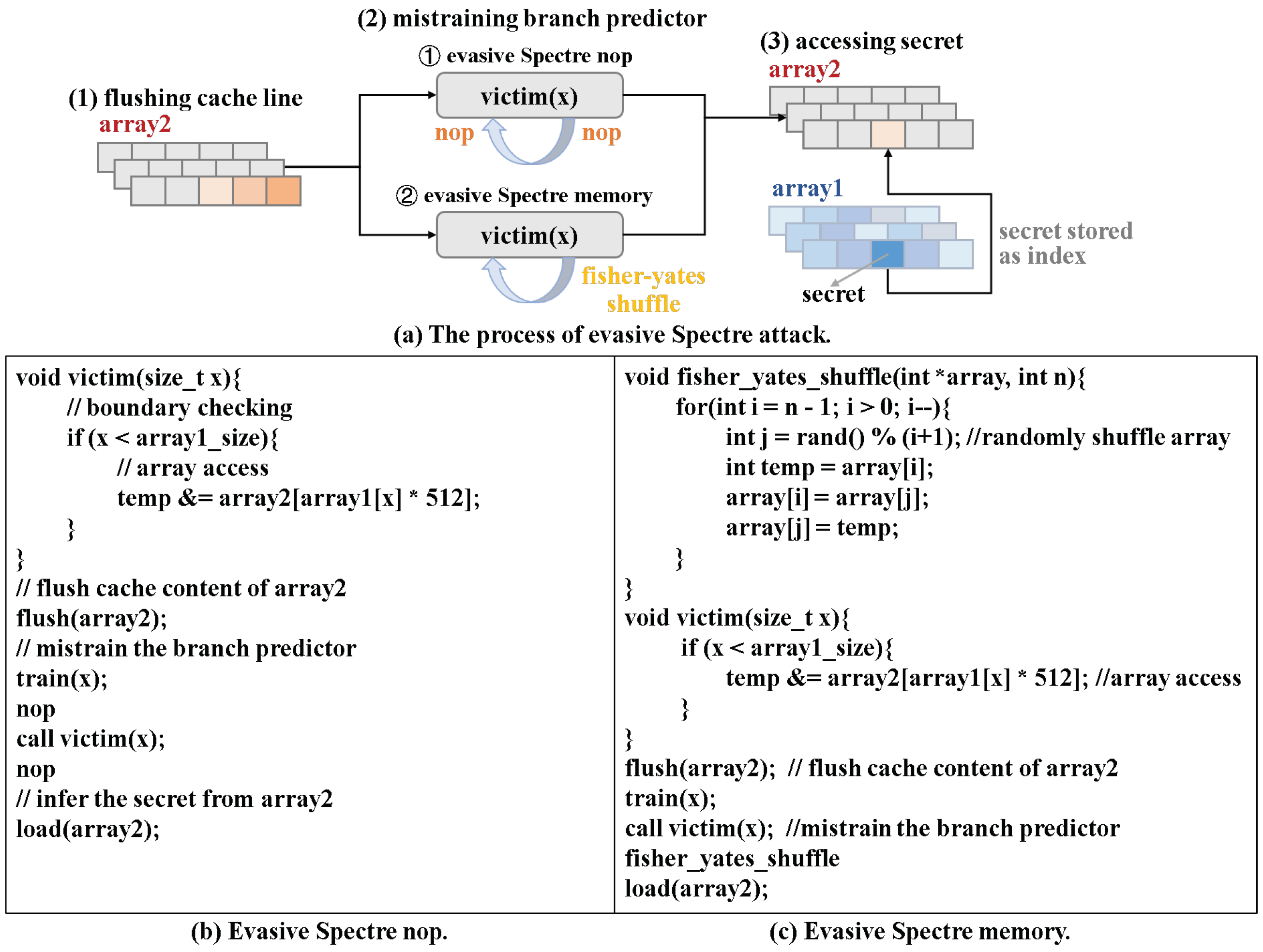

2.2. Evasive Spectre Attack

2.3. Hardware Performance Counter

2.4. Multi-Layer Perceptron

3. Proposed Detector T-Smade

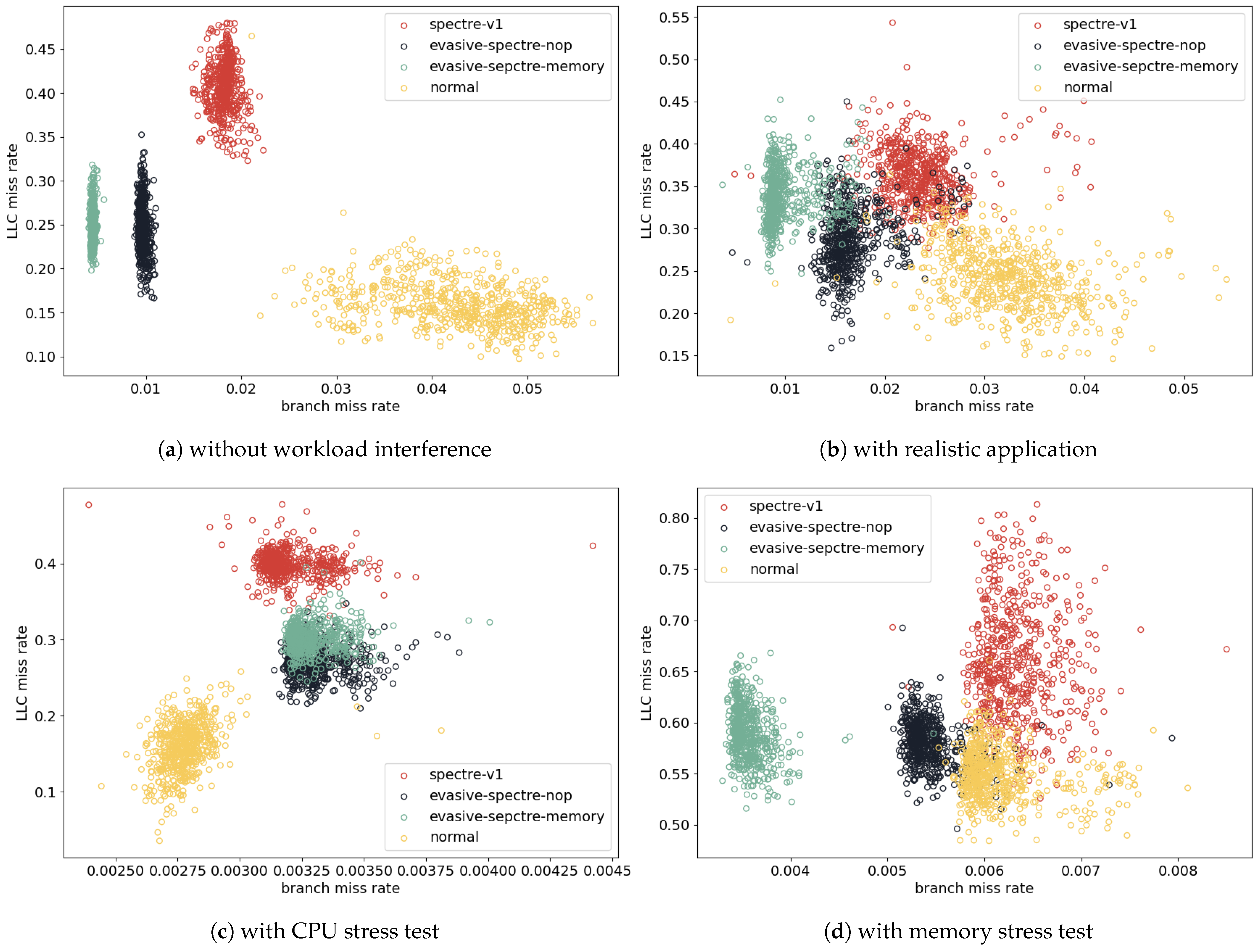

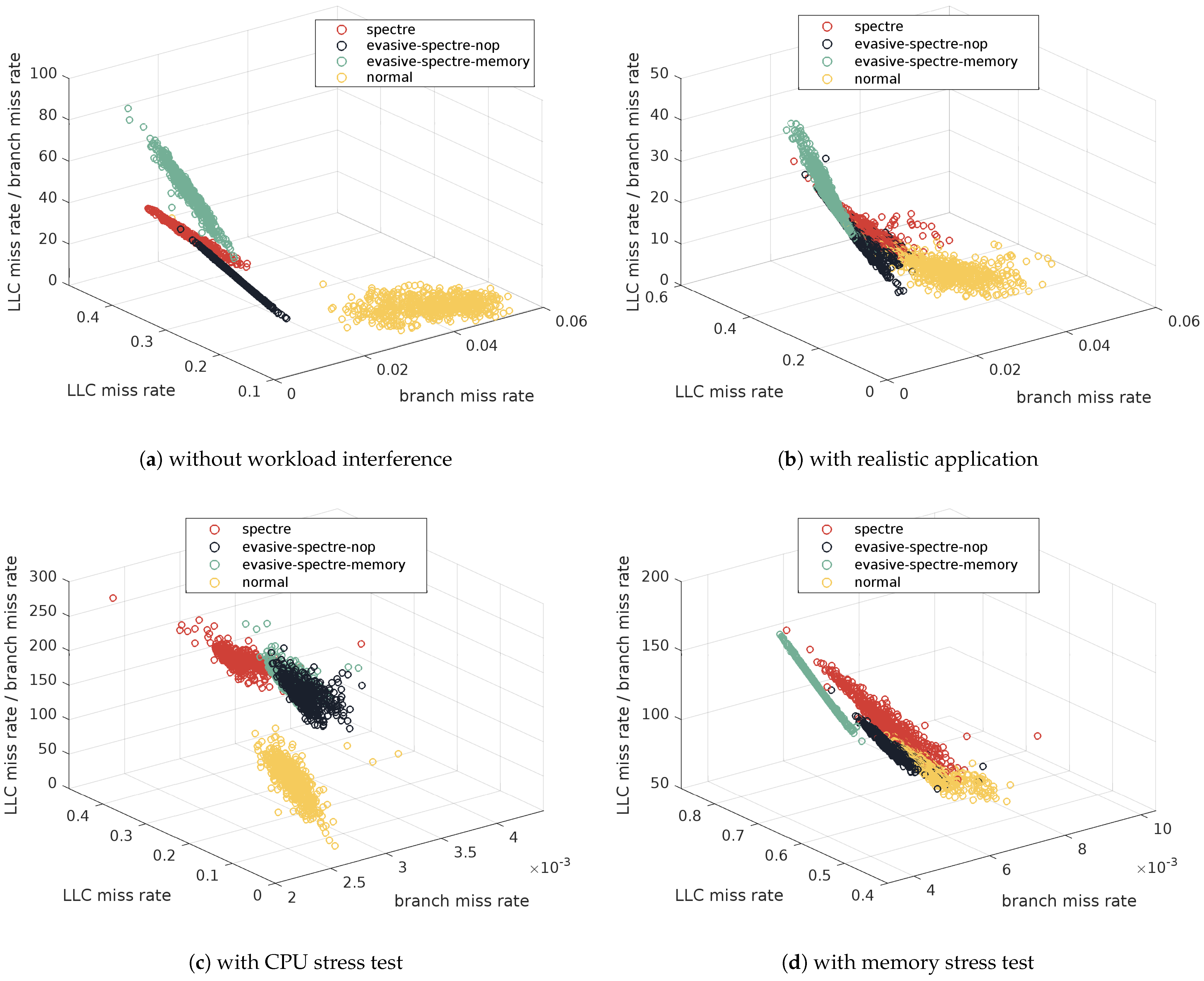

3.1. Motivation

3.2. Overall Framework

| Algorithm 1 Workloads classifier model training process |

| First Stage Classifier Training: |

| Input 1: An array X = [,,,,,] has 6 features of attack (Spectre attack) and non-attack data. (: branches, : branch misses, : LLC reference, : LLC misses, : branch miss rate, and : LLC miss rate) |

| Output 1: A best workloads classifier C |

| 1: Training data: X (combining three different workload categories). |

| 2: Supervised learning label Y: realistic application , CPU stress test , memory stress test . |

| 3: Predicted label: . |

| // start training the workloads classifier |

| 4: for (i = 1 to epoch) do |

| 5: ← MLP ← ; |

| 6: ← ← ; |

| 7: Accuracy, loss ← Y, ; |

| 8: end for; |

| 9: Return C; |

| Algorithm 2 Attack detector model training process |

| Second Stage Detector Training (taking realistic application as an example): |

| Input 2: An array = [,,,,,,] has 7 features of attack (Spectre attack) and non-attack data. (: evasive expanding rate) |

| Output 2: Three best attack detectors. (realistic applications workload attack detector: , CPU stress test workload attack detector: , memory stress test workload attack detector: ) |

| 1: Training data: (each detector only uses one workload data). |

| 2: Supervised learning label L: attack data , non-attack data . |

| 3: Predicted label: . |

| // start training the attack detector |

| 4: for (i = 1 to epoch) do |

| 5: ← MLP ← ; |

| 6: L* ← ← ; |

| 7: Accuracy, loss ← L, ; |

| 8: end for |

| 9: Return ; |

3.3. The Two-Stage Detector Details

- Branch instructions retired event (branches)

- Branch misprediction retired event (branch misses)

- Last-level cache reference event (LLC references)

- Last-level cache missed event (LLC misses)

| Algorithm 3 Two-stage detection process |

| Input: An array T = [(),(),(),()] has 4 features of attack (two evasive Spectre attacks) and non-attack data. ((): branches, (): branch misses, (): LLC reference, (): LLC misses, (): branch miss rate, ( and): LLC miss rate and (): evasive expanding rate) |

| Output: |

| 1: The preprocess data of T: () = [(),(),(),(),(),()]; () = [(),(),(),(),(),(),()]. |

| 2: The workloads predicted label () of T: realistic applications (), CPU stress test (), and memory stress test (). |

| 3: The attack predicted label () of (): attack data () and non-attack data (). |

| // First stage workloads classification |

| 4: () ← C ← () ← T; // C: pretrained workloads classifier |

| 5: if i is in (1, 2, 3) then // |

| 6: if (Y* == ()) then |

| // Second stage attack detection |

| 7: () ← () ← () ← T; // D: pretrained attack detector |

| 8: if (() == ()) then |

| 9: return attack; |

| 10: else |

| 11: return non-attack; |

| 12: end if |

| 13: end if |

| 14: end if |

4. Results and Analysis

4.1. Experiment Configuration

4.2. Detection Performance Results and Analysis Under Different Evasive Spectre Attacks

4.3. Detection Performance Results and Analysis Under Different Workloads

4.4. Detection Performance Results and Analysis Under Varying Realistic Applications

4.5. Good Generalization Verification

4.6. Comparison with State-of-the-Art Researches

4.7. Discussion and Limitation

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Gabbay, F.; Mendelson, A. Speculative Execution Based on Value Prediction; CiteseerX: Princeton, NJ, USA, 1996. [Google Scholar]

- Ravichandran, J.; Na, W.T.; Lang, J.; Yan, M. PACMAN: Attacking ARM pointer authentication with speculative execution. In Proceedings of the 49th Annual International Symposium on Computer Architecture (ISCA 22), New York, NY, USA, 18–22 June 2022; pp. 685–698. [Google Scholar] [CrossRef]

- Hu, G.; Lee, R.B. Protecting Cache States Against Both Speculative Execution Attacks and Side-channel Attacks. arXiv 2023, arXiv:2302.00732. [Google Scholar]

- Tomasulo, R.M. An Efficient Algorithm for Exploiting Multiple Arithmetic Units. IBM J. Res. Dev. 1967, 11, 25–33. [Google Scholar] [CrossRef]

- Hubballi, S.; Siddamal, S.V. Out-of-Order Execution of Instructions for In-Order Five-Stage RISC-V Processor. In Proceedings of the Advances in Microelectronics, Embedded Systems and IoT, Mizoram, India, 6–7 October 2023; Chakravarthy, V.V.S.S.S., Bhateja, V., Anguera, J., Urooj, S., Ghosh, A., Eds.; Springer: Singapore, 2024; pp. 29–35. [Google Scholar]

- Kocher, P.; Horn, J.; Fogh, A.; Genkin, D.; Gruss, D.; Haas, W.; Hamburg, M.; Lipp, M.; Mangard, S.; Prescher, T.; et al. Spectre attacks: Exploiting speculative execution. Commun. ACM 2020, 63, 93–101. [Google Scholar] [CrossRef]

- Li, C.; Gaudiot, J.L. Detecting Spectre Attacks Using Hardware Performance Counters. IEEE Trans. Comput. 2022, 71, 1320–1331. [Google Scholar] [CrossRef]

- Ajorpaz, S.M.; Moghimi, D.; Collins, J.N.; Pokam, G.; Abu-Ghazaleh, N.; Tullsen, D. EVAX: Towards a Practical, Pro-active & Adaptive Architecture for High Performance & Security. In Proceedings of the 2022 55th IEEE/ACM International Symposium on Microarchitecture (MICRO), Chicago, IL, USA, 1–5 October 2022; pp. 1218–1236. [Google Scholar] [CrossRef]

- AL-Zu’bi, M.; Weissenbacher, G. Statistical Profiling of Micro-Architectural Traces and Machine Learning for Spectre Detection: A Systematic Evaluation. In Proceedings of the 2024 Design, Automation & Test in Europe Conference & Exhibition (DATE), Valencia, Spain, 25–27 March 2024; pp. 1–6. [Google Scholar]

- Pan, Z.; Sheldon, J.; Sudusinghe, C.; Charles, S.; Mishra, P. Hardware-Assisted Malware Detection using Machine Learning. In Proceedings of the 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), Virtual, 1–5 February 2021; pp. 1775–1780. [Google Scholar] [CrossRef]

- Carnà, S.; Ferracci, S.; Quaglia, F.; Pellegrini, A. Fight Hardware with Hardware: Systemwide Detection and Mitigation of Side-channel Attacks Using Performance Counters. Digit. Threat. 2023, 4, 1–24. [Google Scholar] [CrossRef]

- Kuruvila, A.P.; Meng, X.; Kundu, S.; Pandey, G.; Basu, K. Explainable Machine Learning for Intrusion Detection via Hardware Performance Counters. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2022, 41, 4952–4964. [Google Scholar] [CrossRef]

- Botacin, M.; Grégio, A. Why We Need a Theory of Maliciousness: Hardware Performance Counters in Security. In Proceedings of the Information Security, Bali, Indonesia, 18–22 December 2022; Susilo, W., Chen, X., Guo, F., Zhang, Y., Intan, R., Eds.; Springer: Cham, Switzerland, 2022; pp. 381–389. [Google Scholar]

- Kapotoglu Koc, M.; Altilar, D.T. Selection of Best Fit Hardware Performance Counters to Detect Cache Side-Channel Attacks. In Proceedings of the 2023 ACM Workshop on Secure and Trustworthy Cyber-Physical Systems, Charlotte, NC, USA, 26 April 2023; SaT-CPS 23. Association for Computing Machinery: New York, NY, USA, 2023; pp. 17–22. [Google Scholar] [CrossRef]

- Hu, Y.; Liang, S.; Li, M.; Xue, T.; Zhang, B.; Wen, Y. CARE: Enabling Hardware Performance Counter based Malware Detection Resilient to System Resource Competition. In Proceedings of the 2022 IEEE 24th International Conference on High Performance Computing & Communications; 8th International Conference on Data Science & Systems; 20th International Conference on Smart City; 8th International Conference on Dependability in Sensor, Cloud & Big Data Systems & Application (HPCC/DSS/SmartCity/DependSys), Hainan, China, 18–20 December 2022; pp. 586–594. [Google Scholar] [CrossRef]

- Pashrashid, A.; Hajiabadi, A.; Carlson, T.E. Fast, Robust and Accurate Detection of Cache-Based Spectre Attack Phases. In Proceedings of the 41st IEEE/ACM International Conference on Computer-Aided Design (ICCAD 22), San Diego, CA, USA, 30 October–3 November 2022; Association for Computing Machinery: New York, NY, USA, 2022. [Google Scholar] [CrossRef]

- Pashrashid, A.; Hajiabadi, A.; Carlson, T.E. HidFix: Efficient Mitigation of Cache-Based Spectre Attacks Through Hidden Rollbacks. In Proceedings of the 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD), San Francisco, CA, USA, 28 October–2 November 2023; pp. 1–9. [Google Scholar] [CrossRef]

- Pashrashid, A.; Hajiabadi, A.; Carlson, T.E. Efficient Detection and Mitigation Schemes for Speculative Side Channels. In Proceedings of the 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, 19–22 May 2024; pp. 1–5. [Google Scholar] [CrossRef]

- Li, C.; Gaudiot, J.L. Challenges in Detecting an “Evasive Spectre”. IEEE Comput. Archit. Lett. 2020, 19, 18–21. [Google Scholar] [CrossRef]

- Polychronou, N.F.; Thevenon, P.H.; Puys, M.; Beroulle, V. MaDMAN: Detection of Software Attacks Targeting Hardware Vulnerabilities. In Proceedings of the 2021 24th Euromicro Conference on Digital System Design (DSD), Palermo, Spain, 1–3 September 2021; pp. 355–362. [Google Scholar] [CrossRef]

- Pan, Z.; Mishra, P. Automated Detection of Spectre and Meltdown Attacks Using Explainable Machine Learning. In Proceedings of the 2021 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Tysons Corner, VA, USA, 12–15 December 2021; pp. 24–34. [Google Scholar] [CrossRef]

- Kosasih, W.; Feng, Y.; Chuengsatiansup, C.; Yarom, Y.; Zhu, Z. SoK: Can We Really Detect Cache Side-Channel Attacks by Monitoring Performance Counters? In Proceedings of the 19th ACM Asia Conference on Computer and Communications Security (ASIA CCS 24), Singapore, 1–5 July 2024; ACM: New York, NY, USA, 2024; pp. 172–185. [Google Scholar] [CrossRef]

- He, Z.; Hu, G.; Lee, R.B. CloudShield: Real-time Anomaly Detection in the Cloud. In Proceedings of the Thirteenth ACM Conference on Data and Application Security and Privacy (CODASPY 23), Charlotte, NC, USA, 24–26 April 2023; ACM: New York, NY, USA, 2023; pp. 91–102. [Google Scholar] [CrossRef]

- Guide, P. Volume 3B: System Programming Guide Part. Intel® 64 and ia-32 Architectures Software Developer’s Manual. 2011, pp. 1–40. Available online: https://www.intel.com/content/www/us/en/developer/articles/technical/intel-sdm.html (accessed on 26 September 2024).

- Advanced Micro Devices. AMD64 Architecture Programmer’s Manual Volume 2: System Programming; Advanced Micro Devices: Santa Clara, CA, USA, 2006. [Google Scholar]

- van Schaik, S.; Minkin, M.; Kwong, A.; Genkin, D.; Yarom, Y. CacheOut: Leaking Data on Intel CPUs via Cache Evictions. In Proceedings of the 2021 IEEE Symposium on Security and Privacy (SP), San Francisco, CA, USA, 24–27 May 2021; pp. 339–354. [Google Scholar] [CrossRef]

- Wang, H.; Tang, M.; Xu, K.; Wang, Q. Cache Bandwidth Contention Leaks Secrets. In Proceedings of the 2024 Design, Automation & Test in Europe Conference & Exhibition (DATE), Valencia, Spain, 25–27 March 2024; pp. 1–6. [Google Scholar]

- Guo, Y.; Zigerelli, A.; Zhang, Y.; Yang, J. Adversarial Prefetch: New Cross-Core Cache Side Channel Attacks. In Proceedings of the 2022 IEEE Symposium on Security and Privacy (SP), San Francisco, CA, USA, 23–25 May 2022; pp. 1458–1473. [Google Scholar] [CrossRef]

- Durstenfeld, R. Algorithm 235: Random permutation. Commun. ACM 1964, 7, 420. [Google Scholar] [CrossRef]

- Putrevu, M.A.; Putrevu, V.S.C.; Shukla, S.K. Early Detection of Ransomware Activity based on Hardware Performance Counters. In Proceedings of the 2023 Australasian Computer Science Week (ACSW 23), Melbourne, VIC, Australia, 30 January–3 February 2023; ACM: New York, NY, USA, 2023; pp. 10–17. [Google Scholar] [CrossRef]

- Qiu, P.; Gao, Q.; Liu, C.; Wang, D.; Lyu, Y.; Li, X.; Wang, C.; Qu, G. PMU-Spill: A New Side Channel for Transient Execution Attacks. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 5048–5059. [Google Scholar] [CrossRef]

- Rosenblatt, F. The perceptron: A probabilistic model for information storage and organization in the brain. Psychol. Rev. 1958, 65, 386–408. [Google Scholar] [CrossRef]

- Cauligi, S.; Disselkoen, C.; Moghimi, D.; Barthe, G.; Stefan, D. SoK: Practical Foundations for Software Spectre Defenses. In Proceedings of the 2022 IEEE Symposium on Security and Privacy (SP), San Francisco, CA, USA, 23–25 May 2022; pp. 666–680. [Google Scholar] [CrossRef]

- Hetterich, L.; Bauer, M.; Schwarz, M.; Rossow, C. Switchpoline: A Software Mitigation for Spectre-BTB and Spectre-BHB on ARMv8. In Proceedings of the 19th ACM Asia Conference on Computer and Communications Security (ASIA CCS 24), Singapore, 1–5 July 2024; ACM: New York, NY, USA, 2024; pp. 217–230. [Google Scholar] [CrossRef]

- Ponce-de Leon, H.; Kinder, J. Cats vs. Spectre: An Axiomatic Approach to Modeling Speculative Execution Attacks. In Proceedings of the 2022 IEEE Symposium on Security and Privacy (SP), San Francisco, CA, USA, 23–25 May 2022; pp. 235–248. [Google Scholar] [CrossRef]

- Yao, Y.; Duan, J.; Xu, K.; Cai, Y.; Sun, Z.; Zhang, Y. A survey on large language model (LLM) security and privacy: The Good, The Bad, and The Ugly. High-Confid. Comput. 2024, 4, 100211. [Google Scholar] [CrossRef]

- Zou, A.; Wang, Z.; Carlini, N.; Nasr, M.; Kolter, J.Z.; Fredrikson, M. Universal and Transferable Adversarial Attacks on Aligned Language Models. arXiv 2023, arXiv:2307.15043. [Google Scholar]

- Islam, M.S.; Kuruvila, A.P.; Basu, K.; Khasawneh, K.N. ND-HMDs: Non-Differentiable Hardware Malware Detectors against Evasive Transient Execution Attacks. In Proceedings of the 2020 IEEE 38th International Conference on Computer Design (ICCD), Hartford, CT, USA, 18–21 October 2020; pp. 537–544. [Google Scholar] [CrossRef]

- Schwarzl, M.; Borrello, P.; Kogler, A.; Varda, K.; Schuster, T.; Schwarz, M.; Gruss, D. Robust and Scalable Process Isolation Against Spectre in the Cloud. In Proceedings of the Computer Security—ESORICS 2022, Copenhagen, Denmark, 26–30 September 2022; Atluri, V., Di Pietro, R., Jensen, C.D., Meng, W., Eds.; Springer: Cham, Switzerland, 2022; pp. 167–186. [Google Scholar]

| Item | Configuration |

|---|---|

| operation system | Linux 5.4.0-146-generic |

| mirror | Ubuntu 18.04.6 LTS |

| memory | 125.5GiB |

| processor | Intel Xeon® Silver 4210 CPU @ 2.2GHz × 20 |

| graphics | llvmpipe (LLVM 10.0.0, 256 bits) |

| GNOME | 3.28.2 |

| OS type | 64 bit |

| disk | 502.9 GB |

| software | Pycharm professional 2022.1.3 |

| Python | Python3.6 |

| Perf (HPCs) | Perf version 5.4.233 |

| Stress-ng | Stress 1.0.4 |

| Datasets | Attacks | Features | The Number of Samples | |

|---|---|---|---|---|

| First stage | train | Spectre | branches | 3600 |

| branch misses | ||||

| LLC reference | ||||

| test | two evasive Spectre | LLC misses | 3600 | |

| branch miss rate | ||||

| LLC miss rate | ||||

| Second stage | train | Spectre | branches | 3 detectors and 1200 for each |

| branch misses | ||||

| LLC reference | ||||

| LLC misses | ||||

| test | two evasive Spectre | branch miss rate | 3 detectors and 1200 for each | |

| LLC miss rate | ||||

| evasive expanding rate |

| Workloads | Description | |

|---|---|---|

| Realistic applications | A1 | Get locally downloaded music and play different music in a loop with Pygame. |

| A2 | Search and watch different types of videos on your Firefox browser. | |

| A3 | Call the WPS (similar to Office, version 11.1.0), and constantly edit and save the document. | |

| A4 | Call the MySQL database (ver 14.14 Distrib 5.7.41) and perform four operations. | |

| A5 | Play snake game with Pygame. | |

| A6 | Call the libreoffice (similar to Office, version 5.4.6), and constantly edit and save the document. | |

| Stress | −c | Run multiple computation-intensive tasks, such as integer operations and floating-point operations, to increase the CPU workload. |

| −m | Repeatedly allocate and deallocate a large amount of memory, increasing memory usage. | |

| 4 Apps (A1–A4) | 5 Apps (A1–A5) | 5 Apps (A1–A2, A4–A6) | ||||

|---|---|---|---|---|---|---|

| TP | TN | TP | TN | TP | TN | |

| evasive Spectre nop | 97.32% | 75.04% | 96.98% | 88.44% | 90.95% | 63.48% |

| evasive Spectre memory | 100% | 75.04% | 100% | 88.44% | 96.48% | 63.48% |

| Model | Training Accuracy | |

|---|---|---|

| First-stage classifier | 99.95% | |

| Second-stage detector | Realistic applications | 95.40% |

| CPU stress test | 100% | |

| Memory stress test | 80.54% | |

| Methods | HPC Events Number | ML | Generalization | Workload Variety | Attack Detection Successful Rate (Security) | Non-Attack Detection Successful Rate (Performance) |

|---|---|---|---|---|---|---|

| [7] (2022) | 4 | LR, SVM, MLP | No | 1 | Evasive Spectre nop: 70% | / |

| [20] (2021) | 6 | LR | No | 2 | Evasive Spectre: 100% | / |

| [21] (2021) | 6 | MLP | No | 1 | Evasive Spectre: 92.45% Evasive Meltdown: 96.8% | Evasive Spectre: 95.6% Evasive Meltdown: 97.7% |

| [22] (2024) | 4 | NN | No | 1 | Evasive Spectre: 100% | Evasive Spectre: 0% |

| Our T-Smade | 4 | MLP | Yes | 3 | Evasive Spectre nop: 95.42% Evasive Spectre memory: 100% | Evasive Spectre nop: 87.49% Evasive Spectre memory: 88.89% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiao, J.; Wen, R.; Li, Y. T-Smade: A Two-Stage Smart Detector for Evasive Spectre Attacks Under Various Workloads. Electronics 2024, 13, 4090. https://doi.org/10.3390/electronics13204090

Jiao J, Wen R, Li Y. T-Smade: A Two-Stage Smart Detector for Evasive Spectre Attacks Under Various Workloads. Electronics. 2024; 13(20):4090. https://doi.org/10.3390/electronics13204090

Chicago/Turabian StyleJiao, Jiajia, Ran Wen, and Yulian Li. 2024. "T-Smade: A Two-Stage Smart Detector for Evasive Spectre Attacks Under Various Workloads" Electronics 13, no. 20: 4090. https://doi.org/10.3390/electronics13204090

APA StyleJiao, J., Wen, R., & Li, Y. (2024). T-Smade: A Two-Stage Smart Detector for Evasive Spectre Attacks Under Various Workloads. Electronics, 13(20), 4090. https://doi.org/10.3390/electronics13204090