A Low-Cost Test Platform for Performance Analysis of Phasor Measurement Units

Abstract

1. Introduction

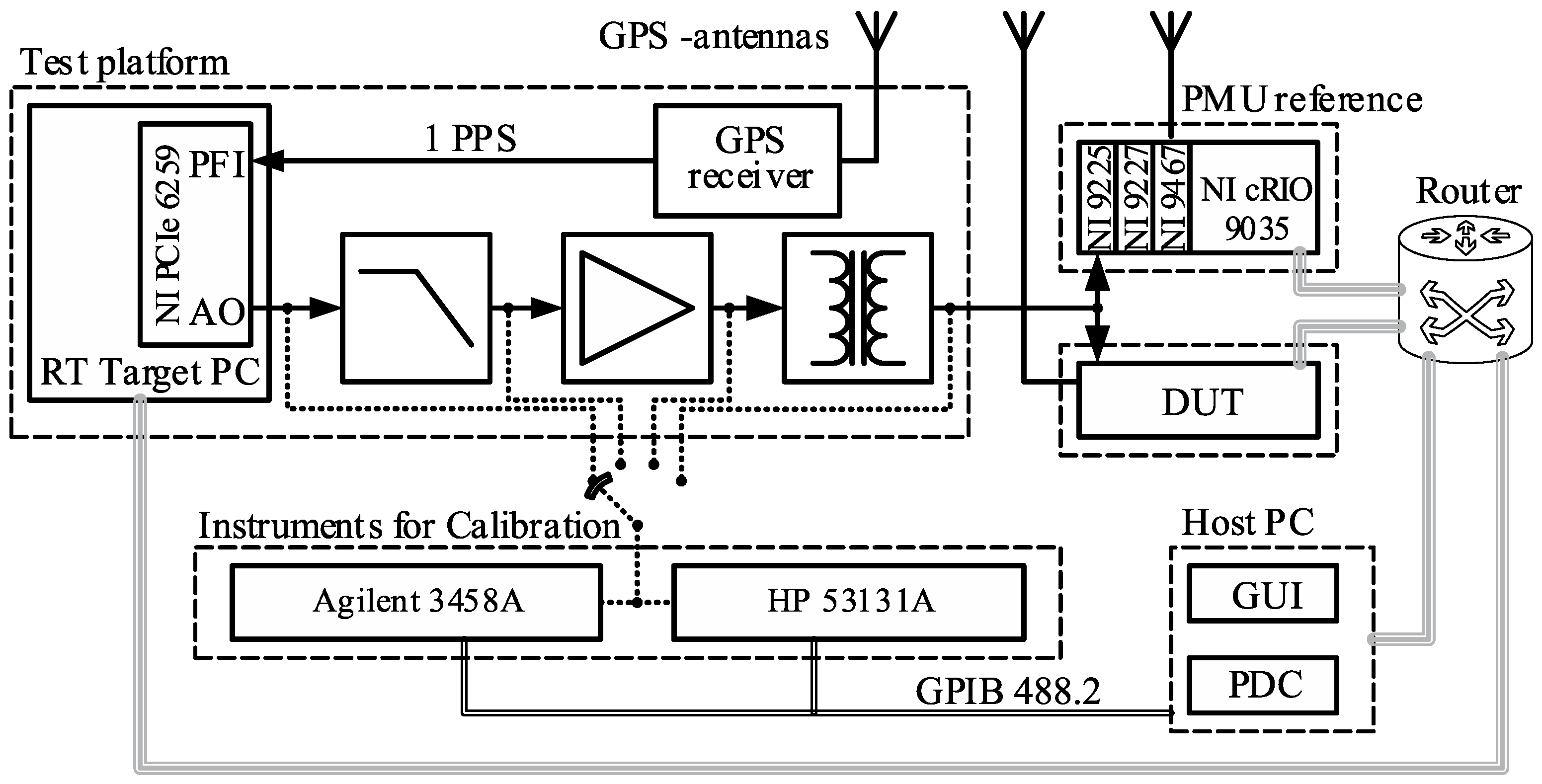

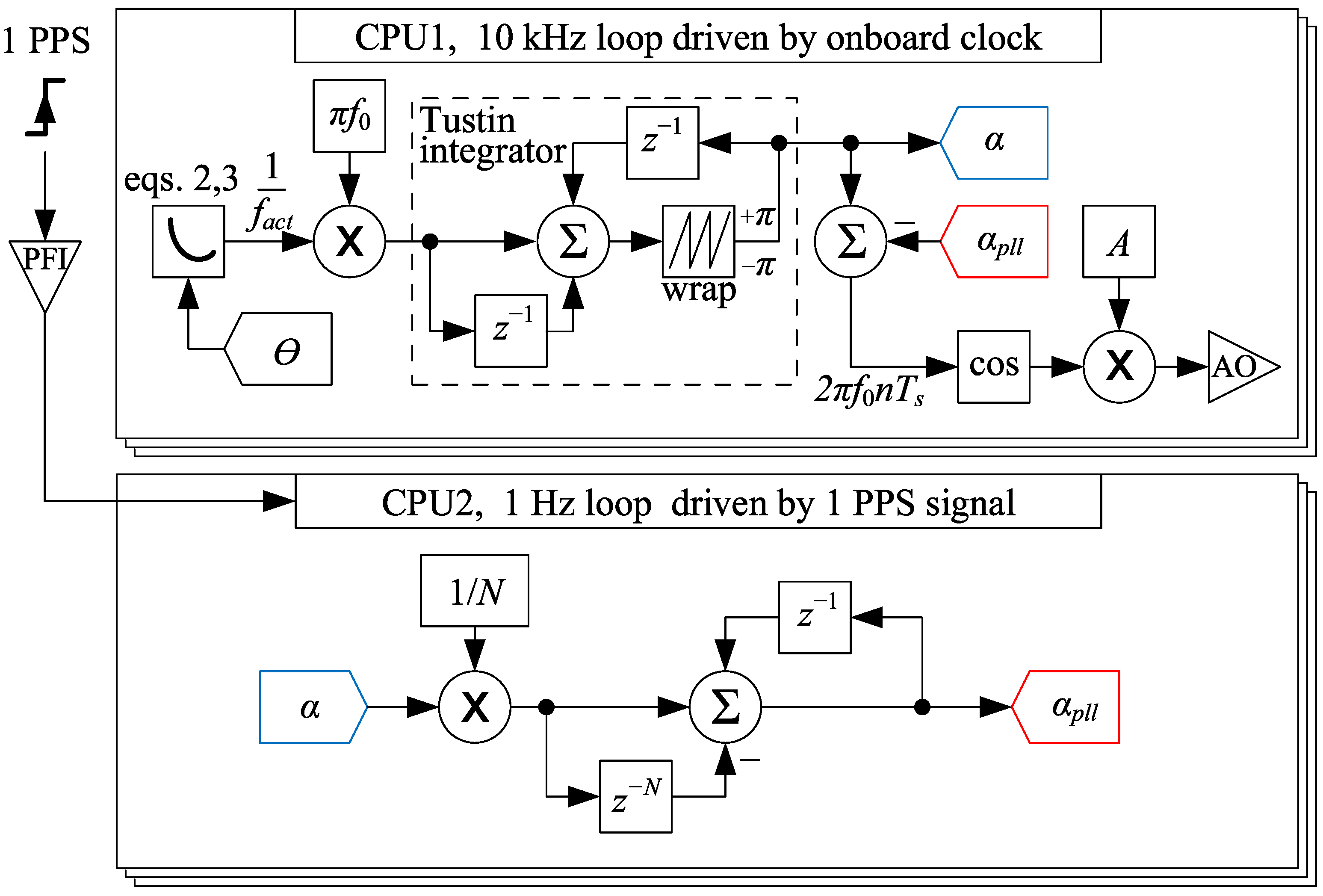

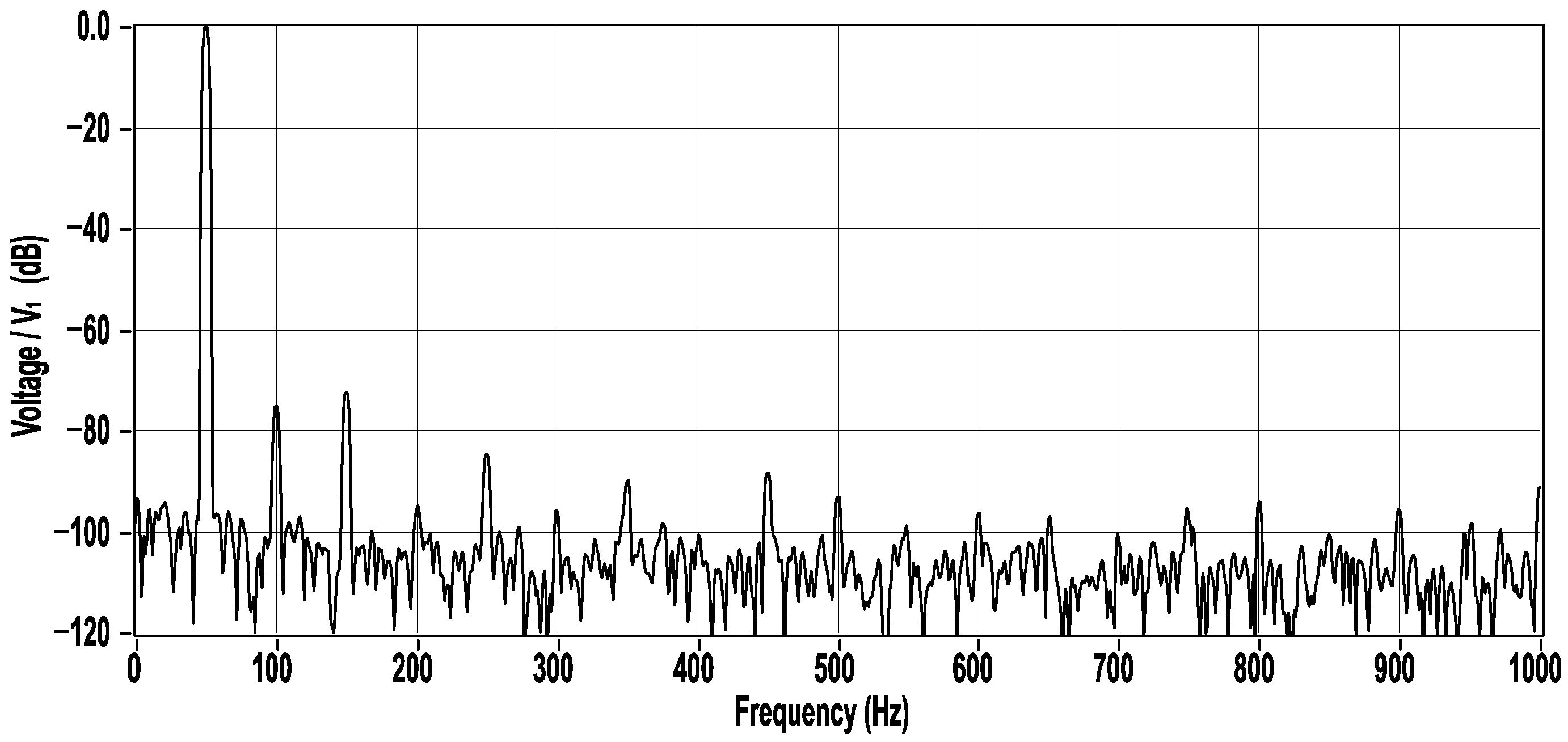

2. System Description

3. Test Platform Calibration

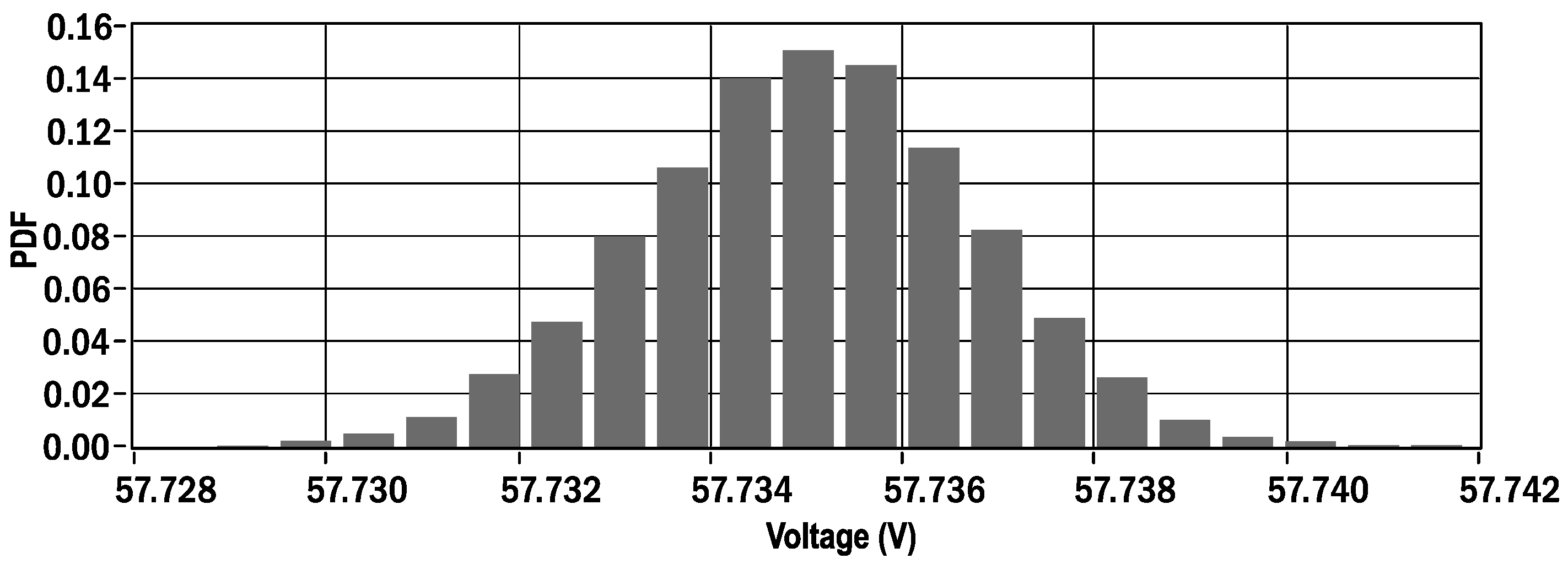

3.1. Voltage Calibration

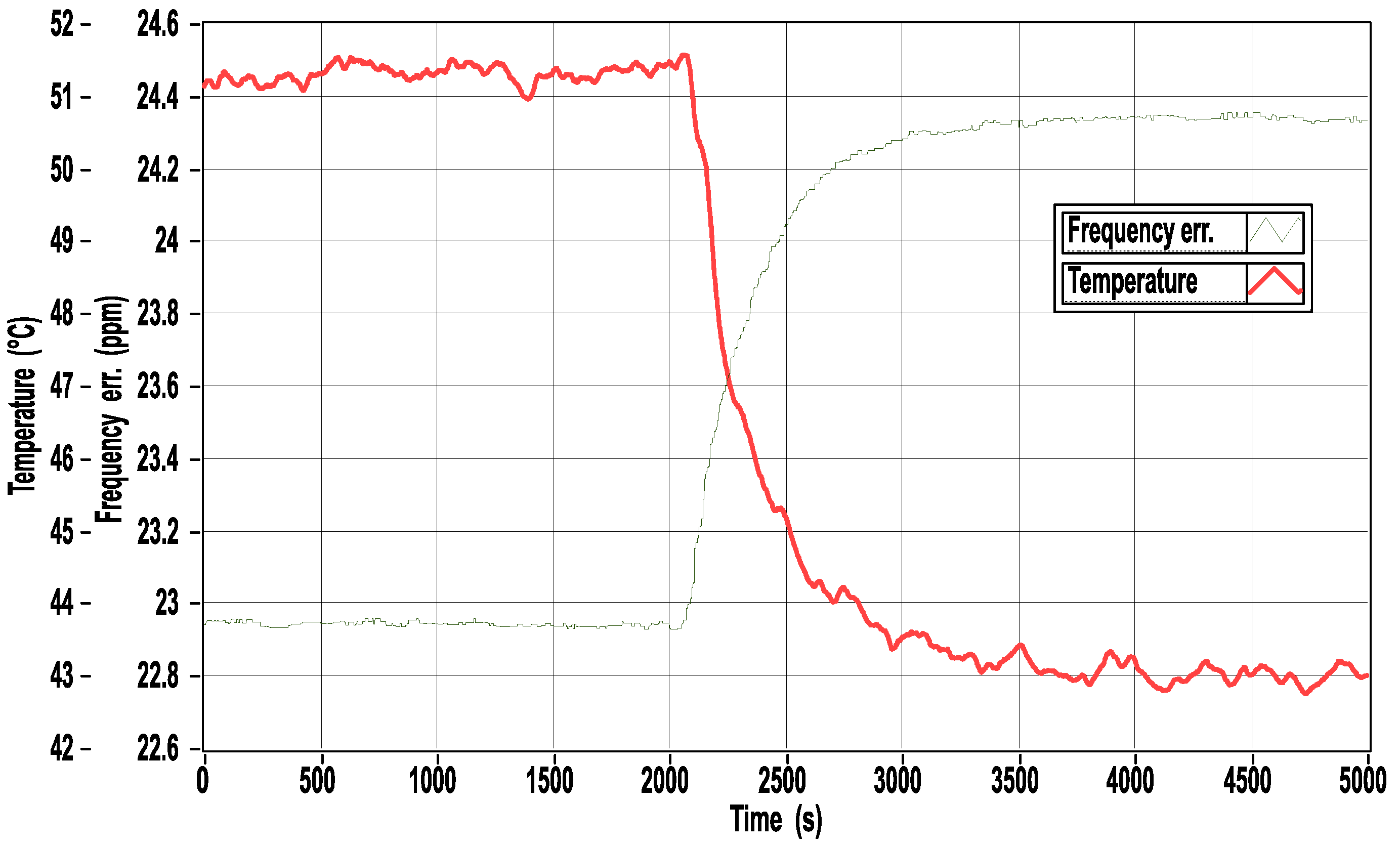

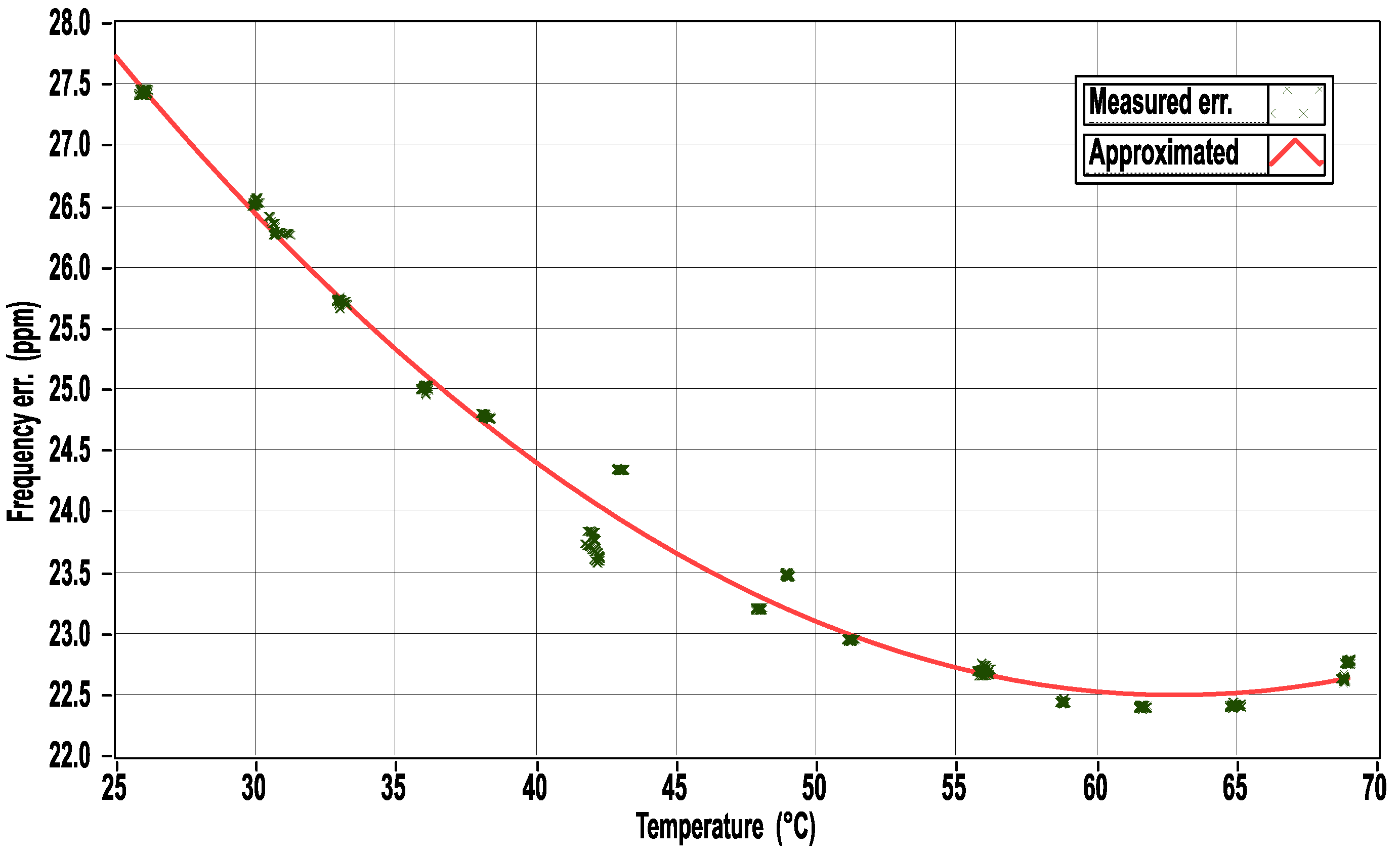

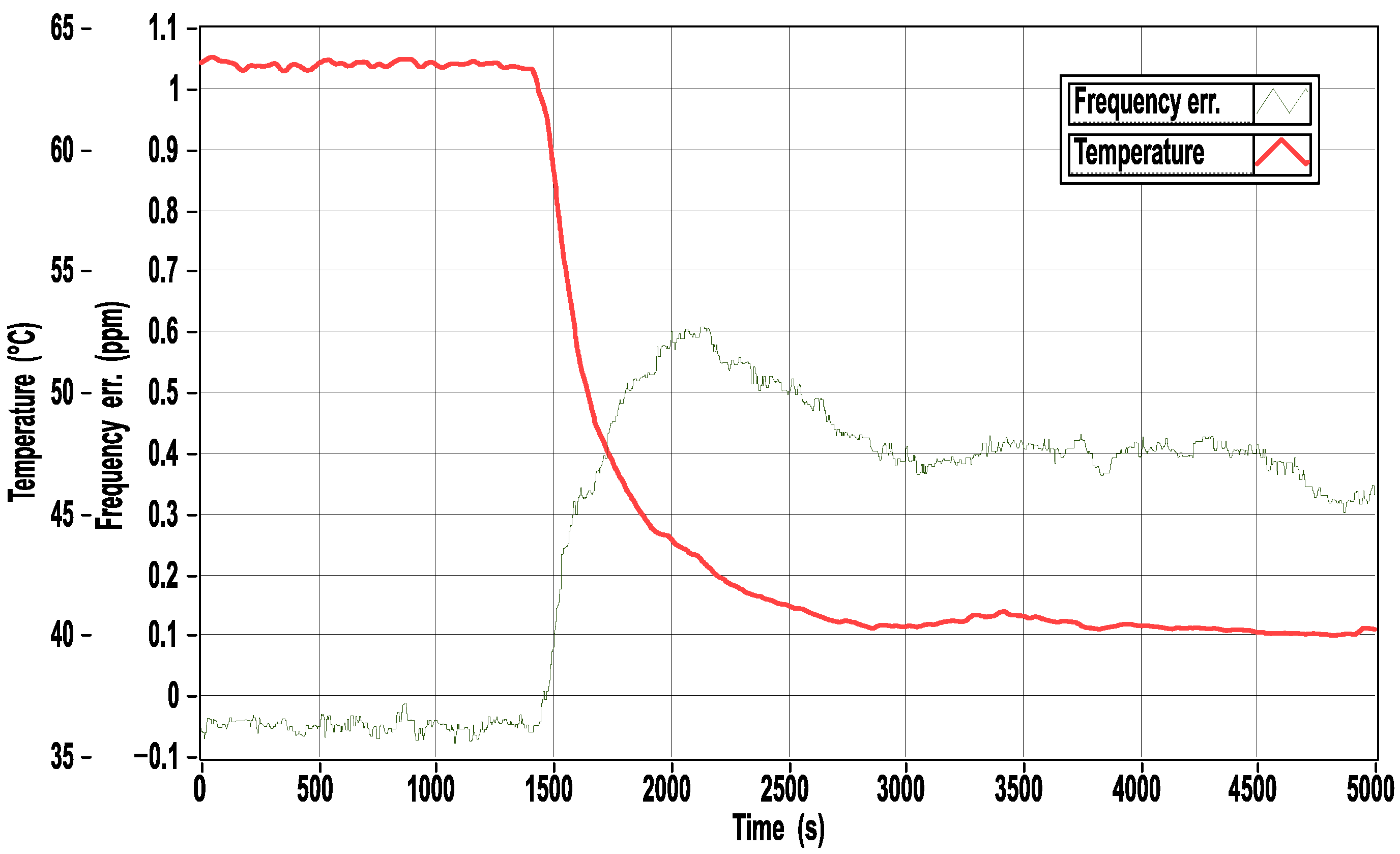

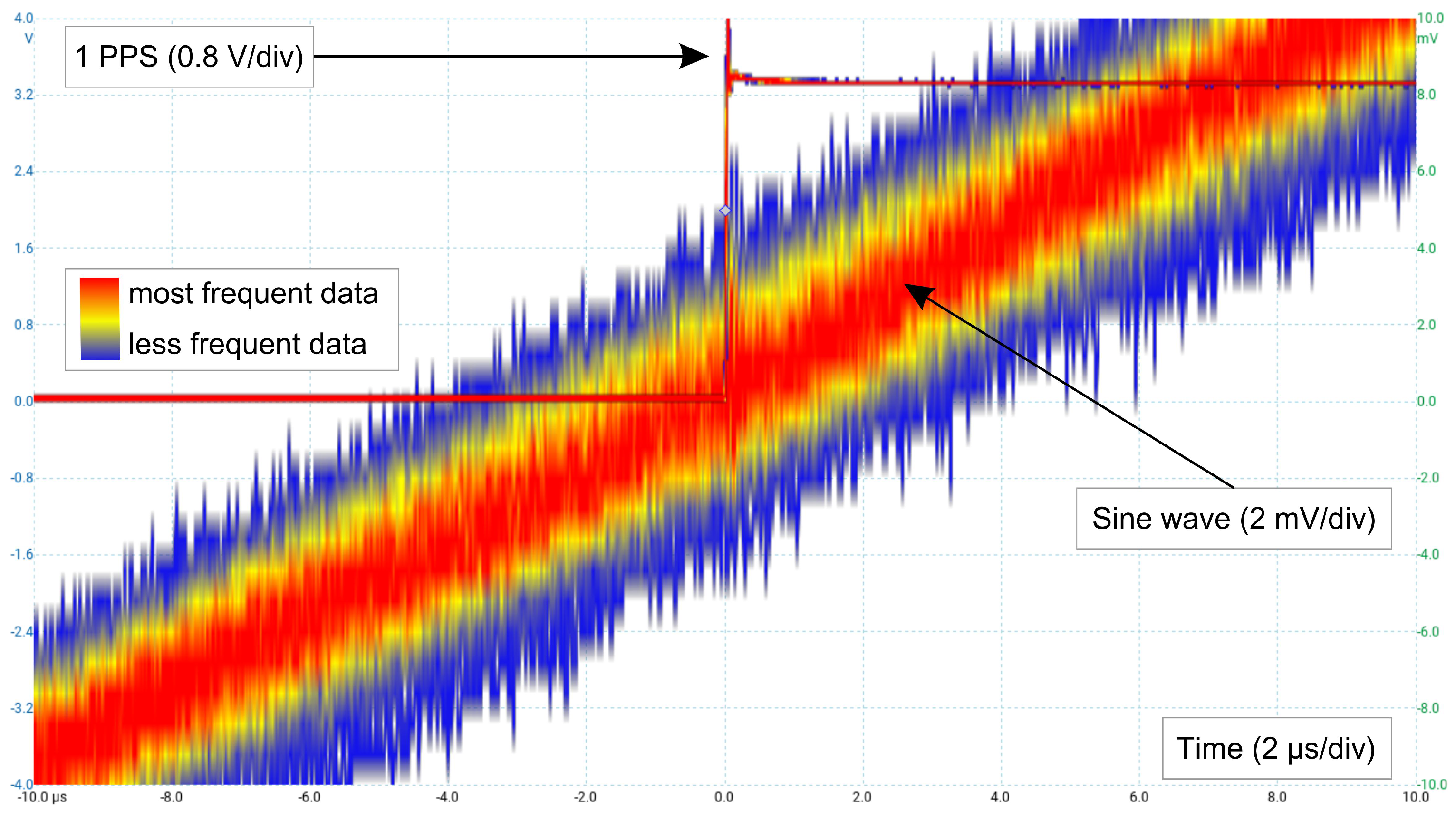

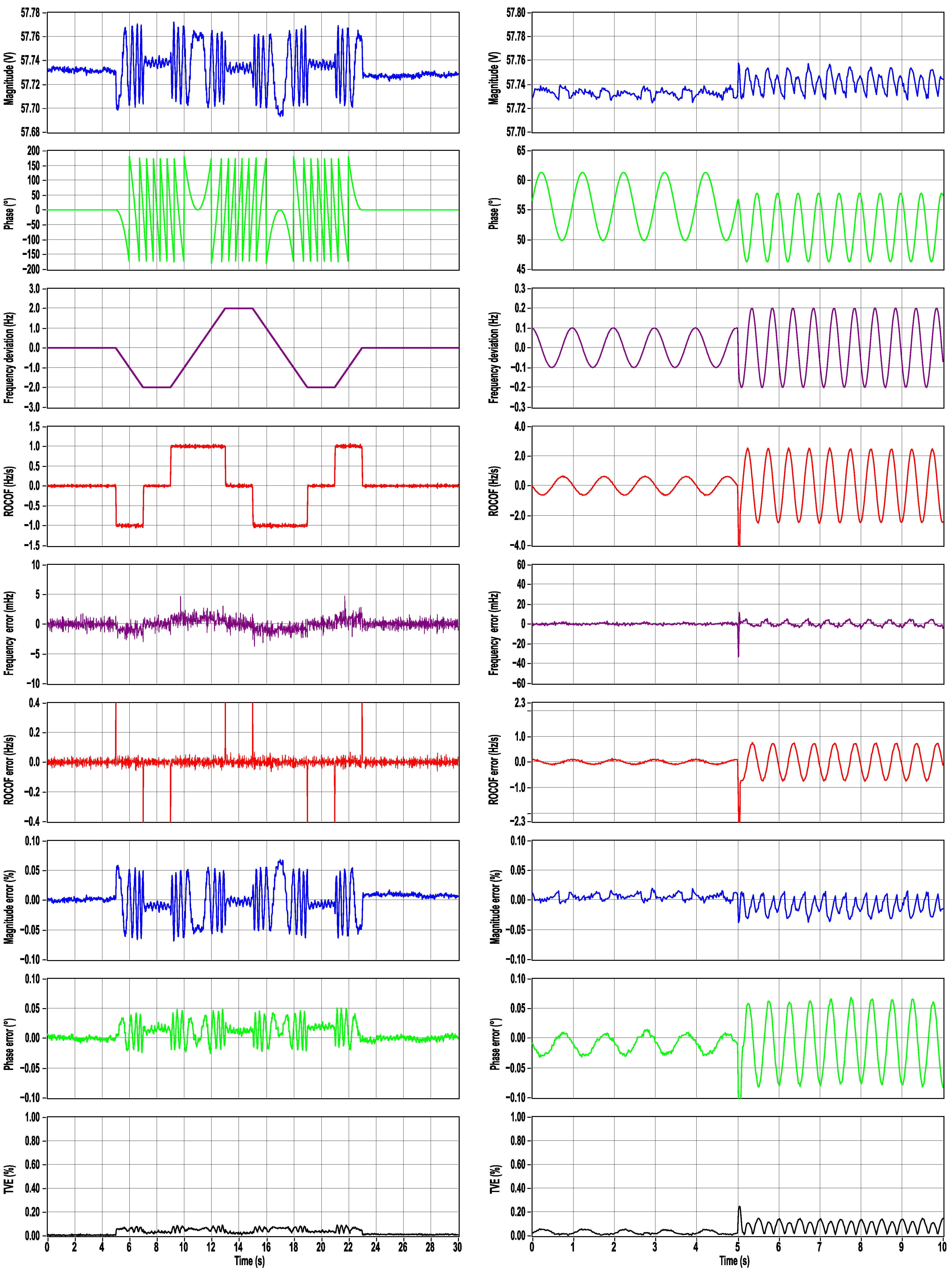

3.2. Onboard Clock Calibration

3.3. Phase (Bias) Correction

4. Phasor Data Concentrator

- (a)

- Configure and open TCP connection to PMU and RT target PC,

- (b)

- Send configuration frames to PMUs, receive corresponding header frames and send command frames to turn on data transmission,

- (c)

- Receiving data messages and parsing syncrophasor and time stamp data,

- (d)

- Harmonization of syncrophasor data according to the time stamp,

- (e)

- Calculation of error and visualization of relevant data,

- (f)

- Return to (c) until the end of test sequence is reached.

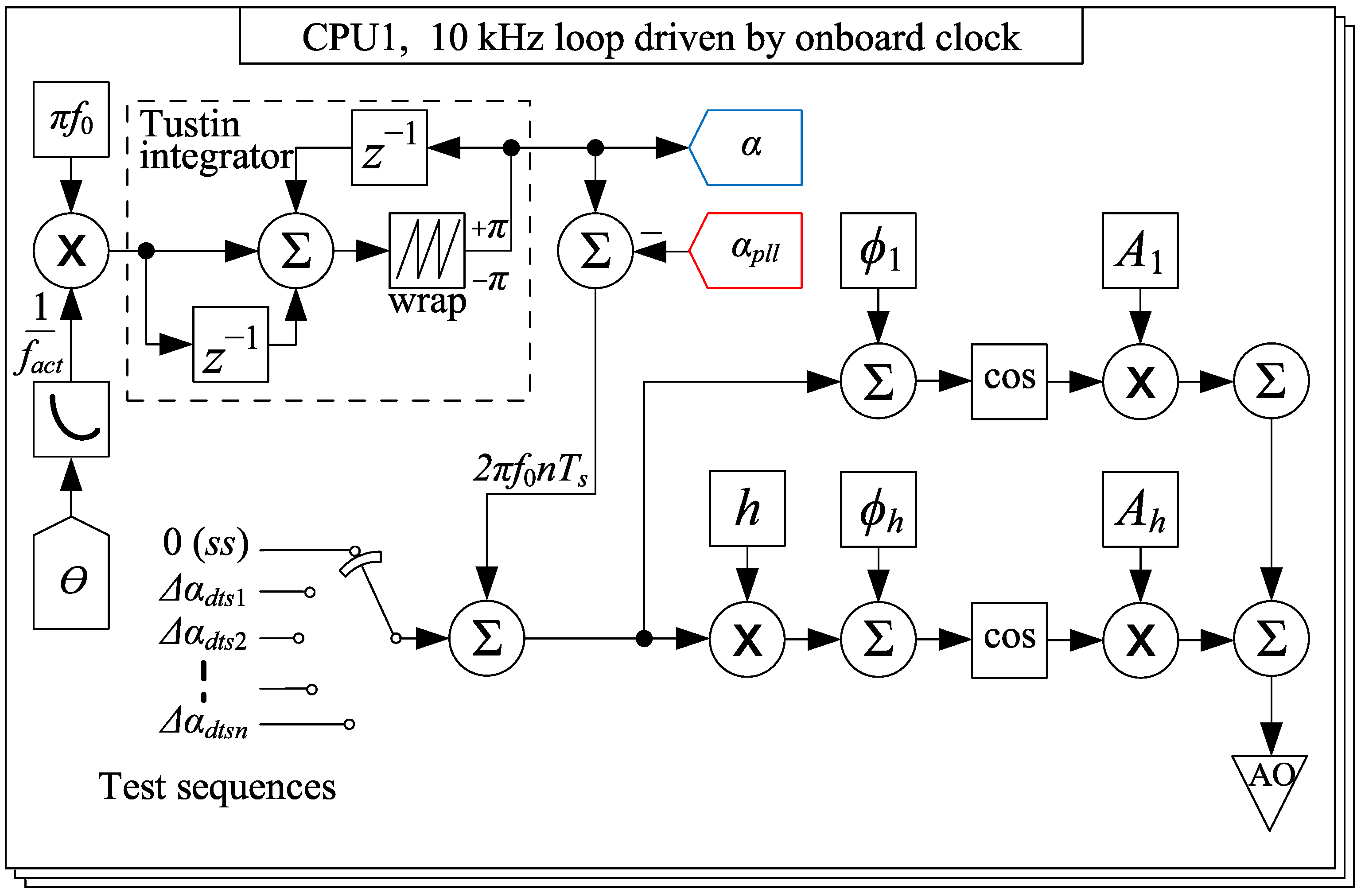

5. Algorithms for Generating Test Sequences

6. Results and Discussion

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| ADC | Analog-to-Digital Converter |

| AO | Analog Output |

| BBB | BeagleBone Black |

| DAQ | Data AcQuisition |

| DFT | Discrete Fourier Transform |

| DMM | Digital MultiMeter |

| FE | Frequency Error |

| FPGA | Field Programmable Gate Array |

| FSR | Full Scale Range |

| GPS | Global Positioning System |

| ME | Magnitude Error |

| NI | National Instruments |

| PDC | Phasor Data Concentrator |

| PE | Phase Error |

| PFI | Programmable Function Input |

| PLL | Phase-Locked Loop |

| PMU | Phasor Measurement Unit |

| PPS | Pulse-per-Second |

| RFE | ROCOF Error |

| ROCOF | Rate of Change of Frequency |

| RT | Real-Time |

| RTOS | Real-Time Operating System |

| SCADA | Supervisory Control and Data Acquisition |

| SoC | System-on-Chip |

| TVE | Total Vector Error |

| UTC | Coordinated Universal Time |

References

- Biswal, C.; Sahu, B.K.; Mishra, M.; Rout, P.K. Real-Time Grid Monitoring and Protection: A Comprehensive Survey on the Advantages of Phasor Measurement Units. Energies 2023, 16, 4054. [Google Scholar] [CrossRef]

- Singh, A.; Parida, S. Estimation of frequency and phasor using enhanced nonlinear least error squares method for synchrophasor application. Electr. Power Syst. Res. 2021, 201, 107494. [Google Scholar] [CrossRef]

- Carducci, C.G.C.; Lipari, G.; Giaquinto, N.; Ponci, F.; Monti, A. Error Model in Single-Board Computer-Based Phasor Measurement Units. IEEE Trans. Instrum. Meas. 2020, 69, 6155–6164. [Google Scholar] [CrossRef]

- Arefin, A.A.; Baba, M.; Singh, N.S.S.; Nor, N.B.M.; Sheikh, M.A.; Kannan, R.; Abro, G.E.M.; Mathur, N. Review of the Techniques of the Data Analytics and Islanding Detection of Distribution Systems Using Phasor Measurement Unit Data. Electronics 2022, 11, 2967. [Google Scholar] [CrossRef]

- Dashti, R.; Daisy, M.; Mirshekali, H.; Shaker, H.R.; Hosseini Aliabadi, M. A survey of fault prediction and location methods in electrical energy distribution networks. Measurement 2021, 184, 109947. [Google Scholar] [CrossRef]

- Qasim Khan, M.; Mohamud Ahmed, M.; Haidar, A.M. An accurate algorithm of PMU-based wide area measurements for fault detection using positive-sequence voltage and unwrapped dynamic angles. Measurement 2022, 192, 110906. [Google Scholar] [CrossRef]

- Sobbouhi, A.R.; Vahedi, A. Transient stability prediction of power system; a review on methods, classification and considerations. Electr. Power Syst. Res. 2021, 190, 106853. [Google Scholar] [CrossRef]

- Ahmed, M.; Meegahapola, L.; Vahidnia, A.; Datta, M. Stability and Control Aspects of Microgrid Architectures–A Comprehensive Review. IEEE Access 2020, 8, 144730–144766. [Google Scholar] [CrossRef]

- Dusabimana, E.; Yoon, S.G. A Survey on the Micro-Phasor Measurement Unit in Distribution Networks. Electronics 2020, 9, 305. [Google Scholar] [CrossRef]

- Sufyan, M.A.A.; Zuhaib, M.; Anees, M.A.; Khair, A.; Rihan, M. Implementation of PMU-Based Distributed Wide Area Monitoring in Smart Grid. IEEE Access 2021, 9, 140768–140778. [Google Scholar] [CrossRef]

- Hojabri, M.; Dersch, U.; Papaemmanouil, A.; Bosshart, P. A Comprehensive Survey on Phasor Measurement Unit Applications in Distribution Systems. Energies 2019, 12, 4552. [Google Scholar] [CrossRef]

- Lee, Y.; Song, H. Decentralized Load Shedding Method Based on Voltage Stability Margin Index Using Synchrophasor Measurement Technology. Electronics 2018, 7, 277. [Google Scholar] [CrossRef]

- Joshi, P.M.; Verma, H. Synchrophasor measurement applications and optimal PMU placement: A review. Electr. Power Syst. Res. 2021, 199, 107428. [Google Scholar] [CrossRef]

- Liu, Y.; Wu, L.; Li, J. D-PMU based applications for emerging active distribution systems: A review. Electr. Power Syst. Res. 2020, 179, 106063. [Google Scholar] [CrossRef]

- Ahmed, W.; Nayel, M.; El-Mohandes, M.T.; Gabbar, H. Simulated testing algorithm for μPMU full observation of unbalanced radial distribution grid. Electr. Power Syst. Res. 2021, 191, 106842. [Google Scholar] [CrossRef]

- Shahriar, M.; Habiballah, I.; Hussein, H. Optimization of Phasor Measurement Unit (PMU) Placement in Supervisory Control and Data Acquisition (SCADA)-Based Power System for Better State-Estimation Performance. Energies 2018, 11, 570. [Google Scholar] [CrossRef]

- Grando, F.L.; Denardin, G.W.; Moreto, M.; De Pelegrini Lopes, J. A PMU prototype for Synchronized Phasor and frequency measurements for smart grid applications. In Proceedings of the 2015 IEEE 13th Brazilian Power Electronics Conference and 1st Southern Power Electronics Conference (COBEP/SPEC), Fortaleza, Brazil, 29 November 2015–2 December 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Femine, A.D.; Gallo, D.; Landi, C.; Luiso, M. A Design Approach for a Low Cost Phasor Measurement Unit. In Proceedings of the 2019 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Auckland, New Zealand, 20–23 May 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Seger, P.V.H.; Grando, F.L.; Lazzaretti, A.E.; Moreto, M.; Denardin, G.W.; Pastro, C.R. Power System Monitoring Through Low-Voltage Distribution Network Using freePMU. IEEE Trans. Ind. Appl. 2022, 58, 3153–3163. [Google Scholar] [CrossRef]

- Romano, P.; Paolone, M.; Chau, T.; Jeppesen, B.; Ahmed, E. A high-performance, low-cost PMU prototype for distribution networks based on FPGA. In Proceedings of the 2017 IEEE Manchester PowerTech, Manchester, UK, 18–22 June 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Joglekar, A.; Gurrala, G.; Kumar, P.; Joseph, F.C.; Kiran, T.S.; Sahasranand, K.R.; Tyagi, H. Open-Source Heterogeneous Constrained Edge-Computing Platform for Smart Grid Measurements. IEEE Trans. Instrum. Meas. 2021, 70, 1–12. [Google Scholar] [CrossRef]

- Samantaray, S.R.; Nanda, S.; Dash, P. A Fast and Adaptive Dynamic Phasor Estimation Algorithm Implemented on Field Programmable Gate Array (FPGA). IEEE Trans. Ind. Electron. 2022, 69, 2088–2098. [Google Scholar] [CrossRef]

- Romano, P.; Paolone, M. Enhanced Interpolated-DFT for Synchrophasor Estimation in FPGAs: Theory, Implementation, and Validation of a PMU Prototype. IEEE Trans. Instrum. Meas. 2014, 63, 2824–2836. [Google Scholar] [CrossRef]

- Xu, S.; Liu, H.; Bi, T.; Martin, K.E. A High-Accuracy Phasor Estimation Algorithm for PMU Calibration and Its Hardware Implementation. IEEE Trans. Smart Grid 2020, 11, 3372–3383. [Google Scholar] [CrossRef]

- Li, J.; Xu, S.; Liu, H.; Bi, T. High-accuracy and low-complexity phasor estimation method for PMU calibration. CSEE J. Power Energy Syst. 2021, 7, 1202–1212. [Google Scholar] [CrossRef]

- Schofield, D.; Mohapatra, D.; Chamorro, H.R.; Roldan-Fernandez, J.M.; Abdellah, K.; Gonzalez-Longatt, F. Design and Implementation of Low-Cost Phasor Measurement Unit: PhasorsCatcher. Energies 2022, 15, 3172. [Google Scholar] [CrossRef]

- Zhao, X.; Laverty, D.M.; McKernan, A.; Morrow, D.J.; McLaughlin, K.; Sezer, S. GPS-Disciplined Analog-to-Digital Converter for Phasor Measurement Applications. IEEE Trans. Instrum. Meas. 2017, 66, 2349–2357. [Google Scholar] [CrossRef]

- Tosato, P.; Macii, D.; Brunelli, D. Implementation of phasor measurement units on low-cost embedded platforms: A feasibility study. In Proceedings of the 2017 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Turin, Italy, 22–25 May 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Tosato, P.; Macii, D.; Luiso, M.; Brunelli, D.; Gallo, D.; Landi, C. A Tuned Lightweight Estimation Algorithm for Low-Cost Phasor Measurement Units. IEEE Trans. Instrum. Meas. 2018, 67, 1047–1057. [Google Scholar] [CrossRef]

- Tosato, P.; Macii, D.; Fontanelli, D.; Brunelli, D.; Laverty, D. A Software-based Low-Jitter Servo Clock for Inexpensive Phasor Measurement Units. In Proceedings of the 2018 IEEE International Symposium on Precision Clock Synchronization for Measurement, Control, and Communication (ISPCS), Geneva, Switzerland, 30 September–5 October 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Leccese, F.; Cagnetti, M.; Di Pasquale, S.; Giarnetti, S.; Caciotta, M. A New Power Quality Instrument Based on Raspberry-Pi. Electronics 2016, 5, 64. [Google Scholar] [CrossRef]

- Mingotti, A.; Peretto, L.; Tinarelli, R.; Angioni, A.; Monti, A.; Ponci, F. Calibration of Synchronized Measurement System: From the Instrument Transformer to the PMU. In Proceedings of the 2018 IEEE 9th International Workshop on Applied Measurements for Power Systems (AMPS), Bologna, Italy, 26–28 September 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Carducci, C.G.C.; Lipari, G.; Bosbach, N.; Raimondo, T.D.; Ponci, F.; Monti, A. A Versatile Low-Cost OS-based Phasor Measurement Unit. In Proceedings of the 2019 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Auckland, New Zealand, 20–23 May 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Singh, A.; Parida, S.K. Power System Frequency and Phasor Estimation for a Low-Cost Synchrophasor Device Using the Nonlinear Least-Square Method. IEEE Trans. Ind. Appl. 2022, 58, 39–48. [Google Scholar] [CrossRef]

- IEC/IEEE 60255-118-1-2018; IEEE/IEC International Standard—Measuring Relays and Protection Equipment—Part 118-1: Synchrophasor for Power Systems—Measurements. IEEE: Piscataway, NJ, USA, 2018. [CrossRef]

- IEEE Std C37.242-2013; IEEE Guide for Synchronization, Calibration, Testing, and Installation of Phasor Measurement Units (PMUs) for Power System Protection and Control. IEEE: Piscataway, NJ, USA, 2013. [CrossRef]

- Grando, F.L.; Lazzaretti, A.E.; Denardin, G.W.; Moreto, M.; Neto, H.V. A Synchrophasor Test Platform for Development and Assessment of Phasor Measurement Units. IEEE Trans. Ind. Appl. 2018, 54, 3122–3131. [Google Scholar] [CrossRef]

- Frigo, G.; Colangelo, D.; Derviškadić, A.; Pignati, M.; Narduzzi, C.; Paolone, M. Definition of Accurate Reference Synchrophasors for Static and Dynamic Characterization of PMUs. IEEE Trans. Instrum. Meas. 2017, 66, 2233–2246. [Google Scholar] [CrossRef]

- Frigo, G.; Derviškadić, A.; Colangelo, D.; Braun, J.; Paolone, M. Characterization of uncertainty contributions in a high-accuracy PMU validation system. Measurement 2019, 146, 72–86. [Google Scholar] [CrossRef]

- Grando, F.L.; Denardin, G.W.; Moreto, M. Test platform for analysis and development of Phasor Measurement Units (PMU). In Proceedings of the 2016 12th IEEE International Conference on Industry Applications (INDUSCON), Curitiba, PR, Brazil, 20–23 November 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Abdolkhalig, A.; Zivanovic, R. Phasor measurement based on IEC 61850-9-2 and Kalman–Filtering. Measurement 2014, 50, 126–134. [Google Scholar] [CrossRef]

- Hajimolahoseini, H.; Taban, M.R.; Soltanian-Zadeh, H. Extended Kalman Filter frequency tracker for nonstationary harmonic signals. Measurement 2012, 45, 126–132. [Google Scholar] [CrossRef]

- Belega, D.; Petri, D.; Dallet, D. Accurate frequency estimation of a noisy sine-wave by means of an interpolated discrete-time Fourier transform algorithm. Measurement 2018, 116, 685–691. [Google Scholar] [CrossRef]

- Mejia-Barron, A.; Granados-Lieberman, D.; Razo-Hernandez, J.; Amezquita-Sanchez, J.; Valtierra-Rodriguez, M. Harmonic PMU Algorithm Based on Complex Filters and Instantaneous Single-Sideband Modulation. Electronics 2019, 8, 135. [Google Scholar] [CrossRef]

- Mingotti, A.; Costa, F.; Cavaliere, D.; Peretto, L.; Tinarelli, R. On the Importance of Characterizing Virtual PMUs for Hardware-in-the-Loop and Digital Twin Applications. Sensors 2021, 21, 6133. [Google Scholar] [CrossRef]

- Hu, Y.; Cheng, J.; Zhou, Y.; Chen, G. Control strategy of a high power grid simulator for the test of renewable energy grid converter. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017; pp. 7747–7752. [Google Scholar] [CrossRef]

- Bountouris, P.; Tzelepis, D.; Abdulhadi, I.; Coffele, F. Dynamic Model of Commercially Available Inverters with Validation Against Hardware Testing. IEEE Trans. Power Syst. 2022, 38, 2007–2017. [Google Scholar] [CrossRef]

- NI 6259; Device Specifications. National Instruments: Austin, TX, USA, 2016.

- NI 9225; Operating Instructions and Specifications. National Instruments: Austin, TX, USA, 2014.

- Adhikari, P.M.; Hooshyar, H.; Vanfretti, L. Experimental Quantification of Hardware Requirements for FPGA-Based Reconfigurable PMUs. IEEE Access 2019, 7, 57527–57538. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kunac, A.; Petrović, G.; Despalatović, M.; Jurčević, M. A Low-Cost Test Platform for Performance Analysis of Phasor Measurement Units. Electronics 2024, 13, 245. https://doi.org/10.3390/electronics13020245

Kunac A, Petrović G, Despalatović M, Jurčević M. A Low-Cost Test Platform for Performance Analysis of Phasor Measurement Units. Electronics. 2024; 13(2):245. https://doi.org/10.3390/electronics13020245

Chicago/Turabian StyleKunac, Antonijo, Goran Petrović, Marin Despalatović, and Marko Jurčević. 2024. "A Low-Cost Test Platform for Performance Analysis of Phasor Measurement Units" Electronics 13, no. 2: 245. https://doi.org/10.3390/electronics13020245

APA StyleKunac, A., Petrović, G., Despalatović, M., & Jurčević, M. (2024). A Low-Cost Test Platform for Performance Analysis of Phasor Measurement Units. Electronics, 13(2), 245. https://doi.org/10.3390/electronics13020245