A Wideband Timing Mismatch Calibration Design for Time-Interleaved Analog-to-Digital Converters with Fast Convergence

Abstract

1. Introduction

2. The Proposed Calibration Design

2.1. Timing Mismatch Estimation and Compensation

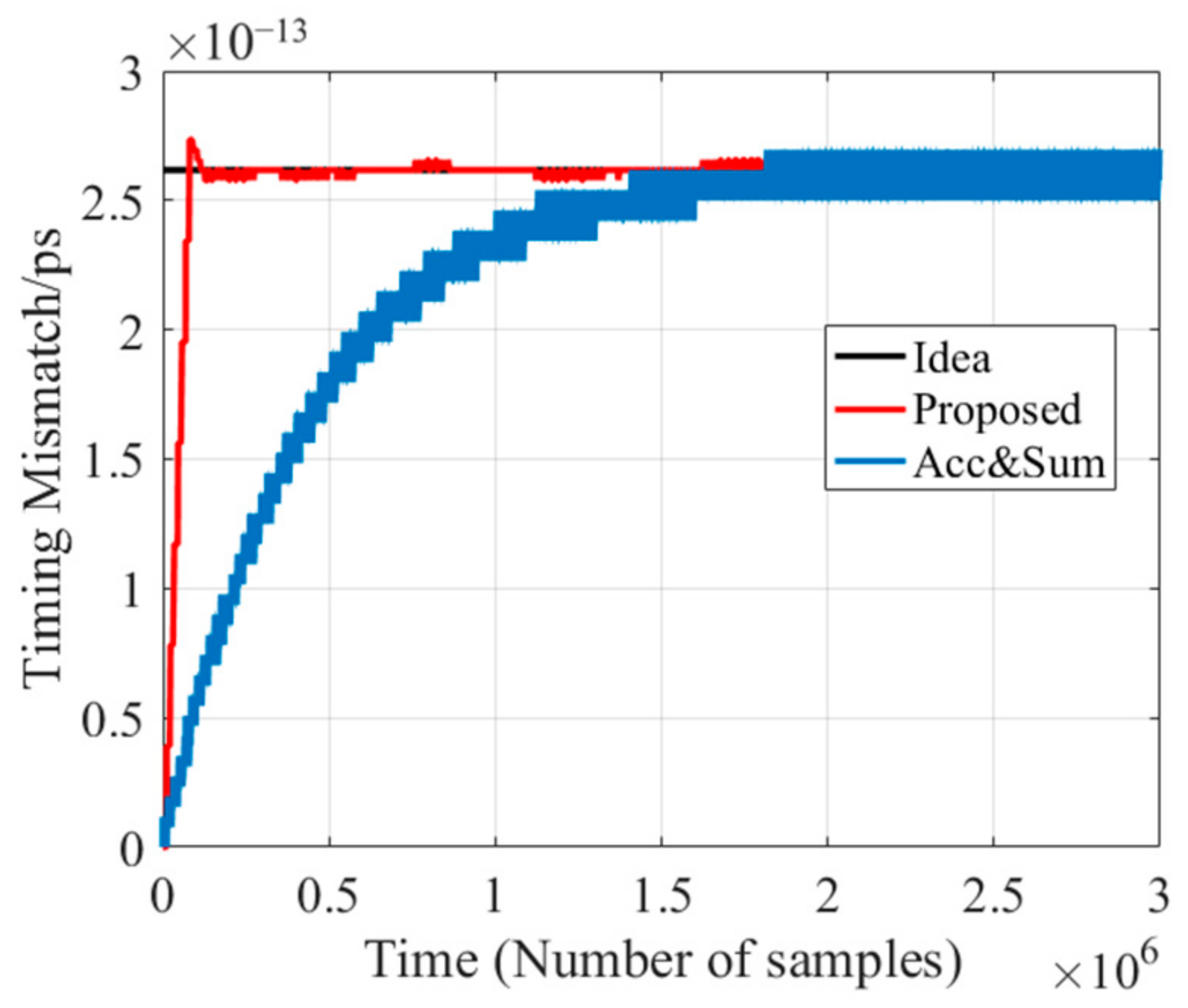

2.2. Mismatch Estimation Fast Convergence

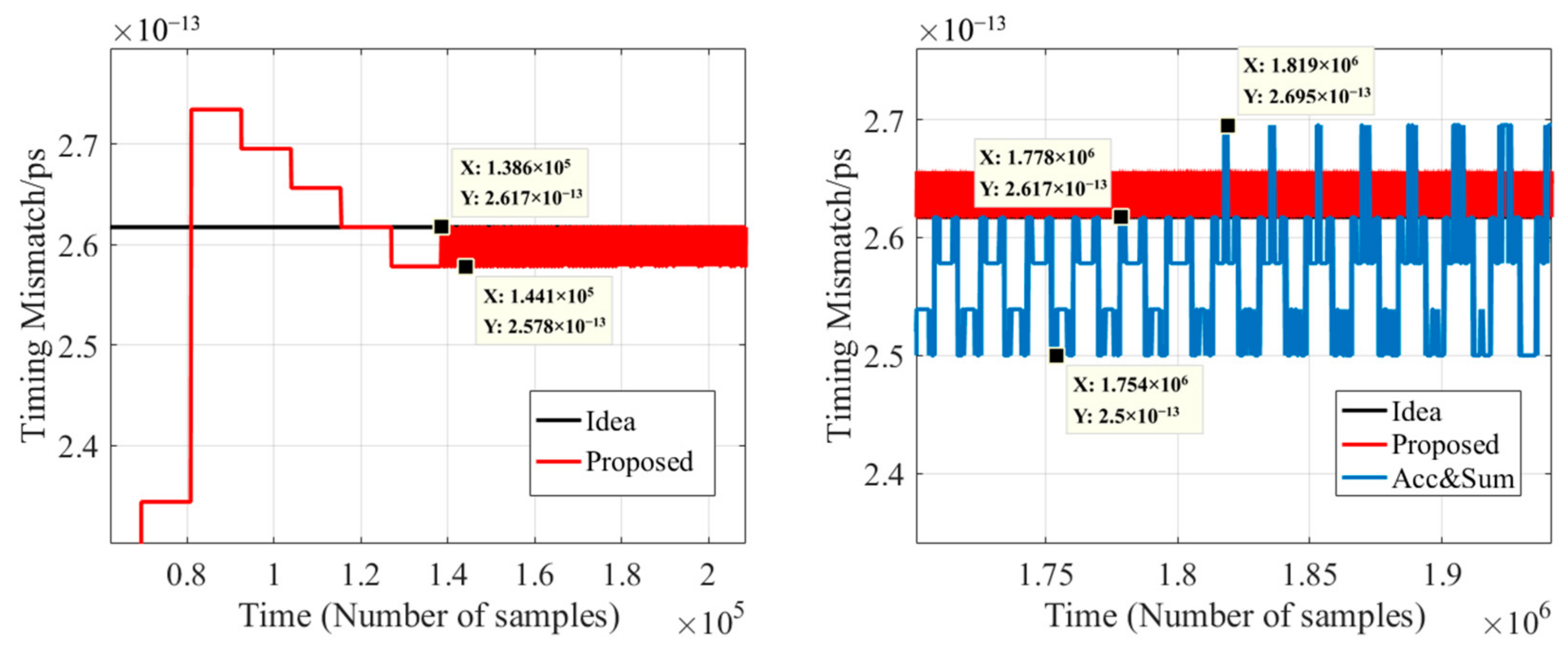

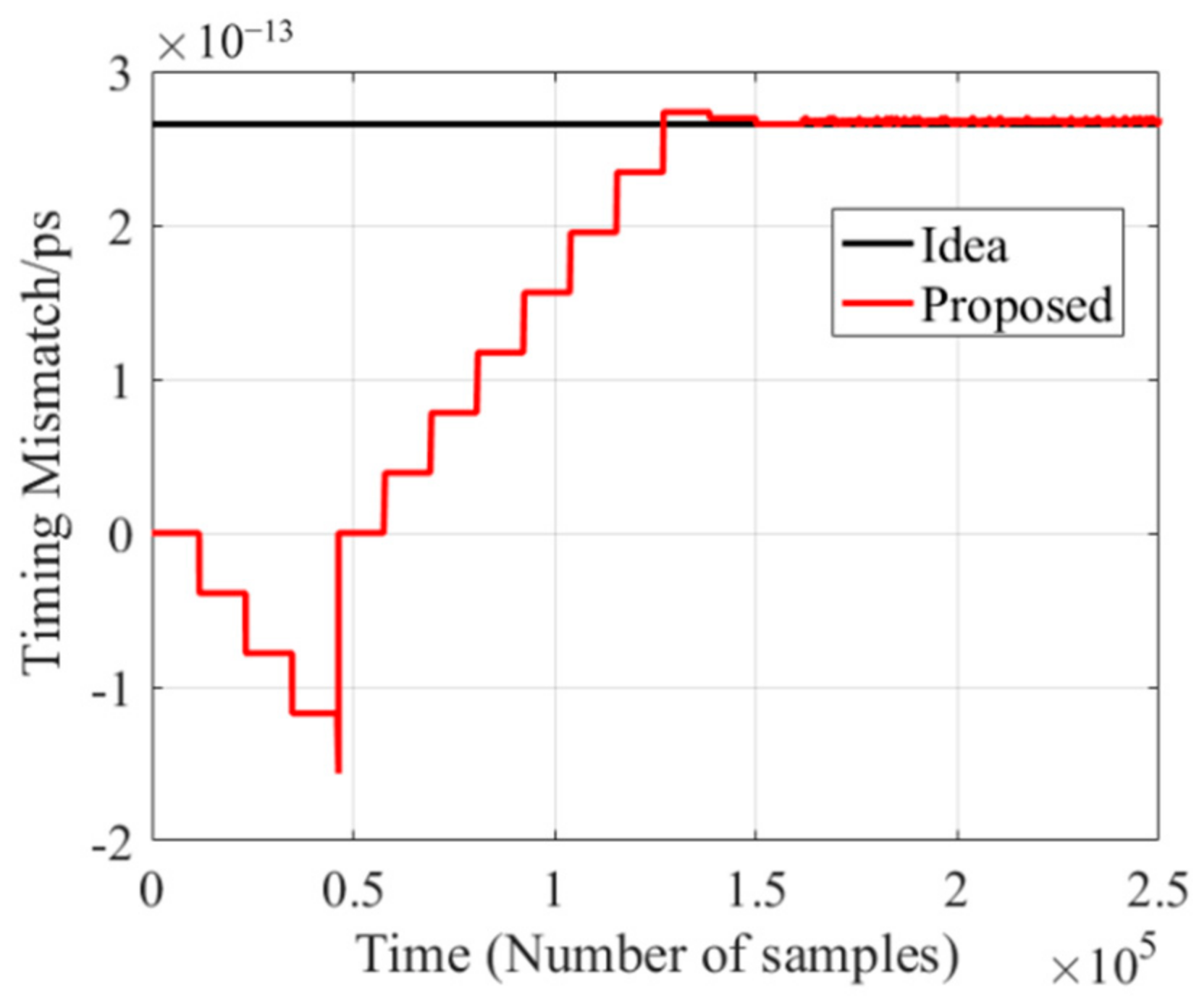

2.3. Calibration Direction Auto Correction

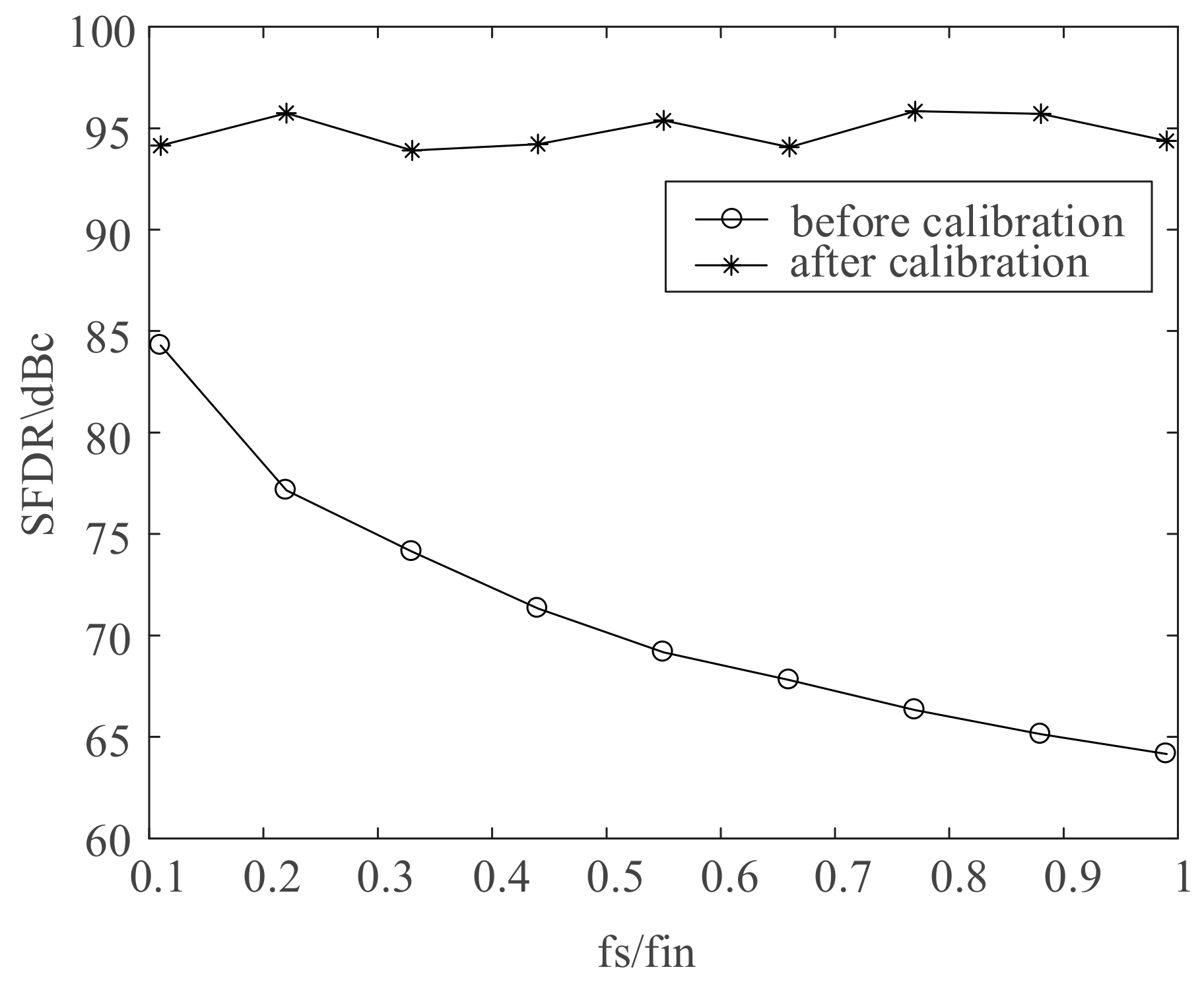

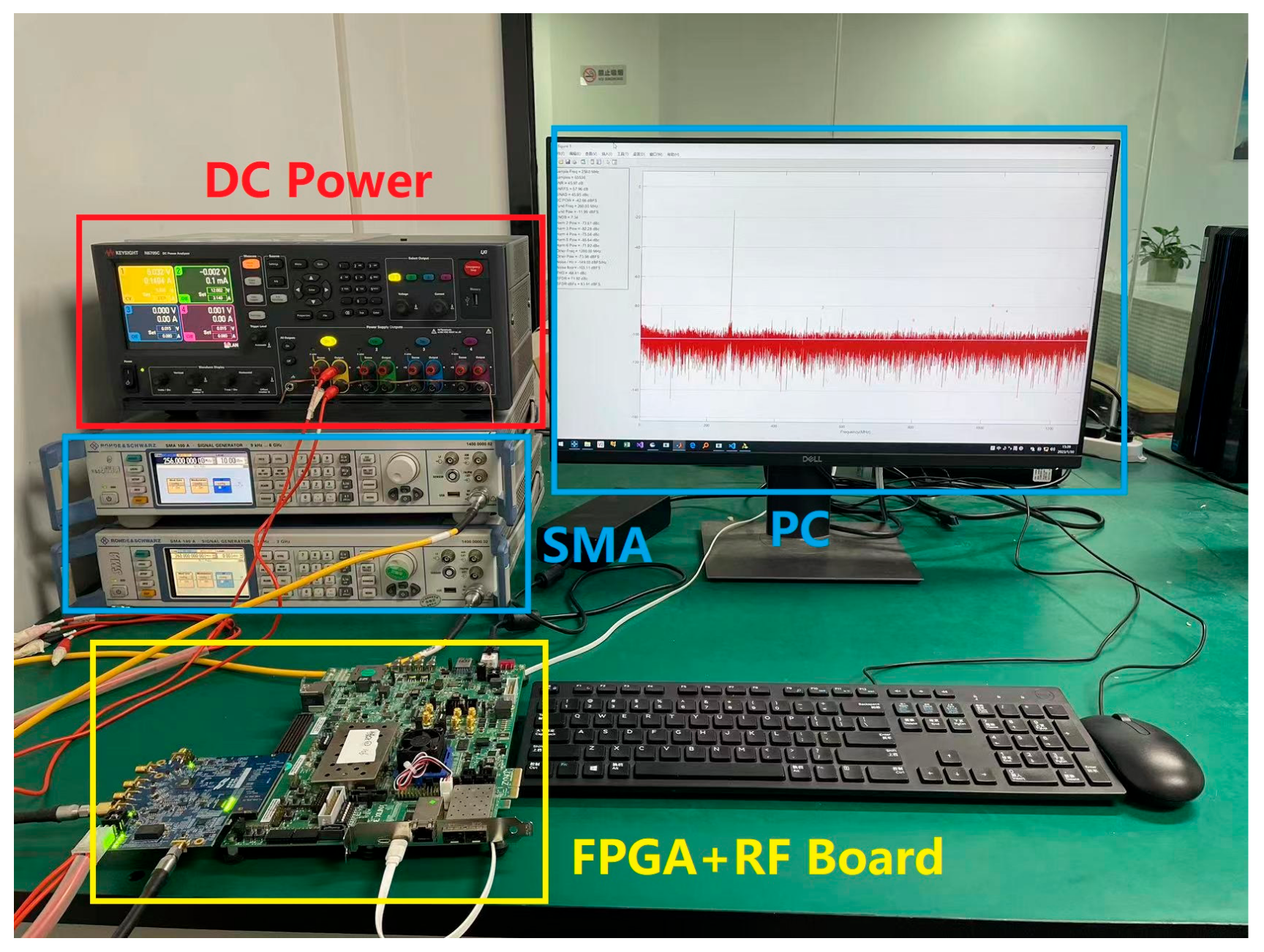

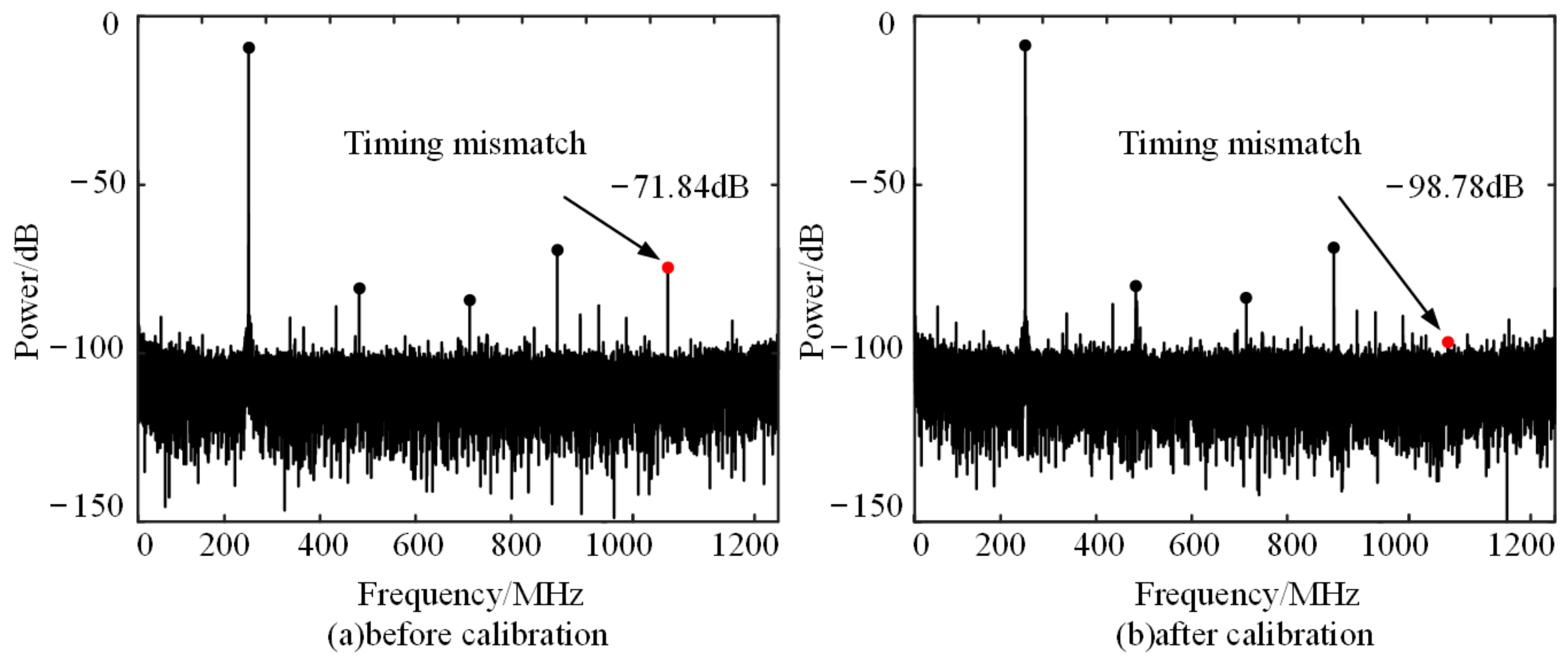

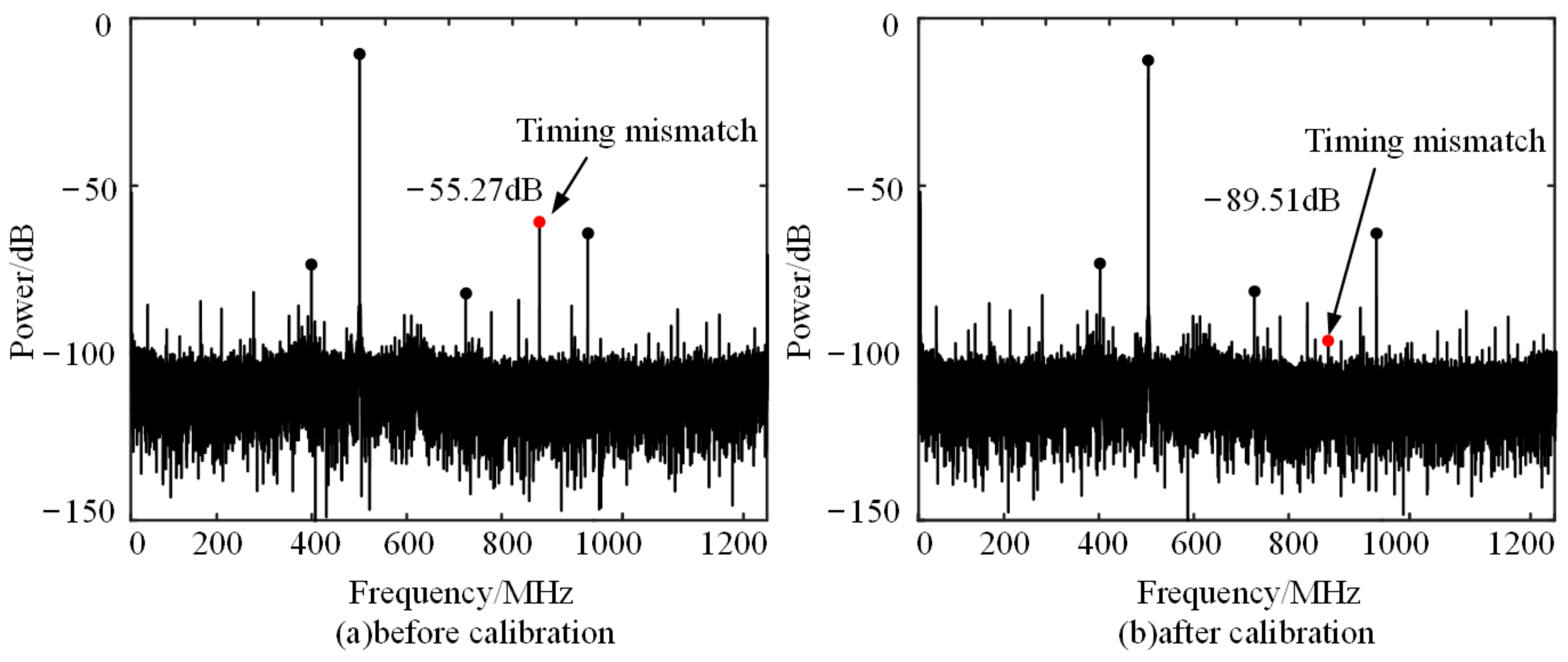

3. Physical Test Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, C.-Y.; Wu, J.; Hung, J.-J.; Li, T.; Liu, W.; Shih, W.-T. A 12-Bit 3 GS/s Pipeline ADC With 0.4 mm2 and 500 mW in 40 nm Digital CMOS. IEEE J. Solid-State Circuits 2012, 47, 1013–1021. [Google Scholar] [CrossRef]

- Janssen, E.; Doris, K.; Zanikopoulos, A.; Murroni, A.; van der Weide, G.; Lin, Y.; Alvado, L.; Darthenay, F.; Fregeais, Y. An 11b 3.6GS/s time-interleaved SAR ADC in 65 nm CMOS. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 464–465. [Google Scholar]

- Doris, K.; Janssen, E.; Nani, C.; Zanikopoulos, A.; van der Weide, G. A 480 mW 2.6 GS/s 10b Time-Interleaved ADC With 48.5 dB SNDR up to Nyquist in 65 nm CMOS. IEEE J. Solid-State Circuits 2011, 46, 2821–2833. [Google Scholar] [CrossRef]

- Guo, M.; Sin, S.-W.; Qi, L.; Xu, D.; Wang, G.; Martins, R.P. Background Timing Mismatch Calibration Techniques in High-Speed Time-Interleaved ADCs: A Tutorial Review. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 2564–2569. [Google Scholar] [CrossRef]

- Razavi, B. Design Considerations for Interleaved ADCs. IEEE J. Solid-State Circuits 2013, 48, 1806–1817. [Google Scholar] [CrossRef]

- Wang, C.-Y.; Wu, J.-T. A background timing-skew calibration technique for time-interleaved analog-to-digital converters. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 299–303. [Google Scholar] [CrossRef]

- Kang, H.-W.; Hong, H.-K.; Kim, W.; Ryu, S.-T. A Time-Interleaved 12-b 270-MS/s SAR ADC With Virtual-Timing-Reference Timing-Skew Calibration Scheme. IEEE J. Solid-State Circuits 2018, 53, 2584–2594. [Google Scholar] [CrossRef]

- Liu, W.; Chiu, Y. Time-Interleaved Analog-to-Digital Conversion with Online Adaptive Equalization. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 1384–1395. [Google Scholar] [CrossRef]

- Ni, M.; Wang, X.; Li, F.; Rhee, W.; Wang, Z. A 13-Bit 2-GS/s Time-Interleaved ADC with Improved Correlation-Based Timing Skew Calibration Strategy. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 481–494. [Google Scholar] [CrossRef]

- El-Chammas, M.; Murmann, B. A 12-GS/s 81-mW 5-bit Time-Interleaved Flash ADC with Background Timing Skew Calibration. IEEE J. Solid-State Circuits 2011, 46, 838–847. [Google Scholar] [CrossRef]

- Wei, H.; Zhang, P.; Datta Sahoo, B.; Razavi, B. An 8-Bit 4-GS/s 120-mW CMOS ADC. In Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, San Jose, CA, USA, 22–25 September 2013; pp. 1–4. [Google Scholar]

- Lee, S.; Chandrakasan, A.P.; Lee, H.-S. A 1 GS/s 10b 18.9 mW Time-Interleaved SAR ADC With Background Timing Skew Calibration. IEEE J. Solid-State Circuits 2014, 49, 2846–2856. [Google Scholar] [CrossRef]

- Song, J.; Ragab, K.; Tang, X.; Sun, N. A 10-b 800-MS/s Time-Interleaved SAR ADC With Fast Variance-Based Timing-Skew Calibration. IEEE J. Solid-state Circuits 2017, 52, 2563–2575. [Google Scholar] [CrossRef]

- Kang, H.-W.; Hong, H.-K.; Park, S.; Kim, K.-J.; Ahn, K.-H.; Ryu, S.-T. A Sign-Equality-Based Background Timing-Mismatch Calibration Algorithm for Time-Interleaved ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 518–522. [Google Scholar] [CrossRef]

- Yin, Y.; Sun, K.; Chen, H.; Wang, X.; Liu, L.; Deng, H.; Meng, X.; Li, K.; Wang, Z. Calibration of timing mismatch in tiadc based on monotonicity detecting of sampled data. IEICE Electron. Express 2020, 17, 20190699. [Google Scholar] [CrossRef]

- Li, D.; Zhu, Z.; Ding, R.; Liu, M.; Yang, Y.; Sun, N. A 10-Bit 600-MS/s Time-Interleaved SAR ADC With Interpolation-Based Timing Skew Calibration. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 16–20. [Google Scholar] [CrossRef]

- Li, D.; Ding, R.; Zhu, Z.; Yang, Y. A Background Timing Skew Calibration Technique in Time-Interleaved ADCs With Second Order Compensation. In Proceedings of the 2018 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Chengdu, China, 26–30 October 2018; pp. 53–56. [Google Scholar]

- Stepanovic, D.; Nikolic, B. A 2.8 GS/s 44.6 mW Time-Interleaved ADC Achieving 50.9 dB SNDR and 3 dB Effective Resolution Bandwidth of 1.5 GHz in 65 nm CMOS. IEEE J. Solid-state Circuits 2013, 48, 971–982. [Google Scholar] [CrossRef]

- Chang, D.-J.; Choi, M.; Ryu, S.-T. A 28-nm 10-b 2.2-GS/s 18.2-mW Relative-Prime Time-Interleaved Sub-Ranging SAR ADC With On-Chip Background Skew Calibration. IEEE J. Solid-State Circuits 2021, 56, 2691–2700. [Google Scholar] [CrossRef]

- Chiu, Y.; Tsang, C.W.; Nikolic, B.; Gray, P.R. Least mean square adaptive digital background calibration of pipelined analog-to-digital converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2004, 51, 38–46. [Google Scholar] [CrossRef]

- Chiu, Y. Equalization techniques for nonlinear analog circuits. IEEE Commun. Mag. 2011, 49, 132–139. [Google Scholar] [CrossRef]

- Oshima, T.; Takahashi, T.; Yamawaki, T. LMS calibration of sampling timing for time-interleaved A/D converters. Electron. Lett. 2009, 45, 615–617. [Google Scholar] [CrossRef]

- Guo, M.; Mao, J.; Sin, S.-W.; Wei, H.; Martins, R.P. A 10b 1.6GS/s 12.2mW 7/8-way Split Time-interleaved SAR ADC with Digital Background Mismatch Calibration. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar]

- Le Dortz, N.; Blanc, J.P.; Simon, T.; Verhaeren, S.; Rouat, E.; Urard, P.; Le Tual, S.; Goguet, D.; Lelandais-Perrault, C.; Benabes, P. 22.5 A 1.62GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70dBFS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 386–388. [Google Scholar]

- Le Duc, H.; Nguyen, D.M.; Jabbour, C.; Desgreys, P.; Jamin, O.; Nguyen, V.T. Fully Digital Feedforward Background Calibration of Clock Skews for Sub-Sampling TIADCs Using the Polyphase Decomposition. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1515–1528. [Google Scholar] [CrossRef]

- Guo, M.; Mao, J.; Sin, S.-W.; Wei, H.; Martins, R.P. A 5 GS/s 29 mW Interleaved SAR ADC With 48.5 dB SNDR Using Digital-Mixing Background Timing-Skew Calibration for Direct Sampling Applications. IEEE Access 2020, 8, 138944–138954. [Google Scholar] [CrossRef]

- Devarajan, S.; Singer, L.; Kelly, D.; Pan, T.; Silva, J.; Brunsilius, J.; Rey-Losada, D.; Murden, F.; Speir, C.; Bray, J.; et al. A 12-b 10-GS/s Interleaved Pipeline ADC in 28-nm CMOS Technology. IEEE J. Solid-State Circuits 2017, 52, 3204–3218. [Google Scholar] [CrossRef]

- Bendat, J.S.; Piersol, A.G. Random Data: Analysis and Measurement Procedures; John Wiley & Sons: Hoboken, NJ, USA, 2011. [Google Scholar]

- Niu, H.; Yuan, J. A Spectral-Correlation-Based Blind Calibration Method for Time-Interleaved ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 5007–5017. [Google Scholar] [CrossRef]

| Design Features | [9] | [29] | [14] | [17] | [11] | This Work |

|---|---|---|---|---|---|---|

| Estimation type | Digital | Digital | Digital | Digital | Digital | Digital |

| Correction type | Digital | Digital | Analog | Digital | Analog | Analog |

| Reference channel | None | Yes | Yes | None | None | None |

| Input signal exceed | No | No | No | No | No | Yes |

| Nyquist zone | ||||||

| Convergence time (samples) | 1.2 M | >1 M | 250 K | 430 K | 382 K | 140 K |

| Mismatch spur (dBFS) | −80 * | <−71 | <−80 * | <−72 * | <−60 | <−85 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, G.; Xu, D.; Gao, P.; Zhou, M.; Liu, J.; Wang, Z. A Wideband Timing Mismatch Calibration Design for Time-Interleaved Analog-to-Digital Converters with Fast Convergence. Electronics 2024, 13, 2459. https://doi.org/10.3390/electronics13132459

Huang G, Xu D, Gao P, Zhou M, Liu J, Wang Z. A Wideband Timing Mismatch Calibration Design for Time-Interleaved Analog-to-Digital Converters with Fast Convergence. Electronics. 2024; 13(13):2459. https://doi.org/10.3390/electronics13132459

Chicago/Turabian StyleHuang, Guojing, Dong Xu, Peng Gao, Min Zhou, Jiarui Liu, and Zhiyu Wang. 2024. "A Wideband Timing Mismatch Calibration Design for Time-Interleaved Analog-to-Digital Converters with Fast Convergence" Electronics 13, no. 13: 2459. https://doi.org/10.3390/electronics13132459

APA StyleHuang, G., Xu, D., Gao, P., Zhou, M., Liu, J., & Wang, Z. (2024). A Wideband Timing Mismatch Calibration Design for Time-Interleaved Analog-to-Digital Converters with Fast Convergence. Electronics, 13(13), 2459. https://doi.org/10.3390/electronics13132459