Dual-Core PLC for Cooperating Projects with Software Implementation

Abstract

1. Introduction

- Two separate PLCs.

- PLC and a PID control instruments.

- Distributed control systems (DCSs) with a controller running a real-time OS.

2. Related Work

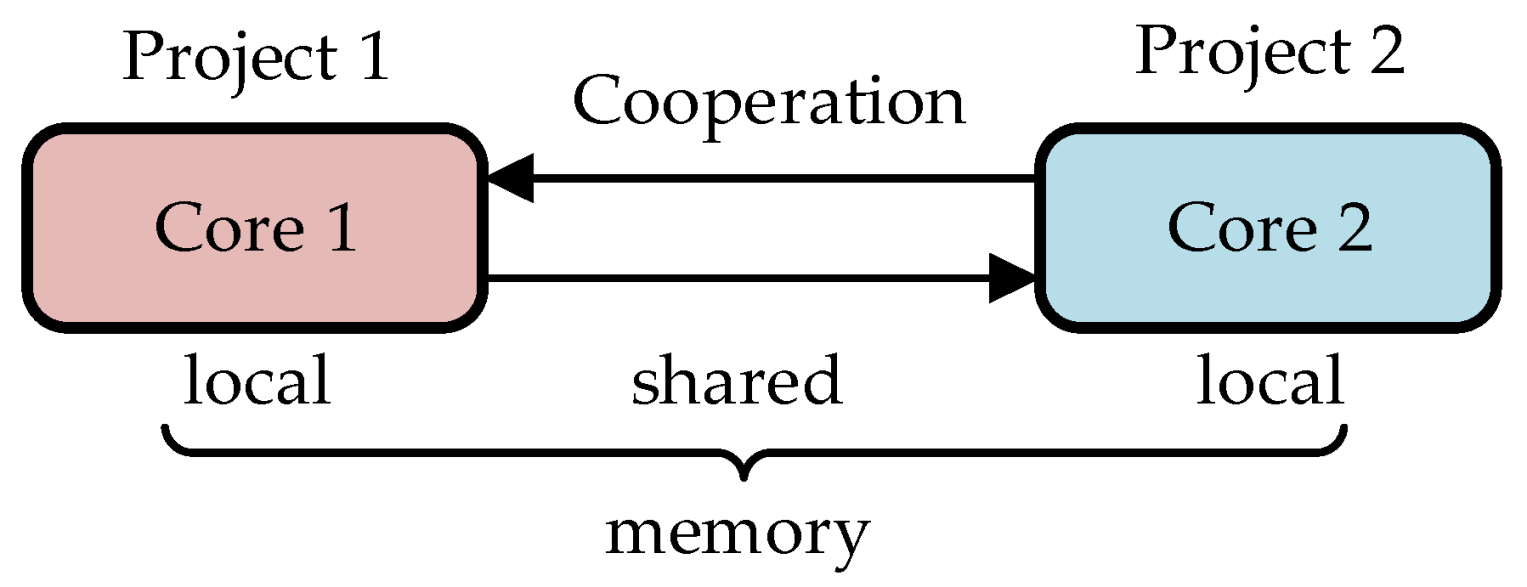

3. The Concept of a Dual-Core PLC

3.1. Notes on the IEC 61131-3 Standard

3.2. General Architecture of a Dual-Core PLC

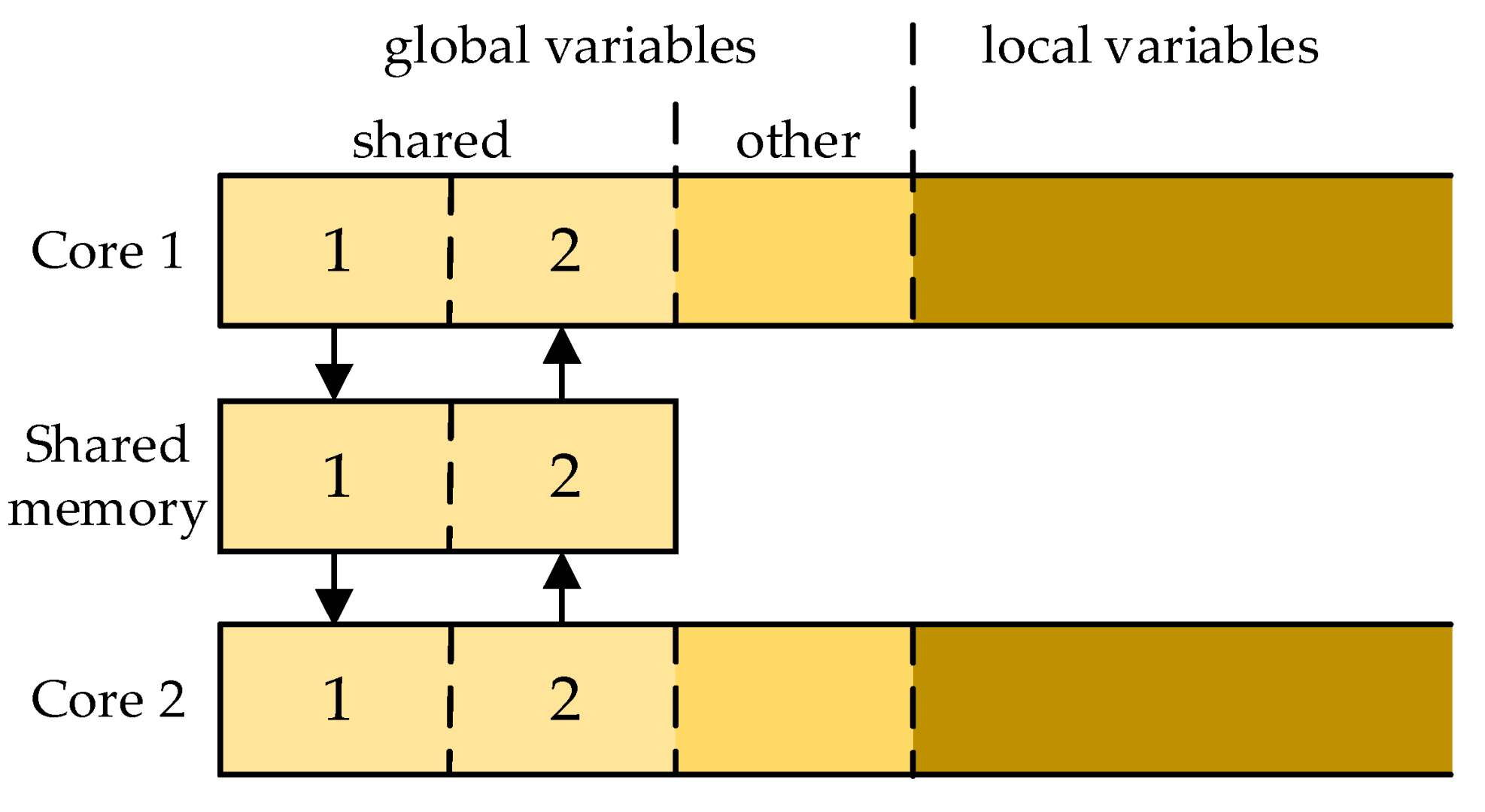

3.3. Shared Global Variables

- Declaration of global variables in each of the two projects must contain all shared variables, i.e., the GV set.

3.4. Improvement of Memory Organization

- CM11—sector for GV1 (updated WRITE, another words output);

- CM12—sector for GV2 (received READ—input).

3.5. Operation of a Dual-Core PLC

- IDE: an additional attribute of a shared global variable to indicate whether it is updated in the actual core or received from the other one.

- Compiler: memory arrangement so as to have updated and received shared variables in compact sectors (optional).

- Runtime: copy-from the shared memory at the beginning of the cycle (precycle) and copy-to at the end (postcycle).

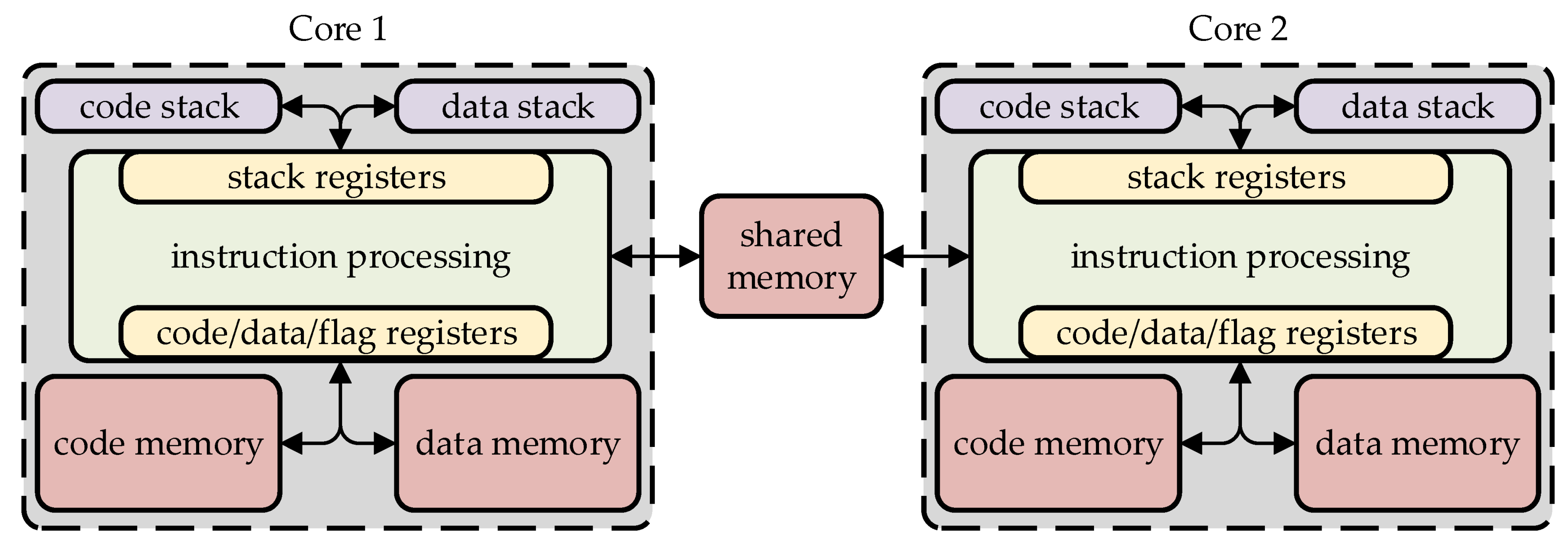

4. Virtual Machine for a Dual-Core Processor

4.1. Runtime Environments

4.2. CPDev Virtual Machine

4.3. Upgrade to Dual-Core

- CM_TO_SH (LocalAddress, SharedAddress, ByteNumber).

- SH_TO_CM (SharedAddress, LocalAddress, ByteNumber).

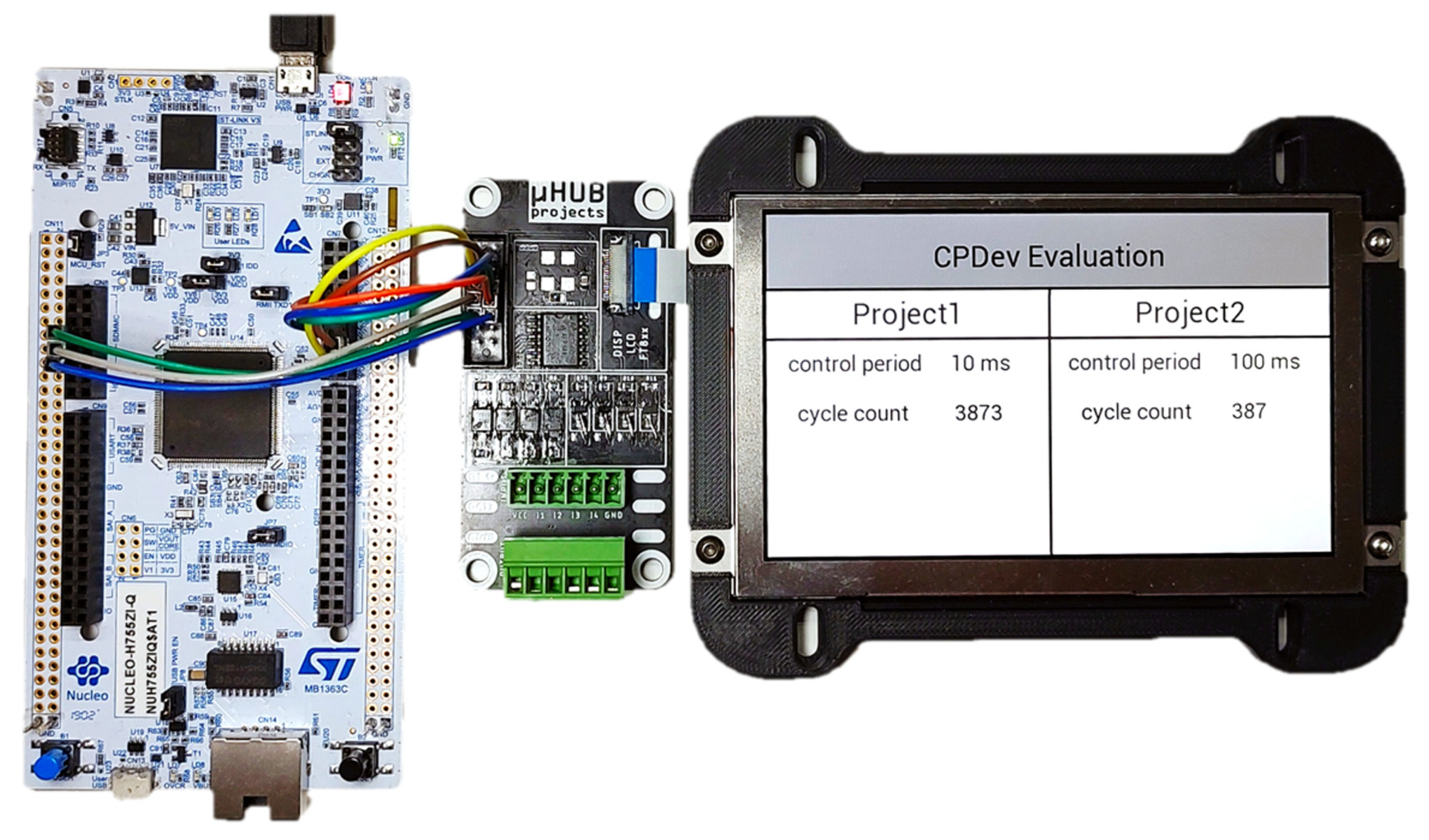

5. Lab Prototype of a Dual-Core PLC

5.1. Multi-Core Processors

5.2. Lab Prototype with STM32

5.3. Time Interrupt and Memory Protection

6. Running Two Projects and Tests

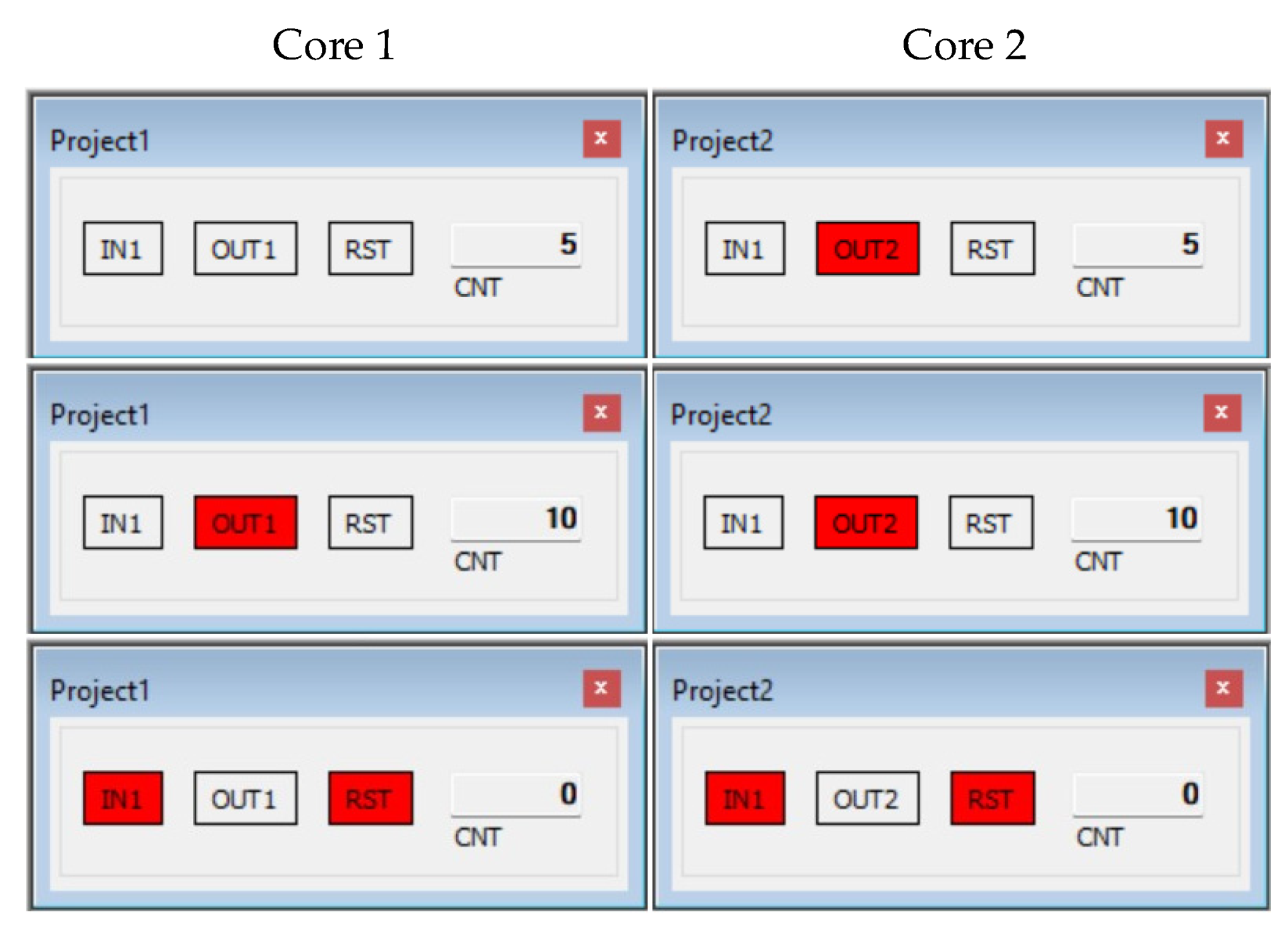

6.1. Details of the Projects

6.2. Experimental Results

7. Conclusions

- New attribute of each shared variable indicating whether it is updated or received in a project.

- Compact sectors for the shared variables in the controller memories (optional).

- Data transfers from/to the shared memory at the beginning and end of the control cycle.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Automation Technology for PLCnext Technology. Phoenix Contact. Available online: https://www.phoenixcontact.com/en-gb/products/plcs-controllers-and-i-os/automation-technology-for-plcnext-technology (accessed on 11 October 2023).

- CX8200|Embedded PC Series (Compact Controller). Beckhoff Automation. Available online: https://www.beckhoff.com/en-en/products/ipc/embedded-pcs/cx8200-arm-cortex-a53/ (accessed on 11 October 2023).

- John, K.H.; Tiegelkamp, M. IEC 61131-3: Programming Industrial Automation Systems; Springer: Berlin/Heidelberg, Germany, 2010. [Google Scholar] [CrossRef]

- ARM Microcontrollers Market Size, Share, Opportunities & Forecast. Verified Market Research. Available online: https://www.verifiedmarketresearch.com/product/arm-microcontrollers-market/ (accessed on 11 October 2023).

- The OpenAMP Project. Available online: https://www.openampproject.org/ (accessed on 11 October 2023).

- Zynq 7000 SOC. AMD (XILINX). Available online: https://www.xilinx.com/products/silicon-devices/soc/zynq-7000.html (accessed on 11 October 2023).

- Cisek, J.; Mikluszka, W.; Świder, Z.; Trybus, L. A Low-Cost DCS with Multifunction Instruments and CAN Bus 1. IFAC Proc. Vol. 2001, 34, 64–69. [Google Scholar] [CrossRef]

- Martos, P.I. Architectural Patterns for Asymmetric Multiprocessing Devices on Embedded Systems. In Proceedings of the SugarLoafPLoP ’16: Proceedings of the 11th Latin-American Conference on Pattern Languages of Programming, Buenos Aires, Argentina, 16 November 2016; pp. 1–13. [Google Scholar]

- Becker, M.; Sandström, K.; Behnam, M.; Nolte, T. A Many-Core Based Execution Framework for IEC 61131-3. In Proceedings of the IECON 2015—41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015. [Google Scholar] [CrossRef]

- Mubeen, S.; Becker, M.; Zhao, X.; Gan, L.; Behnam, M.; Nolte, T. Towards Automated Deployment of IEC 61131-3 Applications on Multi-Core Systems. In Proceedings of the 2016 IEEE World Conference on Factory Communication Systems (WFCS), Aveiro, Portugal, 3–6 May 2016. [Google Scholar] [CrossRef]

- Specht, F.; Flatt, H.; Eickmeyer, J.; Niggemann, O. Exploiting Multicore Processors in PLCs Using Libraries for IEC 61131-3. In Proceedings of the 2015 IEEE 20th Conference on Emerging Technologies & Factory Automation (ETFA), Luxembourg, 8–11 September 2015. [Google Scholar] [CrossRef]

- Ning, B.; Li, D.; Ling, Y.; Zhihua, B.; He, L.; Zhang, G.; Li, M. Asymmetric Software Architecture Design of High Performance Control Chip Applied in Industrial Control Field. In Proceedings of the 2021 4th International Conference on Advanced Electronic Materials, Computers and Software Engineering (AEMCSE), Changsha, China, 26–28 March 2021. [Google Scholar] [CrossRef]

- Salčić, Z.; Nadeem, M.; Park, H.; Teich, J. A Heterogeneous Multi-Core SoC for Mixed Criticality Industrial Automation Systems. In Proceedings of the 2016 IEEE 21st International Conference on Emerging Technologies and Factory Automation (ETFA), Berlin, Germany, 6–9 September 2016. [Google Scholar] [CrossRef]

- Mazur, P.; Czerwinski, R.; Chmiel, M. PLC Implementation in the Form of a System-on-a-Chip. Bull. Pol. Acad. Sci. Tech. Sci. 2020, 68, 1263–1273. [Google Scholar] [CrossRef]

- Zoitl, A.; Lewis, R.W. Modelling Control Systems Using IEC 61499; The Institution of Engineering and Technology: Stevenage, UK, 2014. [Google Scholar] [CrossRef]

- Ochoa-Ruiz, G. Enabling Adaptable IEC 61499-Based Cyber-Physical Systems Using SoC FPGAs and Partial Reconfiguration. ACM Comput. Surv. 2020. [Google Scholar] [CrossRef]

- Sun, Y.; Li, E.; Yang, G.; Liang, Z.; Guo, R. Design of a Dual-Core Processor Based Controller with RTOS-GPOS Dual Operating System. In Proceedings of the 2019 IEEE International Conference on Mechatronics and Automation (ICMA), Tianjin, China, 4–7 August 2019. [Google Scholar] [CrossRef]

- Cong, V.D. Industrial Robot Arm Controller Based on Programmable System-on-Chip Device. FME Trans. 2021, 49, 1025–1034. [Google Scholar] [CrossRef]

- Dočekal, T.; Slanina, Z. Control System Based on FreeRTOS for Data Acquisition and Distribution on Swarm Robotics Platform. In Proceedings of the 2017 18th International Carpathian Control Conference (ICCC), Sinaia, Romania, 28–31 May 2017. [Google Scholar] [CrossRef]

- Alonso, S.; Lázaro, J.; Jiménez, J.; Muguira, L.; Bidarte, U. Evaluating the OpenAMP Framework in Real-Time Embedded SoC Platforms. In Proceedings of the 2021 XXXVI Conference on Design of Circuits and Integrated Systems (DCIS), Vila do Conde, Portugal, 24–26 November 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Alonso, S.; Lázaro, J.; Jiménez, J.; Bidarte, U.; Muguira, L. Evaluating Latency in Multiprocessing Embedded Systems for the Smart Grid. Energies 2021, 14, 3322. [Google Scholar] [CrossRef]

- Queiroz, R.; Cruz, T.; Simões, P. Testing the Limits of General-Purpose Hypervisors for Real-Time Control Systems. Microprocess. Microsyst. 2023, 99, 104848. [Google Scholar] [CrossRef]

- Mariton, M.; Bertrand, P. Reliable Flight Control Systems: Components Placement and Feedback Synthesis. IFAC Proc. Vol. 1987, 20, 151–155. [Google Scholar] [CrossRef]

- Losada, M.; Adin, I.; Perez, A.; Ramírez, R.C.; Mendizabal, J. Connected Heterogenous Multi-Processing Architecture for Digitalization of Freight Railway Transport Applications. Electronics 2022, 11, 943. [Google Scholar] [CrossRef]

- Ulmer, D.; Wittel, S.; Huenlich, K.; Rosenstiel, W. A Hardware-in-the-Loop Testing Platform Based on a Common Off-The-Shelf Non-Real-Time Simulation PC. In Proceedings of the Sixth International Conference on Systems, St. Maarten, The Netherlands, 23–28 January 2011. [Google Scholar]

- CODESYS. Available online: https://www.codesys.com/ (accessed on 11 October 2023).

- SIMATIC STEP 7 (TIA Portal). SIEMENS. Available online: https://www.siemens.com/global/en/products/automation/industry-software/automation-software/tia-portal/software/step7-tia-portal.html (accessed on 11 October 2023).

- Automation Builder. Available online: https://new.abb.com/plc/automationbuilder (accessed on 11 October 2023).

- LogicLab. Available online: https://www.axelsoftware.it/en/logiclab/ (accessed on 11 October 2023).

- Beremiz. Available online: https://beremiz.org/ (accessed on 11 October 2023).

- GEB Automation. Available online: https://www.gebautomation.com/ (accessed on 11 October 2023).

- OpenPLC. Available online: https://autonomylogic.com/ (accessed on 11 October 2023).

- Lindholm, T.; Yellin, F.; Bracha, G.; Buckley, A. The Java Virtual Machine Specification, Java SE 8 Edition; Addison-Wesley Professional: Redwood City, CA, USA, 2014. [Google Scholar]

- Richter, J. CLR via C#, 4th ed.; Microsoft Press: Washington, DC, USA, 2012. [Google Scholar]

- ISaGRAF Technology. Available online: https://www.rockwellautomation.com/en-us/support/documentation/technical-data/isagraf_20190326-0743.html (accessed on 11 October 2023).

- Cavalieri, S.; Puglisi, G.; Scroppo, M.S.; Galvagno, L. Moving IEC 61131-3 Applications to a Computing Framework Based on CLR Virtual Machine. In Proceedings of the 2016 IEEE 21st International Conference on Emerging Technologies and Factory Automation (ETFA), Berlin, Germany, 6–9 September 2016. [Google Scholar] [CrossRef]

- Zhang, M.; Lu, Y.; Xia, T. The Design and Implementation of Virtual Machine System in Embedded SoftPLC System. In Proceedings of the 2013 International Conference on Computer Sciences and Applications, San Francisco, CA, USA, 23–25 October 2013. [Google Scholar] [CrossRef]

- Trybus, B. Development and Implementation of IEC 61131-3 Virtual Machine. Theor. Appl. Inform. 2011, 23, 21–35. [Google Scholar] [CrossRef][Green Version]

- Sadolewski, J.; Trybus, B. Compiler and virtual machine of a multiplatform control environment. Bull. Pol. Acad. Sci. Tech. Sci. 2022, 70, 140554. [Google Scholar] [CrossRef]

- Hubacz, M.; Trybus, B. Data Alignment on Embedded CPUs for Programmable Control Devices. Electronics 2022, 11, 2174. [Google Scholar] [CrossRef]

- CPDev-ControlProgramDeveloper. GitHub. Available online: https://github.com/CPDev-ControlProgramDeveloper (accessed on 11 October 2023).

- Sadolewski, J.; Trybus, B. Denotational Model and Implementation of Scalable Virtual Machine in CPDEV. In Proceedings of the Computer Science and Information Systems (FedCSIS), Federated Conference On 2022, Sofia, Bulgaria, 4–7 September 2022. [Google Scholar] [CrossRef]

- STMicroelectronics. Available online: https://www.st.com/content/st_com/en.html (accessed on 11 October 2023).

| Mnemonic | Meaning |

|---|---|

| JMP | Unconditional jump |

| JZ | Conditional jump |

| JR | Unconditional relative jump |

| CALB | Subroutine call |

| RETURN | Return from subroutine |

| MCD | Initialize data |

| MEMCP | Copy memory block |

| FPAT | Fill memory block |

| Type | Model |

|---|---|

| Microprocessors | Texas Instruments AM5729 (2x Cortex-A15) Broadcom BCM2712 (4x Cortex-A76) |

| Microcontrollers | STMicroelectronics STM32H755 (1x Cortex-M7 + 1x Cortex-M4) Raspberry Pi Foundation RP2040 (2x Cortex-M0+) |

| Hybrid | STMicroelectronics STM32MP1 (1x/2x Cortex-A7 + 1x Cortex-M4) NXP Semiconductors i.MX.8M (4x Cortex-A53 + 1x Cortex-M4) |

| Project | IN1 | CNT | RST |

|---|---|---|---|

| Project 1 | WRITE | WRITE | READ |

| Project 2 | READ | READ | WRITE |

| Test | Precycle | Cycle | Postcycle | |

|---|---|---|---|---|

| Example—Section 6.1 | Project 1 | 0.0074 | 3.28 | 0.0085 |

| Project2 | 0.0101 | 2.53 | 0.0103 | |

| 100 DWORD | compact | 1.49 | 163.97 | 1.49 |

| random | 13.37 | 163.89 | 14.19 | |

| 200 DWORD | compact | 2.93 | 327.11 | 2.96 |

| random | 26.73 | 327.13 | 28.35 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hubacz, M.; Trybus, B. Dual-Core PLC for Cooperating Projects with Software Implementation. Electronics 2023, 12, 4730. https://doi.org/10.3390/electronics12234730

Hubacz M, Trybus B. Dual-Core PLC for Cooperating Projects with Software Implementation. Electronics. 2023; 12(23):4730. https://doi.org/10.3390/electronics12234730

Chicago/Turabian StyleHubacz, Marcin, and Bartosz Trybus. 2023. "Dual-Core PLC for Cooperating Projects with Software Implementation" Electronics 12, no. 23: 4730. https://doi.org/10.3390/electronics12234730

APA StyleHubacz, M., & Trybus, B. (2023). Dual-Core PLC for Cooperating Projects with Software Implementation. Electronics, 12(23), 4730. https://doi.org/10.3390/electronics12234730