Legalized Routing Algorithm Based on Linear Programming

Abstract

1. Introduction

1.1. Previous Work

1.2. Our Contributions

- To simplify the complexity of the detailed routing problem, a solution to realize the wiring using a prescribed topology is proposed, and a specific wiring model is established based on complex design rules;

- Integer linear programming is used to realize the mathematical modeling of detailed wiring problems, and a legalized wiring algorithm based on linear programming is proposed to effectively realize the legalized wiring function of grid pin array (GPA) and staggered pin array (SPA) devices;

- The heuristic strategy of multi-line routing is used to design and implement a detailed routing algorithm, further optimizing the routing quality and the time complexity.

2. Model Building

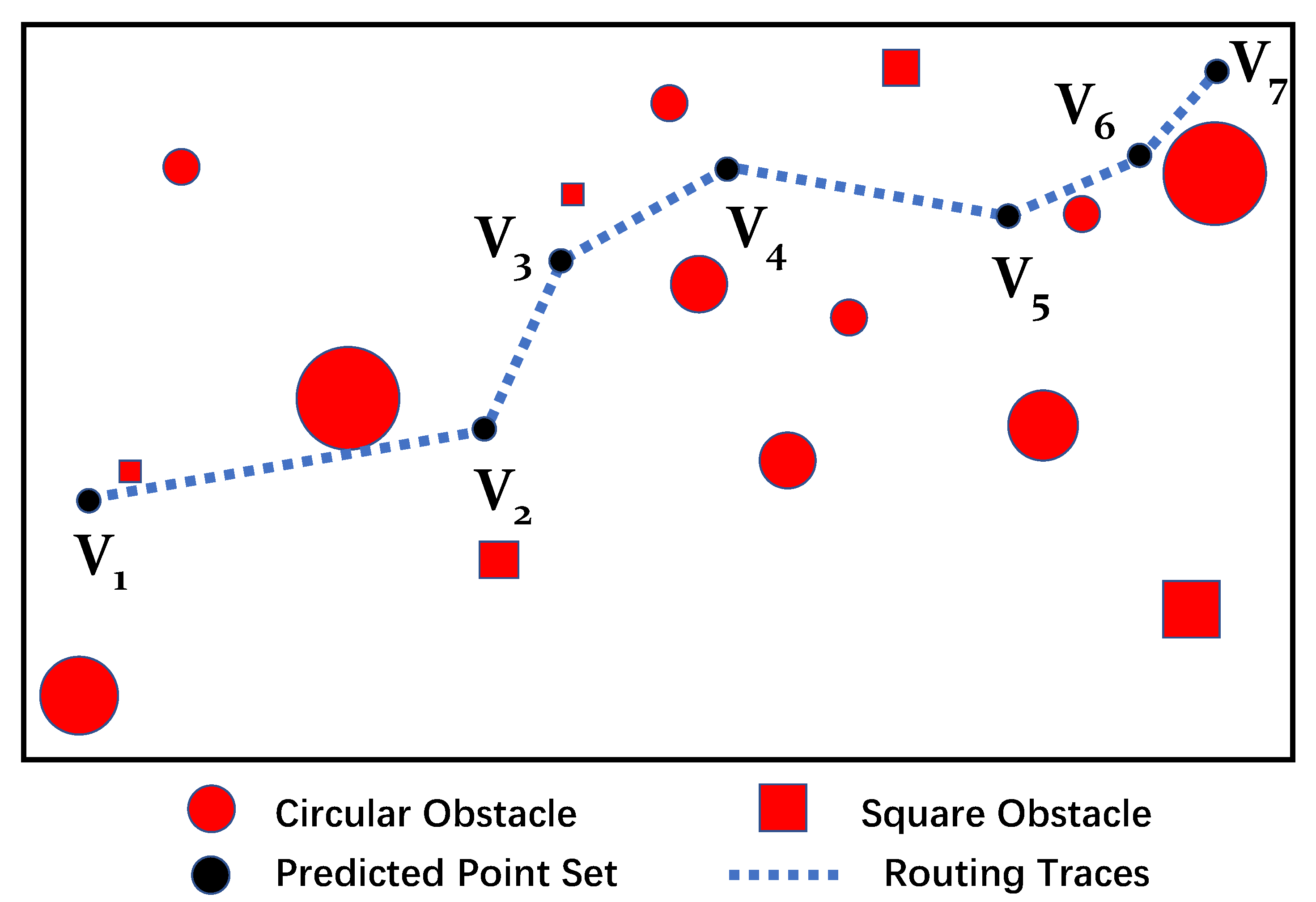

2.1. Problem Statement

- Spacing constraints: The distance between the routing trace and the obstacle is greater than or equal to the minimum spacing value;

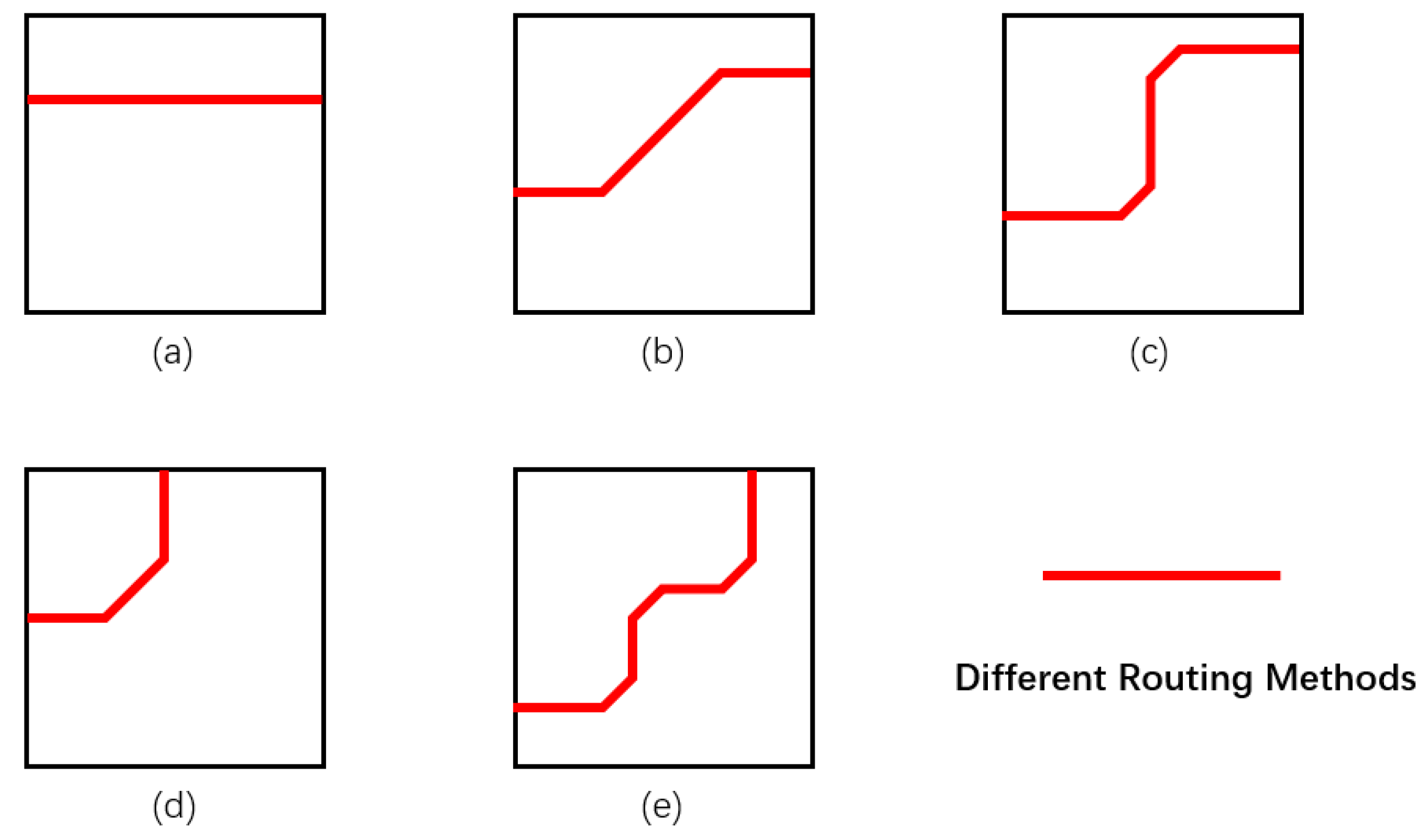

- Routing direction and angle constraint: The angle between the routing direction and the x-axis must be a multiple of 45°, and the routing direction can only be changed by 135°;

- Minimum line length constraint: The shortest line length determined by two points must be greater than or equal to the line width.

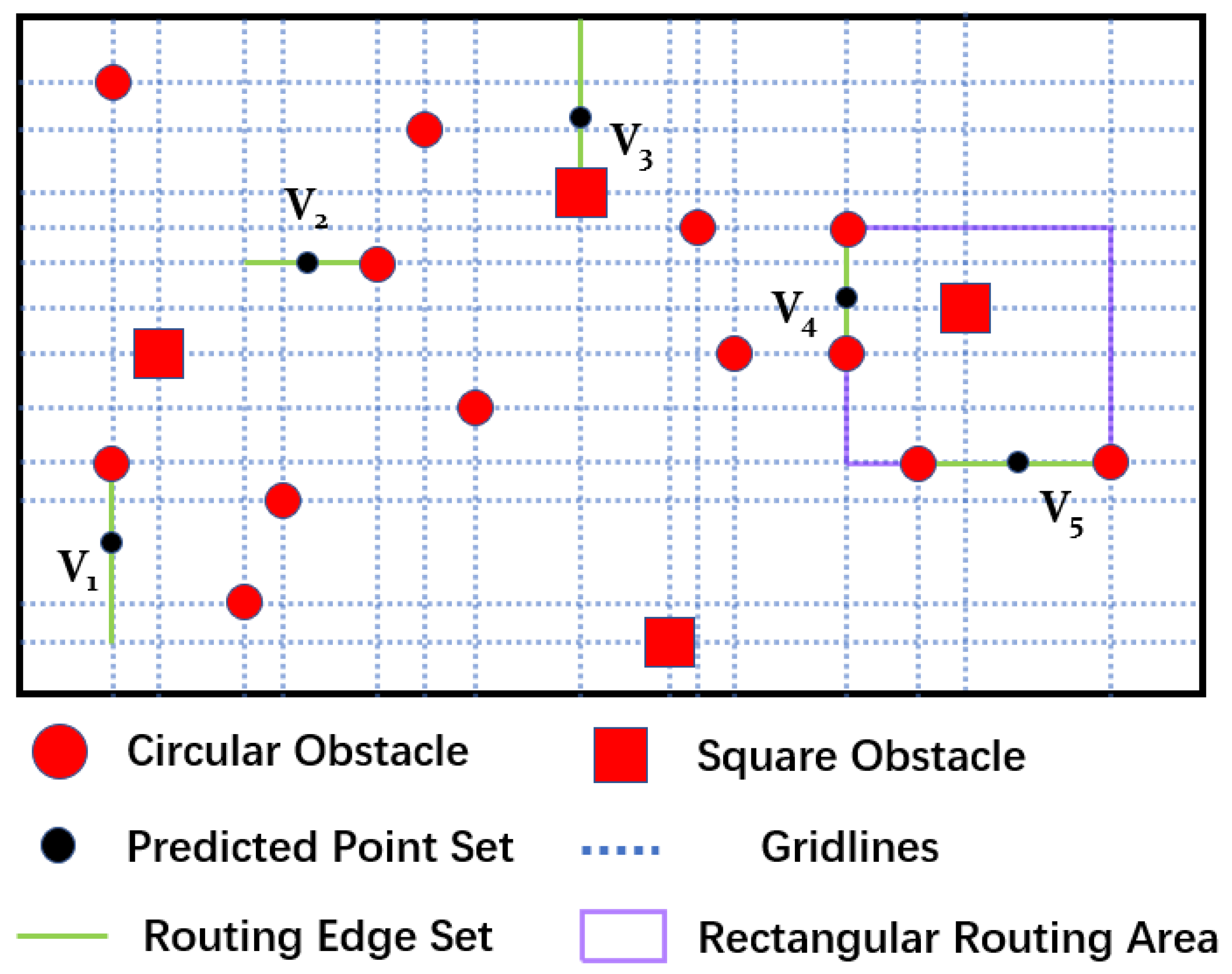

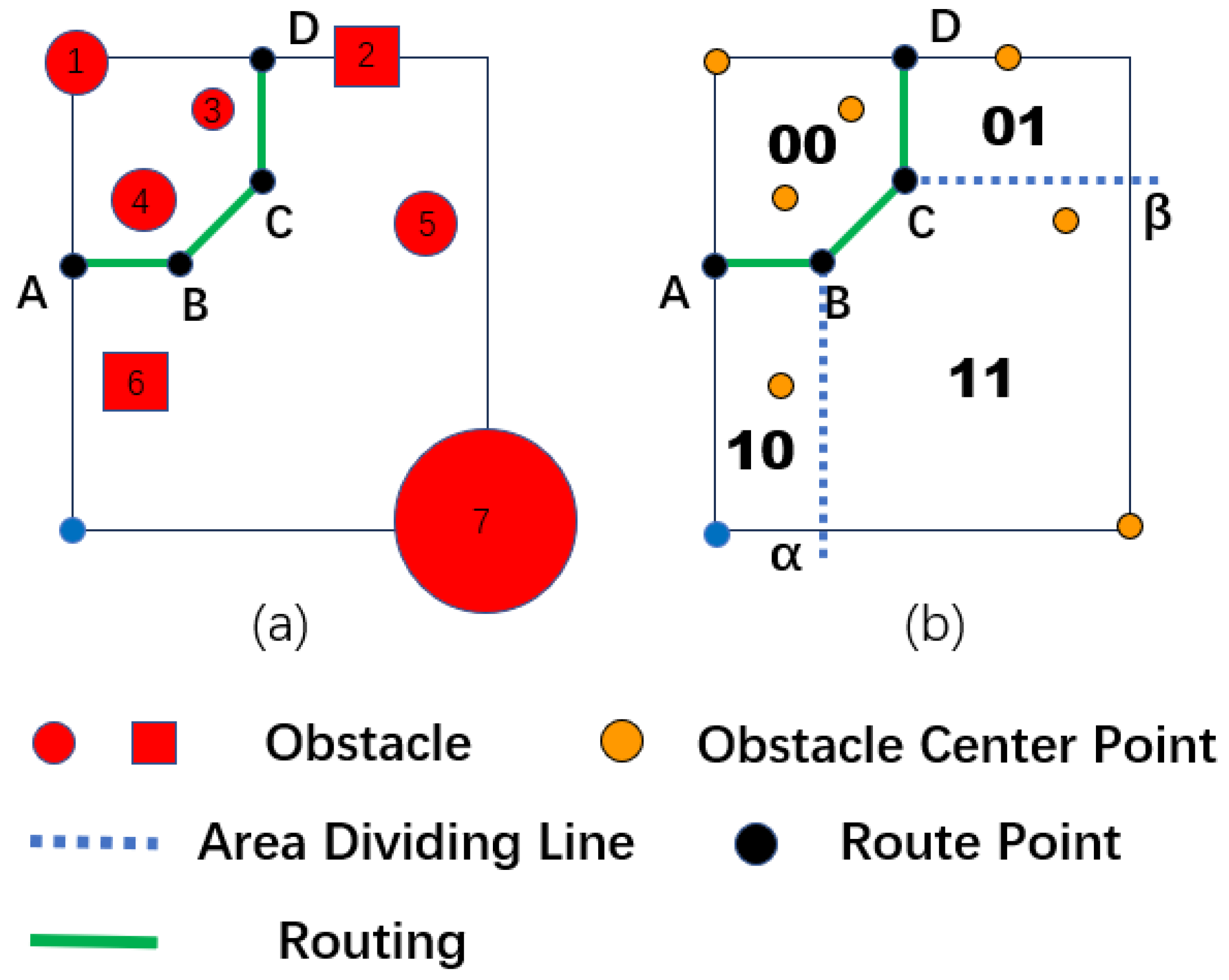

2.2. Routing Topology

3. Linear Programming Modeling

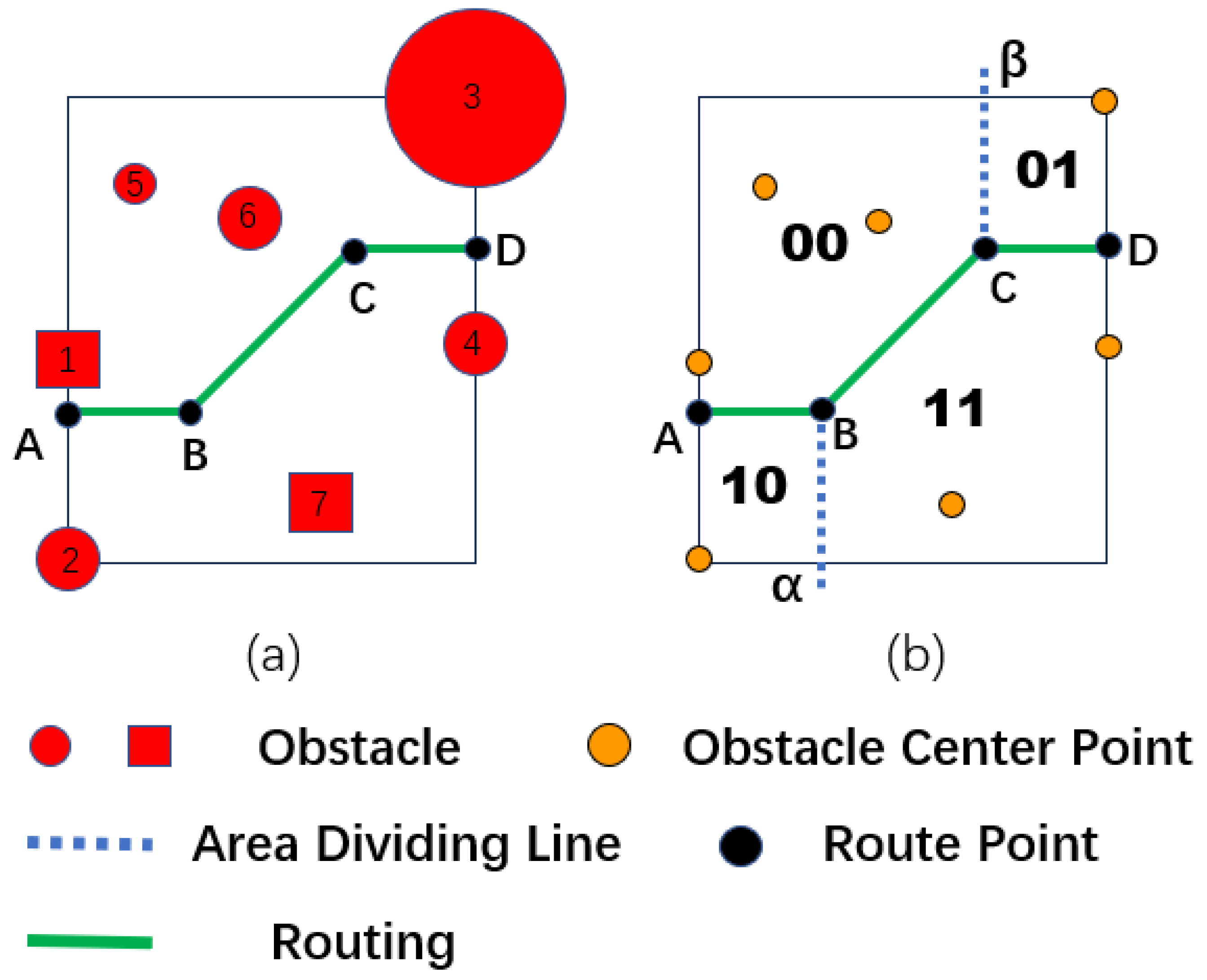

3.1. Composition and Routing Model Establishment

3.2. Integer Linear Programming

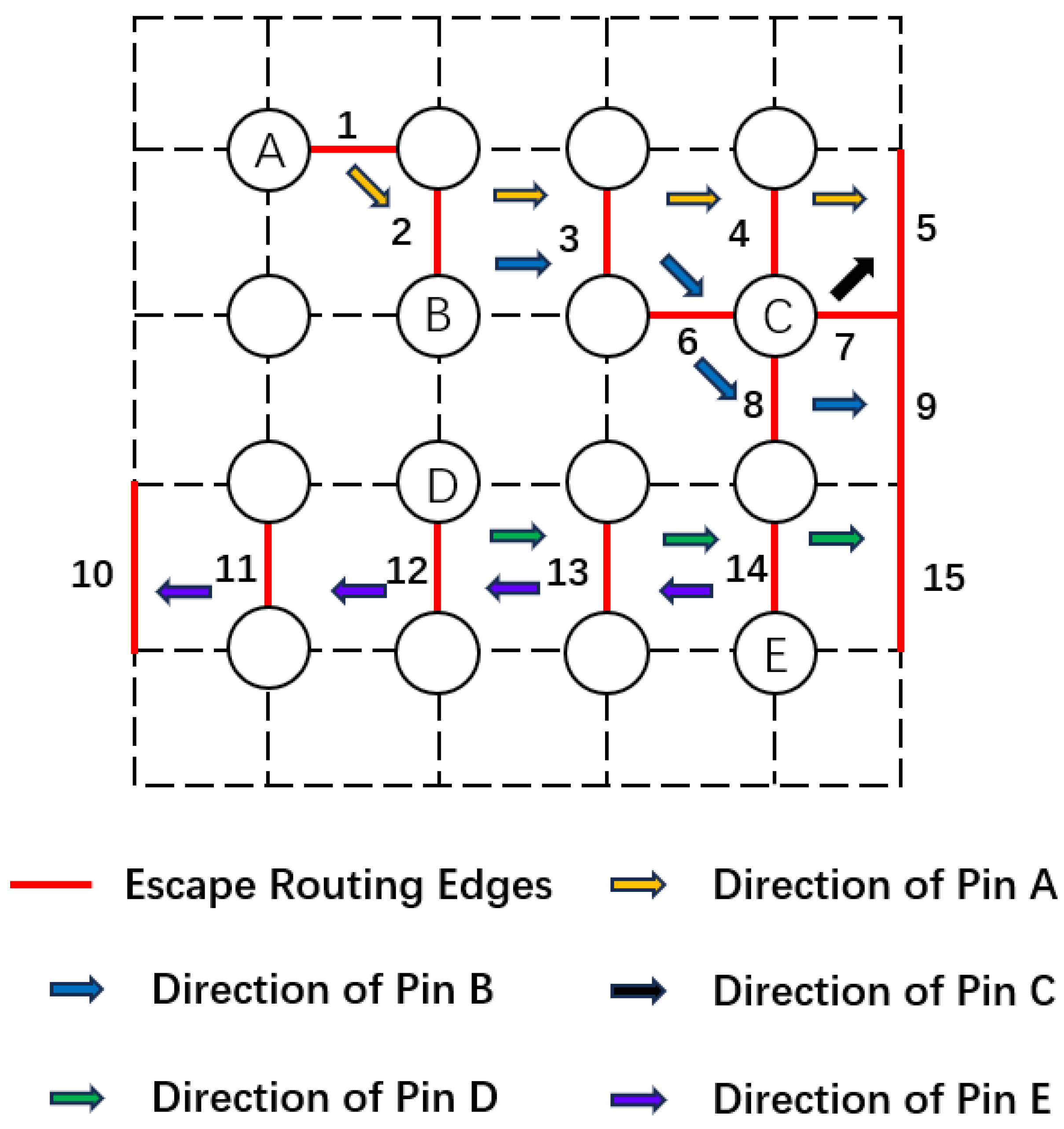

4. Detailed Routing Algorithm

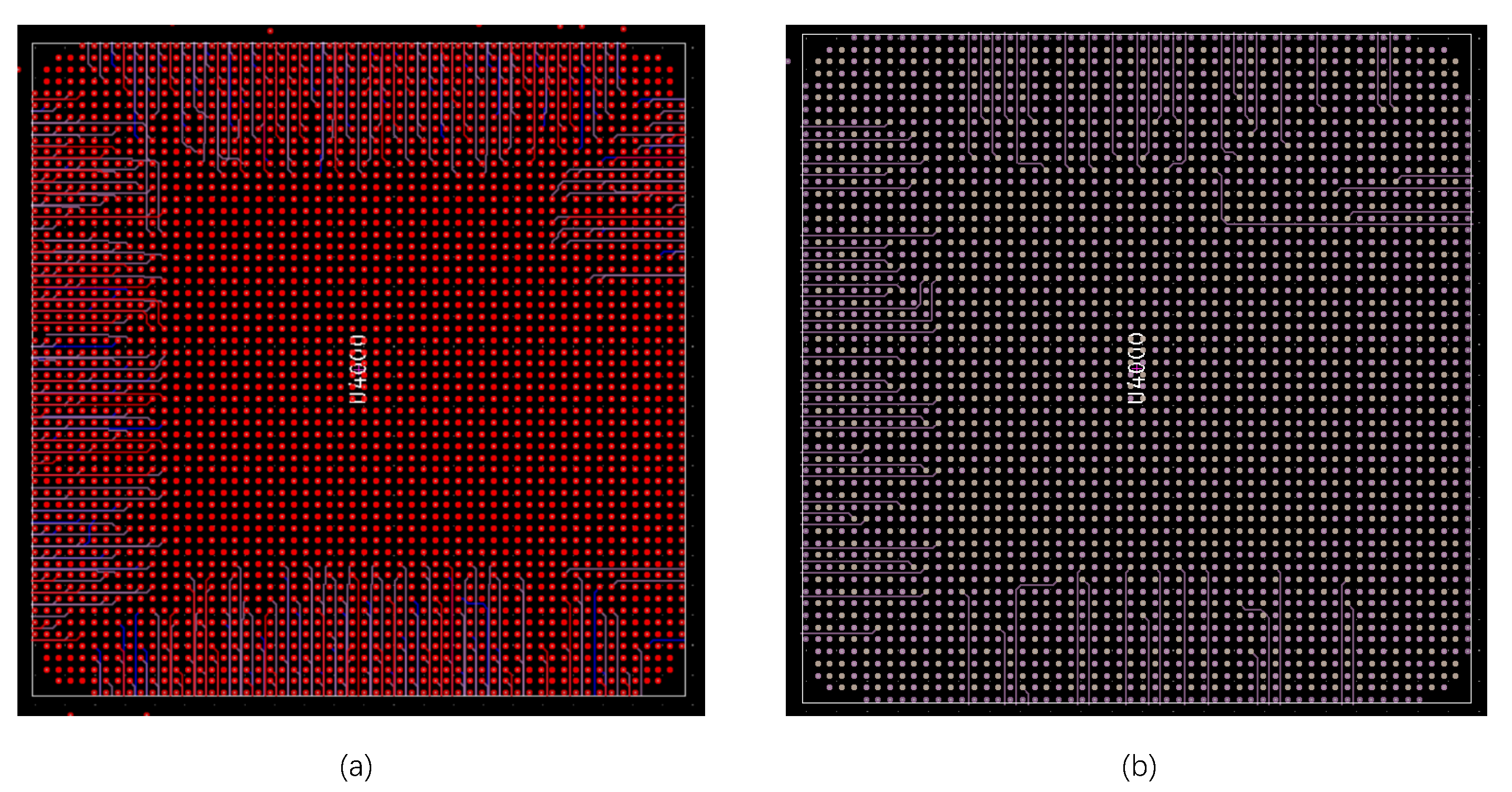

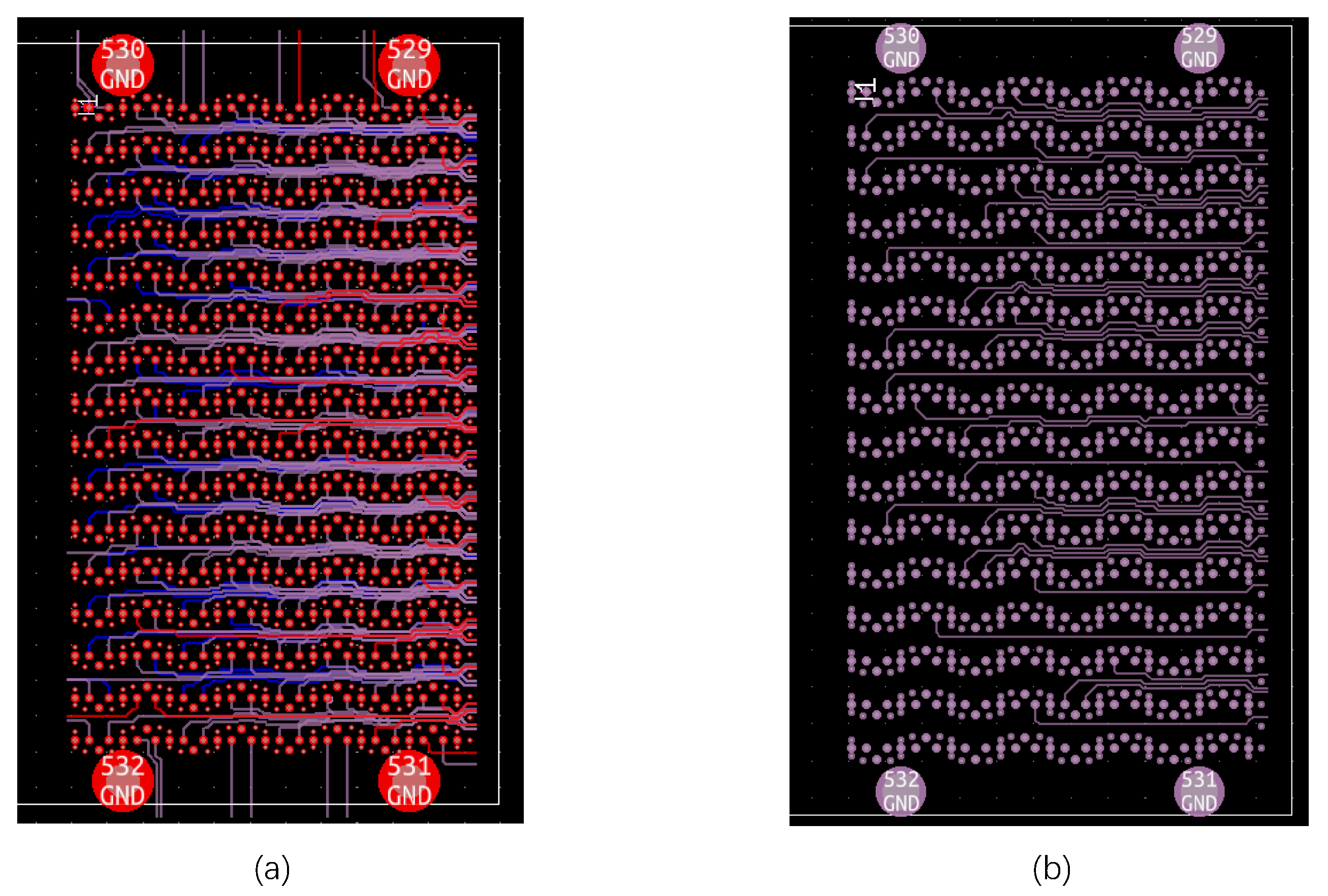

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Yan, T.; Wong, M.D.F. Recent research development in PCB layout. In Proceedings of the 2010 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 7–11 November 2010; pp. 398–403. [Google Scholar]

- Shamkhalichenar, H.; Bueche, C.J.; Choi, J.-W. Printed Circuit Board (PCB) Technology for Electrochemical Sensors and Sensing Platforms. Biosensors 2020, 10, 159. [Google Scholar] [CrossRef] [PubMed]

- Lavagno, L.; Scheffer, L.; Martin, G. (Eds.) EDA for IC Implementation, Circuit Design, and Process Technology, 1st ed.; CRC Press: Boca Raton, FL, USA, 2006. [Google Scholar]

- Ho, Y.K.; Lee, H.C.; Chang, Y.W. Escape Routing for Staggered-Pin-Array PCBs. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2013, 9, 1347–1356. [Google Scholar]

- Shin, H.; Sangiovannivincentelli, A. A detailed router based on incremental routing modifications-mighty. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1987, 11, 942–955. [Google Scholar] [CrossRef]

- Guruswamy, M.; Wong, D.F. Echelon: A multilayer detailed area router. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1996, 9, 1126–1136. [Google Scholar] [CrossRef]

- Tzeng, P.S.; Sequin, C.H. Codar: A congestion-directed general area router. In Proceedings of the [1988] IEEE International Conference on Computer-Aided Design (ICCAD-89) Digest of Technical Papers, Santa Clara, CA, USA, 7–10 November 1988; pp. 30–33. [Google Scholar]

- Fang, J.W.; Lin, I.J.; Chang, Y.W.; Wang, J.H. A Network-Flow-Based RDL Routing Algorithmz for Flip-Chip Design. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2007, 8, 1417–1429. [Google Scholar] [CrossRef]

- Ma, Q.; Kong, H.; Wong, M.D.F.; Young, E.F.Y. A provably good approximation algorithm for Rectangle Escape Problem with application to PCB routing. In Proceedings of the 16th Asia and South Pacific Design Automation Conference (ASP-DAC 2011), Yokohama, Japan, 25–28 January 2011; pp. 843–848. [Google Scholar]

- Chen, C.D.; Lin, D.S.; Wei, R.S.; Liu, Q.H.; Zhu, Z.R.; Chen, J.L. Efficient Global Optimization for Large Scaled Ordered Escape Routing. In Proceedings of the 28th Asia and South Pacific Design Automation Conference (ASP-DAC), Tokyo, Japan, 16–19 January 2023; pp. 535–540. [Google Scholar]

- Lin, S.T.; Wang, H.H.; Kuo, C.Y.; Chen, Y.; Li, Y.L. A complete PCB routing methodology with concurrent hierarchical routing. In Proceedings of the 58th ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 5–9 December 2021; pp. 1141–1146. [Google Scholar]

- Chen, Z.Y.; Ji, W.Q.; Peng, Y.H.; Chen, D.T.; Liu, M.Y.; Yao, H.L. Machine Learning Based Acceleration Method for Ordered Escape Routing. In Proceedings of the 2021 on Great Lakes Symposium on VLSI (GLSVLSI ’21), New York, NY, USA, 22–25 June 2021; pp. 365–370. [Google Scholar]

- Yan, T.; Wong, M.D.F. A correct network flow model for escape routing. In Proceedings of the 2009 46th ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 26–31 July 2009; pp. 332–335. [Google Scholar]

- Yan, T.; Wong, M.D.F. Correctly Modeling the Diagonal Capacity in Escape Routing. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2012, 2, 285–293. [Google Scholar] [CrossRef]

- Luo, L.J.; Wong, M.D.F. Ordered escape routing based on Boolean satisfiability. In Proceedings of the 2008 Asia and South Pacific Design Automation Conference, Seoul, Republic of Korea, 21–24 March 2008; pp. 244–249. [Google Scholar]

- Jiao, F.; Dong, S. Ordered escape routing for grid pin array based on min-cost multi-commodity flow. In Proceedings of the 21st Asia and South Pacific Design Automation Conference (ASP-DAC), Macao, China, 25–28 January 2016; pp. 384–389. [Google Scholar]

- Liao, Z.P.; Dong, S.Q. A Constraint-Driven Compact Model with Partition Strategy for Ordered Escape Routing. In Proceedings of the 2020 on Great Lakes Symposium on VLSI (GLSVLSI ’20), New York, NY, USA, 7–9 September 2020; pp. 393–398. [Google Scholar]

- Tang, P.S. VLSI CAD Theory and Method; Fudan University Press: Shanghai, China, 1990; pp. 262–300. [Google Scholar]

- Gonçalves, S.M.M.; Rosa, L.S.; Marques, F.S. DRAPS: A Design Rule Aware Path Search Algorithm for Detailed Routing. IEEE Trans. Circuits Syst. II Express Briefs 2020, 7, 1239–1243. [Google Scholar] [CrossRef]

- Jia, X.T.; Cai, Y.C.; Zhou, Q.; Chen, G.; Li, Z.Y.; Li, Z.W. MCFRoute: A detailed router based on multi-commodity flow method. In Proceedings of the 2014 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 2–6 November 2014; pp. 397–404. [Google Scholar]

- Jia, X.T.; Cai, Y.C.; Zhou, Q.; Yu, B. A Multicommodity Flow-Based Detailed Router With Efficient Acceleration Techniques. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 1, 217–230. [Google Scholar] [CrossRef]

- Kahng, A.B.; Wang, L.T.; Xu, B.Q. TritonRoute: An Initial Detailed Router for Advanced VLSI Technologies. In Proceedings of the 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 5–8 November 2018; pp. 1–8. [Google Scholar]

- Li, Y.; Zhang, H.; Liang, X.; Huang, B. Event-Triggered-Based Distributed Cooperative Energy Management for Multienergy Systems. IEEE Trans. Ind. Inform. 2019, 8, 2008–2022. [Google Scholar] [CrossRef]

- Gurobi Optimizer. Available online: http://www.gurobi.com (accessed on 10 July 2023).

| Designs | Pins | Obstacles | Devices | Layers | Nets |

|---|---|---|---|---|---|

| Case 1 | 248 | 299 | 2 | 2 | 23 |

| Case 2 | 650 | 835 | 2 | 3 | 130 |

| Case 3 | 820 | 1069 | 3 | 8 | 249 |

| Case 4 | 2207 | 2269 | 7 | 8 | 481 |

| Case 5 | 3676 | 4433 | 3 | 7 | 512 |

| Case 6 | 6004 | 6495 | 5 | 14 | 837 |

| Case 7 | 11,379 | 12,001 | 10 | 16 | 997 |

| Case 8 | 100K+ | 100K+ | 22 | 16 | 7344 |

| Designs | Trial Backtracking | Linear Programming | Detailed Routing | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Length | Time (s) | Ratio (%) | DRVs | Length | Time (s) | Ratio (%) | DRVs | Length | Time (s) | Ratio (%) | DRVs | |

| Case 1 | 797 | 0.9 | 100 | 0 | 693 | 0.5 | 100 | 0 | 675 | 0.3 | 100 | 0 |

| Case 2 | 8100 | 3.6 | 82 | 0 | 7390 | 2.1 | 100 | 0 | 7301 | 0.5 | 100 | 0 |

| Case 3 | 110,395 | 5.5 | 77 | 0 | 13,496 | 3.9 | 100 | 0 | 13,021 | 0.9 | 100 | 0 |

| Case 4 | 27,765 | 9.3 | 53 | 0 | 45,348 | 8.5 | 100 | 0 | 44,315 | 1.7 | 100 | 0 |

| Case 5 | 22,230 | 10.9 | 38 | 0 | 53,966 | 9.3 | 100 | 0 | 50,118 | 2 | 100 | 0 |

| Case 6 | 36,952 | 18.6 | 19 | 0 | 100,999 | 20.7 | 100 | 0 | 98,632 | 2.4 | 100 | 0 |

| Case 7 | 42,994 | 21.1 | 15 | 0 | 130,064 | 25.5 | 100 | 0 | 127,744 | 2.8 | 100 | 0 |

| Case 8 | — | — | — | — | — | — | — | — | 462,895 | 21.6 | 100 | 0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, C.; Tong, X.; Liu, Q.; Chen, J.; Lin, Z. Legalized Routing Algorithm Based on Linear Programming. Electronics 2023, 12, 4338. https://doi.org/10.3390/electronics12204338

Chen C, Tong X, Liu Q, Chen J, Lin Z. Legalized Routing Algorithm Based on Linear Programming. Electronics. 2023; 12(20):4338. https://doi.org/10.3390/electronics12204338

Chicago/Turabian StyleChen, Chuandong, Xin Tong, Qinghai Liu, Jiarui Chen, and Zhifeng Lin. 2023. "Legalized Routing Algorithm Based on Linear Programming" Electronics 12, no. 20: 4338. https://doi.org/10.3390/electronics12204338

APA StyleChen, C., Tong, X., Liu, Q., Chen, J., & Lin, Z. (2023). Legalized Routing Algorithm Based on Linear Programming. Electronics, 12(20), 4338. https://doi.org/10.3390/electronics12204338