An Asymmetrical 19-Level Inverter with a Reduced Number of Switches and Capacitors

Abstract

1. Introduction

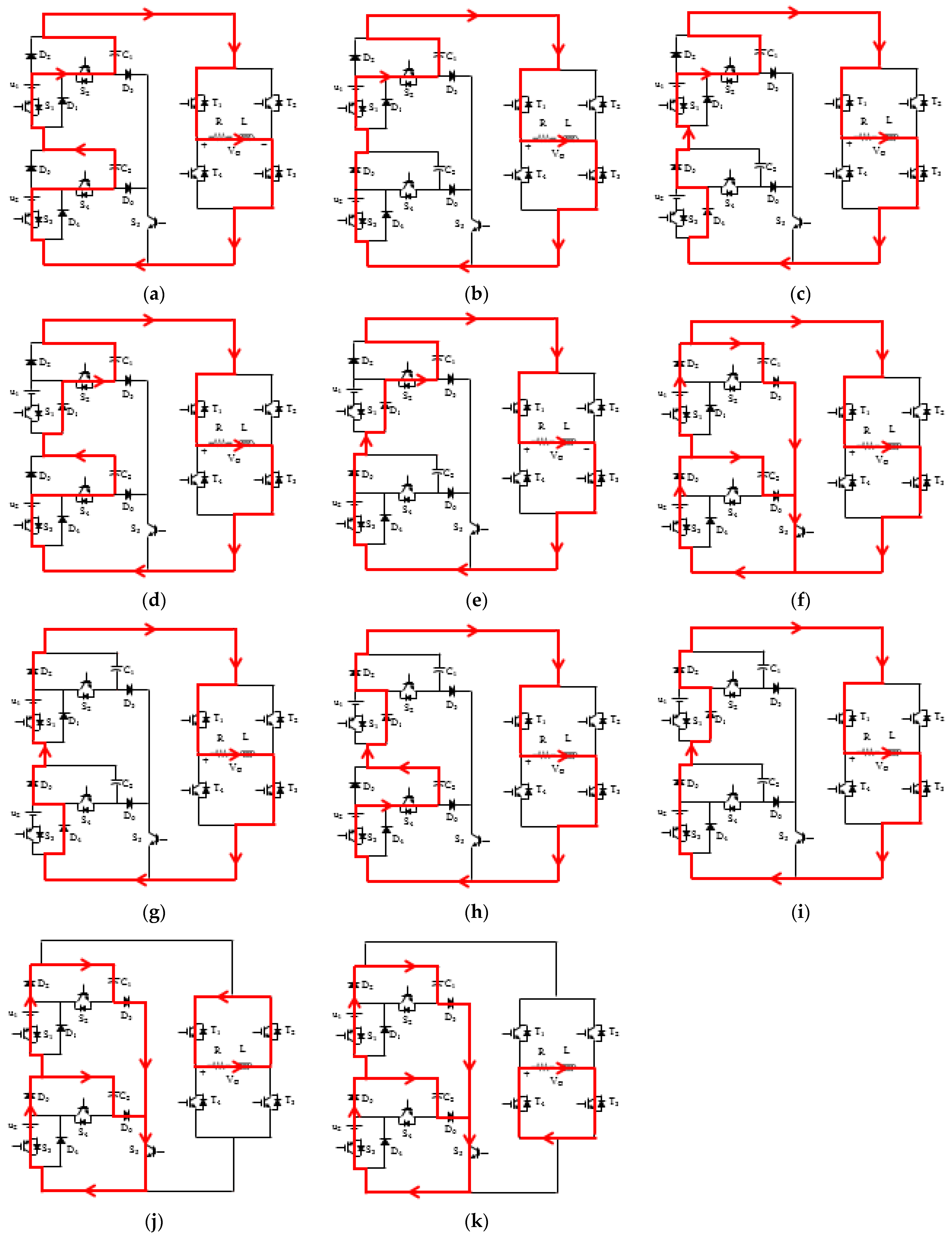

2. Proposed 19-Level Inverter

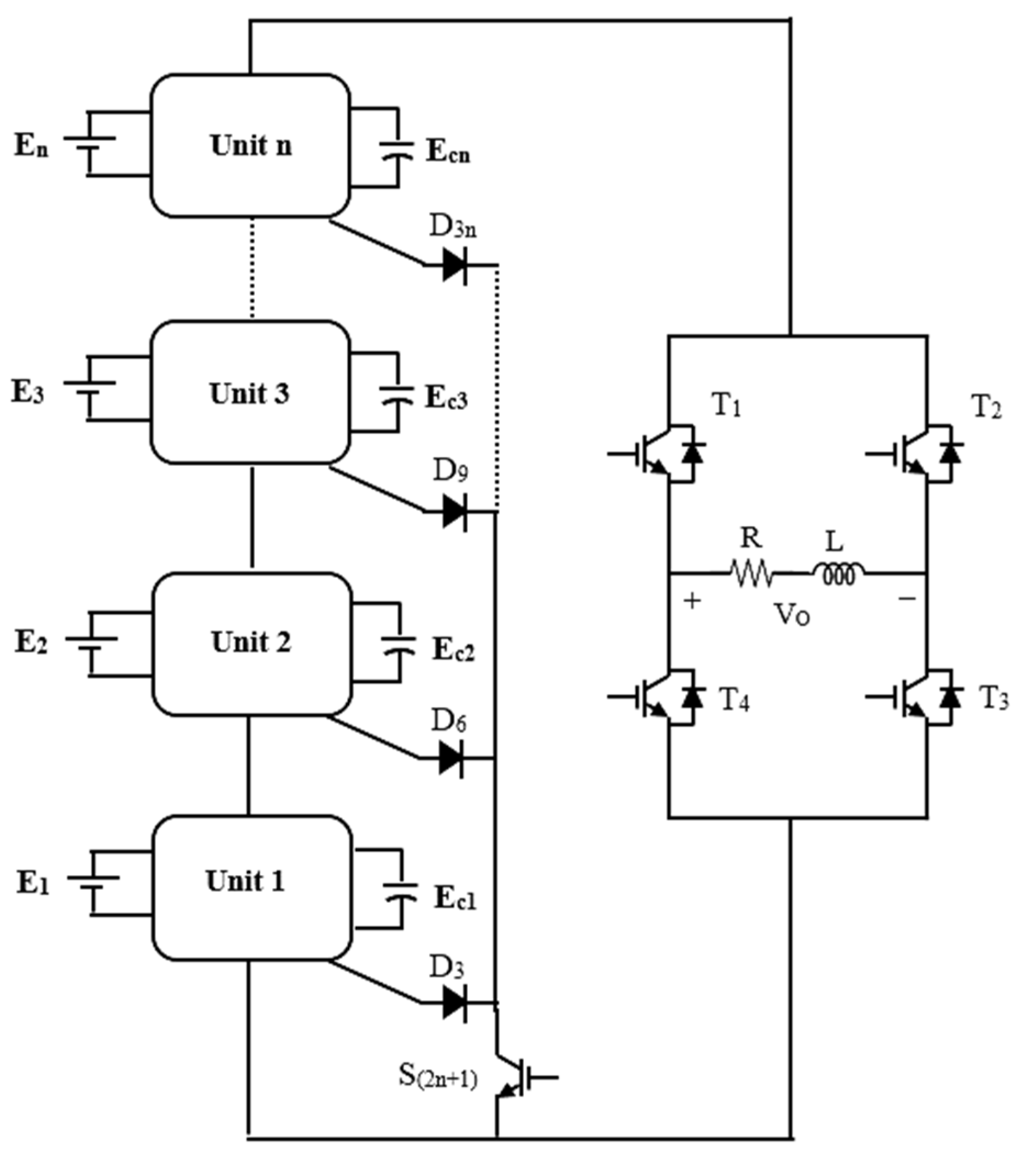

3. The Proposed Generalized Multilevel Inverter

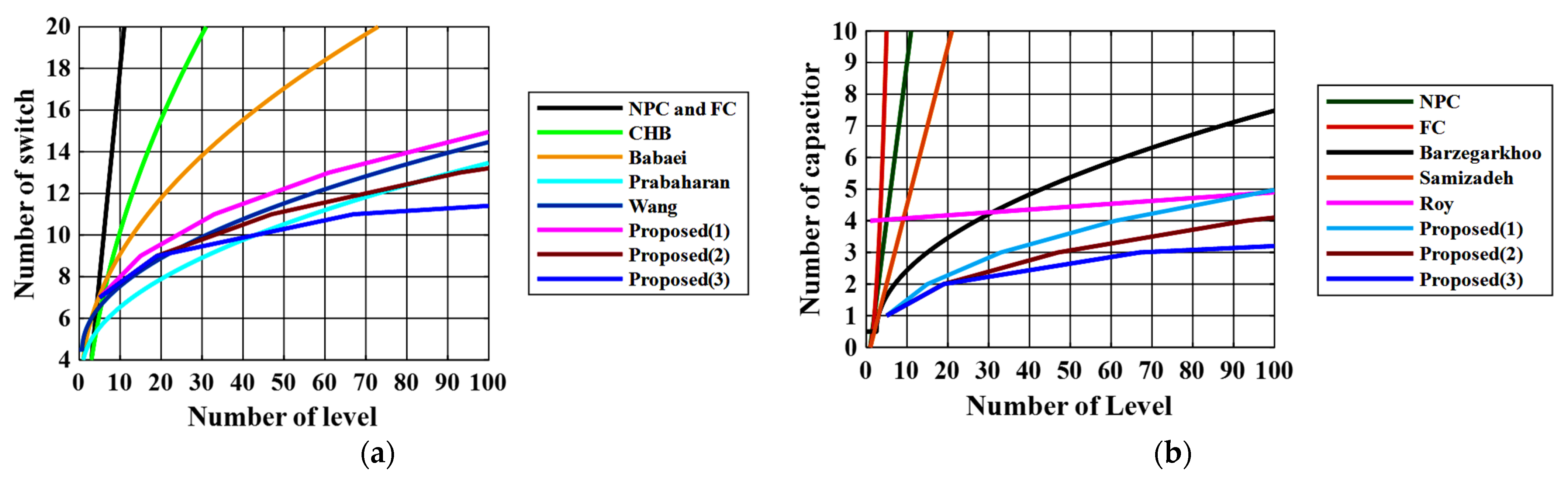

4. Comparison of the Proposed Multilevel Inverter with Other Topologies

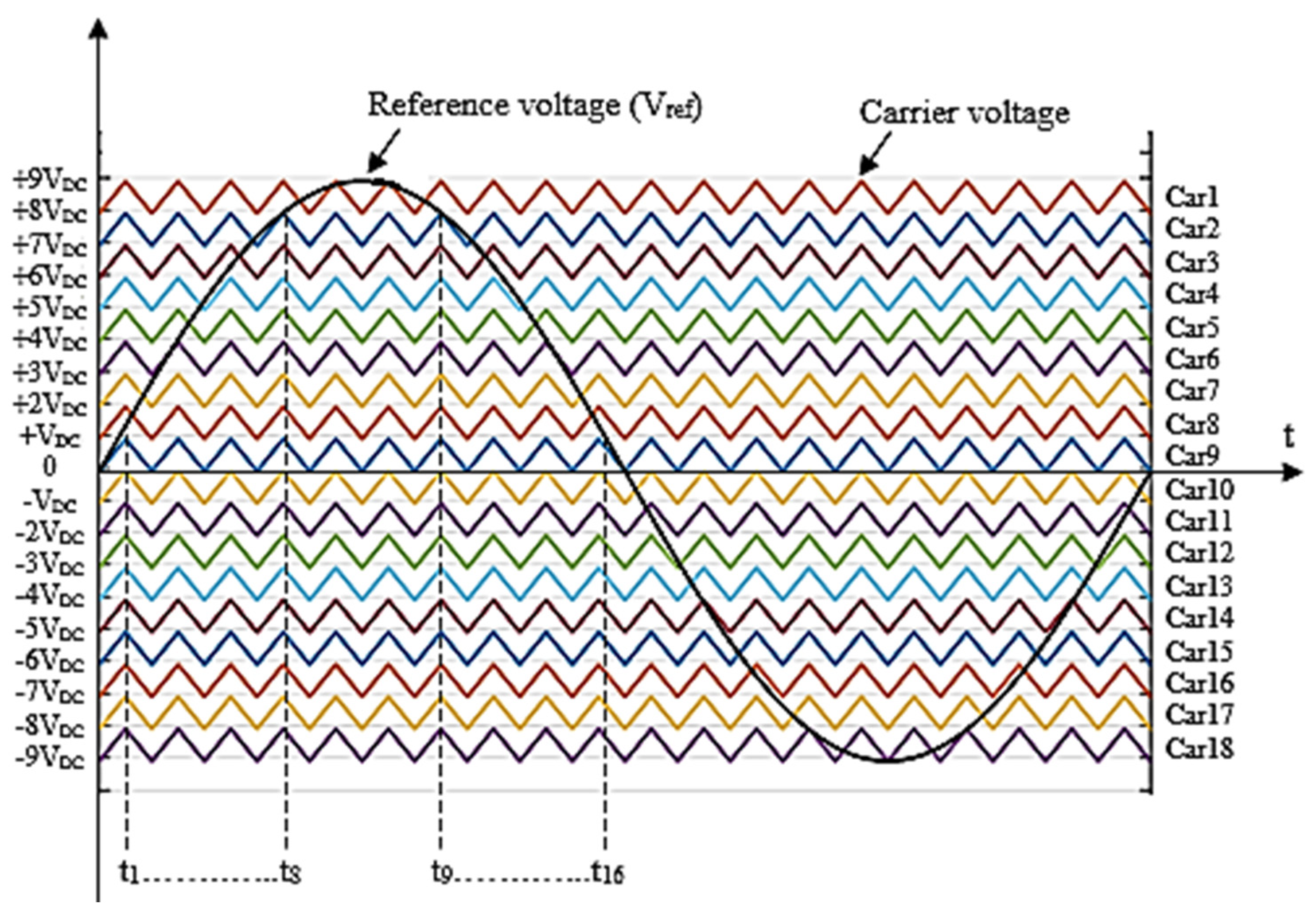

5. Multi-Carrier Pulse Width Modulation Technique

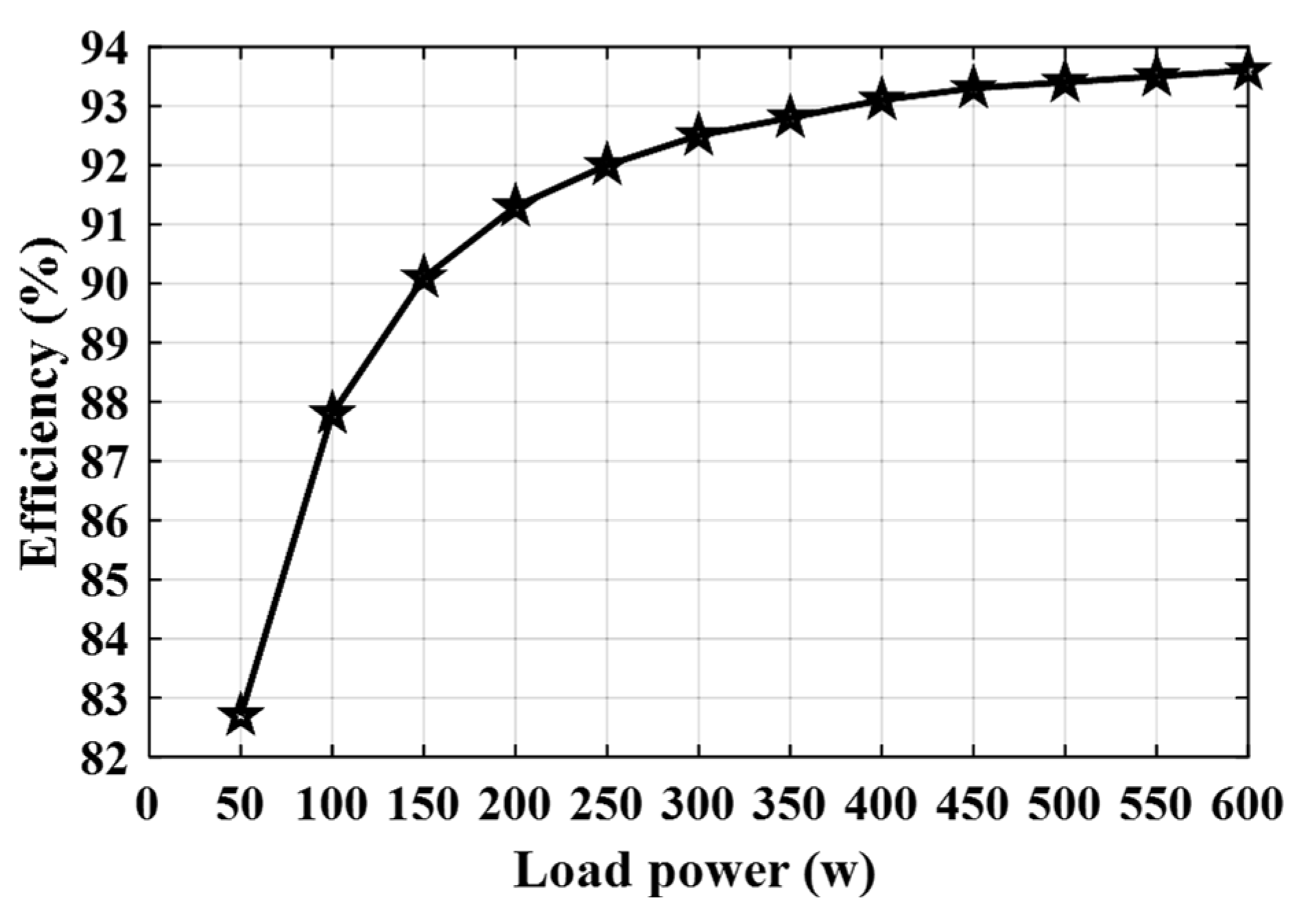

6. Calculation of Losses and Efficiency

6.1. The Capacitor Charging Losses

6.2. The Switching Losses

6.3. The Conducting Losses

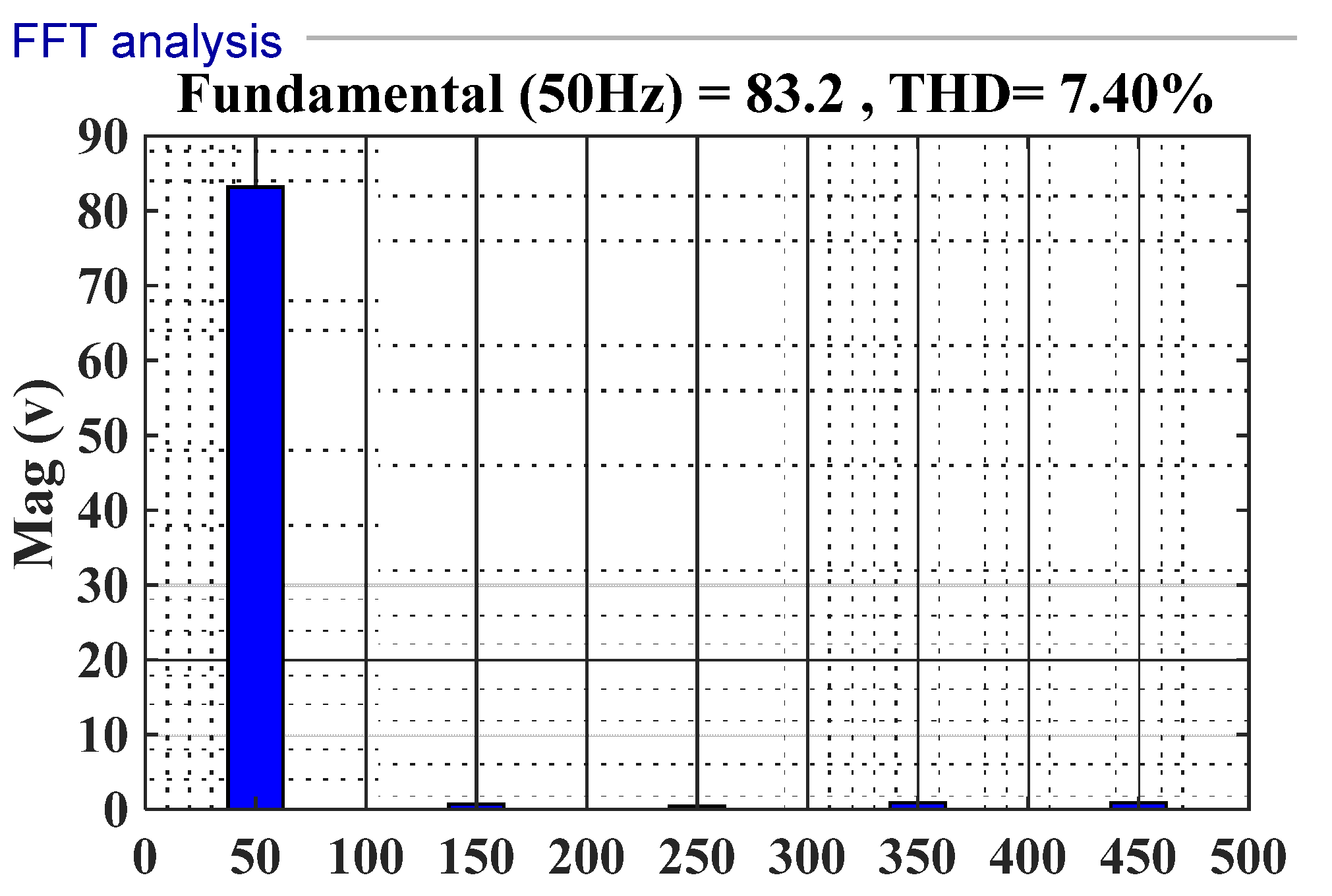

7. Simulation and Experimental Results

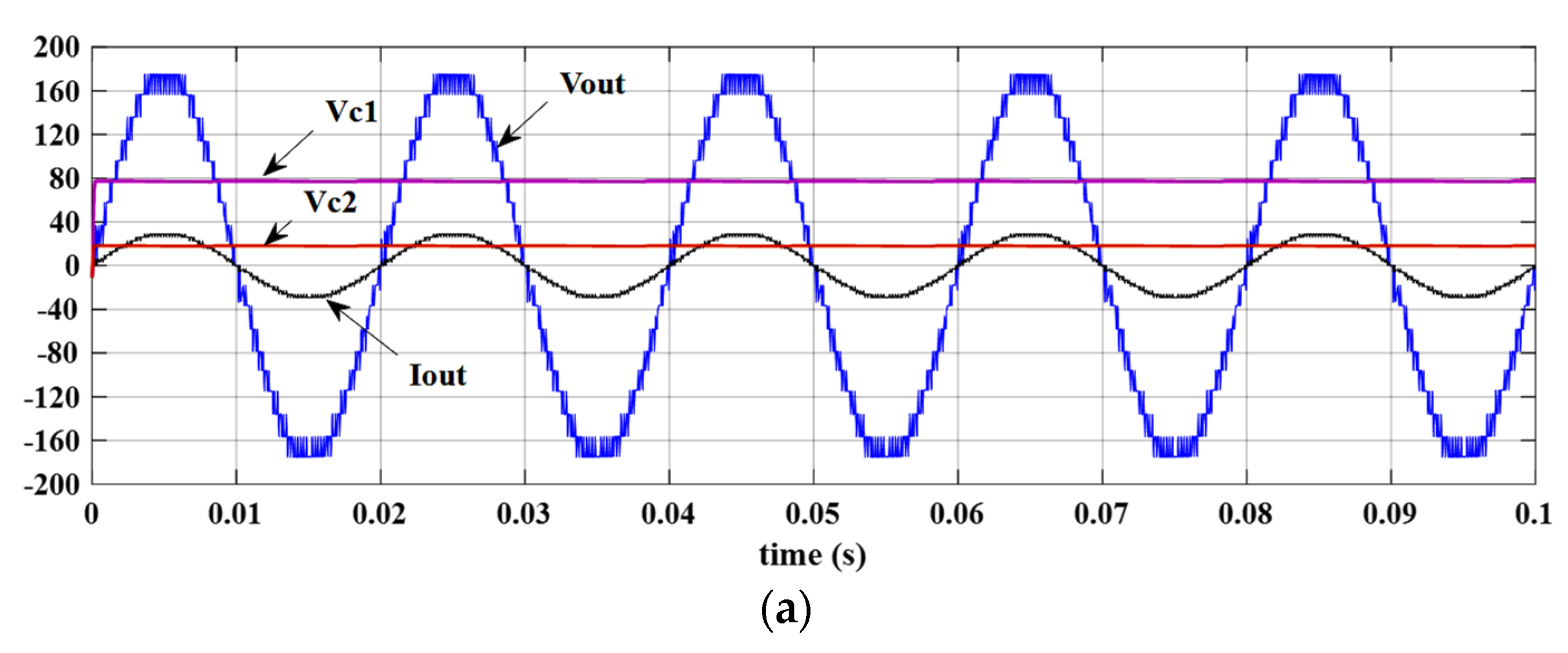

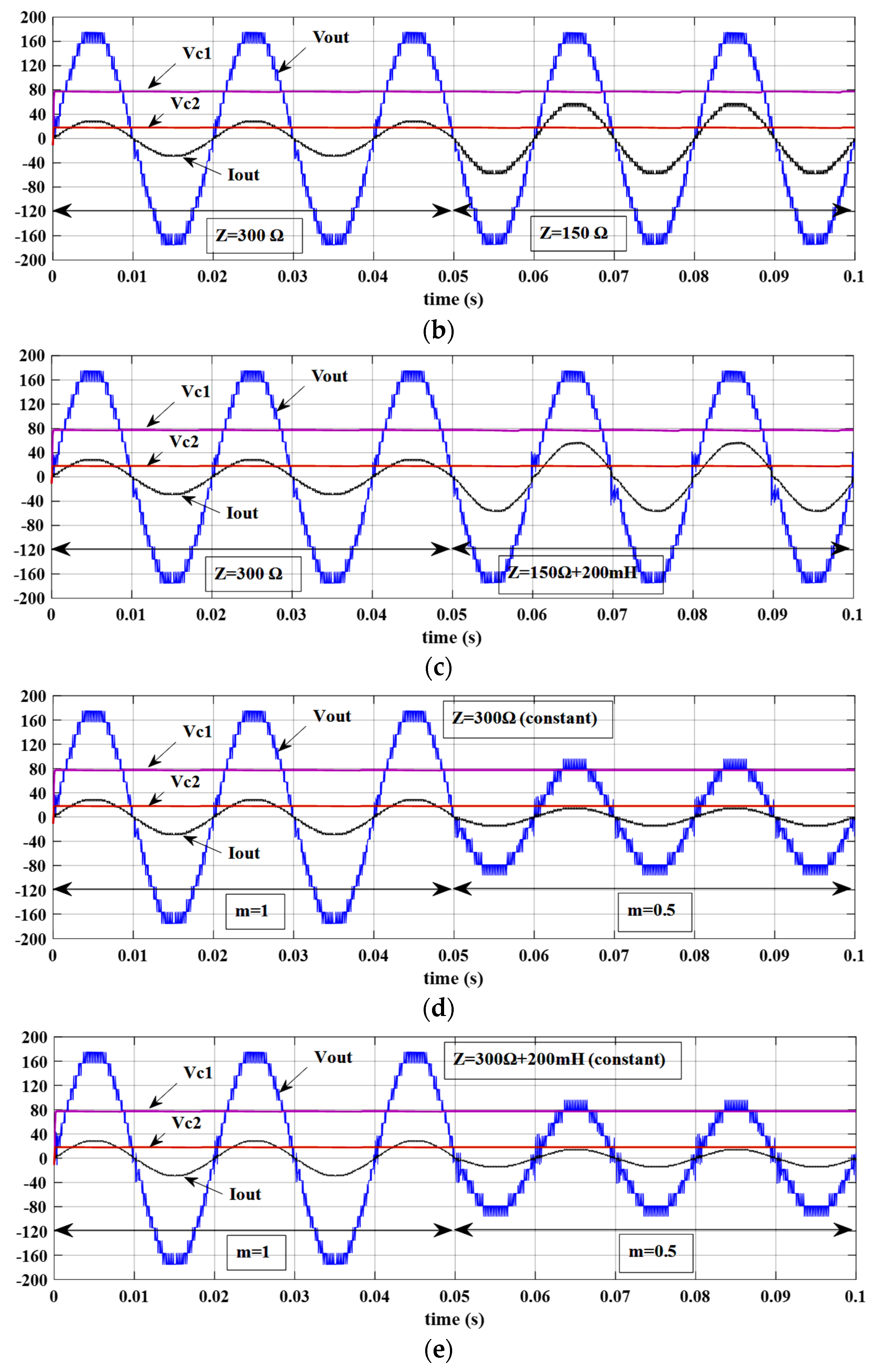

7.1. Simulation Results

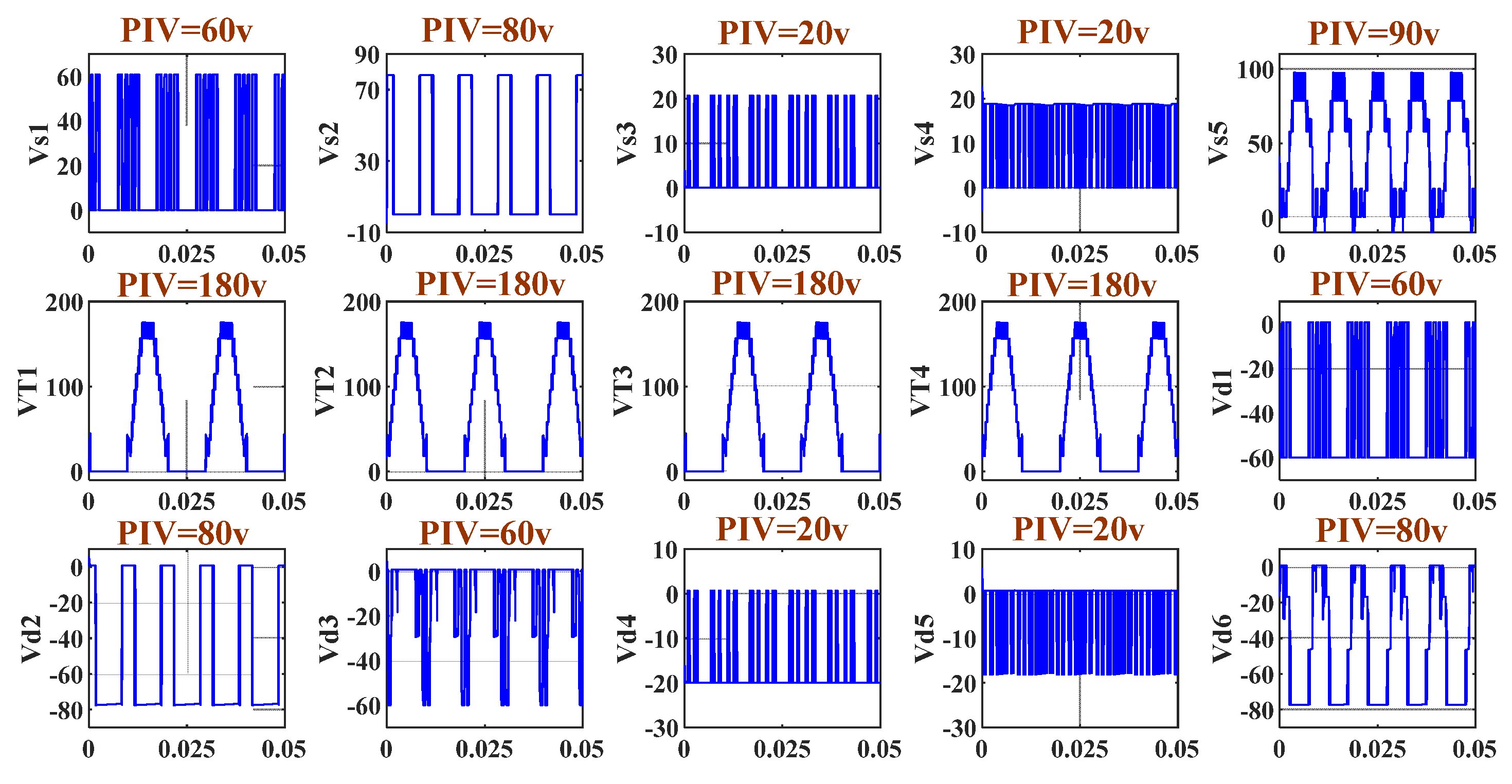

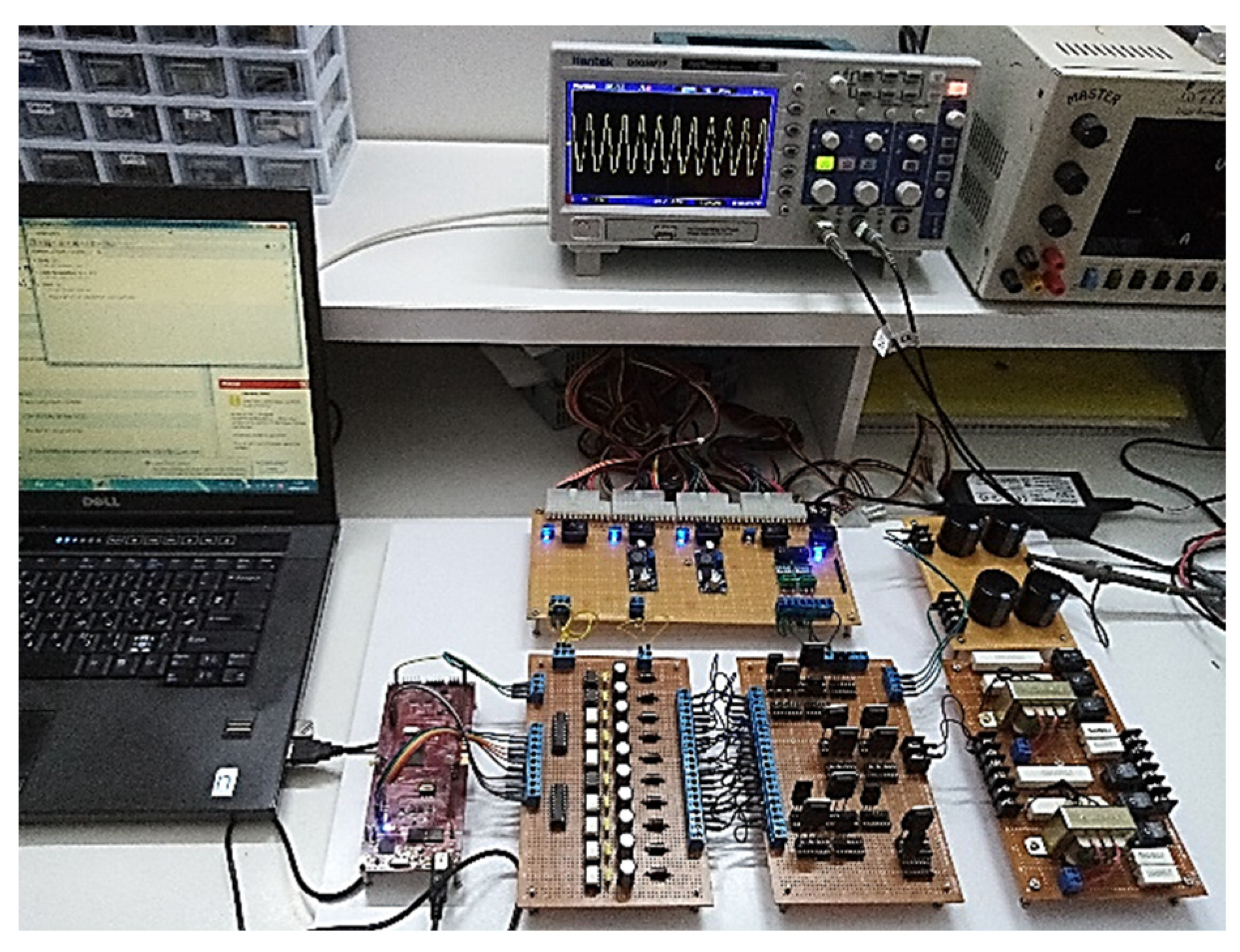

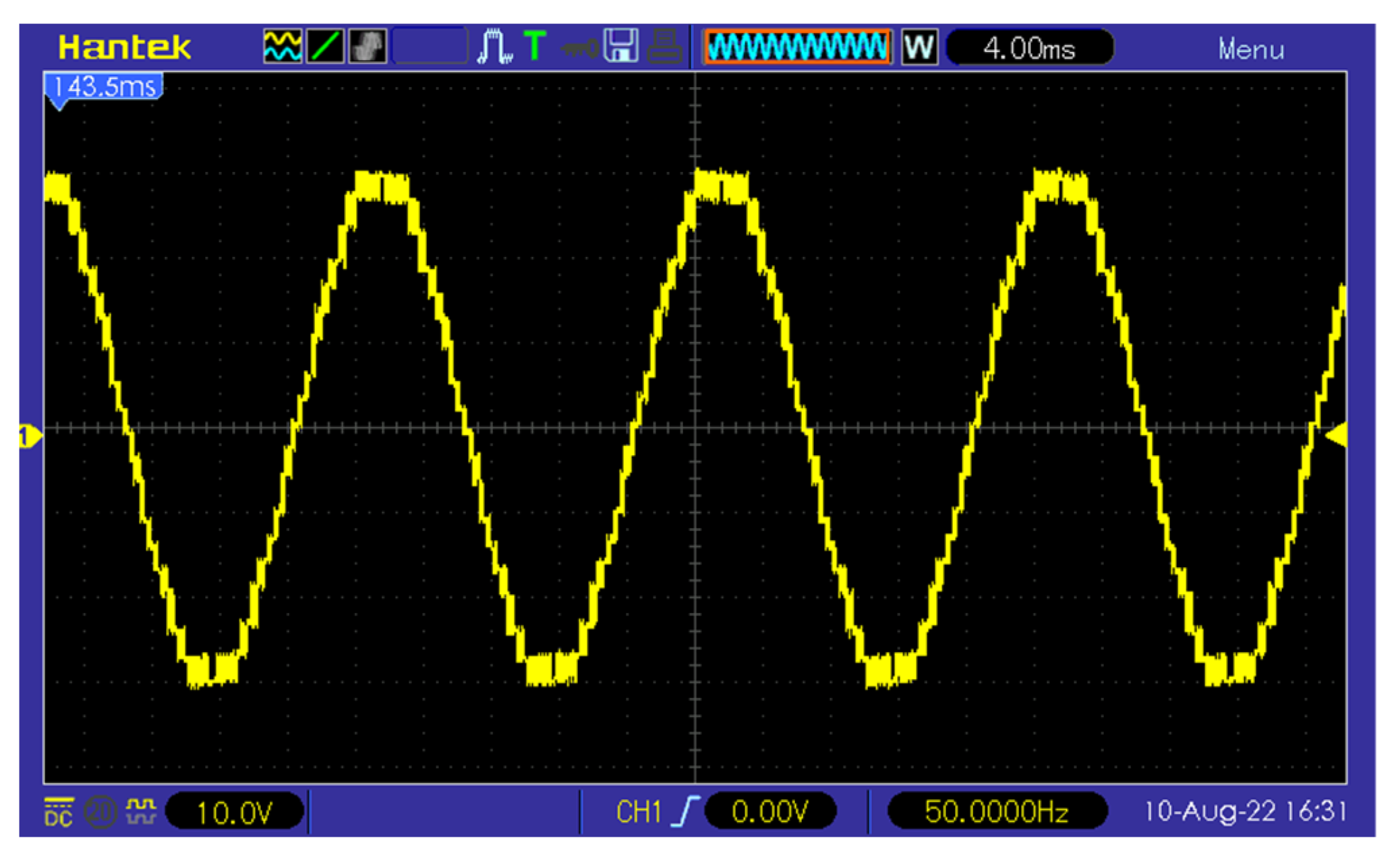

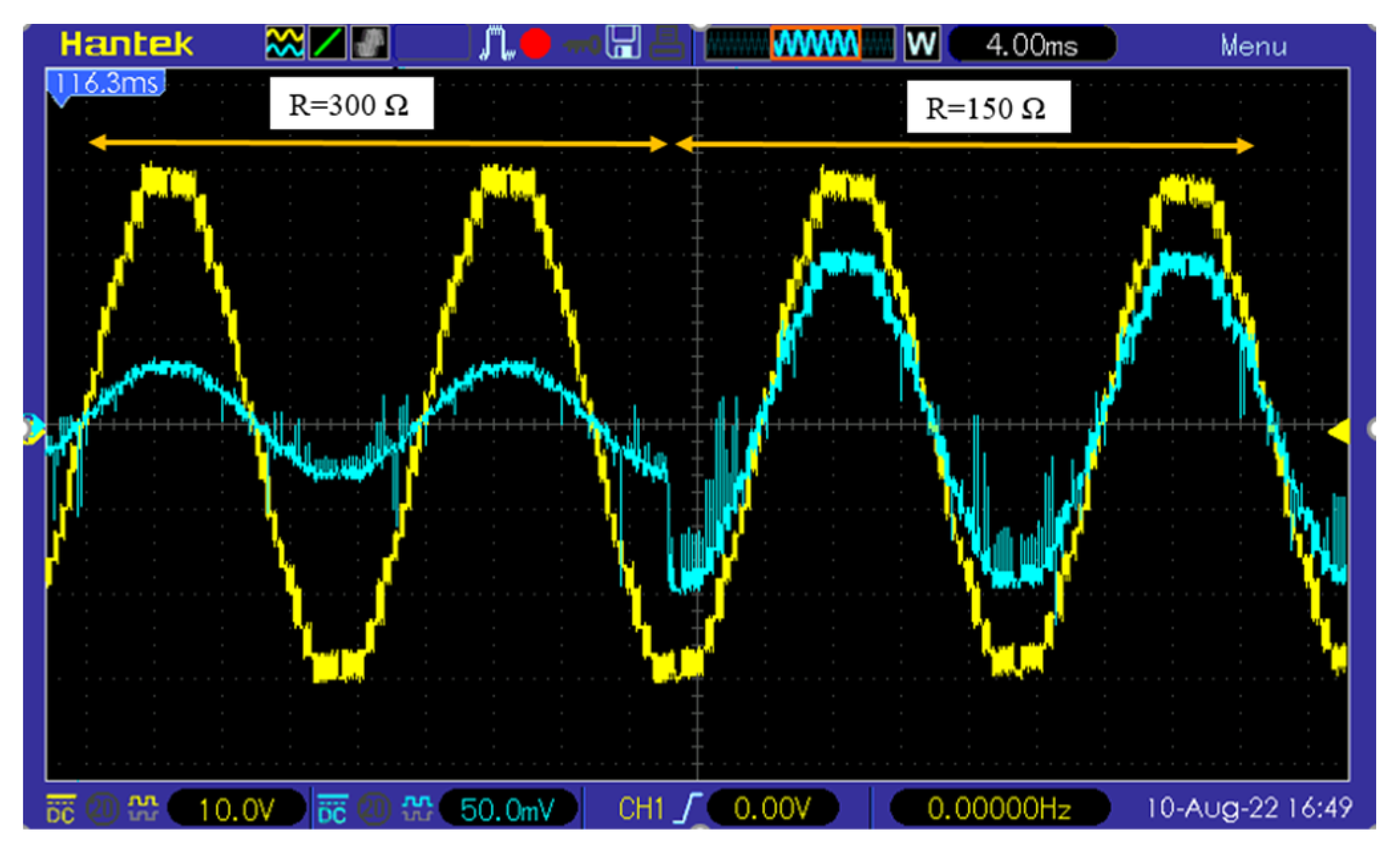

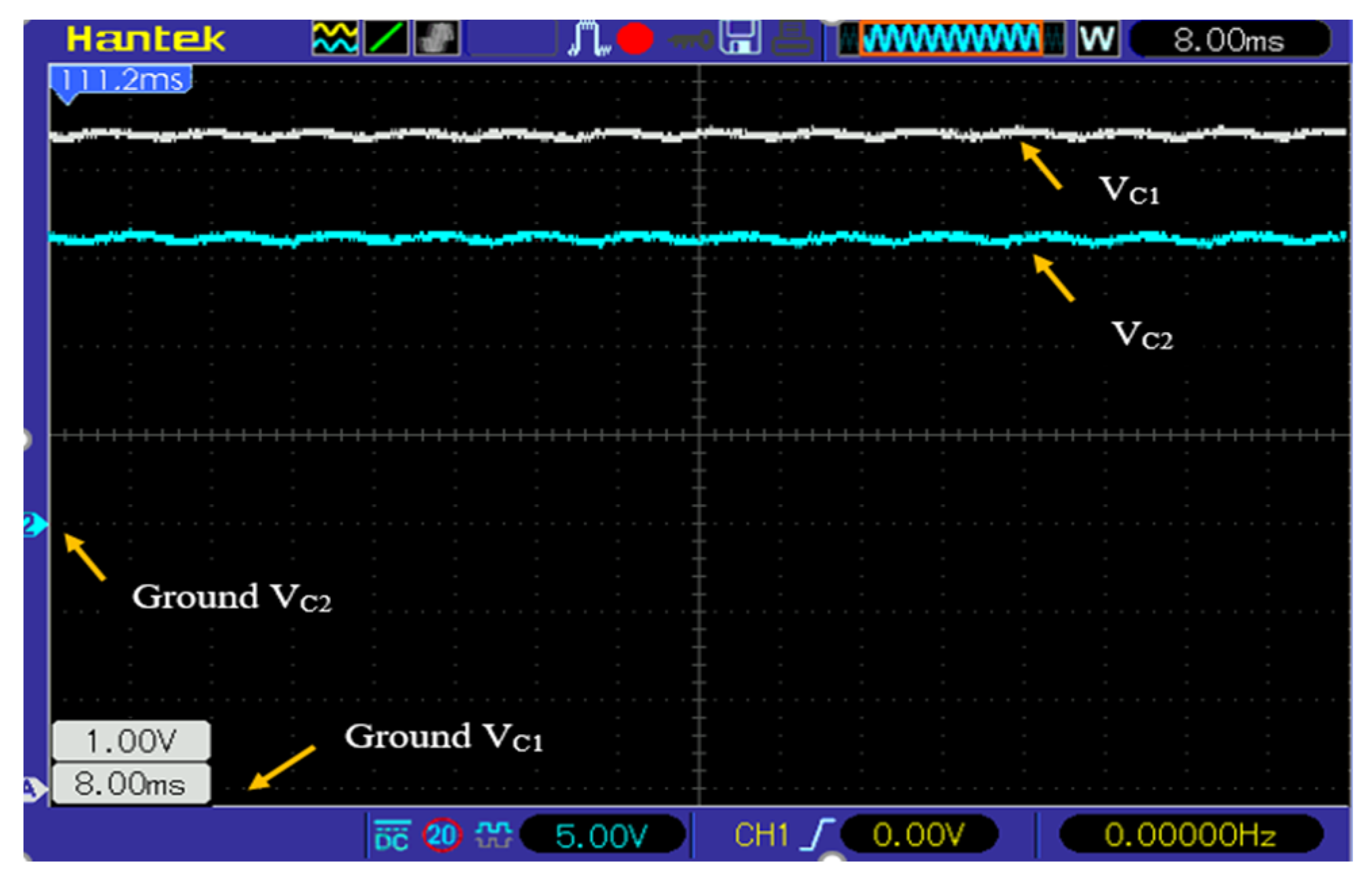

7.2. Experimental Results

- (1)

- All gate driver power supplies should be isolated from each other.

- (2)

- The reference signal in the MC-PWM (see Figure 5) must be set on the sample base mode with 1000/5 samples per period and a sample time of 0.0001 s.

- (3)

- A high-power resistor should be applied parallel to each capacitor for discharging their voltage when the test is completed.

8. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Singh, J.; Dahiya, R.; Saini, L.M. Recent research on transformer based single DC source multilevel inverter: A review. Renew. Sustain. Energy Rev. 2018, 82, 3207–3224. [Google Scholar] [CrossRef]

- Poorfakhraei, A.; Narimani, M.; Emadi, A. A Review of Multilevel Inverter Topologies in Electric Vehicles: Current Status and Future Trends. IEEE Open J. Power Electron. 2021, 2, 155–170. [Google Scholar] [CrossRef]

- Poorfakhraei, A.; Narimani, M.; Emadi, A. A Review of Modulation and Control Techniques for Multilevel Inverters in Traction Applications. IEEE Access 2021, 9, 24187–24204. [Google Scholar] [CrossRef]

- Ye, Y.; Hua, T.; Chen, S.; Wang, X. Neutral-Point-Clamped Five-Level Inverter With Self-Balanced Switched Capacitor. IEEE Trans. Ind. Electron. 2022, 69, 2202–2215. [Google Scholar] [CrossRef]

- Celikovic, J.; Ratul, D.; Hanh-Phuc, L.; Maksimovic, D. Modeling of capacitor voltage imbalance in flying capacitor multilevel DC-DC converters. In Proceedings of the 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Toronto, ON, Canada, 17–20 June 2019; pp. 1–8. [Google Scholar]

- Sajadi, R.; Iman-Eini, H.; Bakhshizadeh, M.K.; Neyshabouri, Y.; Farhangi, S. Selective Harmonic Elimination Technique With Control of Capacitive DC-Link Voltages in an Asymmetric Cascaded H-Bridge Inverter for STATCOM Application. IEEE Trans. Ind. Electron. 2018, 65, 8788–8796. [Google Scholar] [CrossRef]

- Odeh, C.I.; Obe, E.S.; Ojo, O. Topology for cascaded multilevel inverter. IET Power Electron. 2016, 9, 921–929. [Google Scholar] [CrossRef]

- Chivite-Zabalza, J.; Izurza-Moreno, P.; Madariaga, D.; Calvo, G.; Rodríguez, M.A. Voltage Balancing control in 3-Level Neutral-Point Clamped Inverters Using Triangular Carrier PWM Modulation for FACTS Applications. IEEE Trans. Power Electron. 2013, 28, 4473–4484. [Google Scholar] [CrossRef]

- Sanghun, C.; Saeedifard, M. Capacitor voltage balancing of flying capacitor multilevel converters by space vector PWM. IEEE Trans. Power Deliv. 2012, 27, 1154–1161. [Google Scholar]

- Yang, K.; Lan, X.; Zhang, Q.; Tang, X. Unified Selective Harmonic Elimination for Cascaded H-Bridge Asymmetric Multilevel Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 2138–2146. [Google Scholar] [CrossRef]

- Vahedi, H.; Sharifzadeh, M.; Al-Haddad, K. Modified Seven-Level Pack U-Cell Inverter for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1508–1516. [Google Scholar] [CrossRef]

- Gallaj, A.; Beiraghi, M.; Ardashir, J.F.; Ghanizadeh, R. New switched-capacitor multilevel converter with reduced elements. J. Energy Manag. Technol. 2020, 4, 12–20. [Google Scholar]

- Ye, Y.; Cheng, K.W.E.; Liu, J.; Ding, K. A Step-Up Switched-Capacitor Multilevel Inverter With Self-Voltage Balancing. IEEE Trans. Ind. Electron. 2014, 61, 6672–6680. [Google Scholar] [CrossRef]

- Zamiri, E.; Vosoughi, N.; Hosseini, S.H.; Barzegarkhoo, R.; Sabahi, M. A New Cascaded Switched-Capacitor Multilevel Inverter Based on Improved Series-Parallel Conversion with Less Number of Components. IEEE Trans. Ind. Electron. 2016, 63, 3582–3594. [Google Scholar] [CrossRef]

- Hachlowski, J.; Stala, R. A Novel Converter for Voltage Balance in Series-Connected Capacitors and Batteries. Power Electron. Drives 2018, 38, 65–74. [Google Scholar] [CrossRef]

- Yu, H.; Chen, B.; Yao, W.; Lu, Z. Hybrid Seven-Level Converter Based on T-Type Converter and H-bridge Cascaded under SPWM and SVM. IEEE Trans. Power Electron. 2018, 33, 689–702. [Google Scholar] [CrossRef]

- Nagendra, Y.; Swamy, R.K. A Novel Three-Phase Hybrid Multilevel Inverter Using Switched Capacitor Units for Industrial Applications. Int. J. Adv. Res. Electr. Electron. Instrum. Eng. 2016, 5, 7071–7079. [Google Scholar]

- Prabaharan, N.; Saravanan, S.; Jerin, A.; Palanisamy, K. Recent Developments on Power Inverters; IntechOpen: London, UK, 2017; A Reduced Switch Asymmetric Multilevel Inverter Topology Using Unipolar Pulse Width Modulation Strategies for Photovoltaic Application. [Google Scholar]

- Babaei, E.; Hosseini, S.H. New cascaded multilevel inverter topology with minimum number of switches. Energy Convers. Manag. 2009, 50, 2761–2767. [Google Scholar] [CrossRef]

- Wang, L.; Wu, Q.H.; Tang, W. Novel Cascaded Switched-Diode Multilevel Inverter for Renewable Energy Integration. IEEE Trans. Energy Convers. 2017, 32, 1574–1582. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Kojabadi, H.M.; Zamiry, E.; Vosoughi, N.; Chang, L. Generalized Structure for a Single Phase Switched-Capacitor Multilevel Inverter Using a New Multiple DC Link Producer With Reduced Number of Switches. IEEE Trans. Power Electron. 2016, 31, 5604–5617. [Google Scholar] [CrossRef]

- Samizadeh, M.; Yang, X.; Karami, B.; Chen, W.; Houran, M.A.; Abrishamifar, A.; Rahmati, A. A New Topology of Switched-Capacitor Multilevel Inverter for Single-Phase Grid-Connected with Eliminating Leakage Current. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018 -ECCE Asia), Niigata, Japan, 20–24 May 2018. [Google Scholar]

- Roy, T.; Bhattacharjee, B.; Sadhu, P.K.; Dasgupta, A.; Mohapatra, S. Step-up Switched Capacitor Multilevel Inverter with a Cascaded Structure in Asymmetric DC Source Configuration. J. Power Electron. 2018, 18, 1051–1066. [Google Scholar]

- Hinago, Y.; Koizumi, H. A Switched-Capacitor Inverter Using Series/Parallel Conversion With Inductive Load. IEEE Trans. Ind. Electron. 2012, 59, 878–887. [Google Scholar] [CrossRef]

- Babaei, E.; Gowgani, S.S. Hybrid Multilevel Inverter Using Switched Capacitor Units. IEEE Trans. Ind. Electron. 2014, 61, 4614–4621. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure. IEEE Trans. Power Electron. 2018, 33, 199–209. [Google Scholar] [CrossRef]

- Sadigh, A.K.; Dargahi, V.; Corzine, K.A. Analytical Determination of Conduction and Switching Power Losses in Flying-Capacitor-Based Active Neutral-Point-Clamped Multilevel Converter. IEEE Trans. Power Electron. 2016, 31, 5473–5494. [Google Scholar] [CrossRef]

- Hao, J.; Zhang, G.; Zheng, Y.; Hu, W.; Yang, K. Solution for selective harmonic elimination in asymmetric multilevel inverter based on stochastic configuration network and levenberg-marquardt algorithm. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 2855–2858. [Google Scholar]

- Daula, M.; Mekhilef, S.; Shah, N.M.; Memon, M.A. ‘Optimal design of a new cascaded multilevel inverter topology with reduced switch count. IEEE Access 2019, 7, 24498–24510. [Google Scholar]

- Yadav, S.K.; Mishra, N.; Singh, B. Three-phase single PV array fed scott-ternary multilevel converter with nearest level control. In Proceedings of the 2020 IEEE 7th Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON), Prayagraj, India, 27–29 November 2020; pp. 1–5. [Google Scholar]

| States | S1S2S3S4S5 | T1T2T3T4 | C1C2 | Vout |

|---|---|---|---|---|

| 1 | 11110 | 1010 | D-D | +9 V |

| 2 | 11100 | 1010 | D-W | +8 V |

| 3 | 11000 | 1010 | D-W | +7 V |

| 4 | 01110 | 1010 | D-D | +6 V |

| 5 | 01100 | 1010 | D-W | +5 V |

| 6 | 10101 | 1010 | C-C | +4 V |

| 7 | 10100 | 1010 | W-W | +3 V |

| 8 | 00110 | 1010 | W-D | +2 V |

| 9 | 00100 | 1010 | W-W | +V |

| 10 | 10101 | 1100 | C-C | 0+ |

| 11 | 10101 | 1100 | C-C | 0− |

| 12 | 00100 | 0101 | W-W | −V |

| 13 | 00110 | 0101 | W-D | −2 V |

| 14 | 10100 | 0101 | W-W | −3 V |

| 15 | 10101 | 0101 | C-C | −4 V |

| 16 | 01100 | 0101 | D-W | −5 V |

| 17 | 01110 | 0101 | D-D | −6 V |

| 18 | 11000 | 0101 | D-W | −7 V |

| 19 | 11100 | 0101 | D-W | −8 V |

| 20 | 11110 | 0101 | D-D | −9 V |

| NLevel | First Symmetrical Mode | Second Asymmetrical Mode | Third Asymmetrical Mode | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Nsw | Nd | NC | Nsw | Nd | NC | Nsw | Nd | NC | |

| 5 | 7 | 3 | 1 | 7 | 3 | 1 | 7 | 3 | 1 |

| 15 | 9 | 6 | 2 | -- | -- | -- | -- | -- | -- |

| 19 | -- | -- | -- | 9 | 6 | 2 | 9 | 6 | 2 |

| 33 | 11 | 9 | 3 | -- | -- | -- | -- | -- | -- |

| 47 | -- | -- | -- | 11 | 9 | 3 | -- | -- | -- |

| 61 | 13 | 12 | 4 | -- | -- | -- | -- | -- | -- |

| 67 | -- | -- | -- | -- | -- | -- | 11 | 9 | 3 |

| 93 | -- | -- | -- | 13 | 12 | 4 | -- | -- | -- |

| 101 | 15 | 15 | 5 | -- | -- | -- | -- | -- | -- |

| 161 | -- | -- | -- | 15 | 15 | 5 | -- | -- | -- |

| 155 | 17 | 18 | 6 | -- | -- | -- | -- | -- | -- |

| 231 | -- | -- | -- | -- | -- | -- | 13 | 12 | 4 |

| 255 | -- | -- | -- | 17 | 18 | 6 | -- | -- | -- |

| Topology | NL | Nsw | Nd | NC | Ngd | VG | TSVpu |

|---|---|---|---|---|---|---|---|

| [18] | 13 | 7 | 3 | 0 | 7 | 2.16 | 9 |

| [20] | 13 | 14 | 0 | 2 | 11 | 2 | 5.33 |

| [21] | 17 | 10 | 2 | 2 | 10 | 2 | 5.5 |

| [22] | 17 | 10 | 2 | 2 | 10 | 2 | 5.5 |

| [23] | 13 | 11 | 1 | 1 | 10 | 1.5 | 6.3 |

| [24] | 13 | 18 | 0 | 2 | 15 | 2 | 5 |

| [25] | 17 | 18 | 2 | 4 | 14 | 2 | 6 |

| [26] | 19 | 12 | 6 | 4 | 12 | 2.2 | 5.8 |

| [27] | 19 | 12 | 1 | 2 | 10 | 1.8 | 6.66 |

| Pro. | 19 | 9 | 6 | 2 | 9 | 2.25 | 7.2 |

| First input DC-source | u1 = 60 v |

| Second input DC-source | u2 = 20 v |

| Peak output voltage | 180 v |

| Processor | DSP TMS320F28379D |

| Capacitors | C1 = C2 = 4700 μF |

| IGBT | IRG4IBC30S |

| Diode | MBRF20100CT |

| Driver/optocoupler | HCPL-3120 |

| Current sensor | Resistive divider (0.1 Ω, 40 w) |

| Voltage sensor | Resistive divider (5 × 100 kΩ) |

| Sample time | 10 μs |

| Switching frequency | 5 kHz |

| Output frequency | 50 Hz |

| Resistive load | R = 300 Ω, 150 Ω |

| Resistive-Inductive load | R = 300 Ω, L = 22 mH |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sagvand, F.; Siahbalaee, J.; Koochaki, A. An Asymmetrical 19-Level Inverter with a Reduced Number of Switches and Capacitors. Electronics 2023, 12, 338. https://doi.org/10.3390/electronics12020338

Sagvand F, Siahbalaee J, Koochaki A. An Asymmetrical 19-Level Inverter with a Reduced Number of Switches and Capacitors. Electronics. 2023; 12(2):338. https://doi.org/10.3390/electronics12020338

Chicago/Turabian StyleSagvand, Farzad, Jafar Siahbalaee, and Amangaldi Koochaki. 2023. "An Asymmetrical 19-Level Inverter with a Reduced Number of Switches and Capacitors" Electronics 12, no. 2: 338. https://doi.org/10.3390/electronics12020338

APA StyleSagvand, F., Siahbalaee, J., & Koochaki, A. (2023). An Asymmetrical 19-Level Inverter with a Reduced Number of Switches and Capacitors. Electronics, 12(2), 338. https://doi.org/10.3390/electronics12020338