A Family of Five-Level Pseudo-Totem Pole Dual Boost Converters

Abstract

:1. Introduction

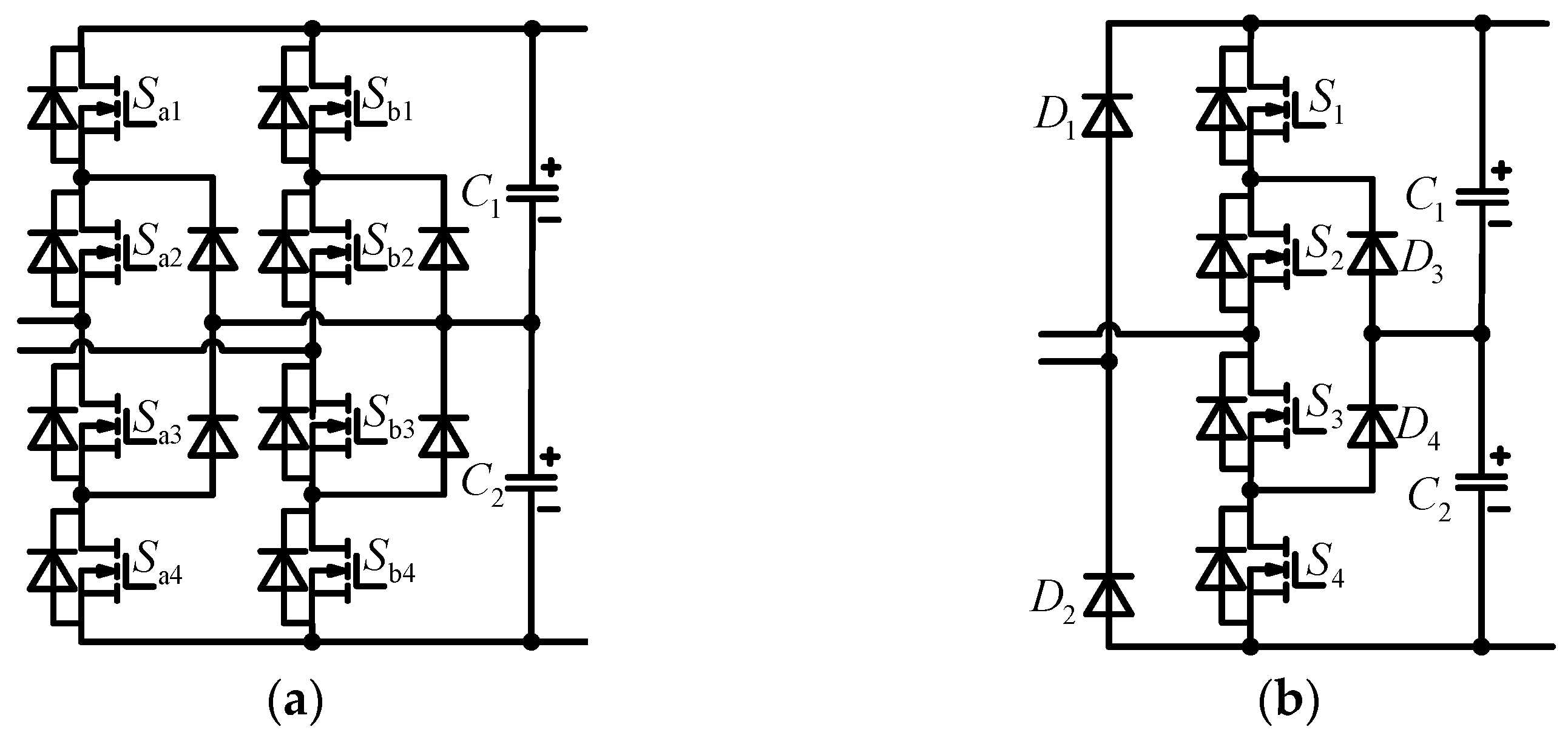

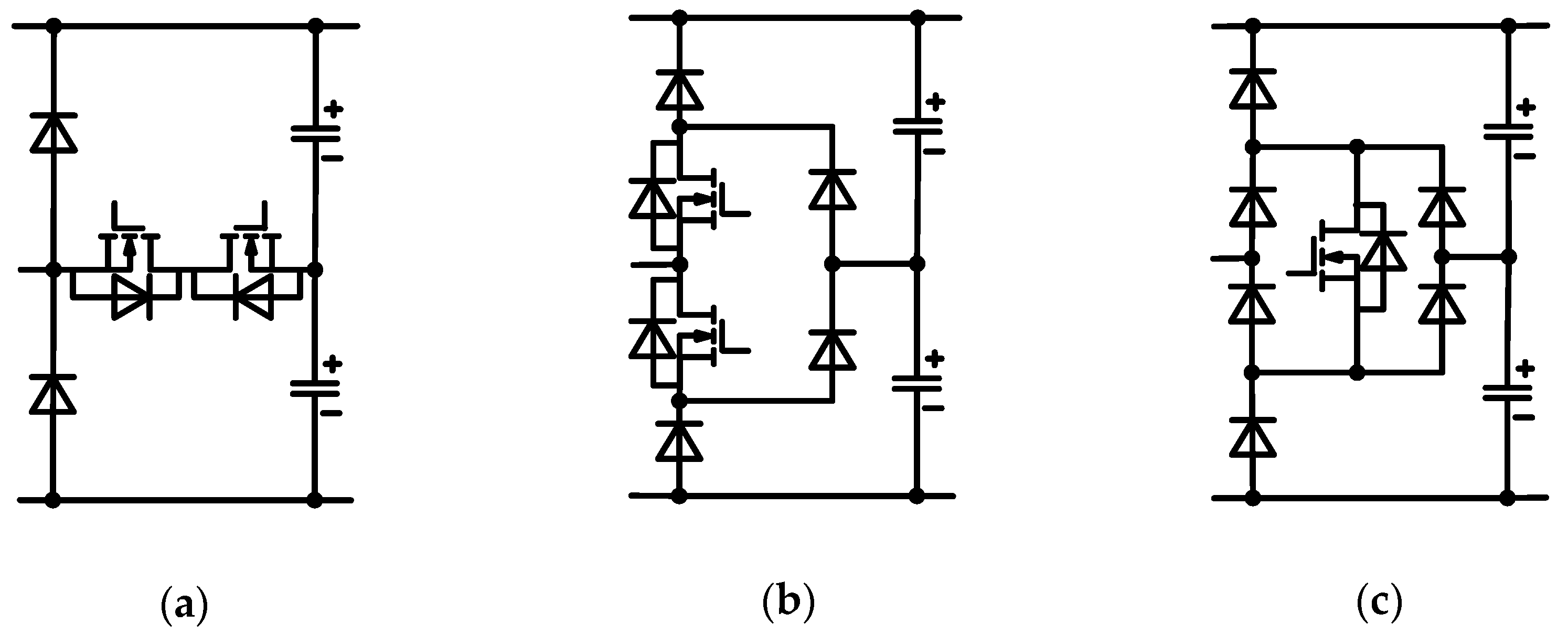

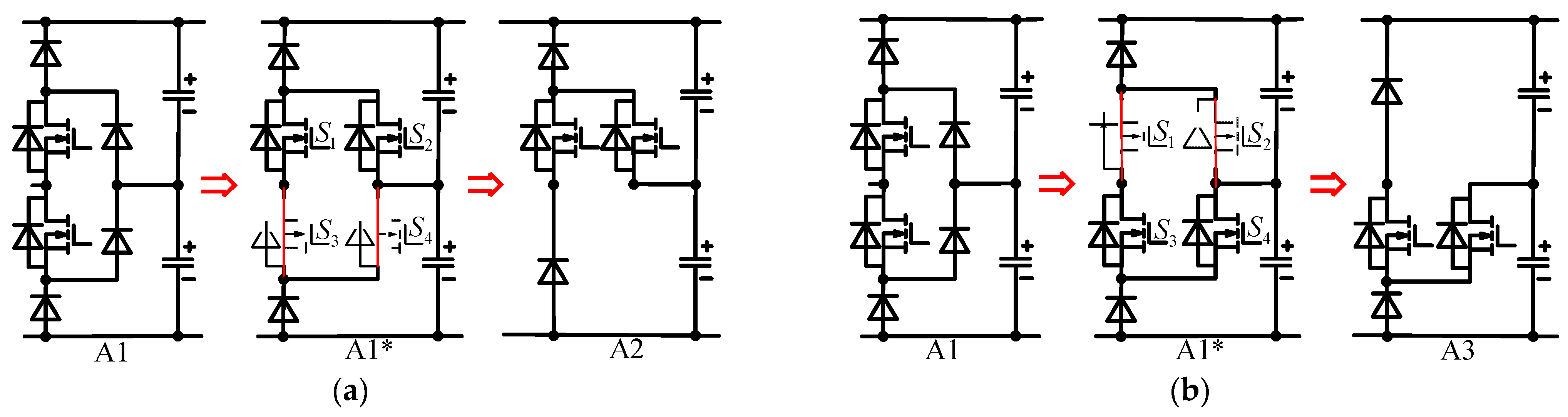

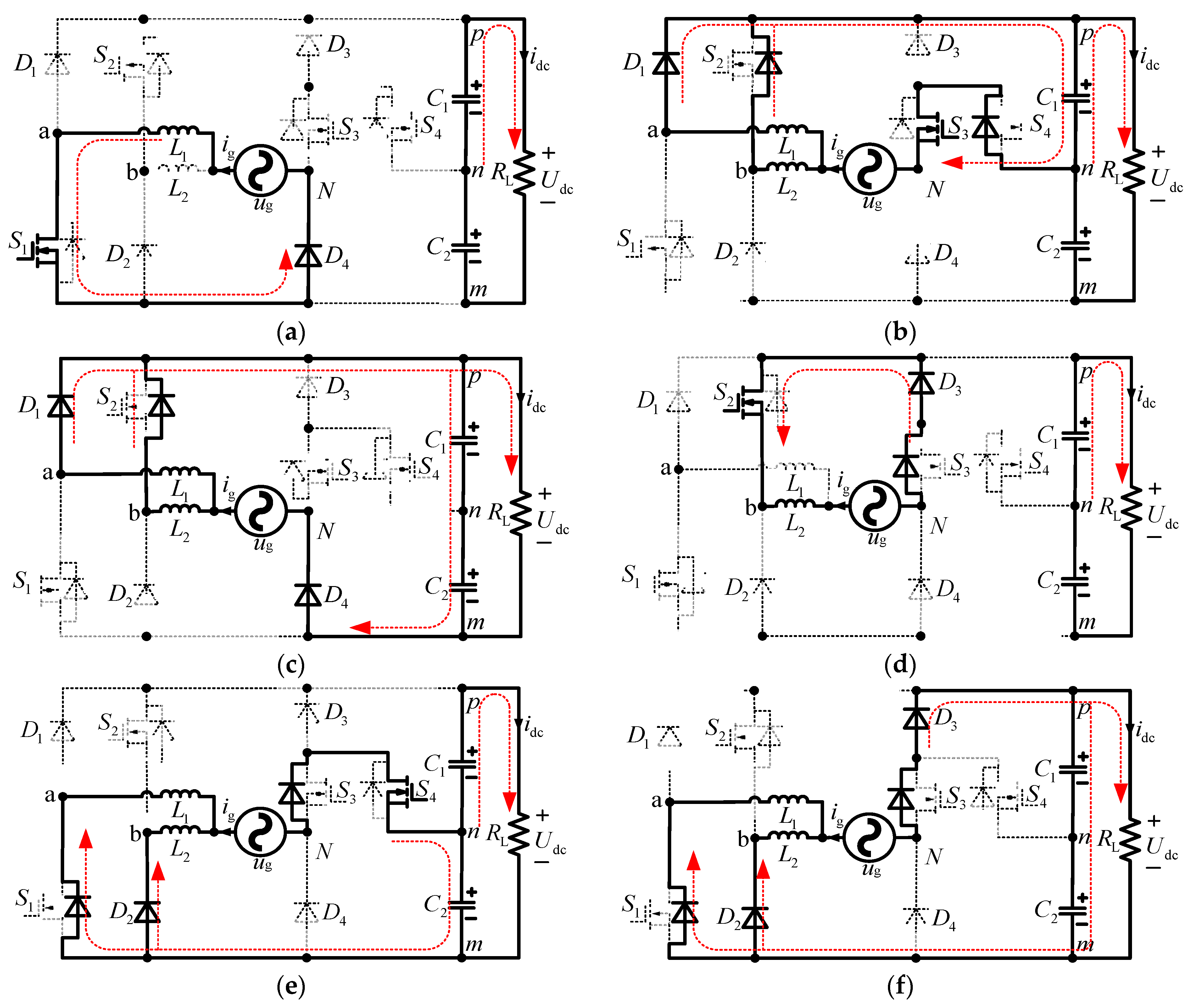

2. Topological Derivation and Operating Principle

2.1. Topological Derivation

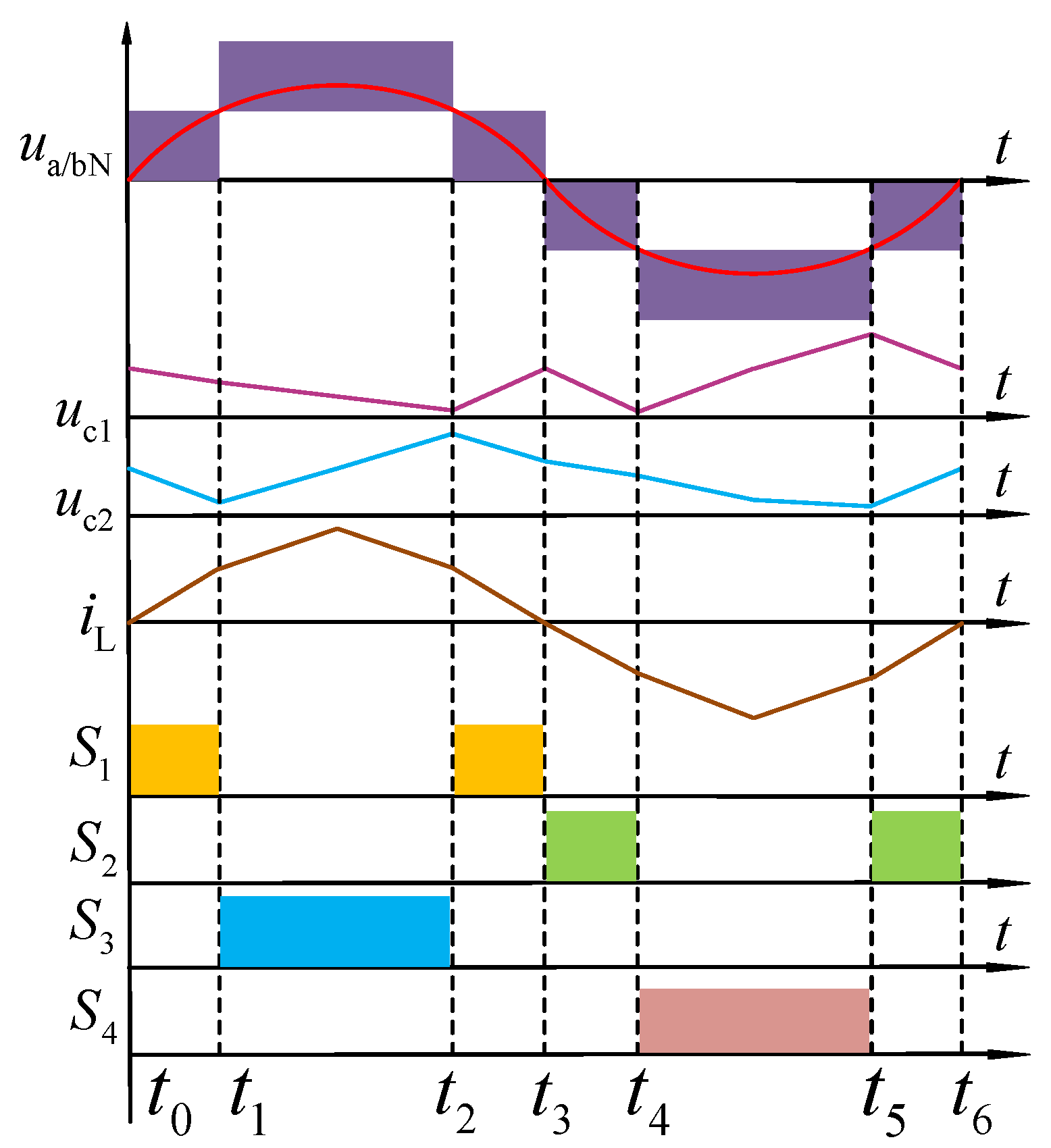

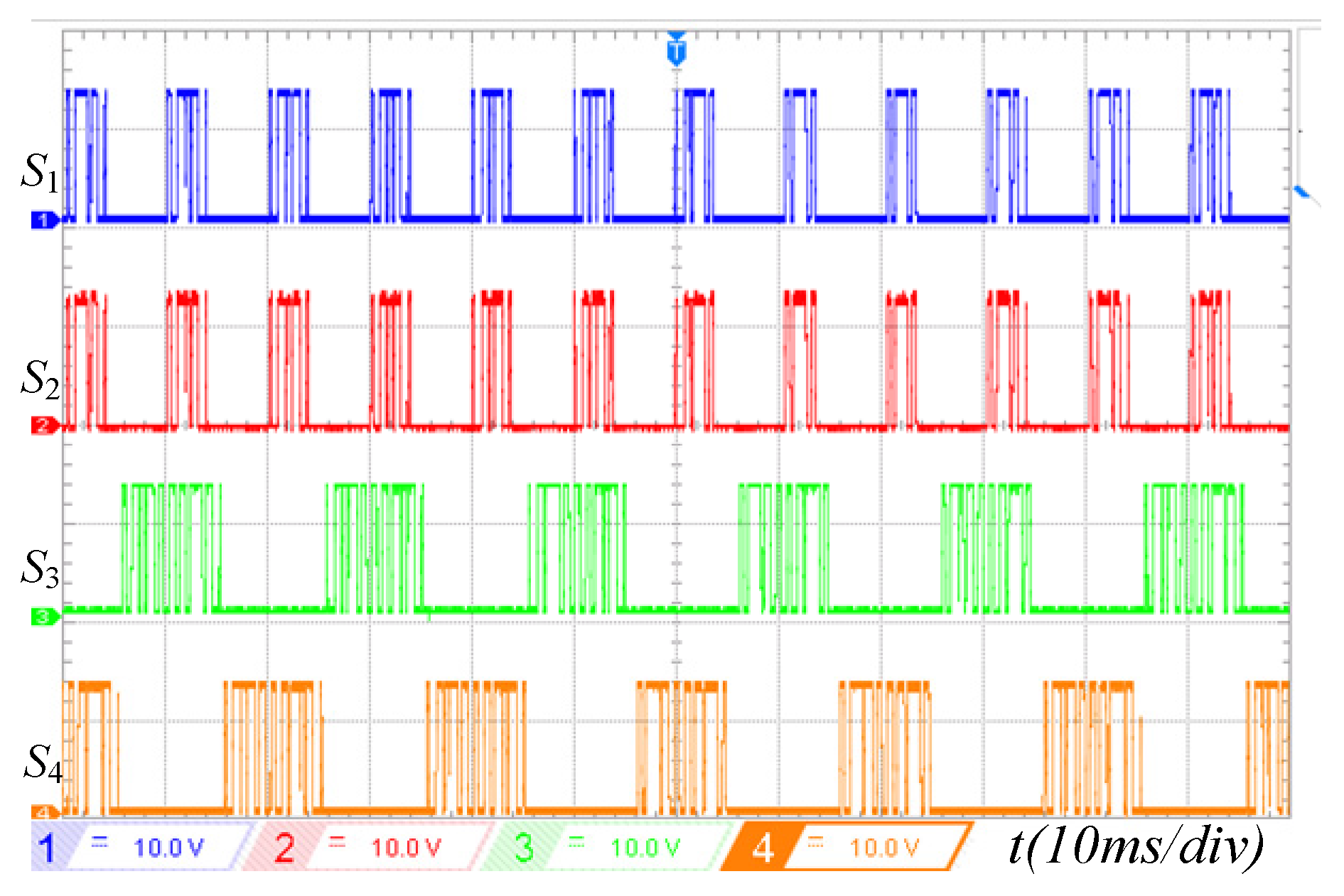

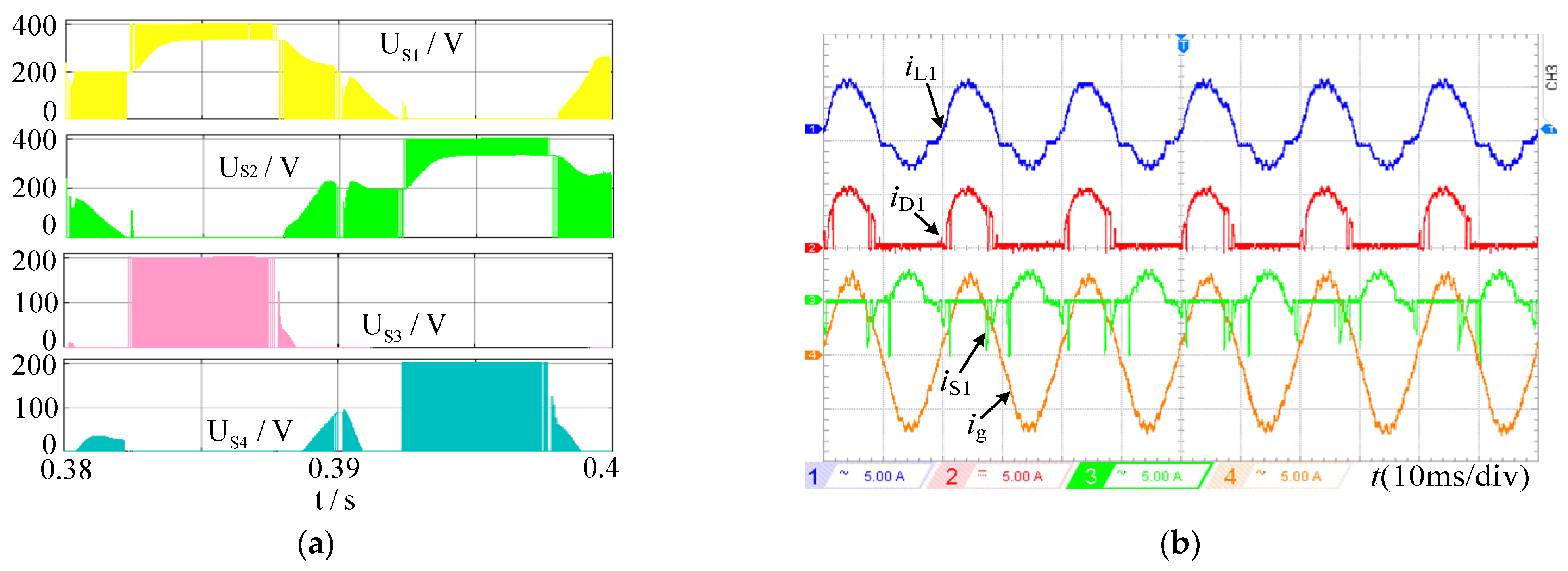

2.2. Operating Principle

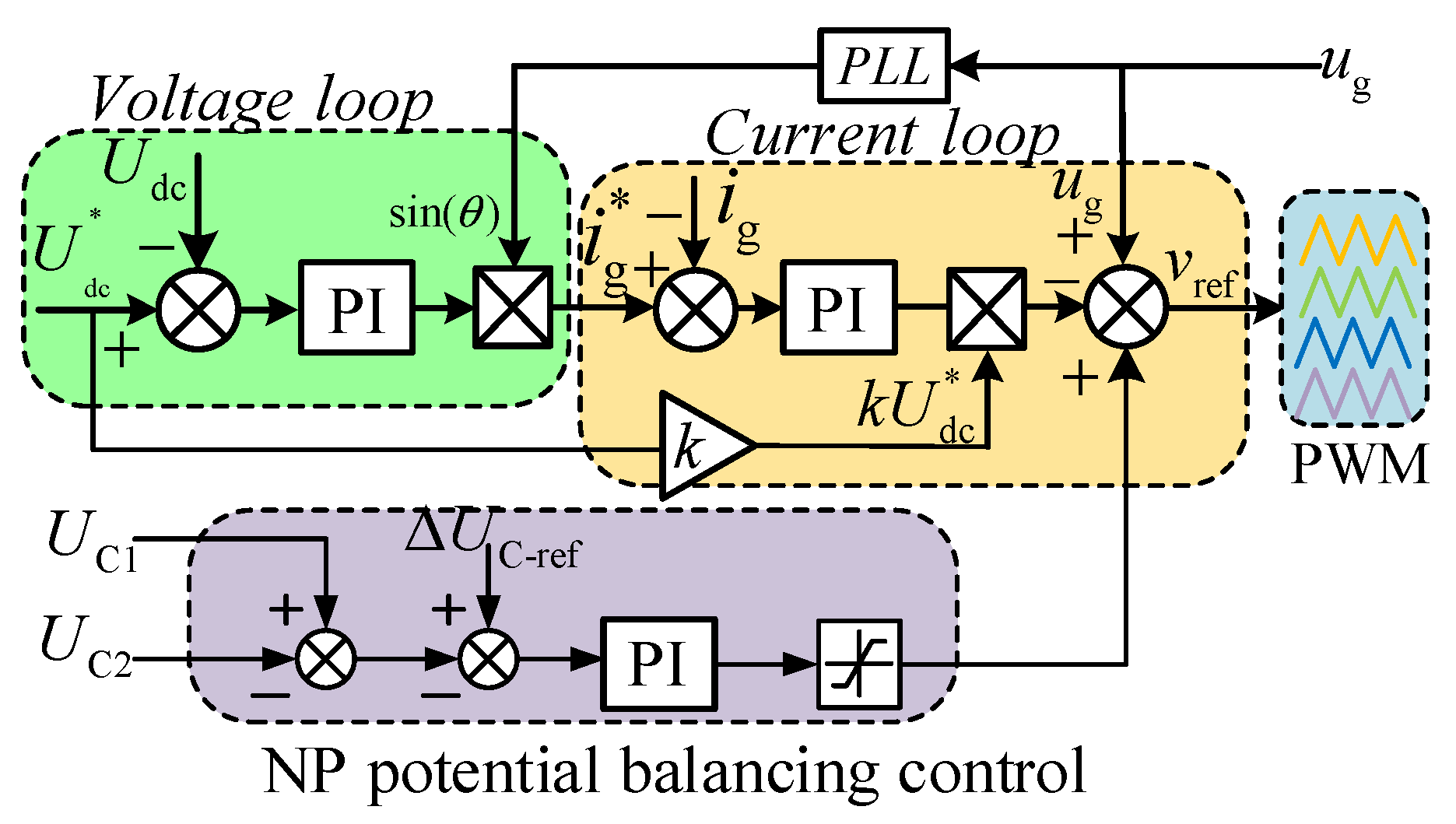

3. Control and Modulation Strategy

3.1. Control Strategy

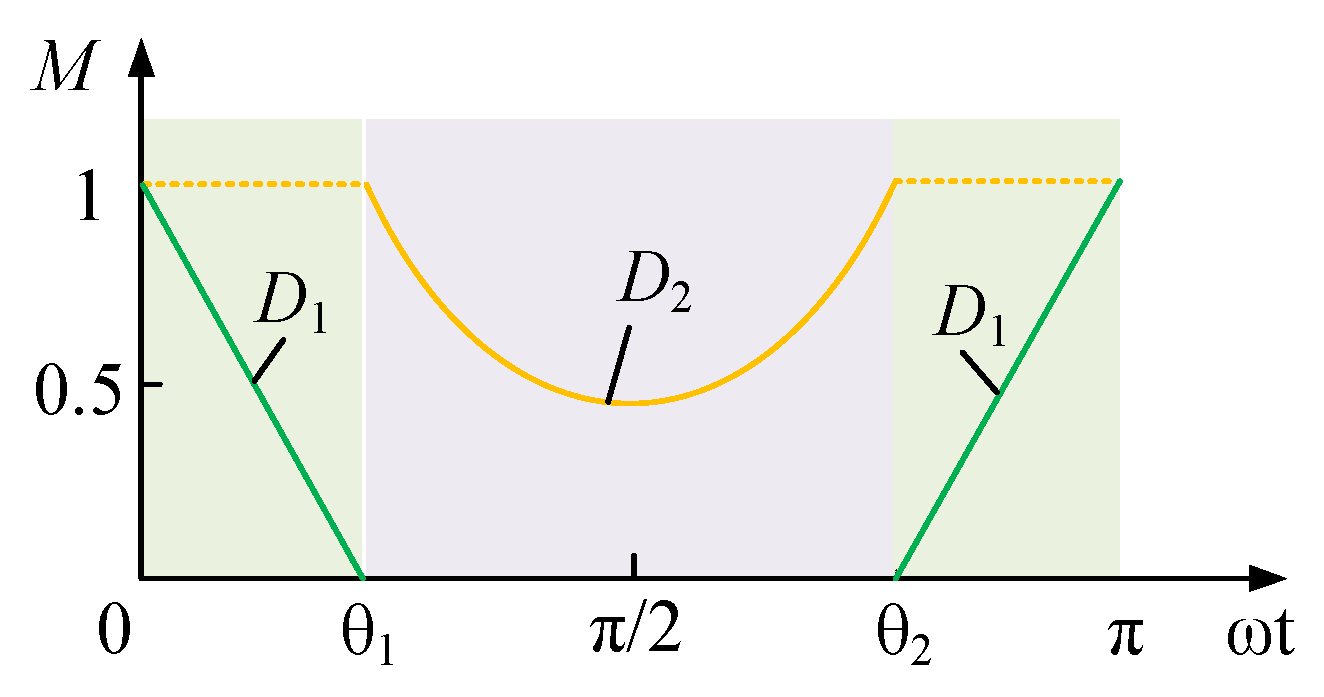

3.2. Modulation Strategy

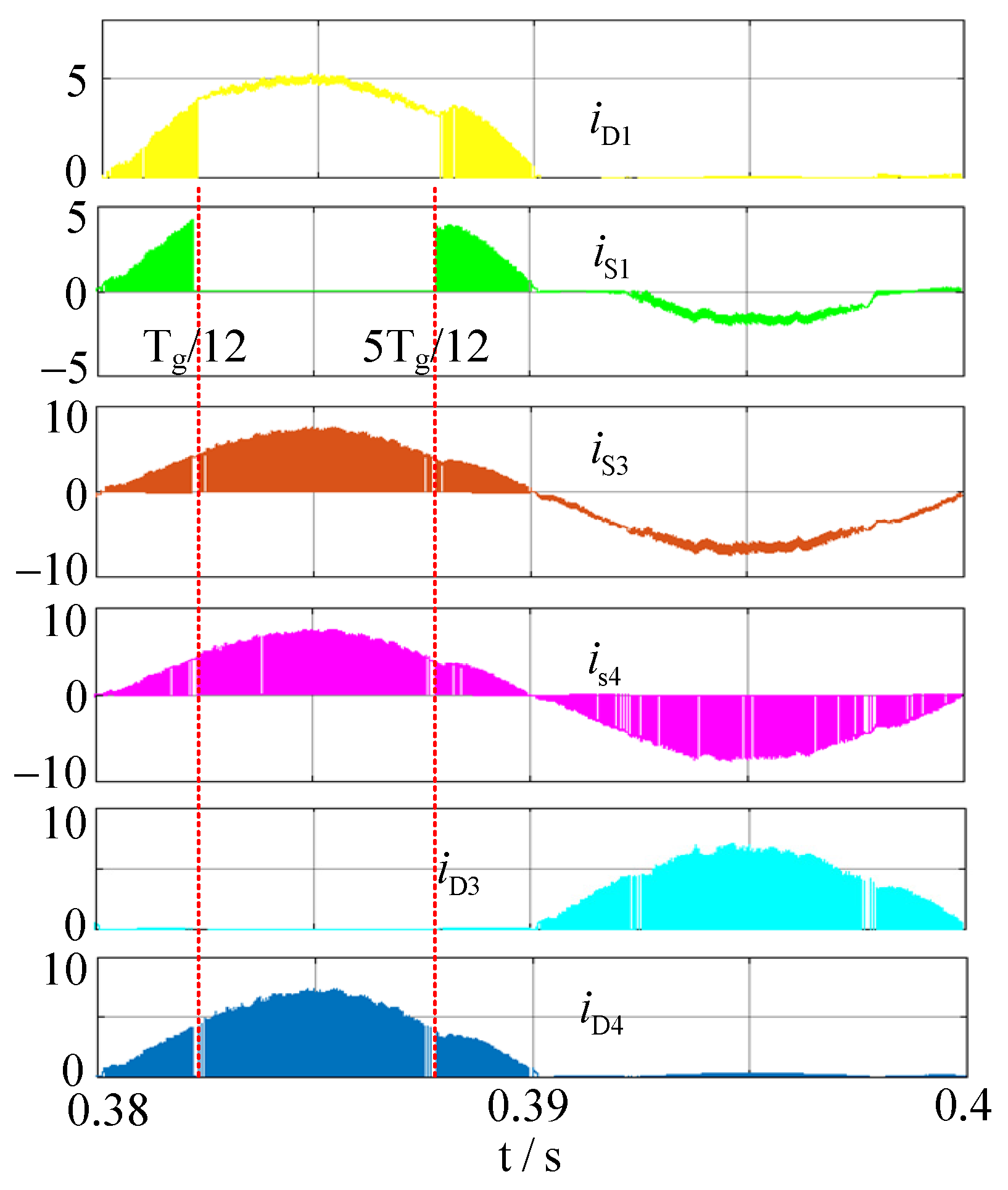

4. Performance Analysis

4.1. Voltage Stress Analysis

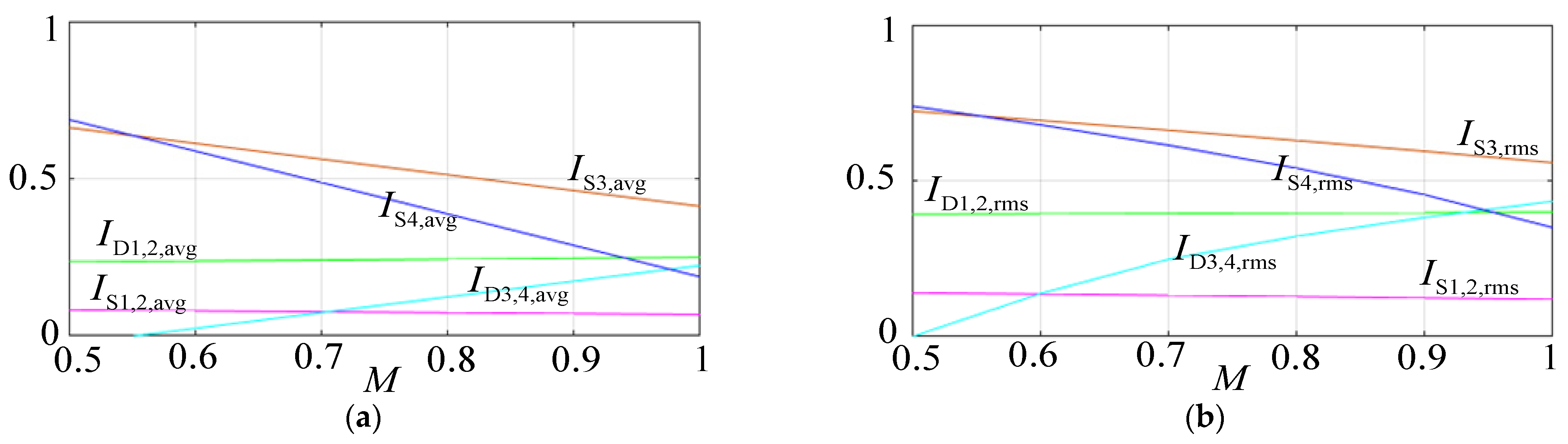

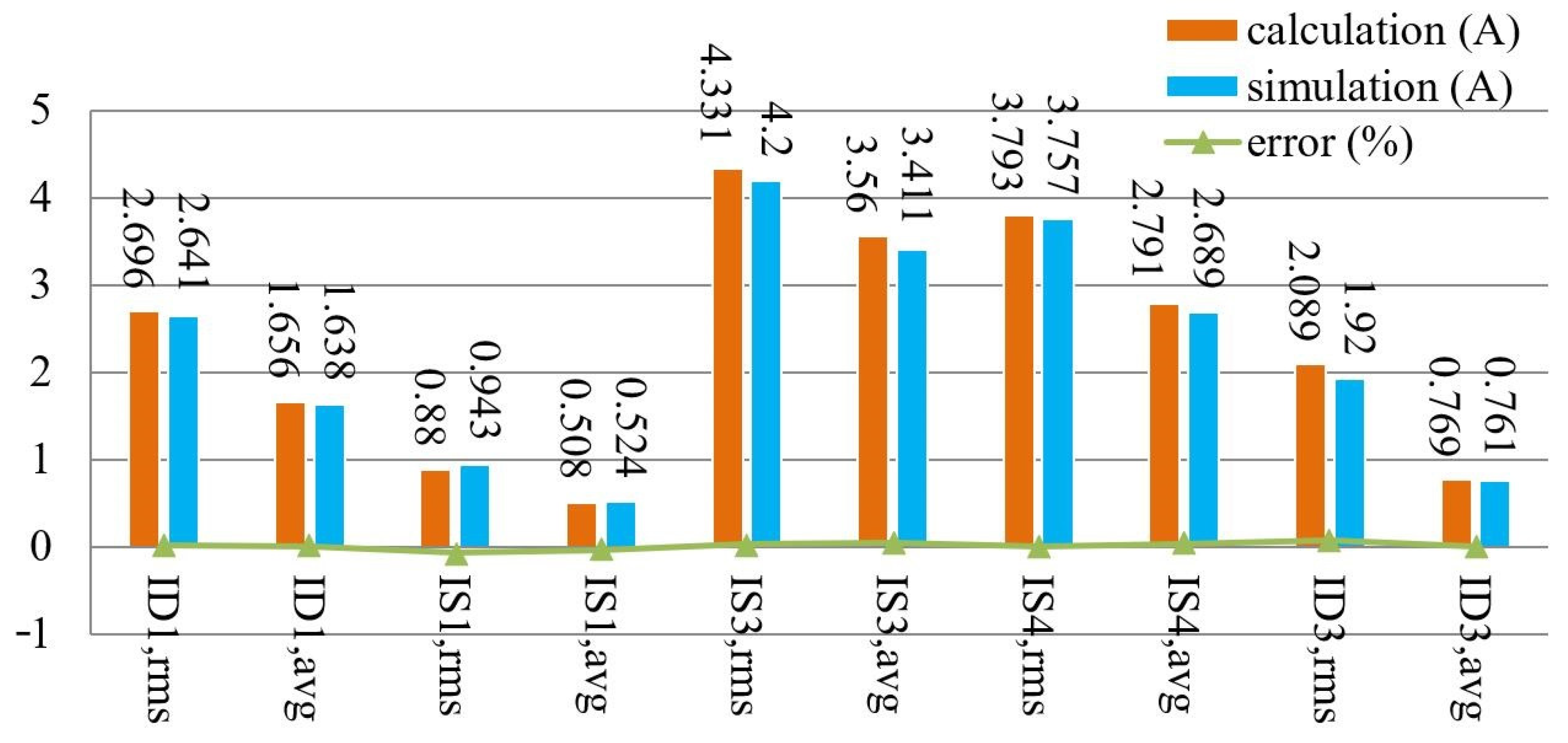

4.2. Current Stress Analysis

4.3. Loss Analysis

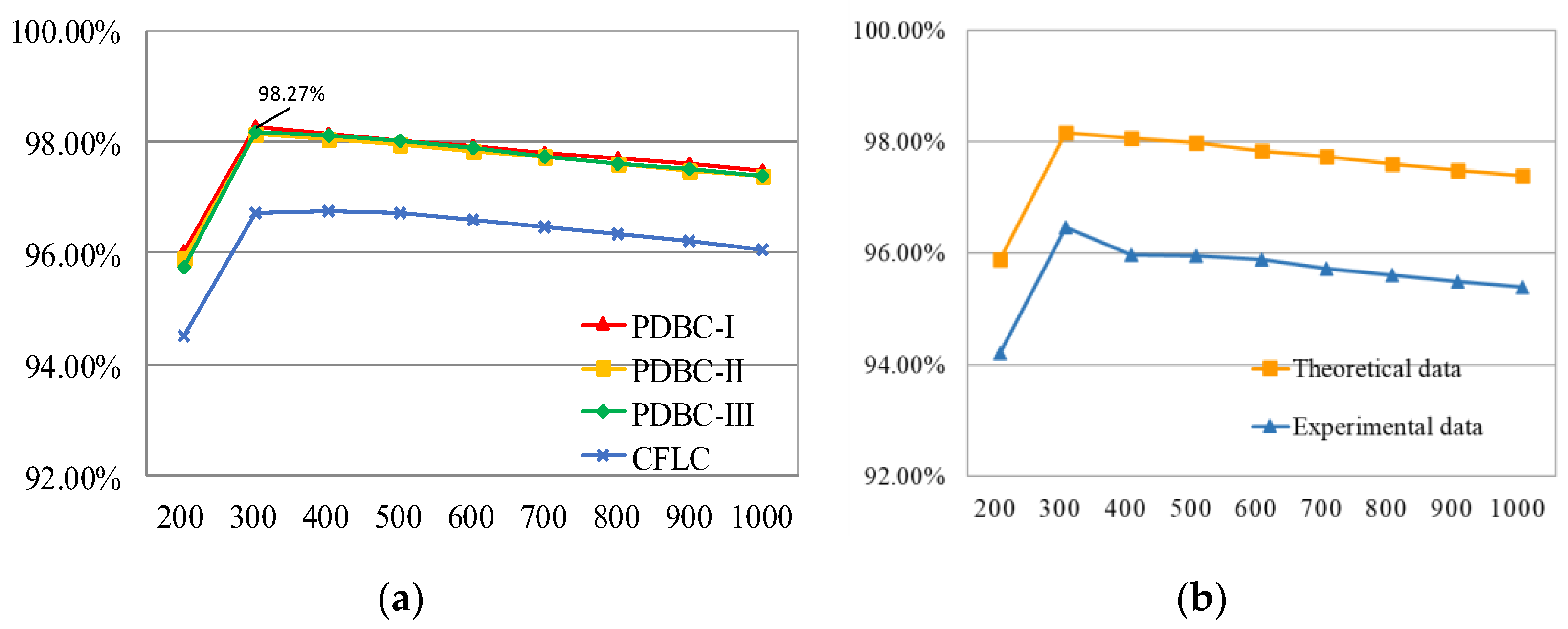

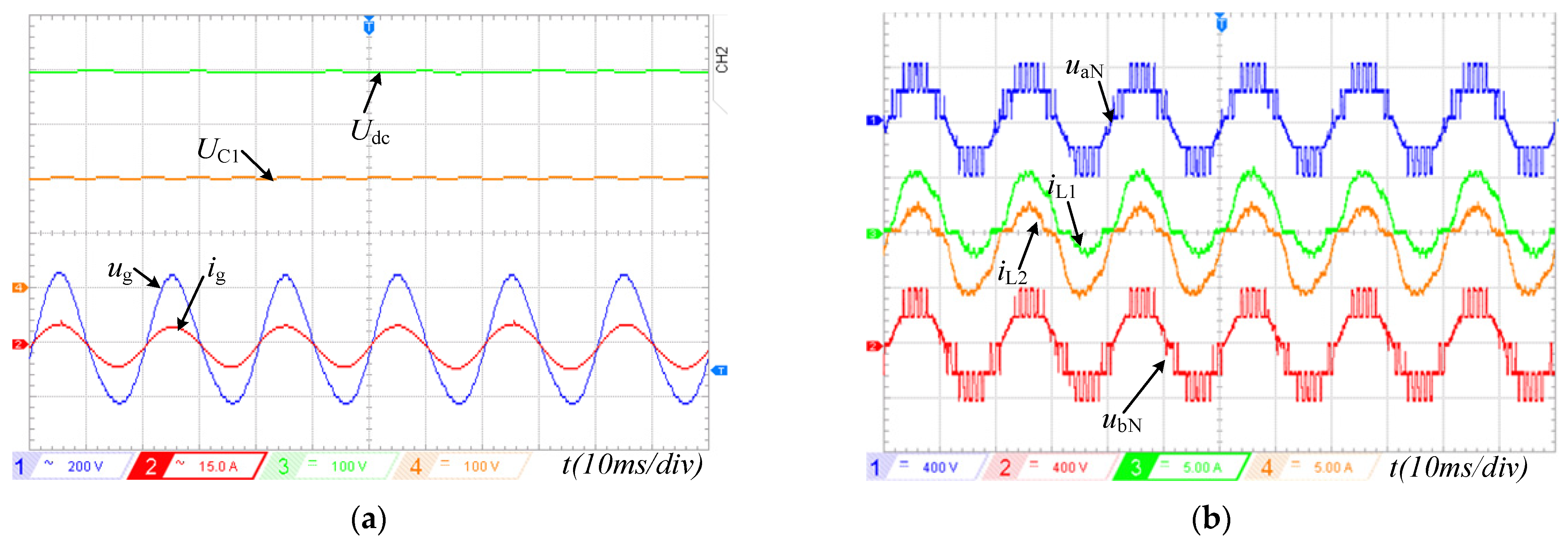

5. Experimental Verification

6. Conclusions

- (1)

- The experimental results show that the PDBCs proposed in this paper have good input and output waveforms at low switching frequency. Therefore, the PDBCs can improve overall efficiency by reducing switching losses.

- (2)

- The efficiency of the five PDBCs proposed in this paper is higher than that of a CFLC. The PDBC-I has the smallest loss and the highest efficiency, with a peak efficiency of 98.27%, and its overall performance is the best.

- (3)

- Compared with the conventional three-level PTP circuit, the five PDBCs proposed in this paper have higher power density, and the voltage stress of some devices is reduced by half. In addition, the PDBC-II and PDBC-III have more devices with voltage stresses halved; thus, their cost is lower.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Shah, M.T.; Chauhan, S.K.; Tekwani, P.N. Analysis of multiaxis current controller for power system friendly front-end converter employing two-level and three-level topologies. IEEE Trans. Ind. Electron. 2021, 68, 586–597. [Google Scholar] [CrossRef]

- Li, K.; Formentini, A.; Dewar, D.; Zanchetta, P. Controller design of an active front-end converter keeping in consideration grid dynamic interaction. IEEE Trans. Ind. Electron. 2022, 69, 5195–5206. [Google Scholar] [CrossRef]

- Gendrin, M.; Gauthier, J.; Lin-Shi, X. A predictive hybrid pulse-width-modulation technique for active-front-end rectifiers. IEEE Trans. Power Electron. 2017, 32, 5487–5496. [Google Scholar] [CrossRef]

- Kang, C.; Wang, W.; Li, W.; Du, H.; Diao, L. Balance midpoint potential control of three-level boost converter for rail transit application. IEEE Access 2019, 7, 47737–47746. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Karshenas, H.; Bakhshai, A. A five-level nested diode-clamped converter for medium-voltage applications. IEEE Trans. Ind. Electron. 2022, 69, 6471–6483. [Google Scholar] [CrossRef]

- Zhang, Y.; Bai, Y.; Yang, H.; Zhang, B. Low switching frequency model predictive control of three-level inverter-fed IM drives with speed-sensorless and field-weakening operations. IEEE Trans. Ind. Electron. 2019, 66, 4262–4272. [Google Scholar] [CrossRef]

- Zhang, G.; Peng, S.; Geng, Q.; Shi, T.; Xia, C. Hybrid discontinuous space vector PWM strategy for three-level inverters under two-phase loads condition. IEEE Trans. Power Electron. 2022, 37, 1711–1721. [Google Scholar] [CrossRef]

- Montero-Robina, P.; Umbría, F.; Salas, F.; Gordillo, F. Integrated control of five-level diode-clamped rectifiers. IEEE Trans. Ind. Electron. 2019, 66, 6628–6636. [Google Scholar] [CrossRef]

- Sebaaly, F.; Vahedi, H.; Kanaan, H.Y.; Al-Haddad, K. Experimental design of fixed switching frequency model predictive control for sensorless five-level packed U-cell inverter. IEEE Trans. Ind. Electron. 2019, 66, 3427–3434. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Palanisamy, A.; Mahajan, A.; Liese, S.; Long, T.; Blaabjerg, F. Analysis and design of a novel six-switch five-level active boost neutral point clamped inverter. IEEE Trans. Ind. Electron. 2020, 67, 10485–10496. [Google Scholar] [CrossRef]

- He, L.; Cheng, C. A flying-capacitor-clamped five-level inverter based on bridge modular switched-capacitor topology. IEEE Trans. Ind. Electron. 2016, 63, 7814–7822. [Google Scholar] [CrossRef]

- Gautam, S.P.; Kumar, L.; Gupta, S.; Agrawal, N. A single-phase five-level inverter topology with switch fault-tolerance capabilities. IEEE Trans. Ind. Electron. 2017, 64, 2004–2014. [Google Scholar] [CrossRef]

- Alsofyani, I.M.; Lee, K.-B. Simple capacitor voltage balancing for three-level NPC inverter using discontinuous PWM method with hysteresis neutral-point error band. IEEE Trans. Power Electron. 2021, 36, 12490–12503. [Google Scholar] [CrossRef]

- Zhang, Y.; Li, C.; Li, C.; Xin, Z.; Chen, R.; Li, W.; He, X.; Ma, H. A SiC and Si hybrid five-level unidirectional rectifier for medium voltage applications. IEEE Trans. Ind. Electron. 2022, 69, 7537–7548. [Google Scholar] [CrossRef]

- Chen, W.; Bazzi, A.M. Model-based voltage quality analysis and optimization in post-fault Reconfigured N-level NPC inverter. IEEE Trans. Power Electron. 2021, 36, 13706–13715. [Google Scholar] [CrossRef]

- He, Z.; Ding, H.; Chen, Z.; Zhao, Q.; Xun, Z.; Zhang, D.; Shao, J. A hybrid DPWM for vienna rectifiers based on the three-level to two-level conversion. IEEE Trans. Ind. Electron. 2022, 69, 9429–9439. [Google Scholar] [CrossRef]

- Wang, S.; Ma, J.; Liu, B.; Jiao, N.; Liu, T.; Wang, Y. Unified SVPWM algorithm and optimization for single-phase three-level NPC converters. IEEE Trans. Power Electron. 2020, 35, 7702–7712. [Google Scholar] [CrossRef]

- Ma, J.; Song, W.; Wang, S.; Feng, X. Model predictive direct power control for single phase three-level rectifier at low switching frequency. IEEE Trans. Power Electron. 2018, 33, 1050–1062. [Google Scholar] [CrossRef]

- Kim, J.; Lee, S.; Cha, W.; Kwon, B. High-efficiency bridgeless three-level power factor correction rectifier. IEEE Trans. Ind. Electron. 2017, 64, 1130–1136. [Google Scholar] [CrossRef]

- Liu, Z.; Xia, Z.; Li, F.; Wang, G.; Li, C. A capacitor voltage precharge method for back-to-back five-level active neutral-point-clamped converter. IEEE Trans. Ind. Electron. 2021, 68, 9277–9286. [Google Scholar] [CrossRef]

- Zhang, L.; Sun, K.; Xing, Y.; Zhao, J. A family of five-level dual-buck full-bridge inverters for grid-tied applications. IEEE Trans. Power Electron. 2016, 31, 7029–7042. [Google Scholar] [CrossRef]

- Rech, C.; Castiblanco, W.A.P. Five-level switched-capacitor ANPC inverter with output voltage boosting capability. IEEE Trans. Ind. Electron. 2022, 70, 29–38. [Google Scholar] [CrossRef]

- Monteiro, V.; Ferreira, J.C.; Meléndez, A.A.N.; Afonso, J.L. Model predictive control applied to an improved five-level bidirectional converter. IEEE Trans. Ind. Electron. 2016, 63, 5879–5890. [Google Scholar] [CrossRef]

- Ma, H.; Zheng, K.; Jiang, H.; Yin, H. A family of dual-boost bridgeless five-level rectifiers with common-core inductors. IEEE Trans. Power Electron. 2021, 36, 12565–12578. [Google Scholar] [CrossRef]

- Vahedi, H.; Shojaei, A.A.; Chandra, A.; Al-Haddad, K. Five-level reduced-switch-count boost PFC rectifier with multicarrier PWM. IEEE Trans. Ind. Appl. 2016, 52, 4201–4207. [Google Scholar] [CrossRef]

| Mode | ig | S1 | S2 | S3 | S4 | C1 | C2 | uaN | ubN |

|---|---|---|---|---|---|---|---|---|---|

| 1 | >0 | 1 | 0 | 0 | 0 | ↓ | ↓ | 0 | ug |

| 2 | >0 | 0 | 0 | 1 | 0 | ↑ | ↓ | Udc/2 | Udc/2 |

| 3 | >0 | 0 | 0 | 0 | 0 | ↑ | ↑ | Udc | Udc |

| 4 | <0 | 0 | 1 | 0 | 0 | ↓ | ↓ | ug | 0 |

| 5 | <0 | 0 | 0 | 0 | 1 | ↓ | ↑ | −Udc/2 | −Udc/2 |

| 6 | <0 | 0 | 0 | 0 | 0 | ↑ | ↑ | −Udc | −Udc |

| Components | PDBC-I | PDBC-II | PDBC-III |

|---|---|---|---|

| S1,2 | Udc | Udc | Udc |

| S3,4 | Udc/2 | Udc/2 | Udc/2 |

| D1,2 | Udc | Udc | Udc |

| D3 | Udc | Udc/2 | Udc |

| D4 | Udc | Udc | Udc/2 |

| Components | Parameters | Values |

|---|---|---|

| IRFP450 | On-state resistance, rds | 0.4 Ω |

| On-delay time, td(on) | 17 ns | |

| Rise time, tr | 47 ns | |

| Turn-off delay time, td(off) | 92 ns | |

| Fall time, tf | 44 ns | |

| RHRP3060 | Conduction voltage, Uf | 1.7 V |

| Reverse peak voltage, Urp | 600 V | |

| Reverse peak current, Irp | 250 μA | |

| Reverse current fall time, tb | 18 ns |

| Parameters | Label | Value |

|---|---|---|

| Input filter inductors | L1, L2 | 2 mH |

| DC-side capacitors | C1, C2 | 1000 μF |

| Input voltage | ug | RMS 220 V |

| Output voltage | Udc | 400 V |

| Rated output power | Po | 1000 W |

| Grid frequency | fg | 50 Hz |

| Switching frequency | fs | 20 kHz |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, Q.; Miao, G.; Dai, H.; Jing, C.; Xu, J.; Li, W.; Ma, H. A Family of Five-Level Pseudo-Totem Pole Dual Boost Converters. Electronics 2023, 12, 3722. https://doi.org/10.3390/electronics12173722

Zhao Q, Miao G, Dai H, Jing C, Xu J, Li W, Ma H. A Family of Five-Level Pseudo-Totem Pole Dual Boost Converters. Electronics. 2023; 12(17):3722. https://doi.org/10.3390/electronics12173722

Chicago/Turabian StyleZhao, Qingsong, Guixi Miao, Hong Dai, Cheng Jing, Jianyuan Xu, Wenjing Li, and Hui Ma. 2023. "A Family of Five-Level Pseudo-Totem Pole Dual Boost Converters" Electronics 12, no. 17: 3722. https://doi.org/10.3390/electronics12173722

APA StyleZhao, Q., Miao, G., Dai, H., Jing, C., Xu, J., Li, W., & Ma, H. (2023). A Family of Five-Level Pseudo-Totem Pole Dual Boost Converters. Electronics, 12(17), 3722. https://doi.org/10.3390/electronics12173722