A Dynamic and Static Binary Translation Method Based on Branch Prediction

Abstract

:1. Overview

- We propose a branch prediction-based dynamic–static binary translation method.

- We implemented a BP-QEMU prototype framework by extending the QEMU binary translation framework to facilitate the proposed method.

- We designed and conducted experiments to validate the correctness and the performance of the BP-QEMU.

2. Preliminaries

2.1. Dynamic Translation Principles of QEMU

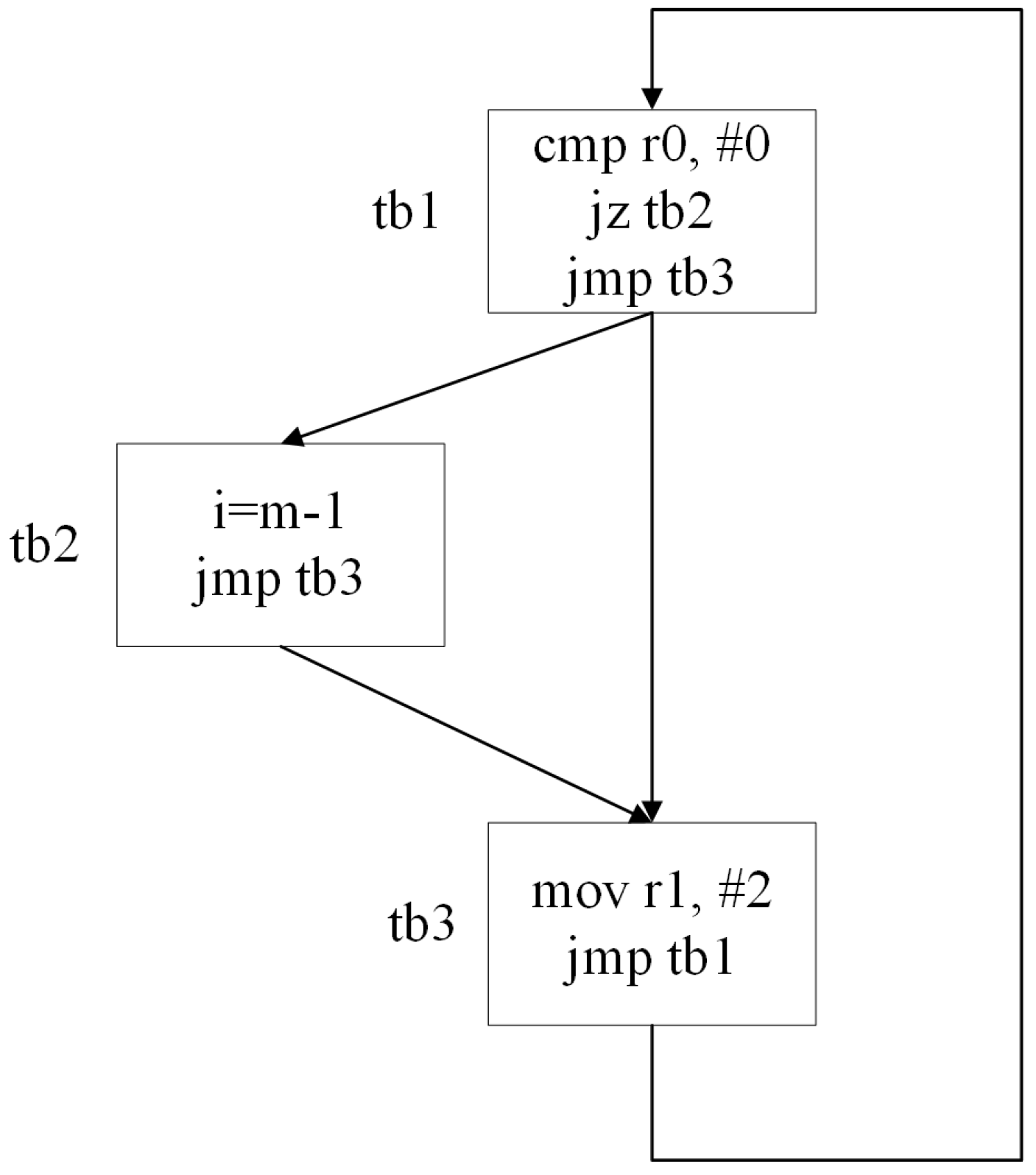

2.2. Branch Prediction

3. Branch Prediction-Based Dynamic–Static Binary Translation Method

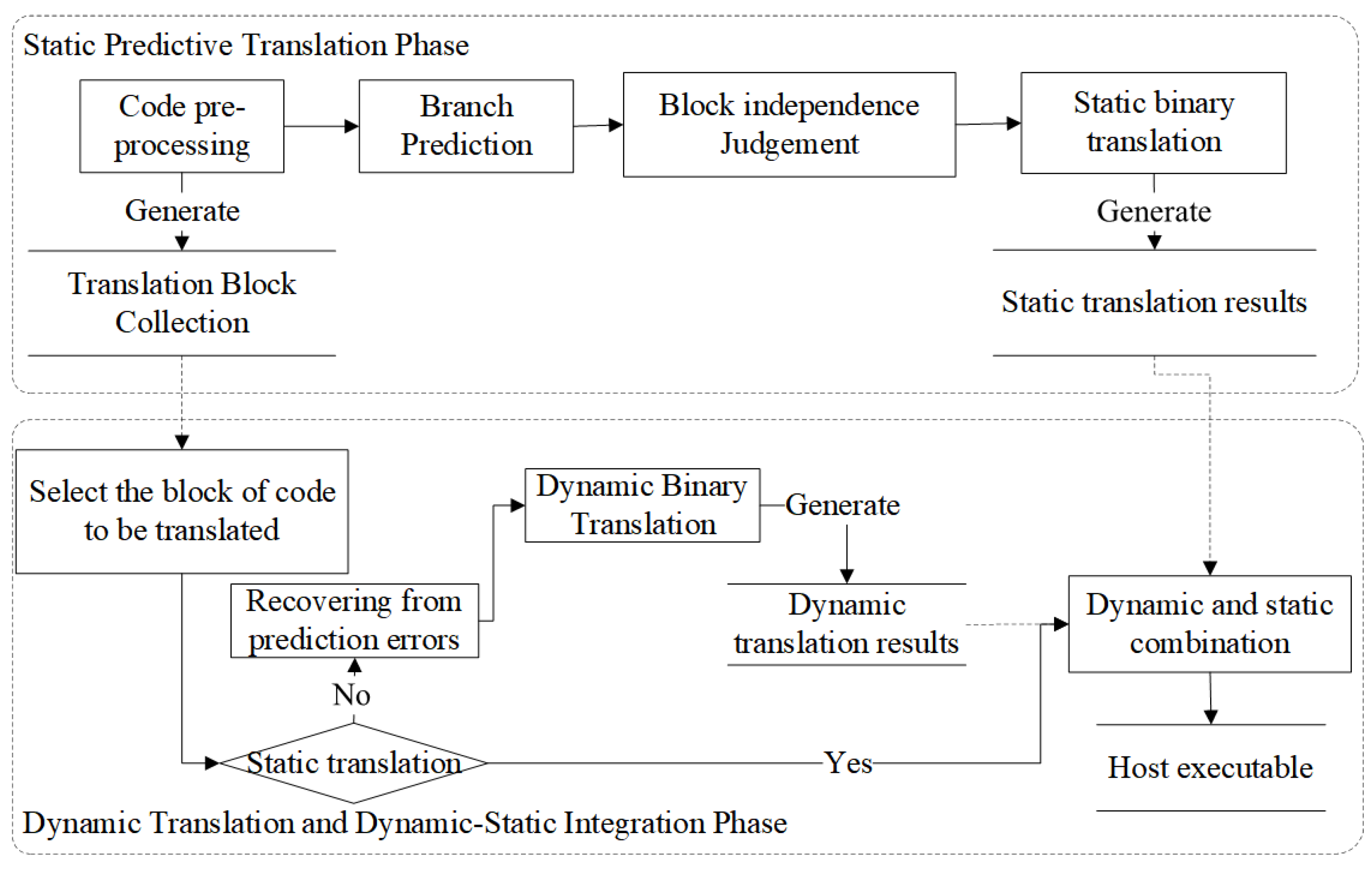

3.1. Methodology Overview

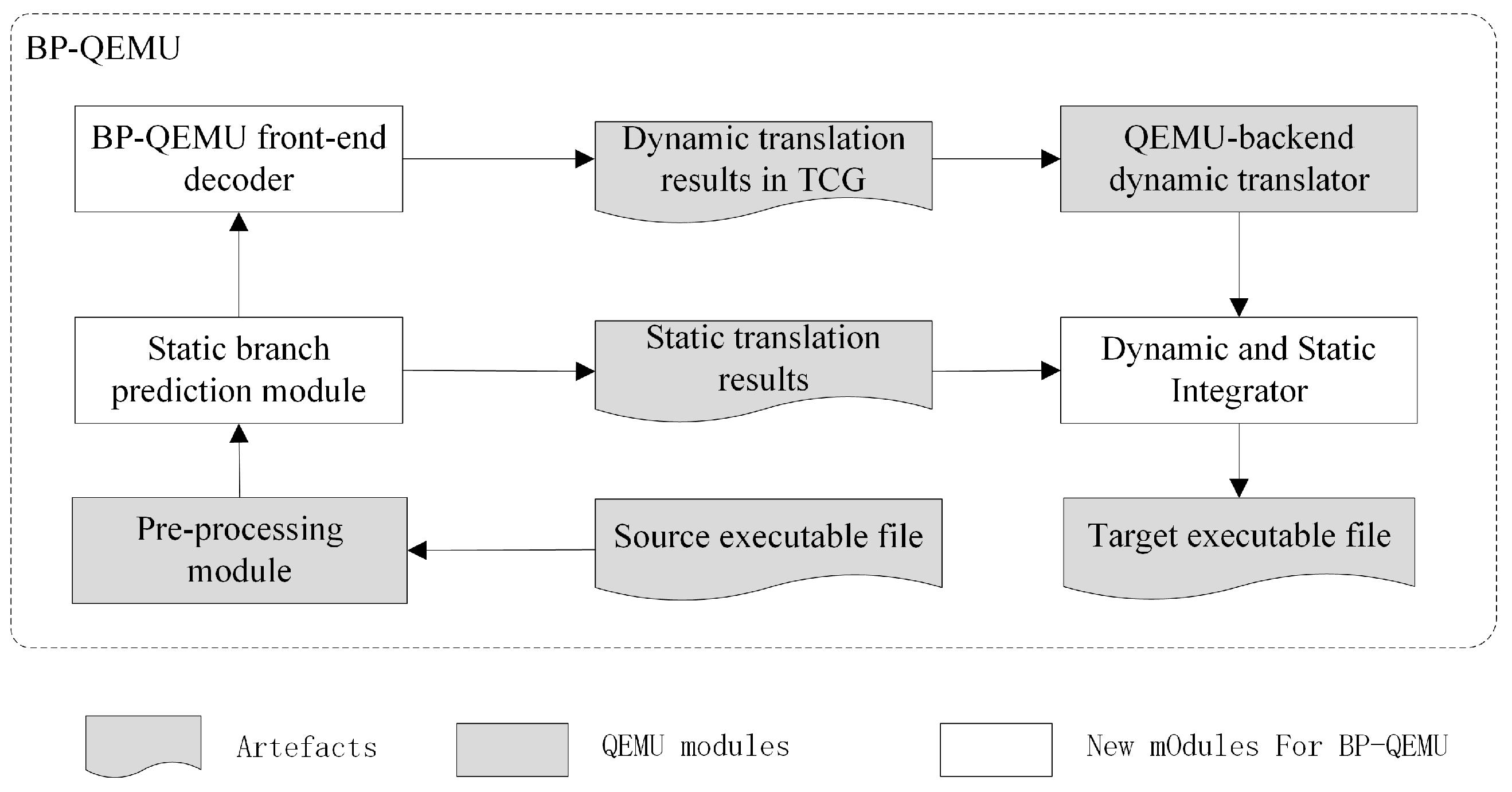

3.2. BP-QEMU System Architecture

3.3. Shared Memory Structure

3.4. Static Translation Module

| Algorithm 1 Judge_Independence |

| Require: Translation Block Collection = ,…,

|

3.5. Dynamic and Static Integration Module

3.5.1. Context Recovery Mechanism

| Algorithm 2 ExecStaticBlock_RestoreContext |

| Require: tb: a statically translated block, ShadowReg[0…16]: the array of shadow registers Ensure: env: dynamic translation context

|

3.5.2. Memory Optimization Mechanism

| Algorithm 3 StaticCache_Optimization |

| Require: tb: static translated block, real_pc

|

4. Experiment Analysis

4.1. Experimental Settings

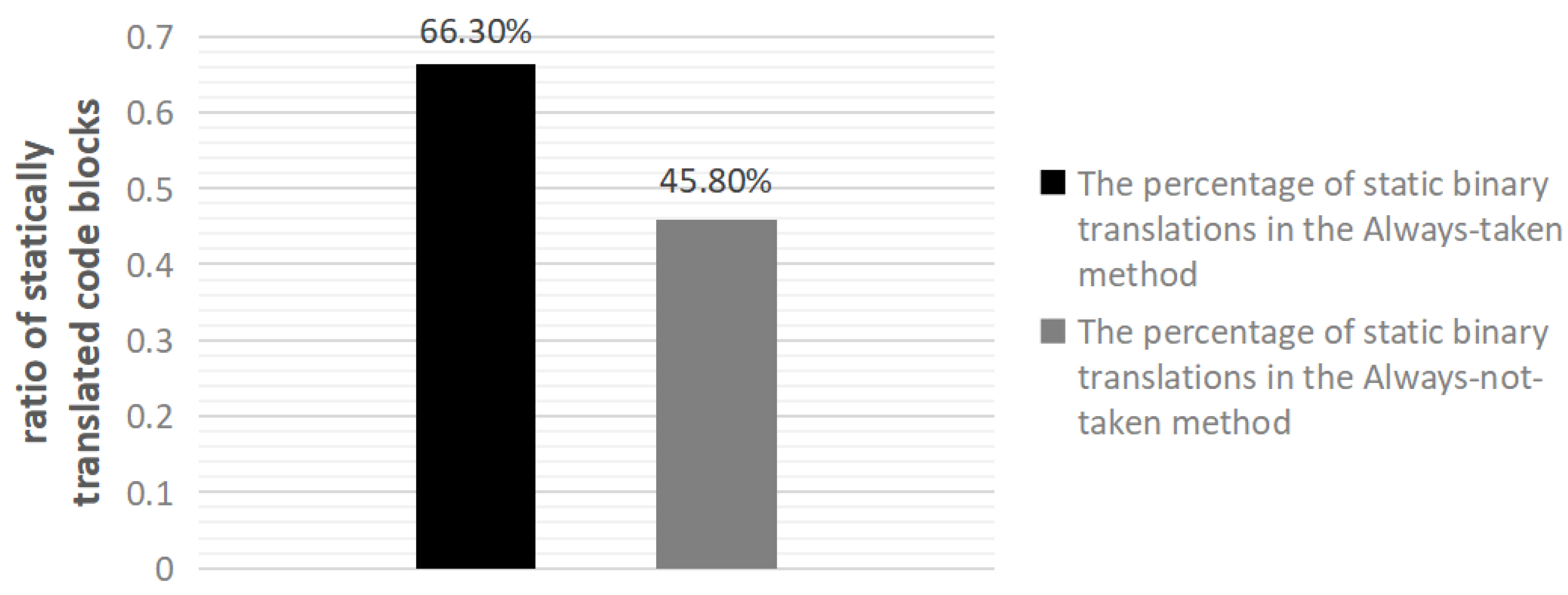

4.2. Correctness and Efficiency Experiments

4.3. Memory Consumption Experiments

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Altman, E.R.; Kaeli, D. Welcome to the opportunities of binary translation. Computer 2000, 33, 40–45. [Google Scholar] [CrossRef] [Green Version]

- Yarza, I.; Azkarate-Askatsua, M.; Onaindia, P.; Gruettner, K.; Ittershagen, P.; Nebel, W. Legacy software migration based on timing contract aware real-time execution environments. J. Syst. Softw. 2021, 172, 110849. [Google Scholar] [CrossRef]

- Chipounov, V.; Kuznetsov, V.; Candea, G. S2E: A platform for in-vivo multi-path analysis of software systems. ACM SIGPLAN Not. 2011, 46, 265–278. [Google Scholar] [CrossRef] [Green Version]

- Ebcioglu, K.; Altman, E.; Gschwind, M.; Sathaye, S. Dynamic binary translation and optimization. IEEE Trans. Comput. 2001, 50, 529–548. [Google Scholar] [CrossRef] [Green Version]

- Rocha, R.C.O.; Sprokholt, D.; Fink, M.; Gouicem, R.; Spink, T.; Chakraborty, S.; Bhatotia, P. Lasagne: A static binary translator for weak memory model architectures. In Proceedings of the 43rd ACM SIGPLAN International Conference on Programming Language Design and Implementation, San Diego, CA, USA, 13–17 June 2022; ACM: New York, NY, USA, 2022; pp. 888–902. [Google Scholar] [CrossRef]

- Wenzl, M.; Merzdovnik, G.; Ullrich, J.; Weippl, E. From hack to elaborate technique—A survey on binary rewriting. ACM Comput. Surv. 2019, 52, 1–37. [Google Scholar] [CrossRef] [Green Version]

- Di Federico, A.; Agosta, G. A jump-target identification method for multi-architecture static binary translation. In Proceedings of the International Conference on Compilers, Architectures and Synthesis for Embedded Systems, Pittsburgh, PA, USA, 2–7 October 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 1–10. [Google Scholar] [CrossRef] [Green Version]

- Hawkins, W.H.; Hiser, J.D.; Co, M.; Nguyen-Tuong, A.; Davidson, J.W. Zipr: Efficient static binary rewriting for security. In Proceedings of the 2017 47th Annual IEEEIFIP International Conference on Dependable Systems and Networks (DSN), Denver, CO, USA, 26–29 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 559–566. [Google Scholar] [CrossRef]

- Knorst, T.; Vicenzi, J.; Jordan, M.G.; Korol, G.; Beck, A.C.S.; Rutzig, M.B. An energy efficient multi-target binary translator for instruction and data level parallelism exploitation. Des. Autom. Embed. Syst. 2022, 26, 55–82. [Google Scholar] [CrossRef]

- Zhang, H.; Ren, M.; Lei, Y.; Ming, J. One size does not fit all: Security hardening of mips embedded systems via static binary debloating for shared libraries. In Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Lausanne, Switzerland, 28 February–4 March 2022; ACM: New York, NY, USA, 2022; pp. 255–270. [Google Scholar] [CrossRef]

- Chen, I.H.; King, C.T.; Chen, Y.H.; Lu, J.-M. Full System Emulation of Embedded Heterogeneous Multicores Based on QEMU. In Proceedings of the 2018 IEEE 24th International Conference on Parallel and Distributed Systems, Singapore, 11–13 December 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 771–778. [Google Scholar] [CrossRef]

- Gouicem, R.; Sprokholt, D.; Ruehl, J.; Rocha, R.C.O.; Spink, T.; Chakraborty, S.; Bhatotia, P. Risotto: A Dynamic Binary Translator for Weak Memory Model Architectures. In Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Vancouver, BC, Canada, 25–29 March 2023; ACM: New York, NY, USA, 2023; Volume 1, pp. 107–122. [Google Scholar] [CrossRef]

- NiWu, J.; Dong, J.; Fang, R.; Zhang, W. FADATest: Fast and adaptive performance regression testing of dynamic binary translation systems. In Proceedings of the 44th International Conference on Software Engineering, Pittsburgh, PA, USA, 25–27 May 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 896–908. [Google Scholar] [CrossRef]

- Kyle, S.; Böhm, I.; Franke, B.; Leather, N. Efficiently parallelizing instruction set simulation of embedded multi-core processors using region-based just-in-time dynamic binary translation. ACM SIGPLAN Not. 2012, 47, 21–30. [Google Scholar] [CrossRef] [Green Version]

- Fan, X.; Li, S.; Zhiying, W. Dual-Core Architecture for Dynamic Binary Translation System: Tradeoff between Frequency and Bandwidth. In Proceedings of the 2012 Fourth International Conference on Computational and Information Sciences, Chongqing, China, 17–19 August 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 989–992. [Google Scholar] [CrossRef]

- Altinay, A.; Nash, J.; Kroes, T.; Rajasekaran, P.; Zhou, D.; Dabrowski, A.; Gens, D.; Na, Y.; Volckaert, S.; Giuffrida, C.; et al. BinRec: Dynamic binary lifting and recompilation. In Proceedings of the Fifteenth European Conference on Computer Systems, Heraklion, Greece, 27–30 April 2020; ACM: New York, NY, USA, 2020; pp. 1–16. [Google Scholar] [CrossRef]

- Yin, L. Dynamic Binary Translation Modeling and Parallelization Research; University of Science and Technology of China: Hefei, China, 2013; Available online: https://kns.cnki.net/kcms2/article/abstract?v=3uoqIhG8C447WN1SO36whHG-SvTYjkCc7dJWN_daf9c2-IbmsiYfKmTpuhyNiwqGSQeMLSmFtTcRJ8SJu7cevoHvOwu2q71d&uniplatform=NZKPT (accessed on 5 November 2022).

- Sun, T.; Yang, Y.; Yang, H.; Haibing, G. Return Instruction Analysis and Optimization in Dynamic Binary Translation. In Proceedings of the 2009 Fourth International Conference on Frontier of Computer Science and Technology, Shanghai, China, 17–19 December 2009; IEEE: Piscataway, NJ, USA, 2010; pp. 435–440. [Google Scholar] [CrossRef]

- Liao, Y.; Sun, G.; Jiang, H.; Jin, G.; Chen, G. All registers direct mapping method in dynamic binary translation. Comput. Appl. Softw. 2011, 28, 21–24. [Google Scholar]

- Wang, J.; Pang, J.; Fu, L.; Yue, F.; Zhang, J. A binary translation backend registers allocation algorithm based on priority. In Proceddings of the Geo-Spatial Knowledge and Intelligence: 5th International Conference, GSKI 2017, Chiang Mai, Thailand, 8–10 December 2017; Revised Selected Papers, Part II 5; Springer: Singapore, 2018; pp. 414–425. [Google Scholar] [CrossRef]

- Faravelon, A.; Gruber, O.; Pétrot, F. Optimizing memory access performance using hardware assisted virtualization in retargetable dynamic binary translation. In Proceedings of the 2017 Euromicro Conference on Digital System Design (DSD), Vienna, Austria, 30 August–1 September 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 40–46. [Google Scholar] [CrossRef]

- Díaz, E.; Mateos, R.; Bueno, E.J.; Nieto, R. Enabling parallelized-QEMU for hardware/software co-simulation virtual platforms. Electronics 2021, 10, 759. [Google Scholar] [CrossRef]

- Qiang, S.; Xianglan, C.; Huaping, C. Optimization technique of redundant instructions elimination in dynamic binary translator QEMU. Comput. Appl. Softw. 2012, 29, 67–69. [Google Scholar]

- Wang, J.; Pang, J.; Liu, X.; Yue, F.; Tan, J.; Fu, L. Dynamic translation optimization method based on static pre-translation. IEEE Access 2019, 7, 21491–21501. [Google Scholar] [CrossRef]

- QEMU Sources and Documentations. Available online: https://www.qemu.org/ (accessed on 5 November 2022).

- Carvalho, H.; Nelissen, G.; Zaykov, P. mcQEMU: Time-Accurate Simulation of Multi-core platforms using QEMU. In Proceedings of the 2020 23rd Euromicro Conference on Digital System Design (DSD), Kranj, Slovenia, 26–28 August 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 81–88. [Google Scholar] [CrossRef]

- Bartholomew, D. Qemu: A multihost, multitarget emulator. Linux J. 2006, 2006, 3. Available online: https://www.ecb.torontomu.ca/~courses/coe518/LinuxJournal/elj2006-145-QEMU.pdf (accessed on 5 November 2022).

- Kersey, C.D. QEMU Internals. The Linux Users Group at Georgia Tech Meeting. 2009. Available online: https://lugatgt.org/content/qemu_internals/downloads/slides.pdf (accessed on 5 November 2022).

- Fabrice, B. QEMU, a fast and portable dynamic translator. In Proceedings of the Annual Conference on USENIX Annual Technical Conference, Berkeley, CA, USA, 10–15 April 2005; USENIX Association: Berkeley, CA, USA, 2005; p. 41. [Google Scholar]

- Smith, J.E. A study of branch prediction strategies. In Proceedings of the 25 Years of the International Symposia on Computer Architecture (Selected Papers), Washington, DC, USA, 12–14 May 1998; pp. 202–215. [Google Scholar] [CrossRef]

- Lin, C.K.; Tarsa, S.J. Branch Prediction Is Not a Solved Problem: Measurements, Opportunities, and Future Directions. In Proceedings of the 2019 IEEE International Symposium on Workload Characterization (IISWC), Orlando, FL, USA, 3–5 November 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 228–238. [Google Scholar]

- Chaudhary, P. Implemented static branch prediction schemes for the parallelism processors. In Proceedings of the 2019 International Conference on Machine Learning, Big Data, Cloud and Parallel Computing (COMITCon), Faridabad, India, 14–16 February 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 79–83. [Google Scholar] [CrossRef]

- Sparsh, M. A survey of techniques for dynamic branch prediction. Concurr. Comput. Pract. Exp. 2019, 31, e4666. [Google Scholar] [CrossRef] [Green Version]

- Ball, T.; Larus, J.R. Branch Prediction for Free. ACM SIGPLAN Not. 1993, 28, 300–313. [Google Scholar] [CrossRef]

- Wagner, T.A.; Maverick, V.; Graham, S.L.; Harrison, M.A. Accurate static estimators for program optimization. ACM SIGPLAN Not. 1994, 29, 85–96. [Google Scholar] [CrossRef]

- Bansal, S.; Aiken, A. Binary Translation Using Peephole Superoptimizers. In Proceedings of the 8th USENIX Symposium on Operating Systems Design and Implementation, San Diego, CA, USA, 8–10 December 2008; USENIX Association: Berkeley, CA, USA, 2008; pp. 177–192. [Google Scholar]

- Lu, S.B.; Pang, J.M.; Shan, Z.; Yue, F. Retargetable static binary translator based on QEMU. J. Zhejiang Univ. Sci. 2016, 50, 158–165. [Google Scholar] [CrossRef]

| Variables | Notes |

|---|---|

| tb_predict_pc | PC pointer to the predicted next TB block |

| tb_size | The TB block size |

| tb_continuous_failures | Count of consecutive failures of tb_predict_pc |

| tb_jump_valid | The validity of the jump address tb_predict_pc |

| tb_jumps | Possible jump addresses after the TB block |

| tb_translated | The TB block is translated or not |

| tb_independence | Data independence between the TB block and the next one |

| Configuration | Host Platform | Target Platform |

|---|---|---|

| OS | Windows10 | No operating system |

| CPU | Intel(R) Core(TM) i7-7700HQ CPU@2.80 GHz | CortexA9 |

| Compiler | Gcc-5.4.1 | Gcc-5.4.1 |

| Frequency | 2.80GHz | 1.4GHz |

| Memory | 16.0 GB | 512 MB |

| Test Case | Function |

|---|---|

| List search, sorting, adding, and deleting operations | |

| Matrix operator program | |

| State machine console application | |

| CRC calculation program | |

| The main function |

| Test Number | Run Score of QEMU | Run Score of BP-QEMU with Always-Taken Predictor | Boost Ratio | Run Score of BP-QEMU with Always-Not-Taken Predictor | Boost Ratio |

|---|---|---|---|---|---|

| 1 | 1954 | 2191 | 12% | 2036 | 4.2% |

| 2 | 1912 | 2253 | 17.8% | 2064 | 7.9% |

| 3 | 1949 | 2175 | 11.6% | 2027 | 4% |

| 4 | 1950 | 2196 | 12.6% | 2103 | 7.8% |

| 5 | 1991 | 2231 | 12.1% | 2114 | 6.2% |

| Average value | 1951 | 2211 | 13.3% | 2069 | 6% |

| Test Case | Code Size | Code Description | Time for Static Translation | Time for Dynamic Translation and Execution | Static Translation Time as a Percentage of Total Time |

|---|---|---|---|---|---|

| case_A | 122KB | The core_list_join test item in CoreMark | 0.4 s | 7.5 s | 5.1% |

| case_B | 1327KB | All test items in CoreMark | 0.6 s | 45.6 s | 1.3% |

| Test Case | Code Size | QEMU | BP-QEMU without Memory Optimization | BP-QEMU with Memory Optimization |

|---|---|---|---|---|

| case_A | 122 KB | 15.2 MB | 16.5 MB | 16 MB |

| case_B | 1327 KB | 18.8 MB | 20.1 MB | 19.5 MB |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, L.; Wu, Y.; Li, L.; Zhang, C.; Tang, J. A Dynamic and Static Binary Translation Method Based on Branch Prediction. Electronics 2023, 12, 3025. https://doi.org/10.3390/electronics12143025

Sun L, Wu Y, Li L, Zhang C, Tang J. A Dynamic and Static Binary Translation Method Based on Branch Prediction. Electronics. 2023; 12(14):3025. https://doi.org/10.3390/electronics12143025

Chicago/Turabian StyleSun, Lianshan, Yanjin Wu, Linxiangyi Li, Changbin Zhang, and Jingyan Tang. 2023. "A Dynamic and Static Binary Translation Method Based on Branch Prediction" Electronics 12, no. 14: 3025. https://doi.org/10.3390/electronics12143025

APA StyleSun, L., Wu, Y., Li, L., Zhang, C., & Tang, J. (2023). A Dynamic and Static Binary Translation Method Based on Branch Prediction. Electronics, 12(14), 3025. https://doi.org/10.3390/electronics12143025