Design of a Power Regulated Circuit with Multiple LDOs for SoC Applications

Abstract

:1. Introduction

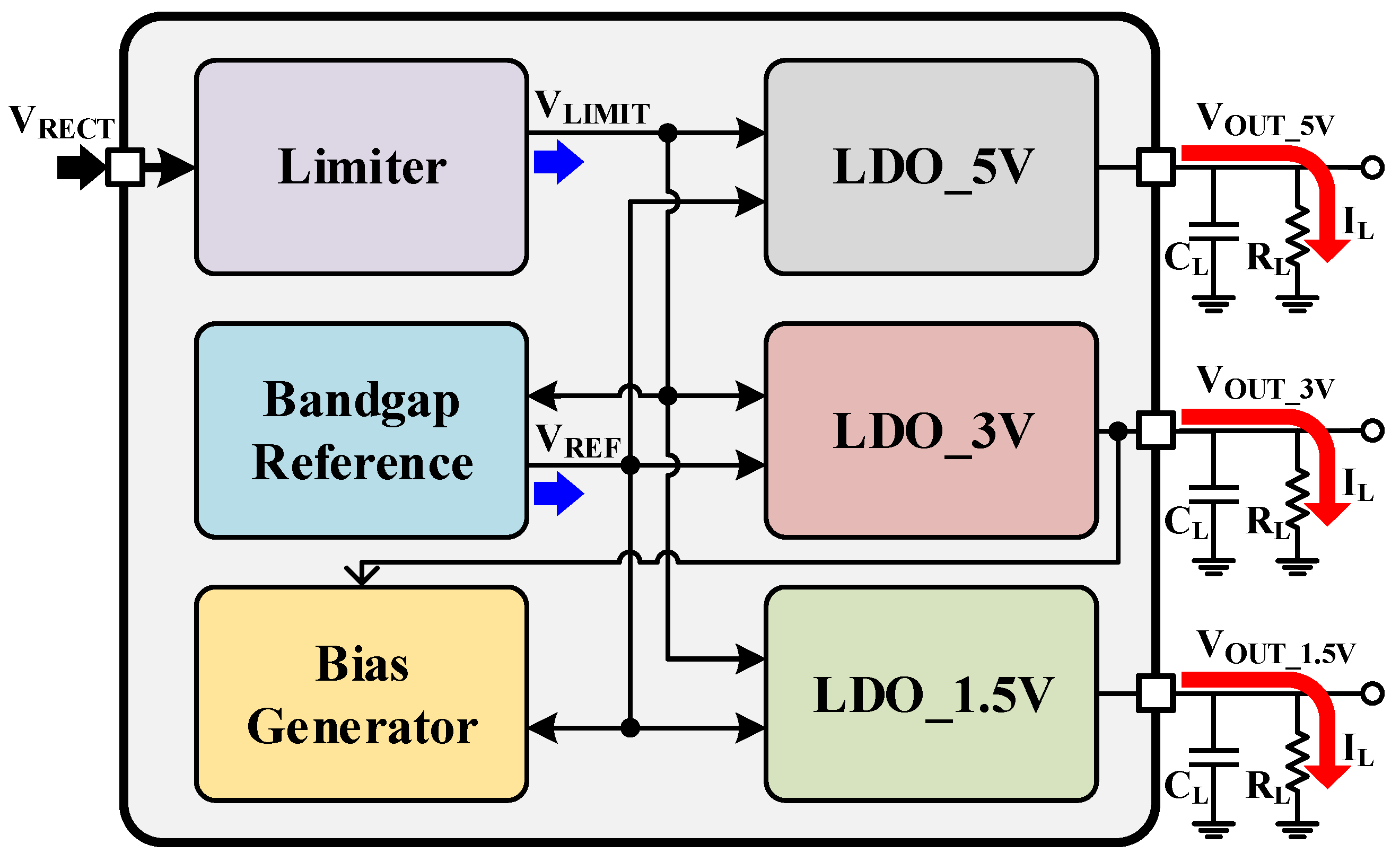

2. Proposed Power Regulated Circuit (PRC)

3. Circuit Description

3.1. Limiter Design

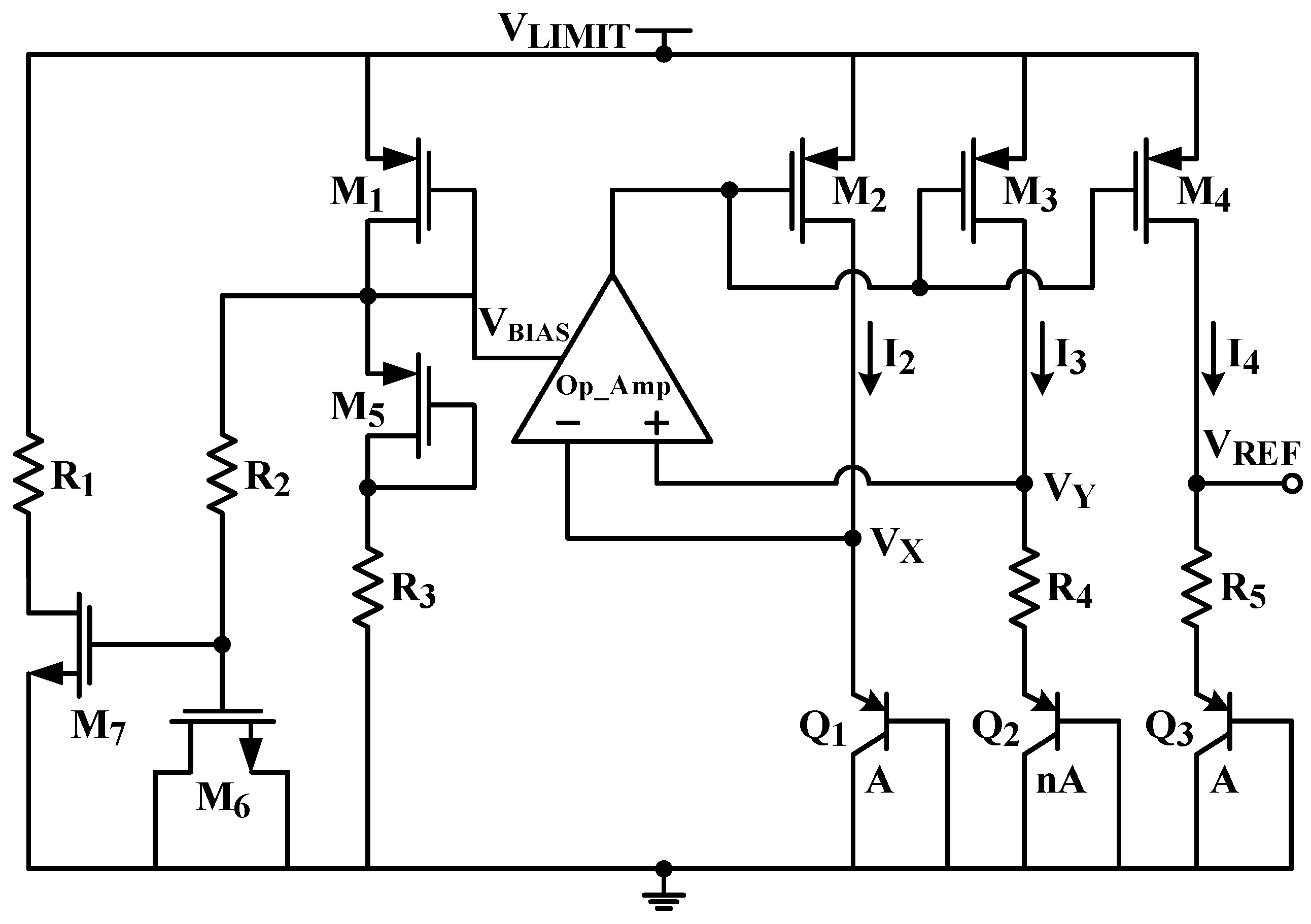

3.2. Bandgap Reference (BGR) Design

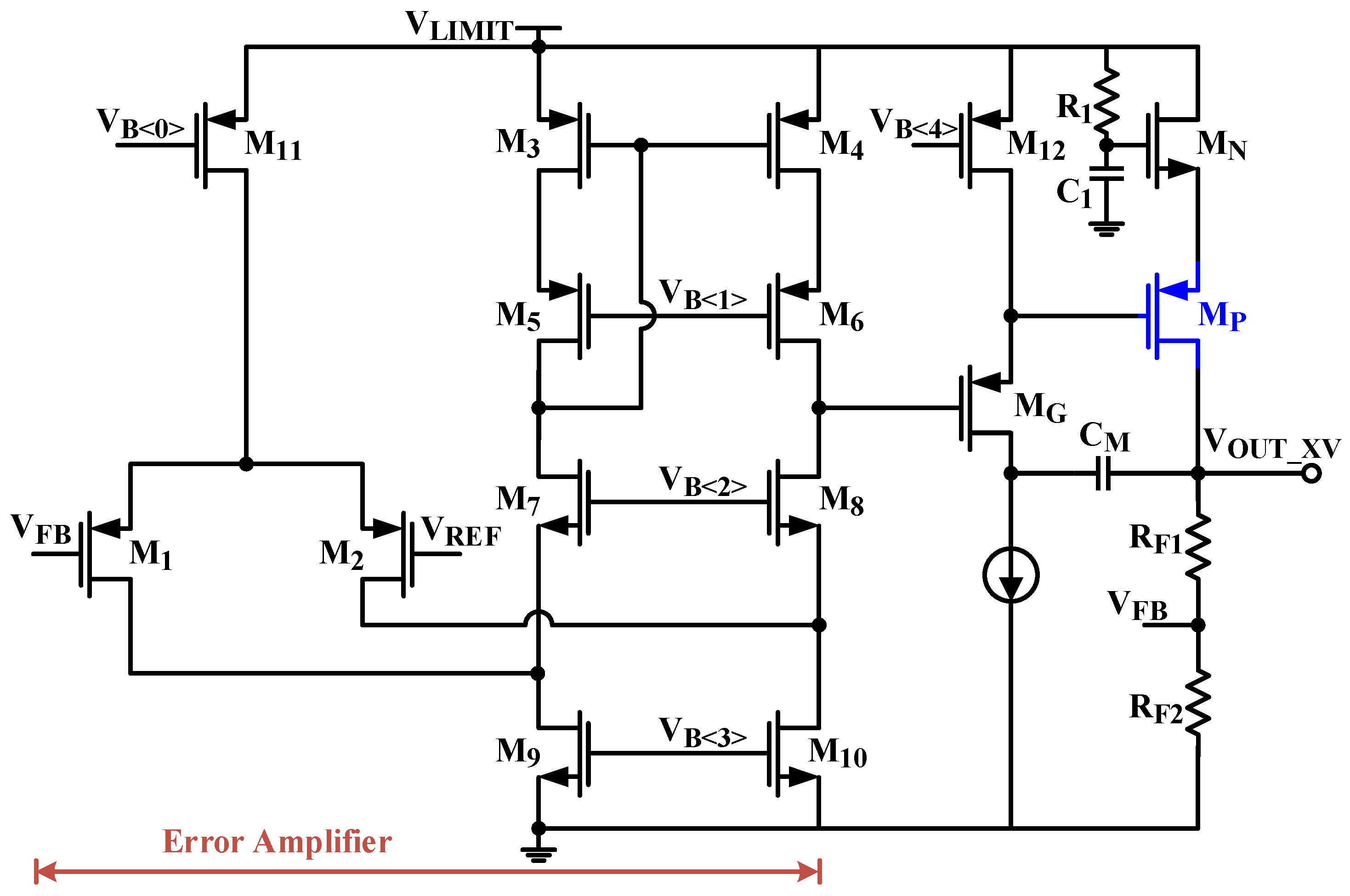

3.3. Low-Dropout Regulator (LDO) Design

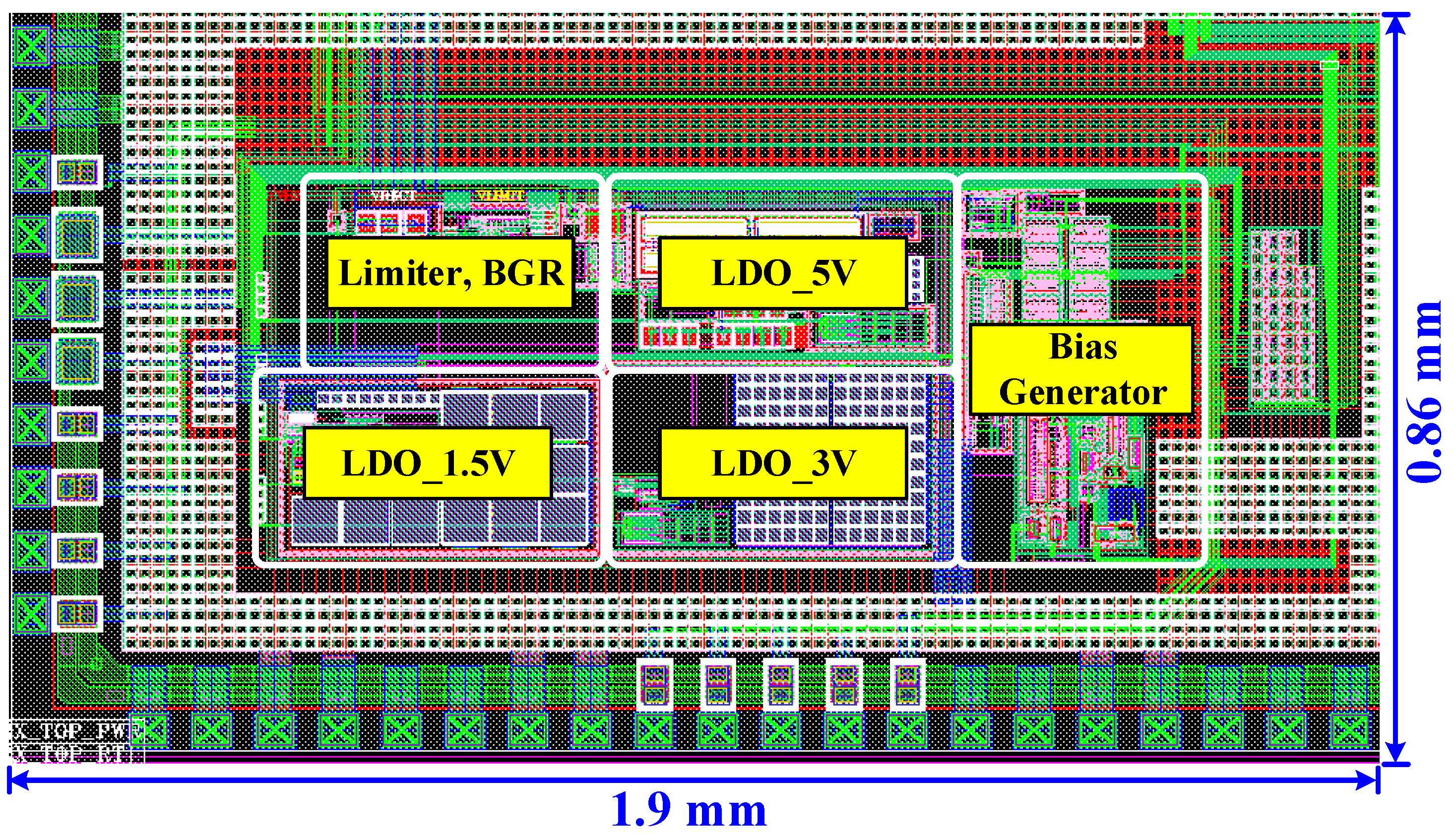

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Hekal, S.; Abdel-Rahman, A.B.; Jia, H.; Allam, A.; Barakat, A.; Pokharel, R.K. A Novel Technique for Compact Size Wireless Power Transfer Applications Using Defected Ground Structures. IEEE Trans. Microw. Theory Technol. 2017, 65, 591–599. [Google Scholar] [CrossRef]

- Jonah, O.; Georgakopoulos, S.V. Wireless Power Transfer in Concrete via Strongly Coupled Magnetic Resonance. IEEE Trans. Antennas Propag. 2013, 61, 1378–1384. [Google Scholar] [CrossRef]

- Yalong, Z.; Xueliang, H.; Jiaming, Z.; Linlin, T. Design of wireless power supply system for the portable mobile device. In Proceedings of the 2013 IEEE International Wireless Symposium (IWS), Beijing, China, 14–18 April 2013; pp. 1–4. [Google Scholar]

- Huh, J.; Lee, S.W.; Lee, W.Y.; Cho, G.H.; Rim, C.T. Narrow-Width Inductive Power Transfer System for Online Electrical Vehicles. IEEE Trans. Power Electron. 2011, 26, 3666–3679. [Google Scholar] [CrossRef]

- Wang, G.; Liu, W.; Sivaprakasam, M.; Kendir, G.A. Design and analysis of an adaptive transcutaneous power telemetry for biomedical implants. IEEE Trans. Circuits Syst. I Reg. Papers. 2005, 52, 2109–2117. [Google Scholar] [CrossRef]

- Kalwar, K.; Aamir, M.; Mekhilef, S. Inductively coupled power transfer (ICPT) for electric vehicle charging—A review. Renew. Sustain. Energy Rev. 2015, 47, 62–475. [Google Scholar] [CrossRef]

- Wireless Power Consortium. System Description, Wireless Power Transfer—Vol. I: Low Power, Part 1: Interface Definition, Version 1.0; Wireless Power Consortium: Piscataway, NJ, USA, 2010. [Google Scholar]

- Texas Instrument. Introduction to Wireless Power; Texas Instrument: Dallas, TX, USA, 2012; pp. 1–49. [Google Scholar]

- Tseng, R.; von Novak, B.; Shevde, S.; Grajski, K.A. Introduction to the alliance for wireless power loosely-coupled wireless power transfer system specification version 1.0. In Proceedings of the 2013 IEEE Wireless Power Transfer (WPT), Perugia, Italy, 15–16 May 2013; pp. 79–83. [Google Scholar]

- Park, H.G.; Jang, J.H.; Kim, H.J.; Park, Y.J.; Oh, S.; Pu, Y.; Lee, K.Y. A Design of a Wireless Power Receiving Unit With a High-Efficiency 6.78-MHz Active Rectifier Using Shared DLLs for Magnetic-Resonant A4WP Applications. IEEE Trans. Power Electron. 2016, 31, 4484–4498. [Google Scholar] [CrossRef]

- Oh, S.J.; Khan, D.; Jang, B.G.; Basim, M.; Asif, M.; Ali, I.; Lee, K.Y. A 15-W Quadruple-Mode Reconfigurable Bidirectional Wireless Power Transceiver With 95% System Efficiency for Wireless Charging Applications. IEEE Trans. Power Electron. 2021, 36, 3814–3827. [Google Scholar] [CrossRef]

- Park, Y.J.; Jang, B.; Park, S.M.; Ryu, H.C.; Oh, S.J.; Kim, S.Y.; Lee, K.Y. A Triple-Mode Wireless Power-Receiving Unit With 85.5% System Efficiency for A4WP, WPC, and PMA Applications. IEEE Trans. Power Electron. 2018, 33, 3141–3156. [Google Scholar] [CrossRef]

- Park, C.; Onabajo, M.; Silva-Martinez, J. External Capacitor-Less Low Drop-Out Regulator With 25 dB Superior Power Supply Rejection in the 0.4–4 MHz Range. IEEE J. Solid-State Circuits 2014, 49, 486–501. [Google Scholar] [CrossRef]

- Keikhosravy, K.; Mirabbasi, S. A 0.13-µm CMOS Low-Power Capacitor-Less LDO Regulator Using Bulk-Modulation Technique. IEEE Trans. Circuits Syst I Reg. Papers 2014, 61, 3105–3114. [Google Scholar] [CrossRef]

- Maity, A.; Patra, A. A Single-Stage Low-Dropout Regulator with a Wide Dynamic Range for Generic Applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2117–2127. [Google Scholar] [CrossRef]

- Khan, D.; Abbasizadeh, H.; Khan, Z.H.N.; Park, Y.; Lee, K. Design of a capacitor-less LDO with high PSRR for RF energy harvesting applications. In Proceedings of the 2017 International SoC Design Conference (ISOCC), Seoul, Korea, 5–8 November 2017; pp. 202–203. [Google Scholar]

- Asif, M.; Ali, I.; Khan, D.; Rehman, M.R.U.; Basim, M.; Pu, Y.G.; Lee, K.Y. A High Performance Adaptive Digital LDO Regulator with Dithering and Dynamic Frequency Scaling for IoT Applications. IEEE Access 2020, 8, 32200–132211. [Google Scholar] [CrossRef]

- El-Nozahi, M.; Amer, A.; Torres, J.; Entesari, K.; Sanchez-Sinencio, E. High PSR Low Drop-Out Regulator With Feed-Forward Ripple Cancellation Technique. IEEE J. Solid-State Circuits 2010, 45, 565–577. [Google Scholar] [CrossRef]

- Yang, B.; Drost, B.; Rao, S.; Hanumolu, P.K. A high-PSR LDO using a feedforward supply-noise cancellation technique. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 19–21 September 2011; pp. 1–4. [Google Scholar]

- Heng, S.; Pham, C. A Low-Power High-PSRR Low-Dropout Regulator with Bulk-Gate Controlled Circuit. IEEE Trans. Circuits Syst. II Exp. Briefs 2010, 57, 245–249. [Google Scholar] [CrossRef]

- Chen, B.H.; Wu, T.Y.; Zheng, K.L.; Chen, K.H.; Lin, Y.H.; Lin, S.R.; Tsai, T.Y. A Feedforward Controlled Digital Low-Dropout Regulator With Weight Redistribution Algorithm and Body Voltage Control for Improving Line Regulation With 99.99% Current Efficiency and 0.5-mV Output Voltage Ripple. IEEE J. Solid-State Circuits 2022, 1–11. [Google Scholar] [CrossRef]

- Song, Y.; Oh, J.; Cho, S.-Y.; Jeong, D.-K.; Park, J.-E. A Fast Droop-Recovery Event-Driven Digital LDO With Adaptive Linear/Binary Two-Step Search for Voltage Regulation in Advanced Memory. IEEE Trans. Power Electron. 2022, 37, 1189–1194. [Google Scholar] [CrossRef]

- Kang, J.-G.; Park, J.; Jeong, M.-G.; Yoo, C. Digital Low-Dropout Regulator with Voltage-Controlled Oscillator Based Control. IEEE Trans. Power Electron. 2022, 37, 6951–6961. [Google Scholar] [CrossRef]

- Krolak, D.; Plojhar, J.; Horsky, P. An Automotive Low-Power EMC Robust Brokaw Bandgap Voltage Reference. IEEE Trans. Electromagn. Comp. 2020, 62, 2277–2284. [Google Scholar] [CrossRef]

- Yu, C.; Siek, L. An Area-Efficient Current-Mode Bandgap Reference with Intrinsic Robust Start-Up Behavior. IEEE Trans. Circuits Syst. II Exp. Briefs 2015, 62, 937–941. [Google Scholar] [CrossRef]

- De Vita, G.; Iannaccone, G. A Sub-1-V, 10 ppm/ C, Nano power Voltage Reference Generator. IEEE J. Solid-State Circuits 2007, 42, 1536–1542. [Google Scholar] [CrossRef]

- Sanborn, K.; Ma, D.; Ivanov, V. A sub-1-V low noise bandgap voltage reference. IEEE J. Solid-State Circuits 2007, 42, 2466–2481. [Google Scholar] [CrossRef]

- Chen, K.; Petruzzi, L.; Hulfachor, R.; Onabajo, M. A 1.16-V 5.8-to-13.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit With a Shared Offset-Cancellation Method for Internal Amplifiers. IEEE J. Solid-State Circuits 2021, 56, 267–276. [Google Scholar] [CrossRef]

- Rezavi, B. Design of Analog CMOS Integrated Circuits, 2nd ed.; McGraw Hill: New York, NY, USA, 2015. [Google Scholar]

| Parameters | This Work | [13] | [14] | [15] | [17] |

|---|---|---|---|---|---|

| Technology (nm) | 130 | 180 | 130 | 180 | 130 |

| Type | Analog | Analog | Analog | Analog | Digital |

| Internal BGR | Yes | No | No | No | No |

| Input Voltage (V) | 5.3 | 1.8 | 1.2 | 1.5 | 0.5–1.2 |

| Output Voltage (V) | 1.24 *, 5 **, 3 ***, 1.5 **** | LDO: 1.6 | LDO: 1 | LDO: 1.2 | LDO: 0.45–1.14 |

| Maximum Load (mA) | 300 **, 100 ***, 100 **** | 50 | 5 | 100 | 10 |

| Quiescent Current (µA) | 38 **, 18.8 ***, 21.5 **** | 55 | 99.04 | 2.4–242 | 24 |

| Load Regulation (mV/mA) | 0.43 **, 0.7 ***, 0.28 **** | 0.14 | 10 | 0.14 | 10 |

| Line Regulation (mV/V) | 25 **, 46.7 ***, 59 **** | 75 | N/A | 12.3 | 3.5 |

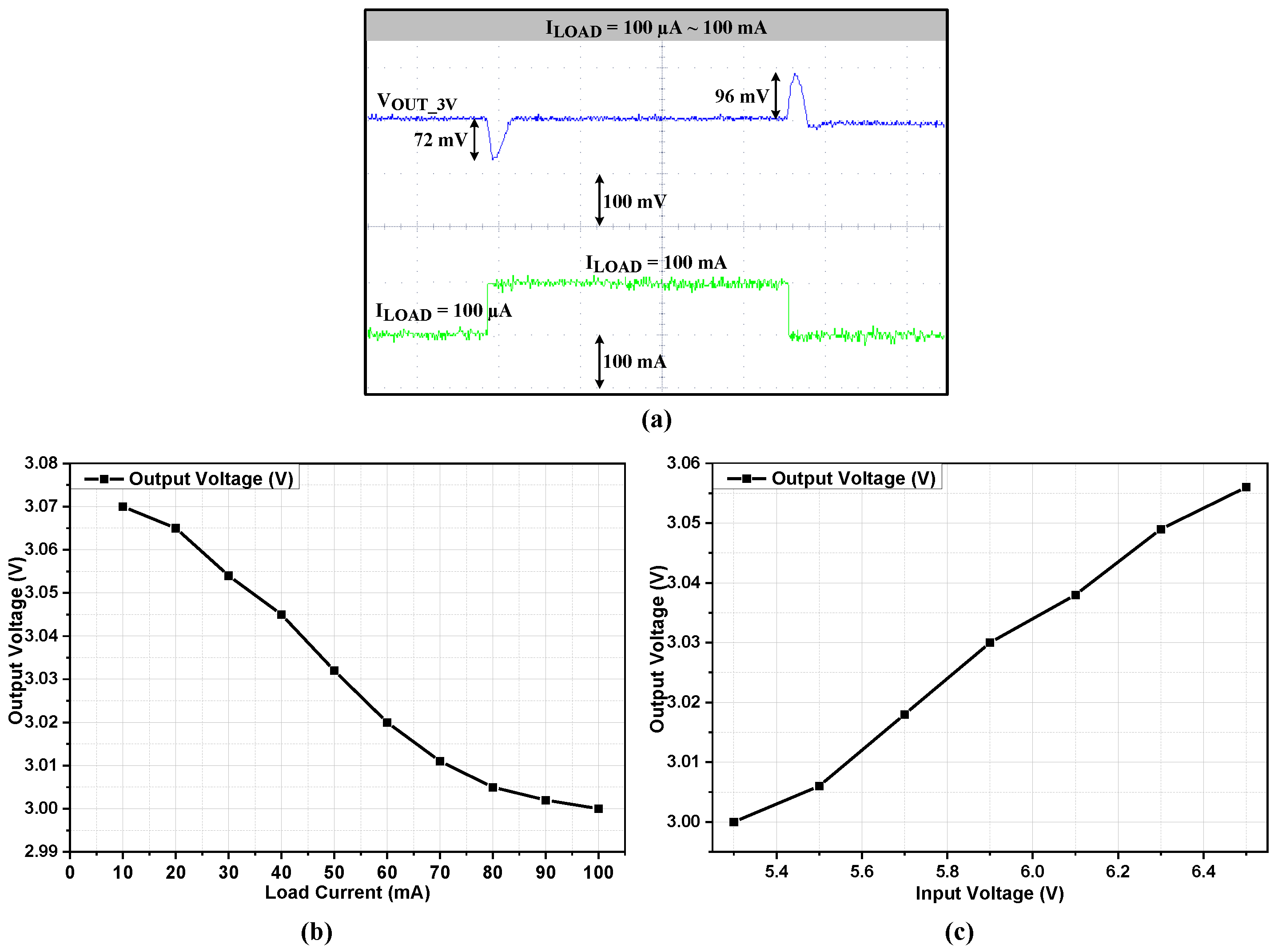

| Undershoot (mV) | 88 **, 72 ***, 62 **** | 80 | N/A | 125 | 48 |

| Overshoot (mV) | 126 **, 96 ***, 84 **** | 120 | N/A | 65 | 24 |

| Load Capacitor (µF) | 1 | 0.0001 | N/A | 1 | 0.0001 |

| Area (mm) | 1.634 | 0.14 | 0.00245 | 0.03 | 0.114 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Khan, D.; Basim, M.; Ain, Q.u.; Shah, S.A.A.; Shehzad, K.; Verma, D.; Lee, K.-Y. Design of a Power Regulated Circuit with Multiple LDOs for SoC Applications. Electronics 2022, 11, 2774. https://doi.org/10.3390/electronics11172774

Khan D, Basim M, Ain Qu, Shah SAA, Shehzad K, Verma D, Lee K-Y. Design of a Power Regulated Circuit with Multiple LDOs for SoC Applications. Electronics. 2022; 11(17):2774. https://doi.org/10.3390/electronics11172774

Chicago/Turabian StyleKhan, Danial, Muhammad Basim, Qurat ul Ain, Syed Adil Ali Shah, Khuram Shehzad, Deeksha Verma, and Kang-Yoon Lee. 2022. "Design of a Power Regulated Circuit with Multiple LDOs for SoC Applications" Electronics 11, no. 17: 2774. https://doi.org/10.3390/electronics11172774

APA StyleKhan, D., Basim, M., Ain, Q. u., Shah, S. A. A., Shehzad, K., Verma, D., & Lee, K.-Y. (2022). Design of a Power Regulated Circuit with Multiple LDOs for SoC Applications. Electronics, 11(17), 2774. https://doi.org/10.3390/electronics11172774