An Efficient Carrier Synchronization Scheme for Demodulation Systems

Abstract

:1. Introduction

2. Conventional Carrier Synchronization Algorithm

2.1. Conventional Carrier Synchronization Scheme

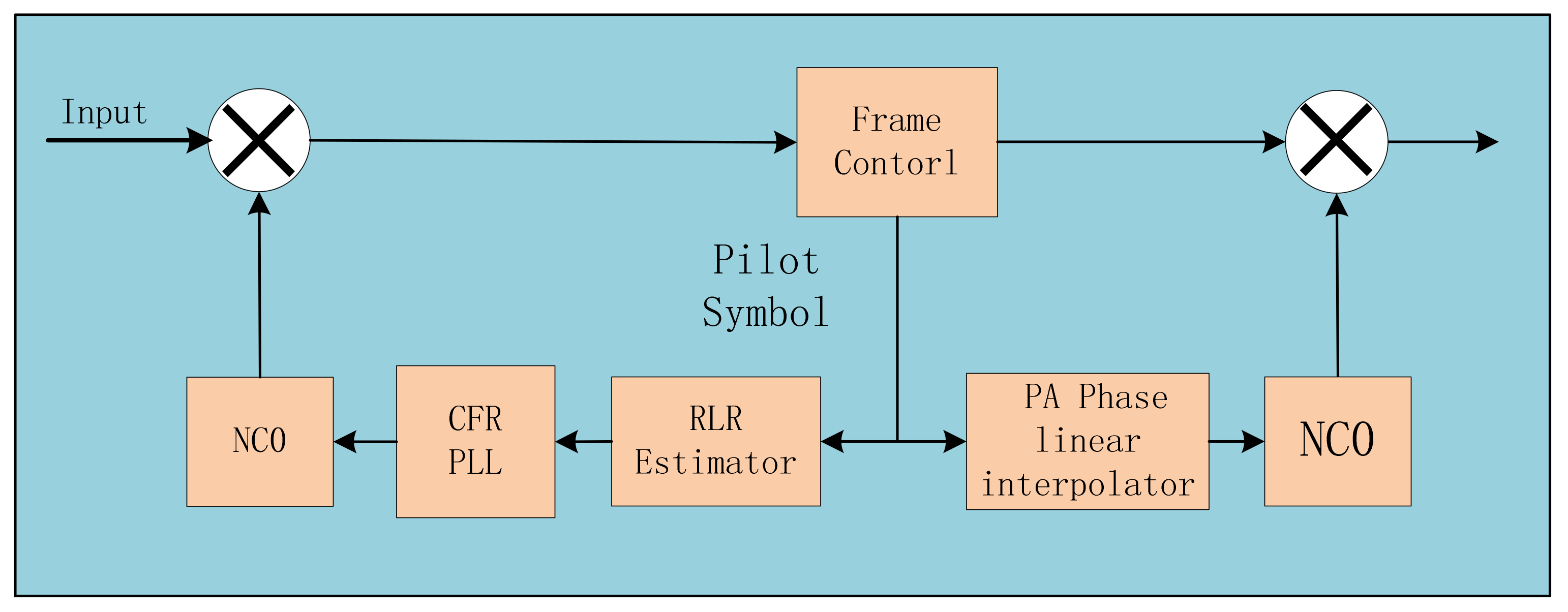

2.2. Proposed Carrier Synchronization Scheme

3. Proposed Carrier Synchronization Algorithm

3.1. Frame Header Detection Algorithm

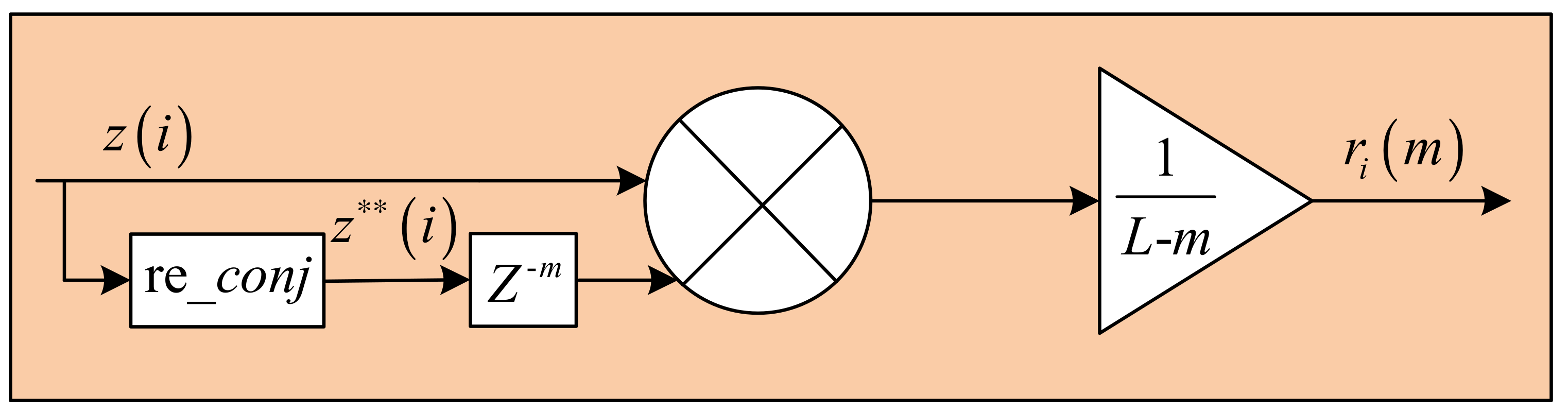

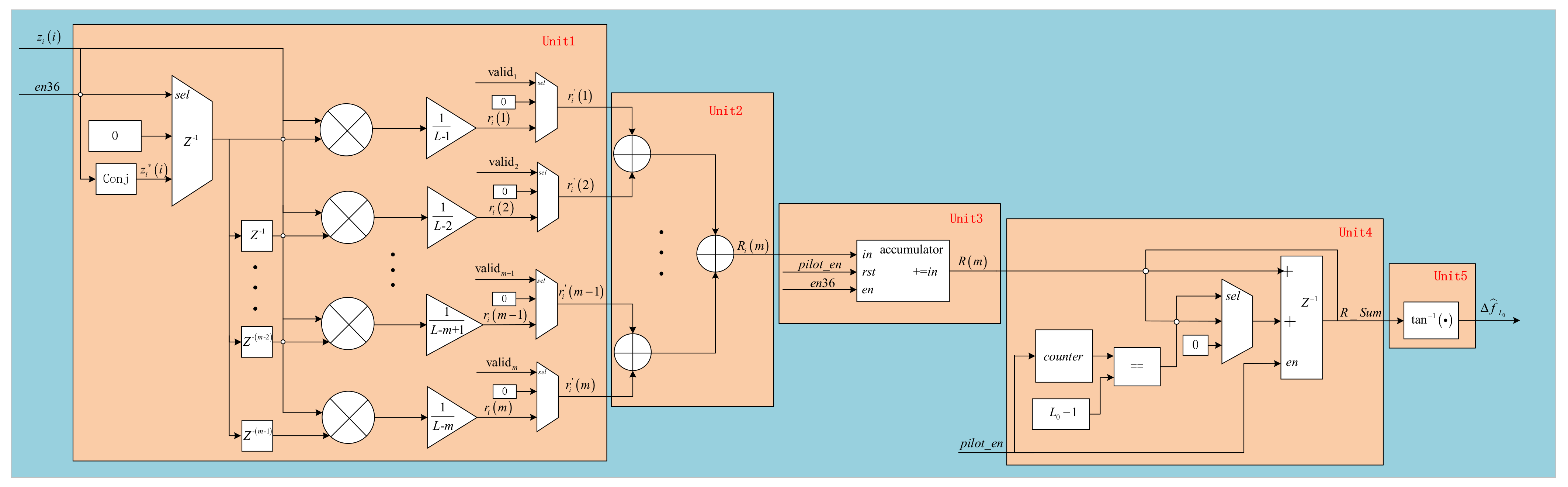

3.2. Carrier Frequency Recovery Algorithm

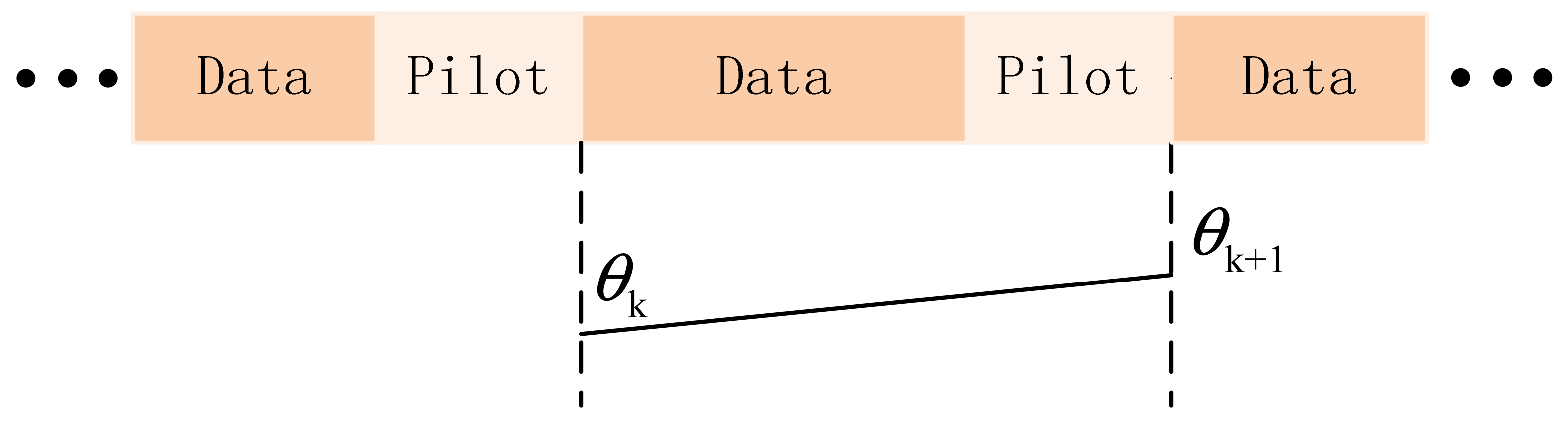

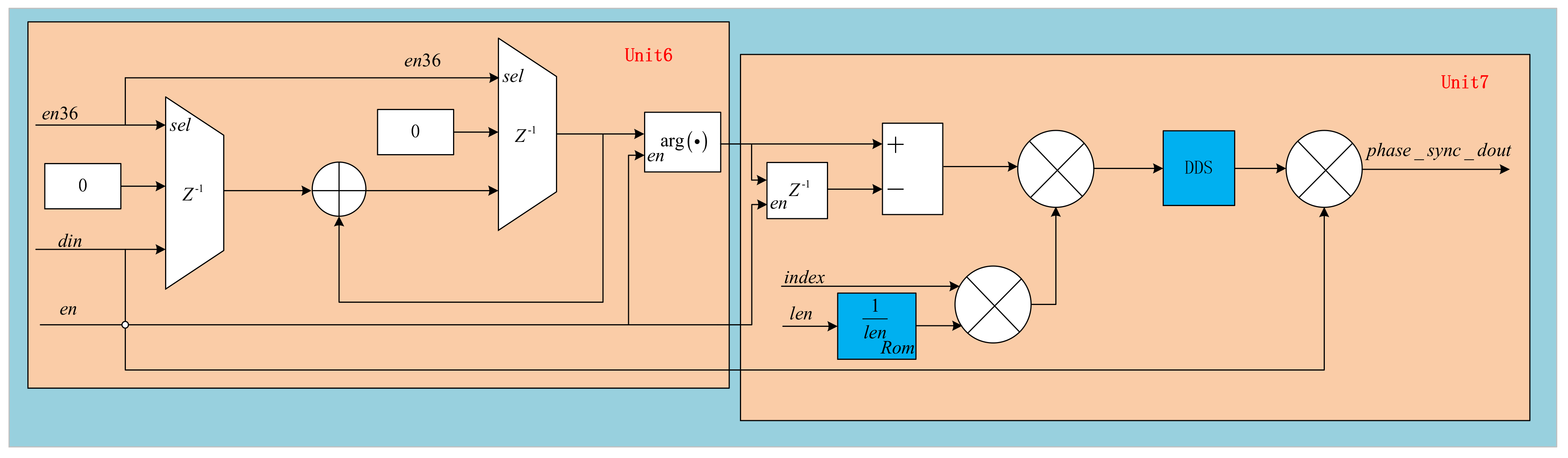

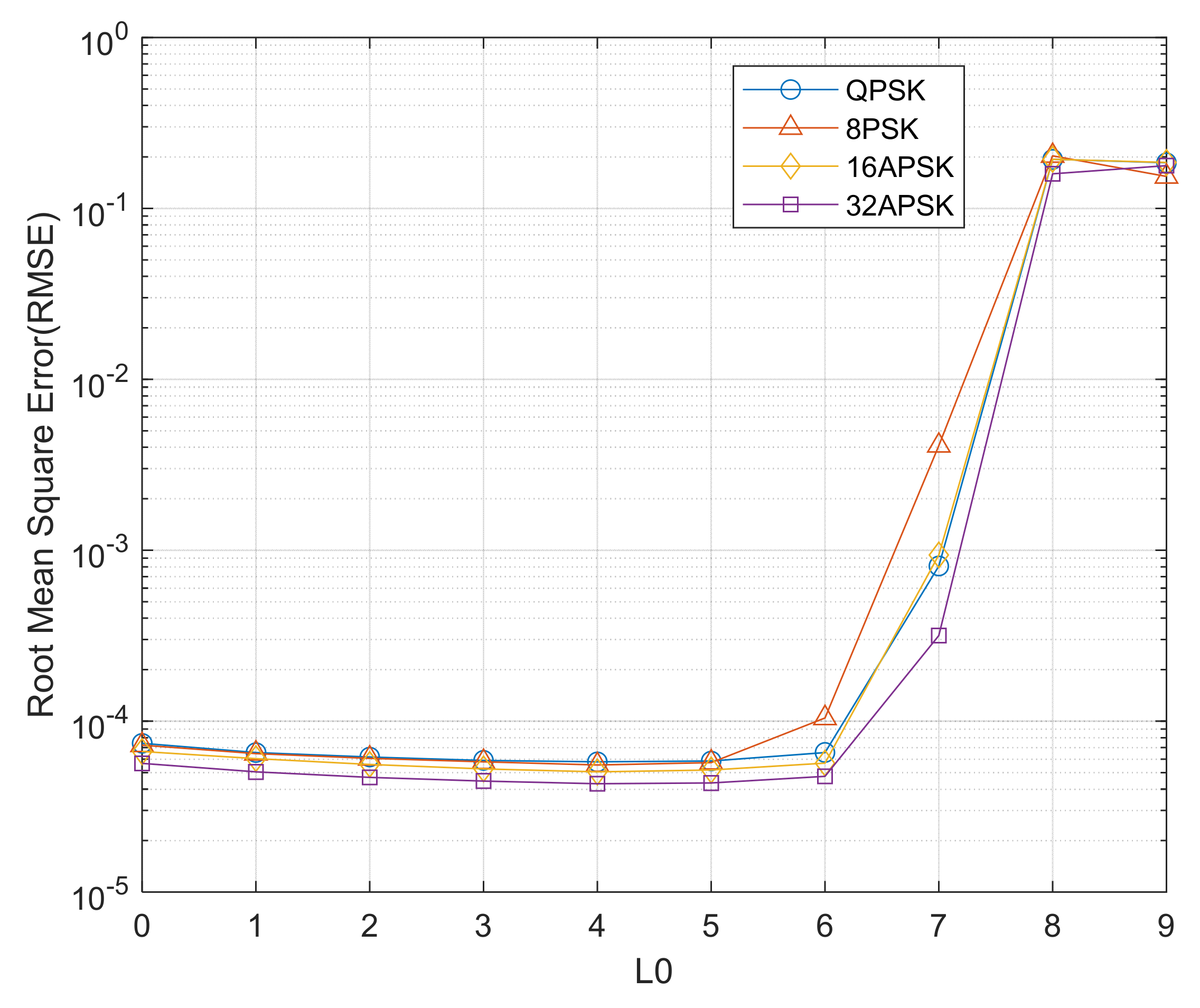

3.3. Carrier Phase Recovery Algorithm

4. Carrier Synchronization Scheme Simulation and Hardware Implementation

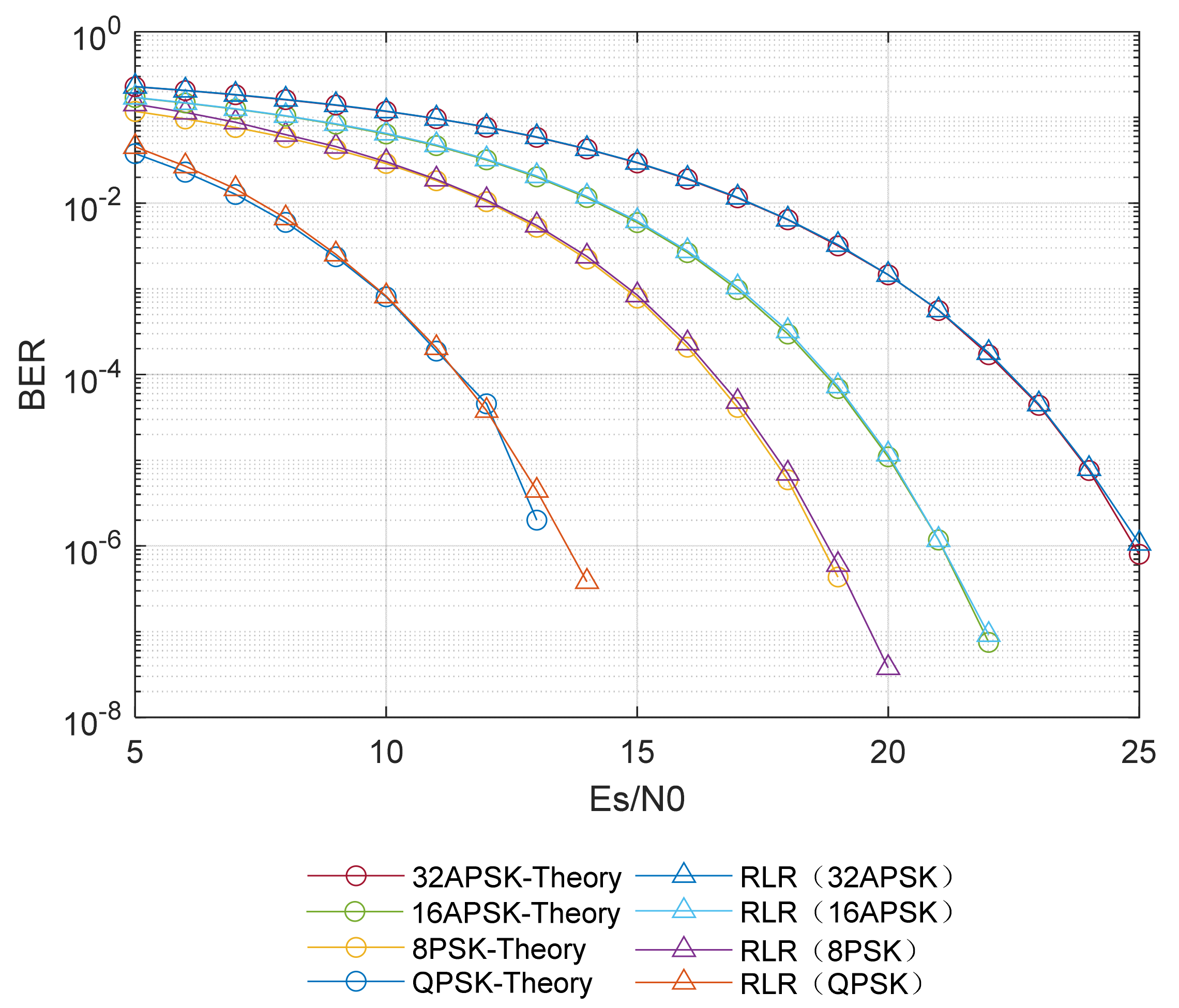

4.1. Carrier Synchronization Scheme Simulation and Performance Analysis

4.2. Carrier Synchronization Scheme Hardware Implementation

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Park, J.W.; Sunwoo, M.H.; Kim, P.S.; Chang, D.I. An Efficient Data-Aided Initial Frequency Synchronizer for DVB-S2. In Proceedings of the IEEE Workshop on Signal Processing Systems, Shanghai, China, 17–19 October 2007; pp. 645–650. [Google Scholar]

- Casini, E.; De Gaudenzi, R.; Ginesi, A. DVB-S2 modem algorithms design and performance over typical satellite channels. Int. J. Satell. Commun. Netw. 2004, 22, 281–318. [Google Scholar] [CrossRef]

- Oh, J.G.; Kim, J.T. An alternative carrier frequency synchronization scheme for DVB-S2 systems. In Proceedings of the International Conference on Advanced Communication Technology, Gangwon, Korea, 11–14 February 2010; pp. 529–533. [Google Scholar]

- Kim, P.; Ryu, J.-G. Carrier phase recovery for DVB-S2x standard in VL SNR channel. In Proceedings of the Advances in Communications Satellite Systems, 37th International Communications Satellite Systems Conference (ICSSC-2019), Okinawa, Japan, 1–8 November 2019. [Google Scholar]

- Barbieri, A.; Colavolpe, G. On Pilot-Symbol-Assisted Carrier Synchronization for DVB-S2 Systems. IEEE Trans. Broadcast. 2007, 53, 685–692. [Google Scholar] [CrossRef] [Green Version]

- Oh, J.G.; Kim, J.T. A simple and robust carrier frequency recovery scheme for DVB-S2 systems. IEEE Int. Symp. Consum. Electron. 2010, 15, 1–4. [Google Scholar] [CrossRef]

- Antiufrieva, L.; Ivchenko, A.; Dvorkovich, A. Features of a coarse frequency synchronization for DVB-S2X system. In Proceedings of the 2020 International Conference Engineering and Telecommunication (En&T), Dolgoprudny, Russia, 1–4 November 2020. [Google Scholar]

- Antiufrieva, L.; Iansitov, K.; Ivchenko, A.; Dvorkovich, A. Features of Frequency Synchronization Algorithms DVB-S2(X) for LEO Satellites. In Proceedings of the 2021, 23rd International Conference on Digital Signal Processing and Its Applications (DSPA), Moscow, Russia, 1–4 November 2021. [Google Scholar]

- Kay, S. A fast and accurate single frequency estimator. IEEE Trans. Acoust. Speech, Signal Process. 1989, 37, 1987–1990. [Google Scholar] [CrossRef] [Green Version]

- Chuang, J.C.-I.; Sollenberger, N.R. Burst coherent demodulation with combined symbol timing, frequency offset estimation, and diversity selection. IEEE Trans. Commun. 1991, 39, 1157–1164. [Google Scholar] [CrossRef]

- Mengali, U.; Morelli, M. Data-aided frequency estimation for burst digital transmission. IEEE Trans. Commun. 1997, 45, 23–25. [Google Scholar] [CrossRef]

- Jiang, Y.M. Synchronization and Channel Parameter Estimation in Wireless Communications; University of Maryland: College Park, MD, USA, 2000. [Google Scholar]

- Fitz, M.P. Planar filtered techniques for burst mode carrier synchronization. In Proceedings of the Global Telecommunications Conference, Phoenix, AZ, USA, 2–5 December 1991; pp. 365–369. [Google Scholar]

- Gong, F.; Shang, G.; Li, Y.; Peng, K. Initial-Estimation-Based Adaptive Carrier Recovery Scheme for DVB-S2 System. IEEE Trans. Broadcast. 2012, 58, 654–659. [Google Scholar] [CrossRef]

- Luise, M.; Reggiannini, R. Carrier frequency recovery in all-digital modems for burst-mode transmissions. IEEE Trans. Commun. 1995, 43, 1169–1178. [Google Scholar] [CrossRef]

- Sun, J.; Shi, J. A two-step frequency offset estimation algorithm using the iNET preamble in multipath fading channels. In Proceedings of the 2018 14th IEEE International Conference on Signal Processing (ICSP), Beijing, China, 12–16 August 2018; pp. 676–681. [Google Scholar]

- Zhang, Y. Research on Key Techniques of VCM/ACM in Satellite Data Transmission Link; University of Chinese Academy of Sciences: Beijing, China, 2019. [Google Scholar]

| Literature 2 | Literature 3 | Literature 4 | This Paper | ||

|---|---|---|---|---|---|

| Coarse CFR | D&M (M = 2) | Fitz (M = 2) | Modified M&M algorithm (M = 9) | RLR (N = 2 and N = 15) | |

| Multiplier | 34 | 73 | 281 | 30 | |

| Arc-tangent operations | 1 | 2 | 1 | 1 | |

| Fine CFR | L&R (M = 9) | Simple Pilot Block Correlation algorithm | Simple Pilot Block Correlation algorithm | None | |

| Multiplier | 288 | 36 | 36 | 0 | |

| Arc-tangent operations | 1 | 1 | 1 | 0 |

| Resource Consumption | Frame Synchronization | CFR Algorithm | CPR Algorithm | CR Scheme |

|---|---|---|---|---|

| DSP | 32 (1.67%) | 240 (12.50%) | 14 (0.73%) | 290 (15.1%) |

| Register | 13,970 (2.88%) | 148,18 (3.06%) | 6640 (1.37%) | 35,905 (7.41%) |

| LUT | 10,048 (4.15%) | 10,293 (4.25%) | 6511 (2.69%) | 27,353 (11.28%) |

| Workable clock (MHz) | 250 | 178.57 | 185.18 | 200.00 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hu, W.; Wang, Z.; Mei, R.; Lin, M. An Efficient Carrier Synchronization Scheme for Demodulation Systems. Electronics 2021, 10, 2942. https://doi.org/10.3390/electronics10232942

Hu W, Wang Z, Mei R, Lin M. An Efficient Carrier Synchronization Scheme for Demodulation Systems. Electronics. 2021; 10(23):2942. https://doi.org/10.3390/electronics10232942

Chicago/Turabian StyleHu, Wanru, Zhugang Wang, Ruru Mei, and Meiyan Lin. 2021. "An Efficient Carrier Synchronization Scheme for Demodulation Systems" Electronics 10, no. 23: 2942. https://doi.org/10.3390/electronics10232942

APA StyleHu, W., Wang, Z., Mei, R., & Lin, M. (2021). An Efficient Carrier Synchronization Scheme for Demodulation Systems. Electronics, 10(23), 2942. https://doi.org/10.3390/electronics10232942