Capacitorless One-Transistor Dynamic Random-Access Memory with Novel Mechanism: Self-Refreshing

Abstract

1. Introduction

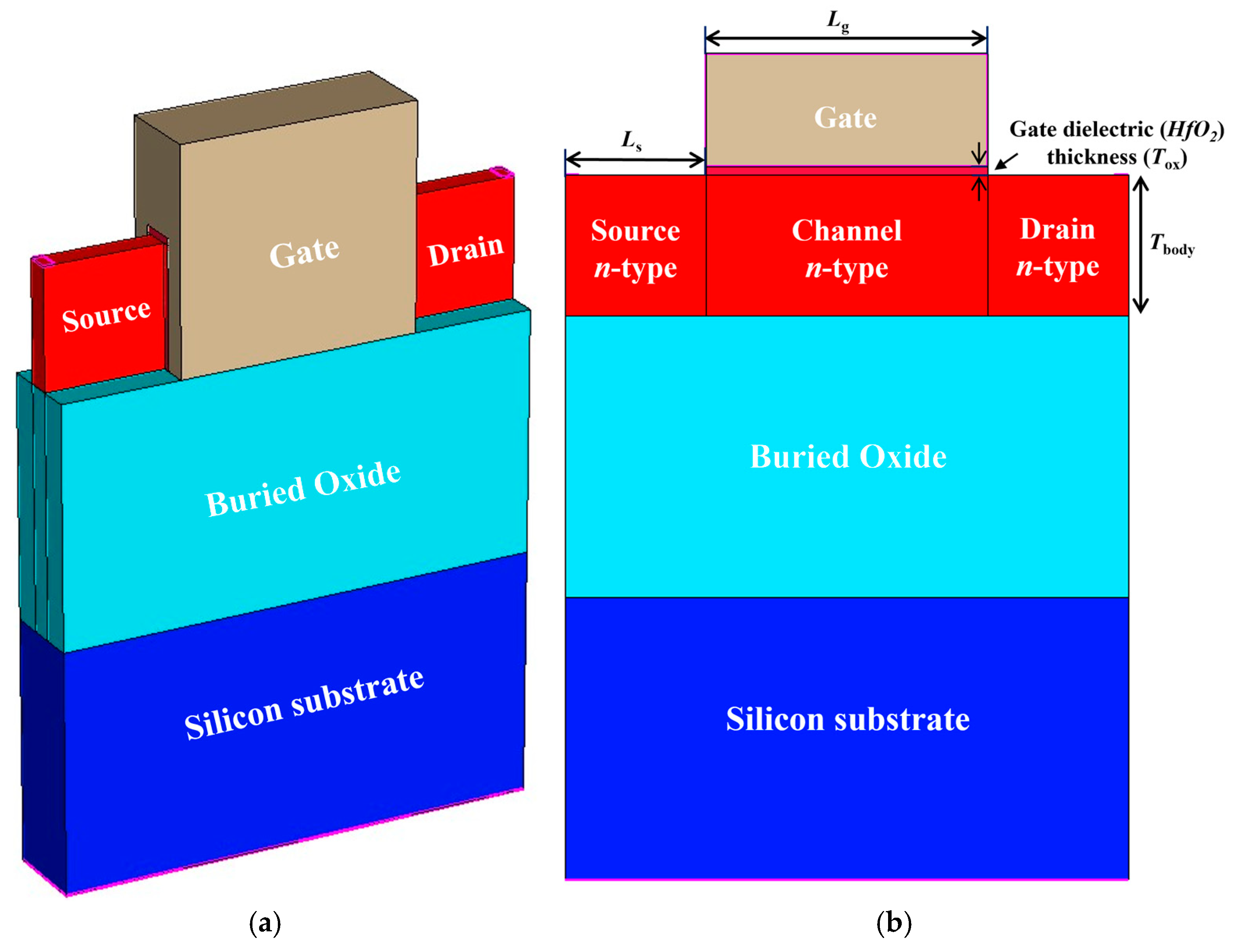

2. Device Structure and Simulation Methodology

3. Results and Discussion

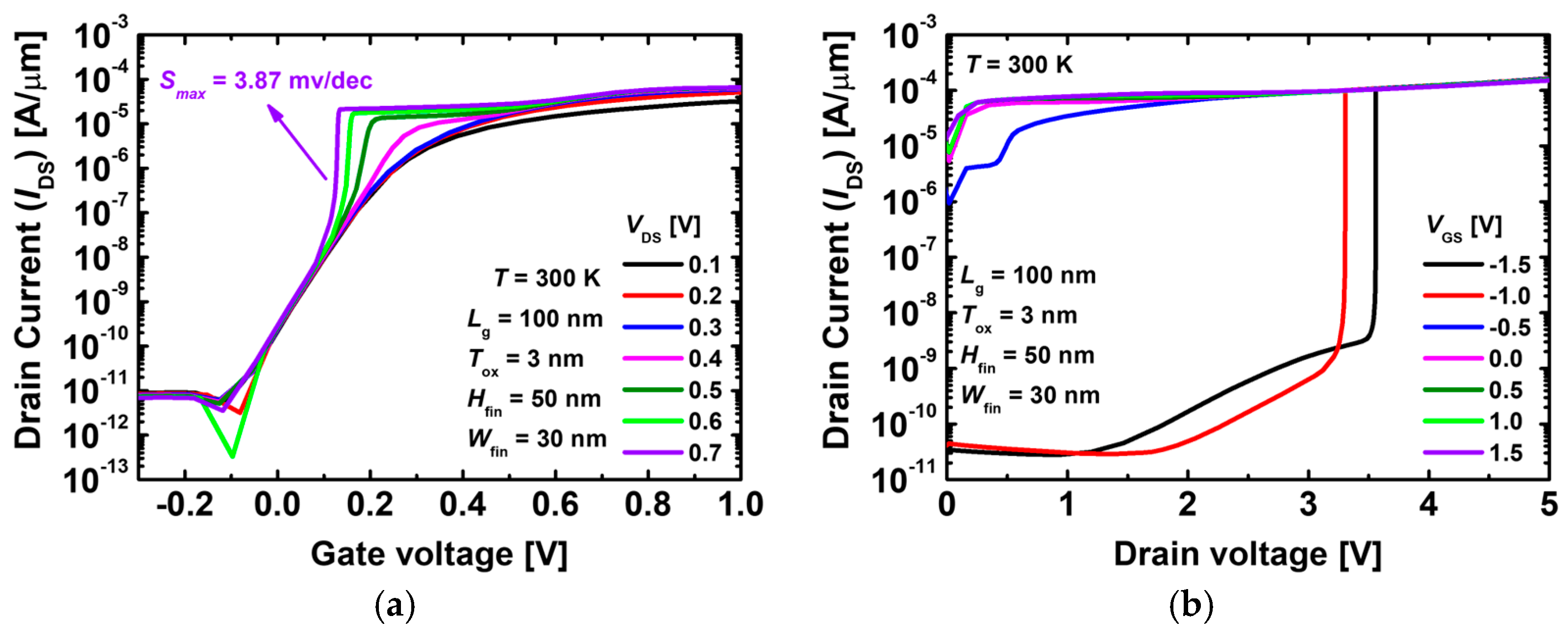

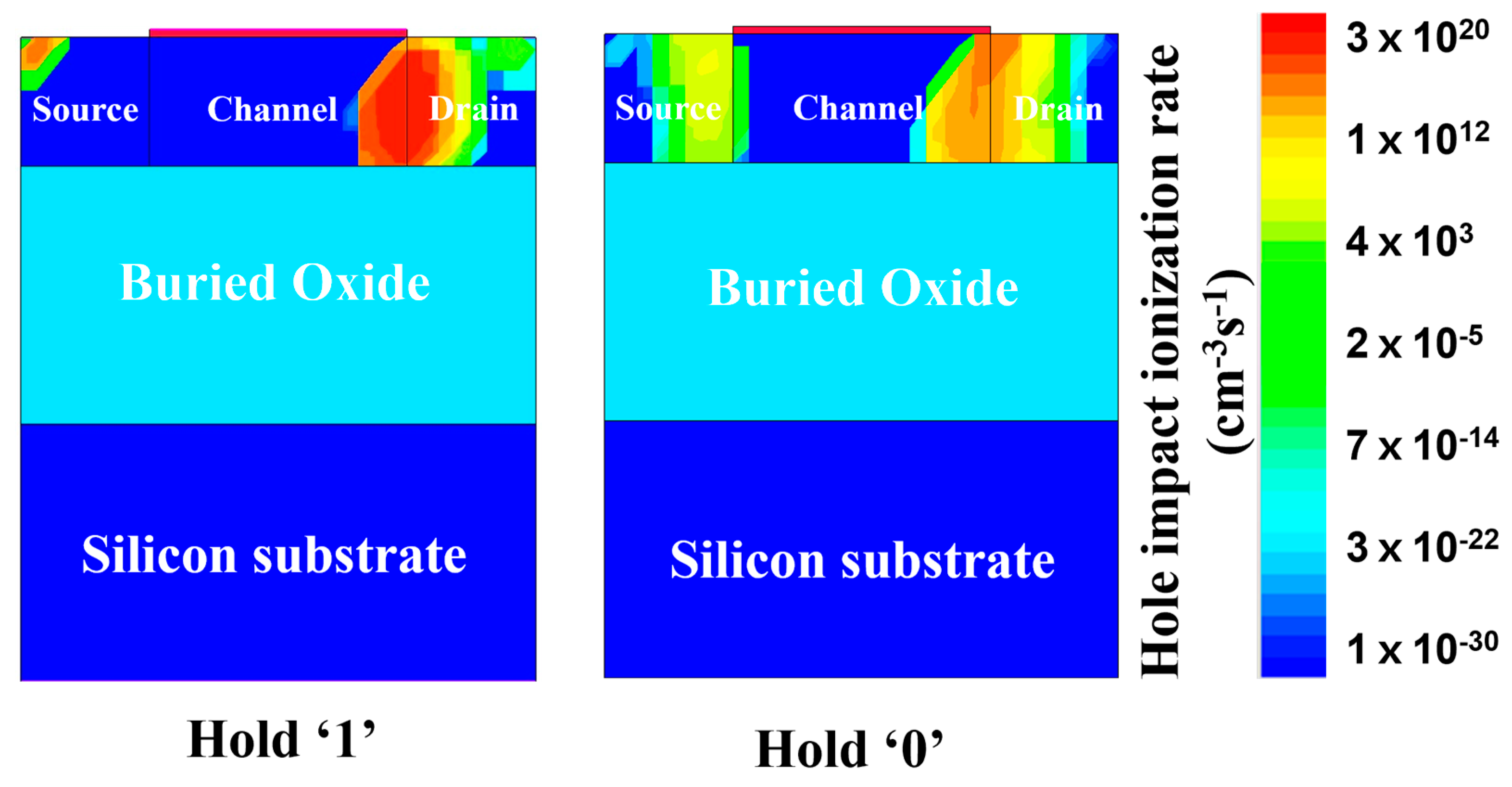

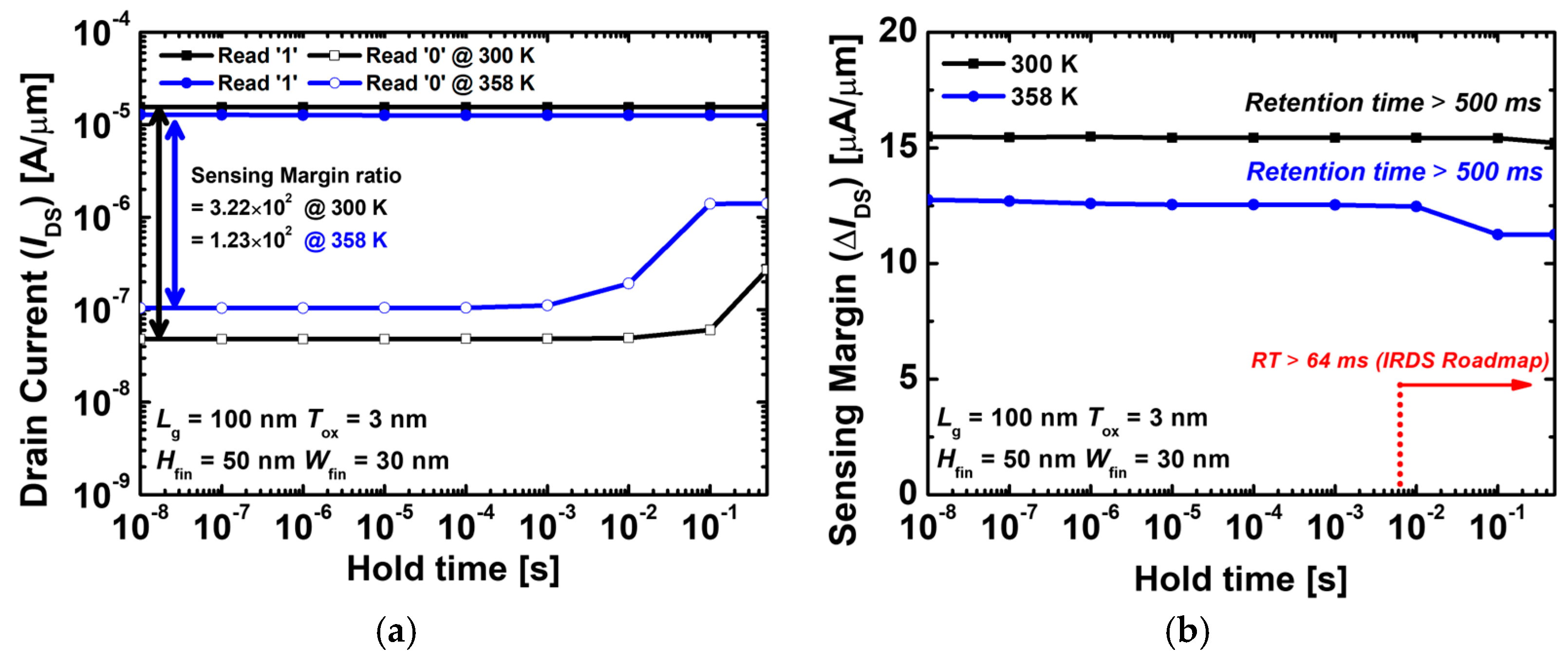

3.1. Characteristics of 1T-DRAM Cell

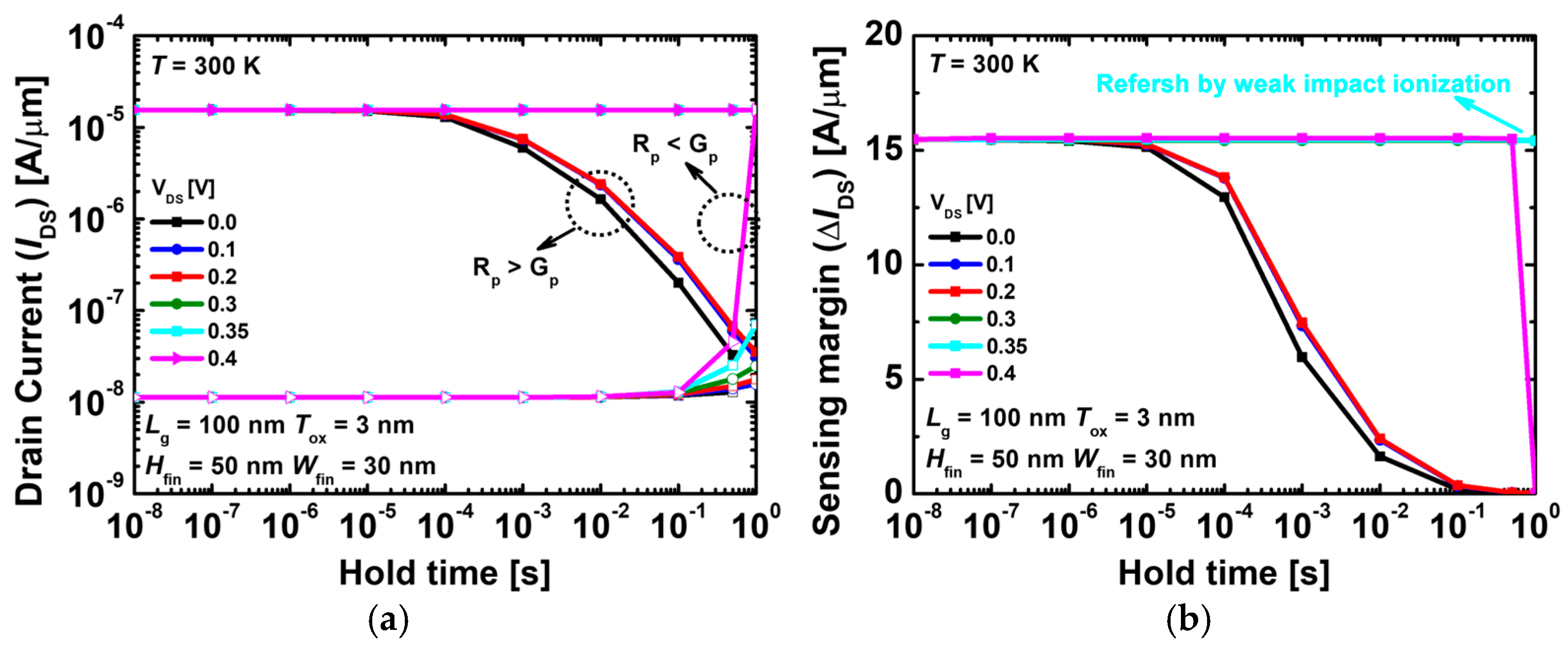

3.2. Array Characteristics of 1T-DRAM and Optimization of Operation Bias

3.3. Memory Characteristics and Energy Consumption of 1T-DRAM

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wann, H.-J.; Hu, C. A capacitorless DRAM cell on SOI substrate. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 635–638. [Google Scholar]

- Kuo, C.; King, T.J.; Hu, C. A Capacitorless Double Gate DRAM Technology for Sub-100-nm Embedded and Stand-Alone Memory Applications. IEEE Trans. Electron. Devices 2003, 50, 2408–2416. [Google Scholar] [CrossRef]

- Ranica, R.; Villaret, A.; Fenouillet-Beranger, C.; Malinge, P.; Mazoyer, P.; Masson, P.; Delille, D.; Charbuillet, C.; Candelier, P.; Skotnicki, T. A capacitor-less DRAM cell on 75 nm gate length, 16 nm thin fully depleted SOI device for high density embedded memories. In Proceedings of the IEDM Technical Digest, IEEE International Electron Devices Meeting, Washington, DC, USA, 13–15 December 2004; pp. 277–280. [Google Scholar]

- Okhonin, S.; Nagoga, M.; Sallese, J.M.; Fazan, P. A capacitor-less 1T-DRAM cell. IEEE Electron. Device Lett. 2002, 23, 85–87. [Google Scholar] [CrossRef]

- Okhonin, S.; Nagoga, M.; Sallese, J.M.; Fazan, P. A SOI capacitor-less 1T-DRAM concept. In Proceedings of the IEEE International SOI Conference, Durango, CO, USA, 1–4 October 2001; pp. 153–154. [Google Scholar]

- Yoshida, E.; Tanaka, T. A design of a capacitorless 1T-DRAM cell using gate-induced drain leakage (GIDL) current for low-power and high-speed embedded memory. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 8–10 December 2003; p. 37. [Google Scholar]

- Park, J.; Lee, S.-H.; Kang, G.-E.; Heo, J.-H.; Jeon, S.-R.; Kim, M.-S.; Bae, S.-J.; Hong, J.-W.; Jang, J.-W.; Bae, J.-H.; et al. Simulation of Capacitorless DRAM Based on the Polycrystalline Silicon Nanotube Structure with Multiple Grain Boundaries. Nanomaterials 2023, 13, 2026. [Google Scholar] [CrossRef] [PubMed]

- Lee, S.H.; Jang, W.D.; Yoon, Y.J.; Seo, J.H.; Mun, H.J.; Cho, M.S.; Jang, J.; Bae, J.-H.; Kang, I.M. Polycrystalline-Silicon-MOSFET-Based Capacitorless DRAM With Grain Boundaries and Its Performances. IEEE Access 2021, 9, 50281–50290. [Google Scholar] [CrossRef]

- Park, J.; Cho, M.S.; Lee, S.H.; An, H.D.; Min, S.R.; Kim, G.U.; Yoon, Y.J.; Seo, J.H.; Lee, S.-H.; Jang, J.; et al. Design of Capacitorless DRAM Based on Polycrystalline Silicon Nanotube Structure. IEEE Access 2021, 9, 163675–163685. [Google Scholar] [CrossRef]

- Ertosun, M.G.; Cho, H.; Kapur, P.; Saraswat, K.C. A nanoscale vertical double-gate single-transistor capacitorless DRAM. IEEE Electron. Device Lett. 2008, 29, 615–617. [Google Scholar] [CrossRef]

- Belmonte, A.; Oh, H.; Rassoul, N.; Donadio, G.L.; Mitard, J.; Dekkers, H.; Delhougne, R.; Subhechha, S.; Chasin, A.; Van Setten, M.J.; et al. Capacitor-less, long-retention (>400 s) DRAM cell paving the way towards low-power and high-density monolithic 3D DRAM. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 12–18 December 2020; pp. 28–32. [Google Scholar]

- Lu, W.; Zhu, Z.; Chen, K.; Liu, M.; Kang, B.M.; Duan, X.; Niu, J.; Liao, F.; Dan, W.; Wu, X.-S.; et al. First Demonstration of Dual-Gate IGZO 2T0C DRAM with Novel Read Operation, One Bit Line in Single Cell, ION = 1500 μA/μm@VDS = 1 V and Retention Time > 300 s. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 3–7 December 2022; pp. 26–34. [Google Scholar]

- Navarro, C.; Navarro, S.; Marquez, C.; Donetti, L.; Sampedro, C.; Karg, S.; Gamiz, F. InGaAs capacitor-less DRAM cells TCAD demonstration. IEEE J. Electron. Devices Soc. 2018, 6, 884–892. [Google Scholar] [CrossRef]

- Navarro, C.; Karg, S.; Marquez, C.; Navarro, S.; Convertino, C.; Zota, C.; Czornomaz, L.; Gamiz, F. Capacitor-less dynamic random access memory based on a III–V transistor with a gate length of 14 nm. Nat. Electron. 2019, 2, 412–419. [Google Scholar] [CrossRef]

- Ertosun, M.G.; Saraswat, K.C. Investigation of capacitorless double-gate single-transistor DRAM: With and without quantum well. IEEE Trans. Electron. Devices 2010, 57, 608–613. [Google Scholar] [CrossRef]

- Lee, S.H.; Park, J.; Min, S.R.; Kim, G.U.; Jang, J.; Bae, J.-H.; Lee, S.-H.; Kang, I.M. 3-D stacked polycrystalline-silicon-MOSFET-based capacitorless DRAM with superior immunity to grain-boundary’s influence. Sci. Rep. 2022, 12, 14455. [Google Scholar] [CrossRef]

- Chen, W.C.; Lue, H.T.; Wu, M.Y.; Yeh, T.H.; Du, P.Y.; Hsu, T.H.; Hsieh, C.-C.; Lu, K.-C.; Lu, C.Y. A 3D Stackable DRAM: Capacitor-less Three-Wordline Gate-Controlled Thyristor (GCT) RAM with >40 μA Current Sensing Window, >1010 Endurance, and 3-second Retention at Room Temperature. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 3–7 December 2022; p. 26. [Google Scholar]

- Kuo, C.; King, T.J.; Hu, C. A capacitorless double-gate DRAM cell design for high density applications. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 2002; pp. 843–846. [Google Scholar]

- Bawedin, M.; Cristoloveanu, S.; Flandre, D. A Capacitorless 1T-DRAM on SOI Based on Dynamic Coupling and Double-Gate Operation. IEEE Electron. Device Lett. 2008, 29, 795–798. [Google Scholar] [CrossRef]

- Biswas, A.; Ionescu, A.M. 1T capacitor-less DRAM cell based on asymmetric tunnel FET design. IEEE J. Electron. Devices Soc. 2014, 3, 217–222. [Google Scholar] [CrossRef]

- Yoon, Y.J. Fabrication of Polycrystalline Silicon Dual-Gate MOSFET-Based One-Transistor Dynamic Random-Access Memory and Its Electrical Performance. Ph.D. Thesis, Kyungpook National University, Daegu, Republic of Korea, 2019. Available online: http://www.riss.kr/link?id=T15076380 (accessed on 21 November 2023).

- Sentaurus Device User Guide Version P-2019.03; Synopsys TCAD Sentaurus: San Jose, CA, USA, 2019.

- More Moore, 2021 International Roadmap for Devices and Systems (IRDS™) Edition. 2021. Available online: https://irds.ieee.org/editions/2021 (accessed on 21 November 2023).

- Colinge, J.P.; Lee, C.W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; Neill, B.O.; Blake, A.; White, M.; et al. Nanowire transistors without junctions. Nat. Nanotechnol. 2010, 5, 225–229. [Google Scholar] [CrossRef] [PubMed]

- Andrade, M.G.C.; Martino, J.A.; Aoulaiche, M.; Collaert, N.; Simoen, E.; Claeys, C. The impact of back bias on the floating body effect in UTBOX SOI devices for 1T-FBRAM memory applications. In Proceedings of the 2012 8th International Caribbean Conference on Devices, Circuits and Systems (ICCDCS), Playa del Carmen, Mexico, 14–17 March 2012; pp. 1–4. [Google Scholar]

- Lu, Z.; Collaert, N.; Aoulaiche, M.; De Wachter, B.; De Keersgieter, A.; Schwarzenbach, W.; Bonnin, O.; Bourdelle, K.K.; Nguyen, B.-Y.; Mazur, C.; et al. A novel low-voltage biasing scheme for double gate FBC achieving 5s retention and 1016 endurance at 85 °C. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; p. 12. [Google Scholar]

- Jeon, J.; Cho, K.; Kim, S. Disturbance Characteristics of 1T-DRAM Arrays Consisting of Feedback Field-Effect Transistors. Micromachines 2023, 14, 1138. [Google Scholar] [CrossRef] [PubMed]

- Lin, J.-T.; Lin, P.-H.; Haga, S.W.; Wang, Y.-C.; Lu, D.-R. Transient and Thermal Analysis on Disturbance Immunity for 4F2 Surrounding Gate 1T-DRAM with Wide Trenched Body. IEEE Trans. Electron. Devices 2014, 62, 61–68. [Google Scholar]

- Lin, J.T.; Lin, H.-H.; Chen, Y.-J.; Yu, C.-Y.; Kranti, A.; Lin, C.-C.; Lee, W.-H. Vertical Transistor With n-Bridge and Body on Gate for Low-Power 1T-DRAM Application. IEEE Trans. Electron. Devices 2017, 64, 4937–4945. [Google Scholar] [CrossRef]

- Lahgere, A.; Kumar, M.J. 1-T Capacitorless DRAM Using BandgapEngineered Silicon-Germanium Bipolar I-MOS. IEEE Trans. Electron. Devices 2017, 64, 1583–1590. [Google Scholar] [CrossRef]

- Han, J.-W.; Ryu, S.-W.; Kim, D.-H.; Choi, Y.-K. Polysilicon Channel TFT With Separated Double-Gate for Unified RAM (URAM)—Unified Function for Nonvolatile SONOS Flash and High-Speed Capacitorless 1T-DRAM. Trans. Electron. Devices 2010, 57, 601–607. [Google Scholar] [CrossRef]

- Lee, S.; Shin, J.S.; Jang, J.; Bae, H.; Yun, D.; Lee, J.; Kim, D.H.; Kim, D.M. A Novel Capacitorless DRAM Cell Using Superlattice Bandgap-Engineered (SBE) Structure With 30-nm Channel Length. IEEE Trans. Nanotechnol. 2010, 10, 1023–1030. [Google Scholar] [CrossRef]

- Li, H.; Lin, Y. A 2T Dual Port Capacitor-Less DRAM. IEEE Electron. Device Lett. 2013, 35, 187–189. [Google Scholar] [CrossRef]

- Kwon, W.; Liu, T.J.K. A Highly Scalable Capacitor-Less Cell Having a Doubly Gated Vertical Channel. Jap. J. Appl. Phys. 2010, 49, 04DD04. [Google Scholar] [CrossRef]

- Cheng, C.H.; Chin, A. Low-leakage-current DRAM-like memory using a one-transistor ferroelectric MOSFET with a Hf-based gate dielectric. IEEE Electron. Device Lett. 2013, 35, 138–140. [Google Scholar] [CrossRef]

- Lee, S.; Cho, H.; Son, Y.H.; Ro, Y.; Kim, N.S.; Ahn, J.H. Leveraging power-performance relationship of energy-efficient modern DRAM devices. IEEE Access 2018, 6, 31387–31398. [Google Scholar] [CrossRef]

- Yu, E.; Cho, S. A Highly Scalable and Energy-Efficient 1T-DRAM Embedding a SiGe Quantum Well Structure for Significant Retention Enhancement. In Proceedings of the 2018 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Austin, TX, USA, 24–26 September 2018; pp. 255–257. [Google Scholar]

- Navarro, C.; Marquez, C.; Navarro, S.; Lozano, C.; Kwon, S.; Kim, Y.-T.; Gamiz, F. Simulation Perspectives of Sub-1V Single-Supply Z2-FET 1T-DRAM Cells for Low-Power. IEEE Access 2019, 7, 40279–40284. [Google Scholar] [CrossRef]

| Parameters | Values |

|---|---|

| Gate length (Lg) | 100 nm |

| Source/Drain length (Ls, Ld) | 50 nm |

| Gate dielectric (HfO2) thickness (Tox) | 3 nm |

| Fin height (Hfin) | 50 nm |

| Fin width (Wfin) | 30 nm |

| Source/Body/Drain doping concentration | n-type, 3 × 1018 cm−3 |

| Gate metal work function | 5.0 eV |

| Operation | Program (Write ‘1’) | Erase (Write ‘0’) | Read | Hold |

|---|---|---|---|---|

| Gate voltage [V] | 0.2 | 0.2 | 0.1 | −0.2 |

| Drain voltage [V] | 2.5 | −0.5 | 0.5 | 0.35 |

| Disturbance Conditions | SMdisturbed/SMundisturbed [%] @ tdisturbance = 10 ns | |||

|---|---|---|---|---|

| Device Condition | Disturb Source | Device Operation | 300 K | 358 K |

| Hold ‘1’ | Bit-line | Erase | 17.3% | 15.2% |

| Program | 100.3% | 100.4% | ||

| Read | 100.2% | 100.5% | ||

| Word-Line | Erase | 50.0% | 45.8% | |

| Program | 50.0% | 45.8% | ||

| Read | 87.7% | 83.6% | ||

| Hold ‘0’ | Bit-line | Erase | 100.0% | 100.0% |

| Program | 100.0% | 100.0% | ||

| Read | 100.0% | 100.0% | ||

| Word-Line | Erase | 100.0% | 100.0% | |

| Program | 100.0% | 100.0% | ||

| Read | 100.0% | 100.0% | ||

| Disturbance Conditions | SMdisturbed/SMundisturbed [%] @ tdisturbance = 10 ns | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Vgs = 0.2 V, Vds = 2.5 V | Vgs = 0.2 V, Vds = 4.5 V | Vgs = 0.1 V, Vds = 4.5 V | Vgs = 0.0 V, Vds = 4.5 V | |||||||||

| Device Condition | Disturb Source | Device Operation | 300 K | 358 K | 300 K | 358 K | 300 K | 358 K | 300 K | 358 K | ||

| Hold ‘1’ | Bit-line | Erase | 17.3% | 15.2% | 17.3% | 15.1% | 17.3% | 15.1% | - | - | ||

| Program | 100.3% | 100.4% | 99.9% | 99.9% | 100.0% | 99.9% | - | - | ||||

| Read | 100.2% | 100.5% | 100.0% | 100.0% | 100.1% | 100.0% | - | - | ||||

| Word-Line | Erase | 50.0% | 45.8% | 50.0% | 45.8% | 50.1% | 45.8% | - | - | |||

| Program | 50.0% | 45.8% | 50.0% | 45.8% | 87.9% | 83.3% | - | - | ||||

| Read | 87.7% | 83.6% | 87.7% | 83.3% | 87.9% | 83.3% | - | - | ||||

| Hold ‘0’ | Bit-line | Erase | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | ||

| Program | 100.0% | 100.0% | 99.9% | 99.3% | 99.9% | 99.3% | - | - | ||||

| Read | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | ||||

| Word-Line | Erase | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | |||

| Program | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | ||||

| Read | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | ||||

| Operation temp | 300 K | Percentage (%) | 90~100% | 60~90% | 0~60% | SM Error | ||||||

| 358 K | ||||||||||||

| Disturbance Conditions | SMdisturbed/SMundisturbed [%] @ tdisturbance = 10 ns | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Vgs = 0.20 V, Vds = −0.50 V | Vgs = 0.15 V, Vds = −0.50 V | Vgs = 0.15 V, Vds = −0.40 V | Vgs = 0.15 V, Vds = −0.35 V | Vgs = 0.15 V, Vds = −0.30 V | ||||||||

| Device Condition | Disturb Source | Device Operation | 300 K | 358 K | 300 K | 358 K | 300 K | 358 K | 300 K | 358 K | 300 K | 358 K |

| Hold ‘1’ | Bit-line | Erase | 17.3% | 15.1% | 17.3% | 15.1% | 49.9% | 45.7% | 71.0% | 66.2% | - | - |

| Program | 100.0% | 99.9% | 100.0% | 99.9% | 100.0% | 99.9% | 100.0% | 99.9% | - | - | ||

| Read | 100.1% | 100.0% | 100.1% | 100.0% | 100.1% | 100.0% | 100.1% | 100.0% | - | - | ||

| Word-Line | Erase | 50.1% | 45.8% | 71.0% | 66.3% | 71.0% | 66.2% | 71.0% | 66.2% | - | - | |

| Program | 87.9% | 83.3% | 87.9% | 83.3% | 87.8% | 83.3% | 87.8% | 83.3% | - | - | ||

| Read | 87.9% | 83.3% | 87.9% | 83.3% | 87.8% | 83.3% | 87.8% | 83.3% | - | - | ||

| Hold ‘0’ | Bit-line | Erase | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - |

| Program | 99.9% | 99.3% | 99.9% | 99.3% | 99.8% | 99.3% | 99.6% | 98.9% | - | - | ||

| Read | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | ||

| Word-Line | Erase | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | |

| Program | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | ||

| Read | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | - | - | ||

| Operation temp | 300 K | Percentage (%) | 90~100% | 60~90% | 0~60% | SM Error | ||||||

| 358 K | ||||||||||||

| Device | Reference | Sensing Margin (μA/μm) | Retention Time | Features and Challenges |

|---|---|---|---|---|

| This work | - | 12.7~15.4 | >500 ms | CMOS compatible |

| Poly-Si MOSFET 1T-DRAM | [8] | 8.7 | 704 ms | A complex fabrication process of dual gates |

| Poly-Si nanotube 1T-DRAM | [9] | 422 | 120 ms | A complex fabrication process of the inner and outer gate |

| Vertical Double-gate 1T-DRAM | [10] | 3~6 | 25 ms | Poor memory characteristics |

| IGZO-based 1T-DRAM | [11] | - | >400 s | CMOS incompatible |

| InGaAs-based 1T-DRAM | [14] | ~2 | >1 ms | CMOS incompatible |

| 3D stacked 1T-DRAM | [16] | 17.4 | 200 ms | Complex fabrication process |

| 1T-FeMOS | [35] | ~1 | 5 s | Good retention time but poor sensing margin |

| Operation | Program (Write ‘1’) | Erase (Write ‘0’) | Read | Hold |

|---|---|---|---|---|

| Gate voltage [V] | 0.1 | 0.15 | 0.1 | −0.2 |

| Drain voltage [V] | 4.5 | −0.35 | 0.5 | 0.35 |

| Drain current [A] | 9.1395 × 10−6 | 4.9959 × 10−6 | R ‘1’: 1.7039 × 10−6 R ‘0’: 1.2374 × 10−9 | H ‘1’: 5.0051 × 10−7 H ‘0’: 1.7928 × 10−14 |

| Operation time [ns] | 10 | 10 | 10 | 10 |

| Energy consumption [J] (E = VD × ID × Time) | 411.3 fJ | 17.5 fJ | 8.5 fJ 0.006 fJ | 1.8 fJ 0 fJ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.H.; Park, J.; Yoon, Y.J.; Kang, I.M. Capacitorless One-Transistor Dynamic Random-Access Memory with Novel Mechanism: Self-Refreshing. Nanomaterials 2024, 14, 179. https://doi.org/10.3390/nano14020179

Lee SH, Park J, Yoon YJ, Kang IM. Capacitorless One-Transistor Dynamic Random-Access Memory with Novel Mechanism: Self-Refreshing. Nanomaterials. 2024; 14(2):179. https://doi.org/10.3390/nano14020179

Chicago/Turabian StyleLee, Sang Ho, Jin Park, Young Jun Yoon, and In Man Kang. 2024. "Capacitorless One-Transistor Dynamic Random-Access Memory with Novel Mechanism: Self-Refreshing" Nanomaterials 14, no. 2: 179. https://doi.org/10.3390/nano14020179

APA StyleLee, S. H., Park, J., Yoon, Y. J., & Kang, I. M. (2024). Capacitorless One-Transistor Dynamic Random-Access Memory with Novel Mechanism: Self-Refreshing. Nanomaterials, 14(2), 179. https://doi.org/10.3390/nano14020179