Low-Loss Micro-Resonator Filters Fabricated in Silicon by CMOS-Compatible Lithographic Techniques: Design and Characterization

Abstract

:1. Introduction

2. Materials and Methods

2.1. Filter Design

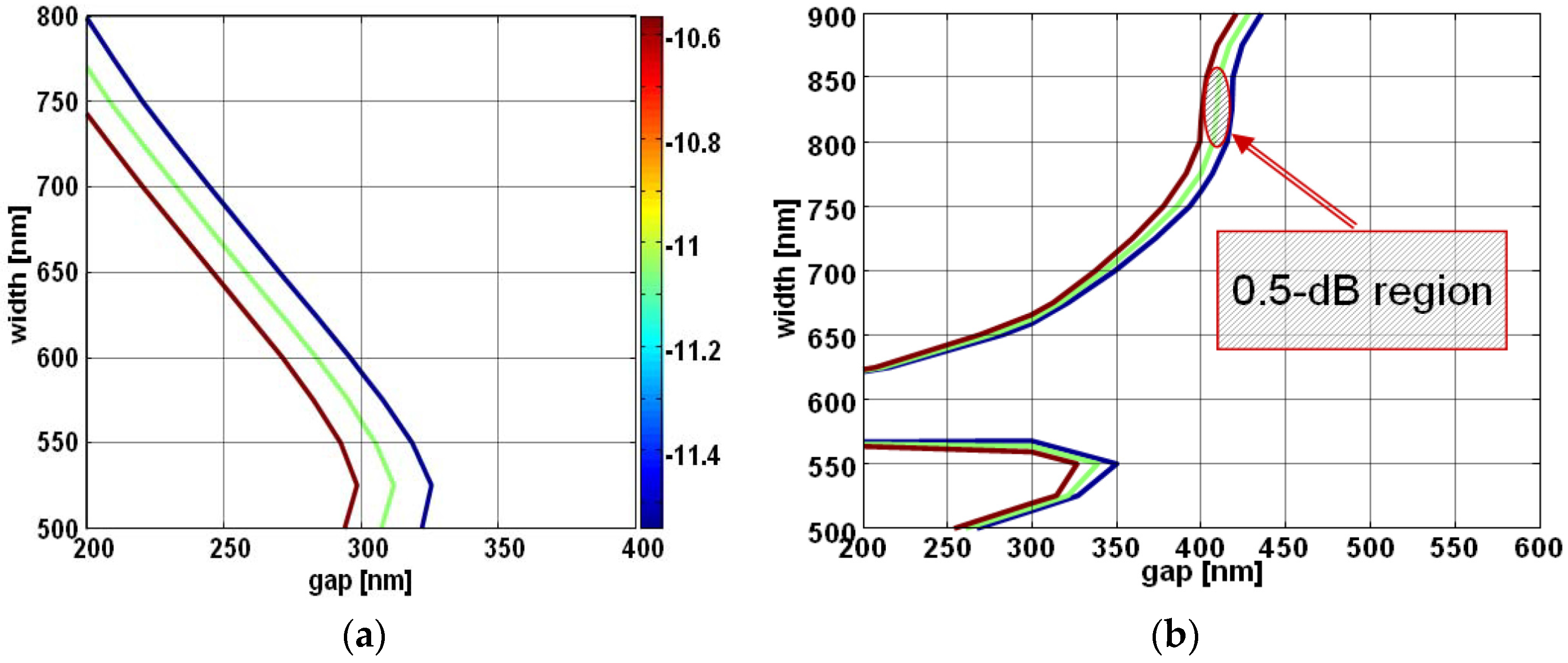

- the minimum gap between adjacent waveguides was set to 200 nm, in order to allow a full-etch of the region using standard lithographic techniques;

- the bus waveguide had to be 500 nm wide, so as to match the width of the waveguides used for the other components of the final chip;

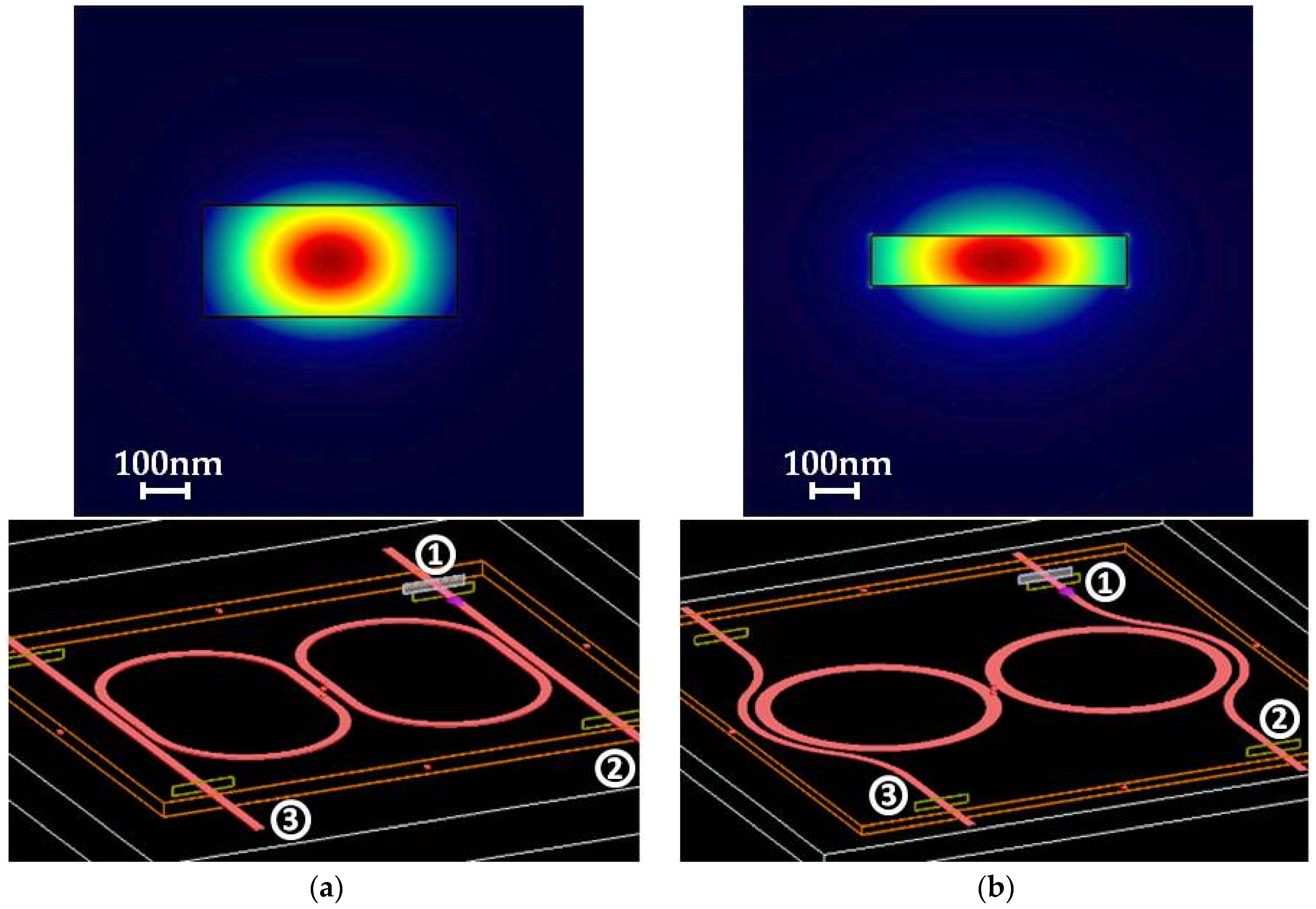

- the height of the waveguides could be 220 nm (corresponding to the height of the Si layer present on the SOI wafers), or could be reduced to 100 nm, as a fabrication step with a 120-nm etch depth was already present in the process flow, but no other height-value could be used for the filter’s design;

- it was important to realize a fabrication-tolerant design, as the fabrication process was based on standard lithographic techniques and was not exploiting the e-beam high-resolution, as often done in scientific research where performance is the main challenge and production-price is not an issue.

2.2. Structures Parameters

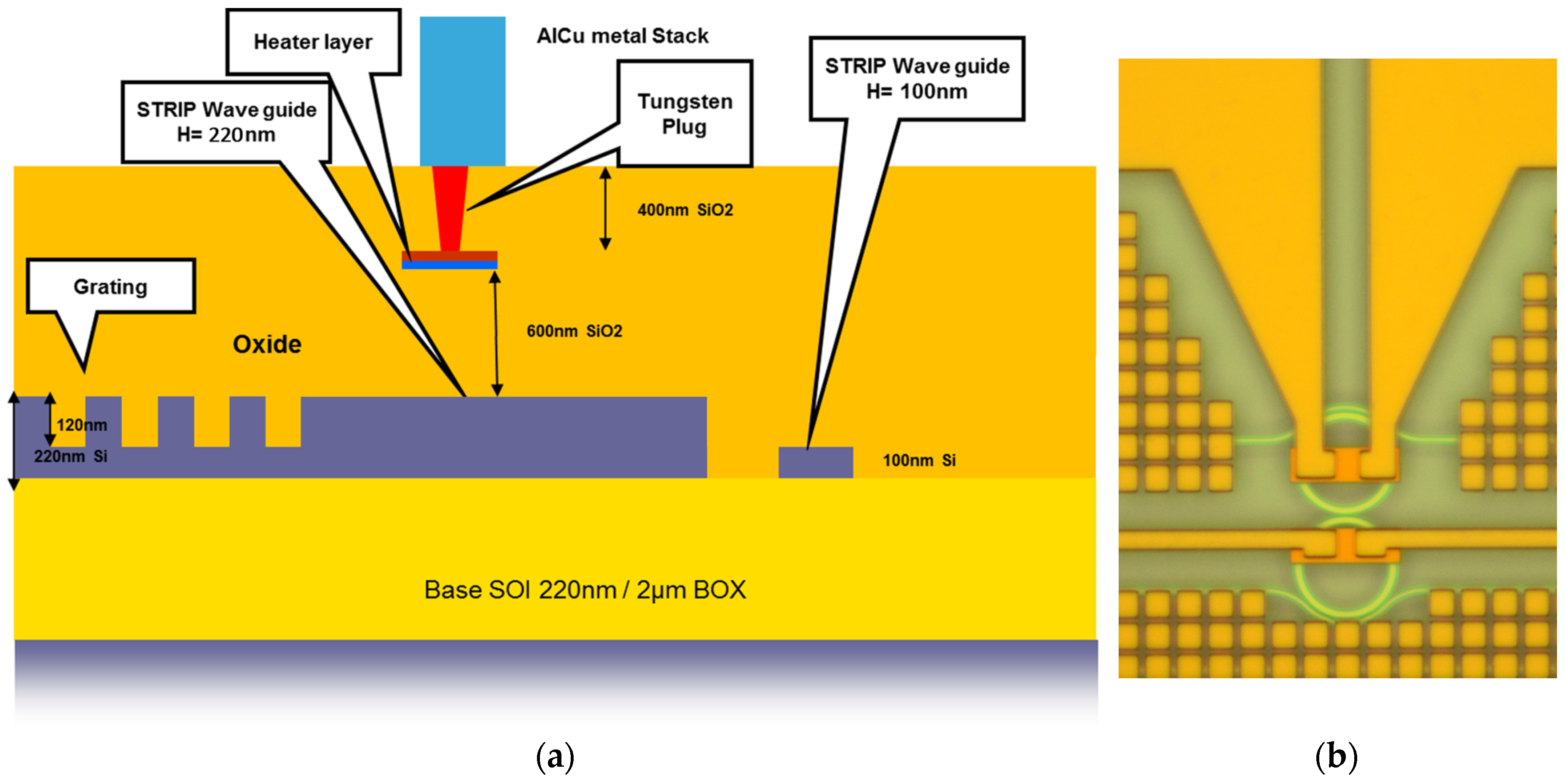

2.3. Fabrication Procedure

2.4. Experimental Characterization Setup

3. Results

3.1. Experimental Results

3.2. Final Filter Design

3.2.1. Structures Parameters

3.2.2. Experimental Results

4. Discussion

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Lim, A.E.-J.; Song, J.; Fang, Q.; Li, C.; Tu, X.; Duan, N.; Chen, K.K.; Tern, R.P.-C.; Liow, T.-Y. Review of Silicon Photonics Foundry Efforts. IEEE J. Sel. Top. Quantum Electron. 2014, 20, 405–416. [Google Scholar] [CrossRef]

- Thomson, D.; Zilkie, A.; Bowers, J.E.; Komljenovic, T.; Reed, G.T.; Vivien, L.; Marris-Morini, D.; Cassan, E.; Virot, L.; Fédéli, J.-M.; et al. Roadmap on silicon photonics. J. Opt. 2016, 18. [Google Scholar] [CrossRef]

- Xia, F.; Rooks, M.; Sekaric, L.; Vlasov, Y. Ultra-compact high order ring resonator filters using submicron silicon photonic wires for on-chip optical interconnects. Opt. Express 2007, 15, 11934–11941. [Google Scholar] [CrossRef] [PubMed]

- Bogaerts, W.; De Heyn, P.; Van Vaerenbergh, T.; De Vos, K.; Kumar Selvaraja, S.; Claes, T.; Dumon, P.; Bienstman, P.; Van Thourhout, D.; Baets, R. Silicon microring resonators. Laser Photonics Rev. 2012, 6, 47–73. [Google Scholar] [CrossRef]

- Reed, G.T.; Mashanovich, G.; Gardes, F.Y.; Thomson, D.J. Silicon optical modulators. Nat. Photonics 2010, 4, 518–526. [Google Scholar] [CrossRef]

- Thomson, D.J.; Gardes, F.Y.; Fedeli, J.M.; Zlatanovic, S.; Hu, Y.; Kuo, B.P.P.; Myslivets, E.; Alic, N.; Radic, S.; Mashanovich, G.Z.; et al. 50-Gb/s silicon optical modulator. IEEE Photonics Technol. Lett. 2012, 24, 234–236. [Google Scholar] [CrossRef]

- Fang, Q.; Liow, T.Y.; Song, J.F.; Ang, K.W.; Yu, M.B.; Lo, G.Q.; Kwong, D.L. WDM multi-channel silicon photonic receiver with 320 Gbps data transmission capability. Opt. Express 2010, 18, 5106–5113. [Google Scholar] [CrossRef] [PubMed]

- Espinola, R.L.; Dadap, J.I.; Richard, M.; McNab, S.J.; Vlasov, Y.A. C-band wavelength conversion in silicon photonic wire waveguides. Opt. Express 2005, 13, 4341–4349. [Google Scholar] [CrossRef] [PubMed]

- Yamada, K.; Fukuda, H.; Tsuchizawa, T.; Watanabe, T.; Shoji, T.; Itabashi, S. All-optical efficient wavelength conversion using silicon photonic wire waveguide. IEEE Photonics Technol. Lett. 2006, 18, 1046–1048. [Google Scholar] [CrossRef]

- Roelkens, G.; Vermeulen, D.; Van Thourhout, D.; Baets, R.; Brision, S.; Lyan, P.; Gautier, P.; Fédéli, J.M. High efficiency diffractive grating couplers for interfacing a single mode optical fiber with a nanophotonic silicon-on-insulator waveguide circuit. Appl. Phys. Lett. 2008, 92, 131101. [Google Scholar] [CrossRef]

- Taillaert, D.; Van Laere, F.; Ayre, M.; Bogaerts, W.; Van Thourhout, D.; Bienstman, P.; Baets, R. Grating couplers for coupling between optical fibers and nanophotonic waveguides. Jpn. J. Appl. Phys. 2006, 45, 6071–6077. [Google Scholar] [CrossRef]

- Dahlem, M.S.; Holzwarth, C.W.; Khilo, A.; Kärtner, F.X.; Smith, H.I.; Ippen, E.P. Reconfigurable multi-channel second-order silicon microring-resonator filterbanks for on-chip WDM systems. Opt. Express 2011, 19, 306–316. [Google Scholar] [CrossRef] [PubMed]

- Nawrocka, M.S.; Liu, T.; Wang, X.; Panepucci, R.R. Tunable silicon microring resonator with wide free spectral range. Appl. Phys. Lett. 2006, 89, 71110. [Google Scholar] [CrossRef]

- Hu, T.; Wang, W.; Qiu, C.; Yu, P.; Qiu, H.; Zhao, Y.; Jiang, X.; Yang, J. Thermally tunable filters based on third-order microring resonators for WDM applications. IEEE Photonics Technol. Lett. 2012, 24, 524–526. [Google Scholar] [CrossRef]

- Luo, L.W.; Wiederhecker, G.S.; Cardenas, J.; Poitras, C.; Lipson, M. High quality factor etchless silicon photonic ring resonators. Opt. Express 2011, 19, 6284–6289. [Google Scholar] [CrossRef] [PubMed]

- Xiao, S.; Khan, M.H.; Shen, H.; Qi, M. Compact silicon microring resonators with ultra-low propagation loss in the C band. Opt. Express 2007, 15, 14467–14475. [Google Scholar] [CrossRef] [PubMed]

- Abrate, S.; Straullu, S.; Nespola, A.; Savio, P.; Chang, J.; Ferrero, V.; Charbonnier, B.; Gaudino, R. Overview of the FABULOUS EU Project: Final System Performance Assessment with Discrete Components. J. Lightwave Technol. 2016, 34, 798–804. [Google Scholar] [CrossRef]

- Straullu, S.; Savio, P.; Chang, J.; Ferrero, V.; Nespola, A.; Gaudino, R.; Abrate, S. Optimization of Reflective FDMA-PON Architecture to Achieve 32 Gb/s Per Upstream Wavelength Over 31 dB ODN Loss. J. Lightwave Technol. 2015, 33, 474–480. [Google Scholar] [CrossRef]

- Barwicz, T.; Haus, H.A. Three-dimensional analysis of scattering losses due to sidewall roughness in microphotonic waveguides. J. Lightwave Technol. 2005, 23, 2719–2732. [Google Scholar] [CrossRef]

- Lacava, C.; Marchetti, R.; Vitali, V.; Cristiani, I.; Giuliani, G.; Fournier, M.; Bernabe, S.; Minzioni, P. Reduced nonlinearities in 100-nm high SOI waveguides. In Proceedings of the SPIE Photonic West 2016, Optical Interconnects XVI, San Francisco, CA, USA, 13–18 February 2016; Schröder, H., Chen, R.T., Eds.; SPIE International: Bellingham, WA, USA, 2016; Volume 9753, pp. 975313–975318. [Google Scholar]

| Parameter | Value |

|---|---|

| Operation band | 1530–1570 nm |

| Channel spacing | 100 GHz |

| Free Spectral Range | 12.8 nm |

| Insertion Loss | <1 dB |

| Suppression adjacent channels | >15 dB |

| Suppression non-adjacent channels | >20 dB |

| Parameter | Units | Racetracks | Rings |

|---|---|---|---|

| Bus waveguide (width × height) | nm × nm | 500 × 220 | 500 × 100 |

| Resonator waveguide (width × height) | nm × nm | 500 × 220 | 825 × 100 |

| Straight-leg | nm | 4745 | N.A. |

| Curve radius (@ waveguide center) | nm | 4490 | 6000 |

| Bus-to-Resonator gap | nm | 200 | 410 |

| Inter-Resonator gap | nm | 415 | 340 |

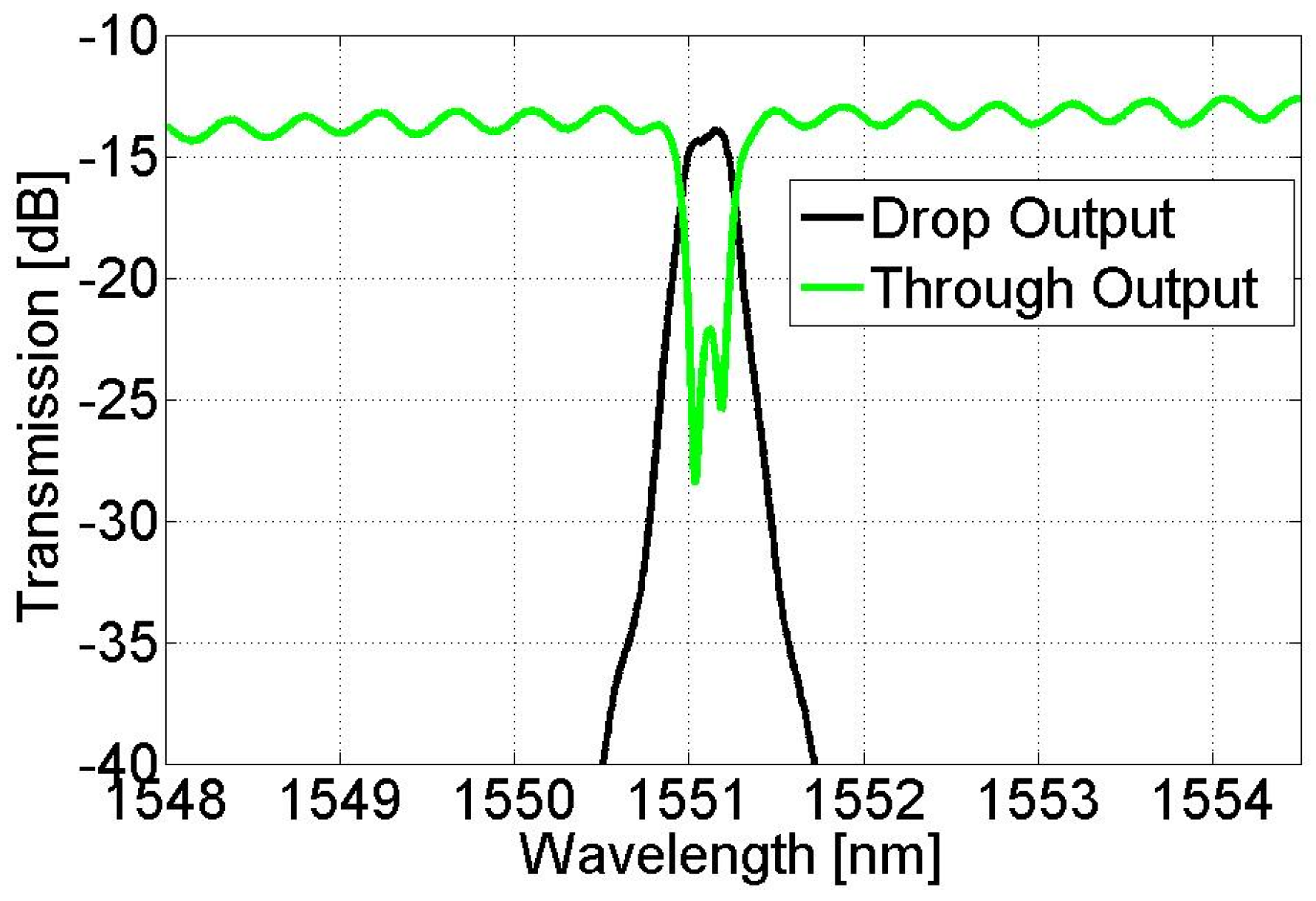

| Parameter | Units | Racetracks | Rings |

|---|---|---|---|

| Insertion Loss | dB | 2.0 | 4.6 |

| −3 dB Bandwidth | GHz | 47 | 73 |

| −20 dB Bandwidth | GHz | 158 | 208 |

| Suppression @ 100 GHz | dB | 24 | 19 |

| Parameter | Units | Racetracks | Rings |

|---|---|---|---|

| Bus waveguide (width × height) | nm × nm | 500 × 220 | 500 × 100 |

| Resonator waveguide (width × height) | nm × nm | 500 × 220 | 800 × 100 |

| Straight-leg | nm | 8160 | N.A. |

| Curve radius (@ waveguide center) | nm | 3600 | 8400 |

| Bus-to-Resonator gap | nm | 250 | 515 |

| Inter-Resonator gap | nm | 460 | 355 |

| Parameter | Units | Racetracks | Rings |

|---|---|---|---|

| Insertion Loss | dB | 1.9–2.9 | 0.8–1.5 |

| −3 dB Bandwidth | GHz | 37–40 | 35–39 |

| −20 dB Bandwidth | GHz | 115–131 | 95–109 |

| Suppression @ 100 GHz | dB | 26–35 | 30–35 |

| Thermo-optical tuning efficiency | mW/nm | 2.5–2.6 | 4.8–5.5 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Marchetti, R.; Vitali, V.; Lacava, C.; Cristiani, I.; Giuliani, G.; Muffato, V.; Fournier, M.; Abrate, S.; Gaudino, R.; Temporiti, E.; et al. Low-Loss Micro-Resonator Filters Fabricated in Silicon by CMOS-Compatible Lithographic Techniques: Design and Characterization. Appl. Sci. 2017, 7, 174. https://doi.org/10.3390/app7020174

Marchetti R, Vitali V, Lacava C, Cristiani I, Giuliani G, Muffato V, Fournier M, Abrate S, Gaudino R, Temporiti E, et al. Low-Loss Micro-Resonator Filters Fabricated in Silicon by CMOS-Compatible Lithographic Techniques: Design and Characterization. Applied Sciences. 2017; 7(2):174. https://doi.org/10.3390/app7020174

Chicago/Turabian StyleMarchetti, Riccardo, Valerio Vitali, Cosimo Lacava, Ilaria Cristiani, Guido Giuliani, Viviane Muffato, Maryse Fournier, Silvio Abrate, Roberto Gaudino, Enrico Temporiti, and et al. 2017. "Low-Loss Micro-Resonator Filters Fabricated in Silicon by CMOS-Compatible Lithographic Techniques: Design and Characterization" Applied Sciences 7, no. 2: 174. https://doi.org/10.3390/app7020174

APA StyleMarchetti, R., Vitali, V., Lacava, C., Cristiani, I., Giuliani, G., Muffato, V., Fournier, M., Abrate, S., Gaudino, R., Temporiti, E., Carroll, L., & Minzioni, P. (2017). Low-Loss Micro-Resonator Filters Fabricated in Silicon by CMOS-Compatible Lithographic Techniques: Design and Characterization. Applied Sciences, 7(2), 174. https://doi.org/10.3390/app7020174