Structure and Principles of Operation of a Quaternion VLSI Multiplier

Abstract

1. Introduction

2. Short Background

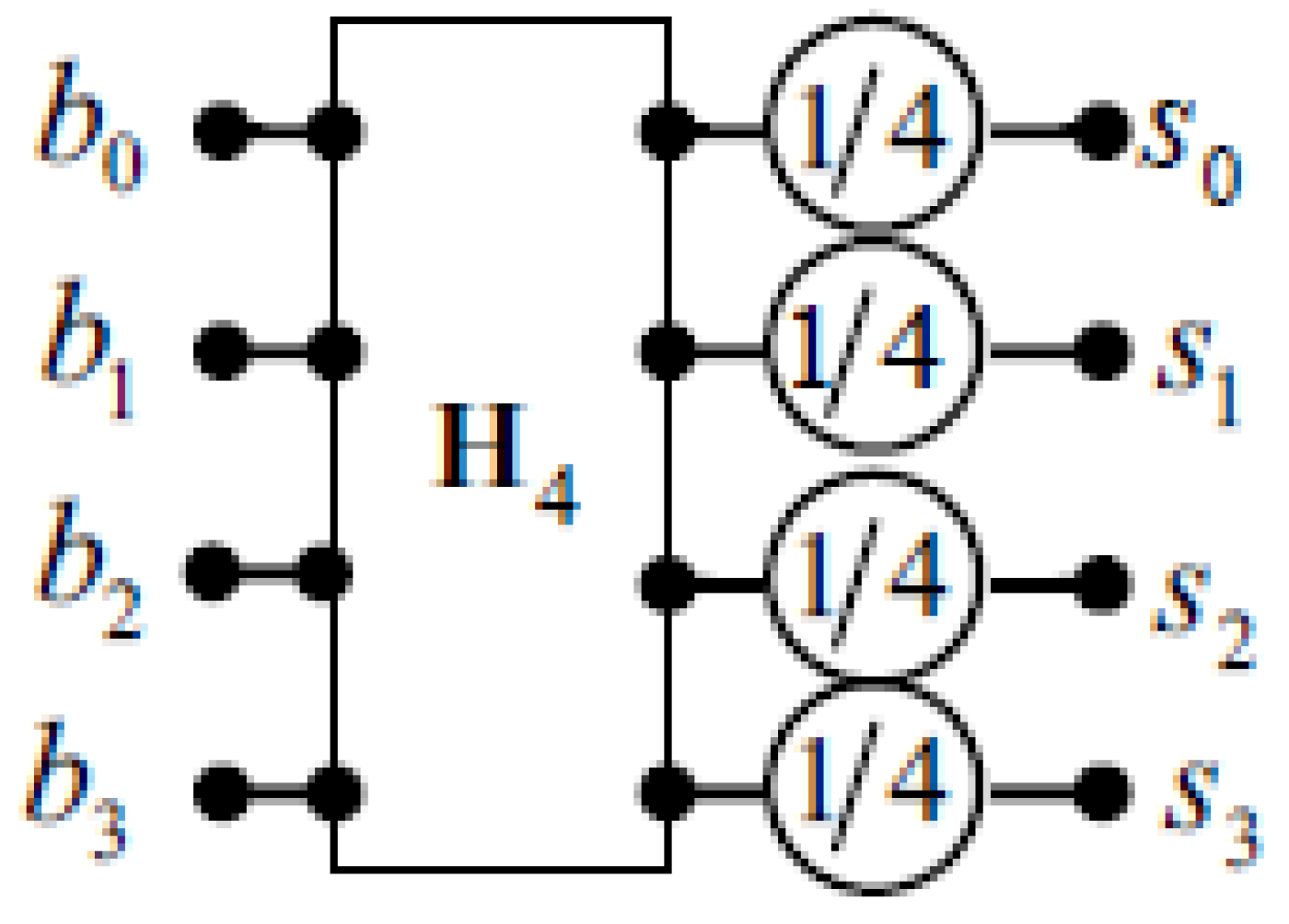

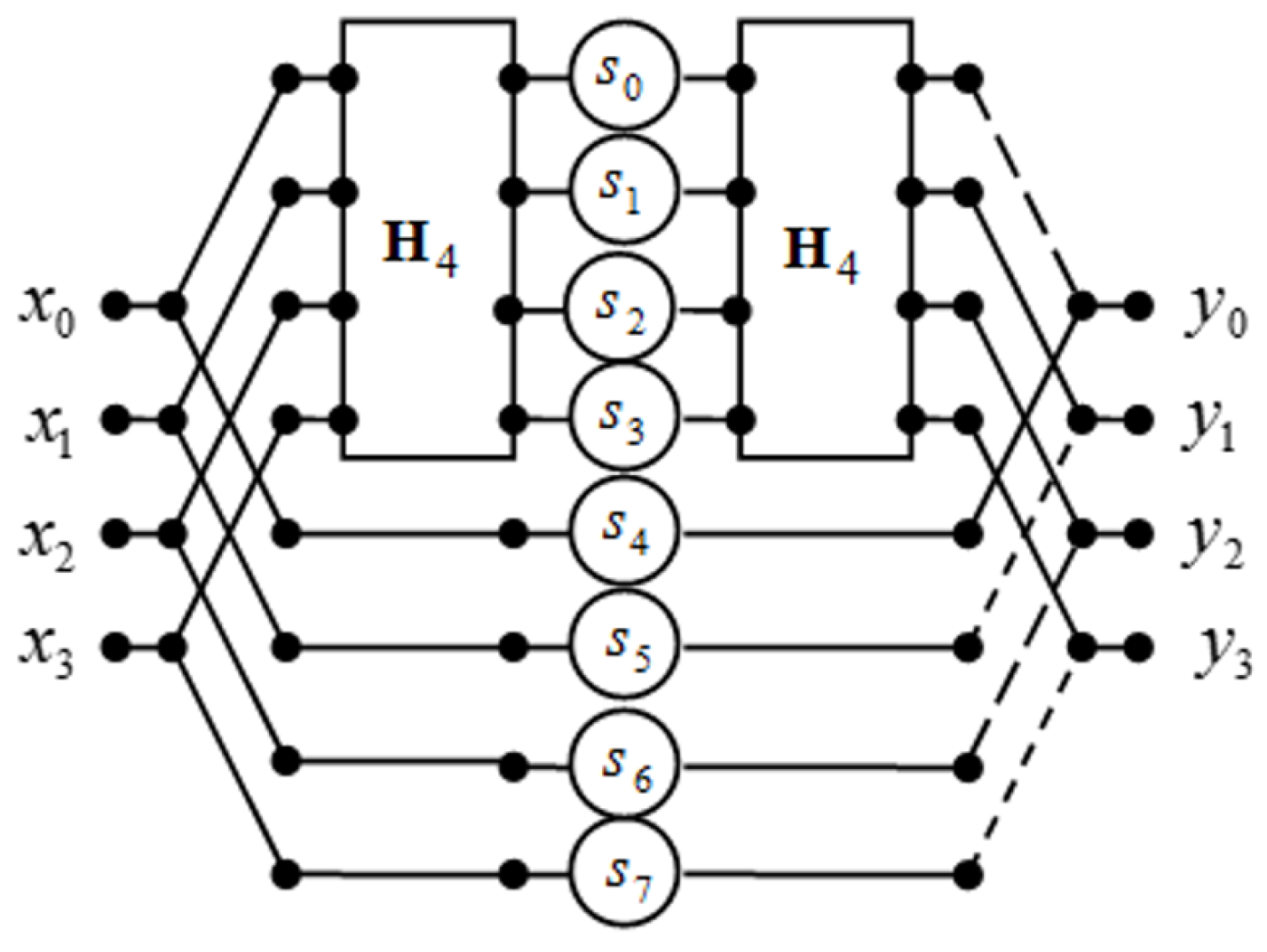

3. Algorithmic Aspect

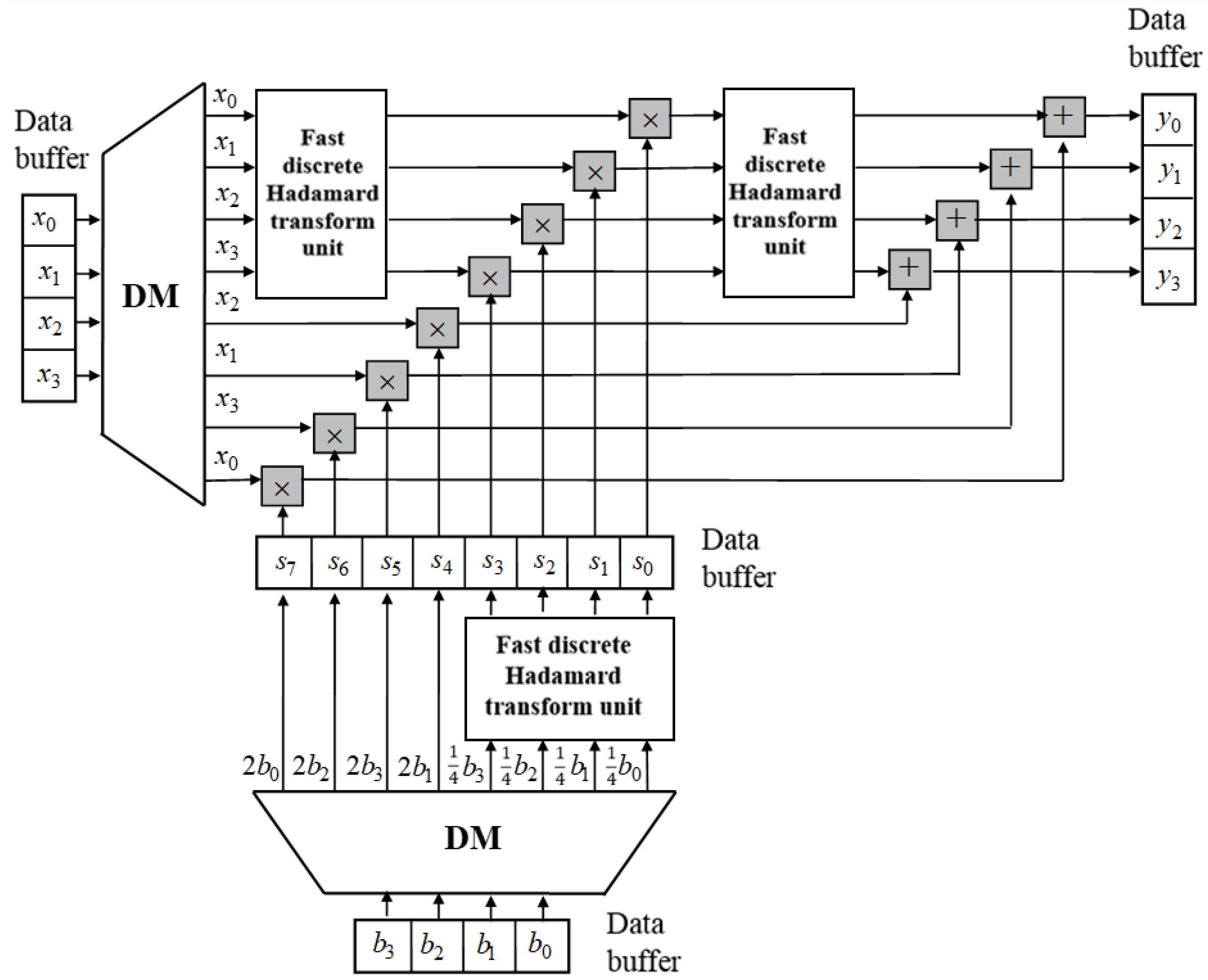

4. Quaternion Multiplier Structure

5. Hardware Implementation of Quaternion Multiplication

5.1. Implementation on FPGA

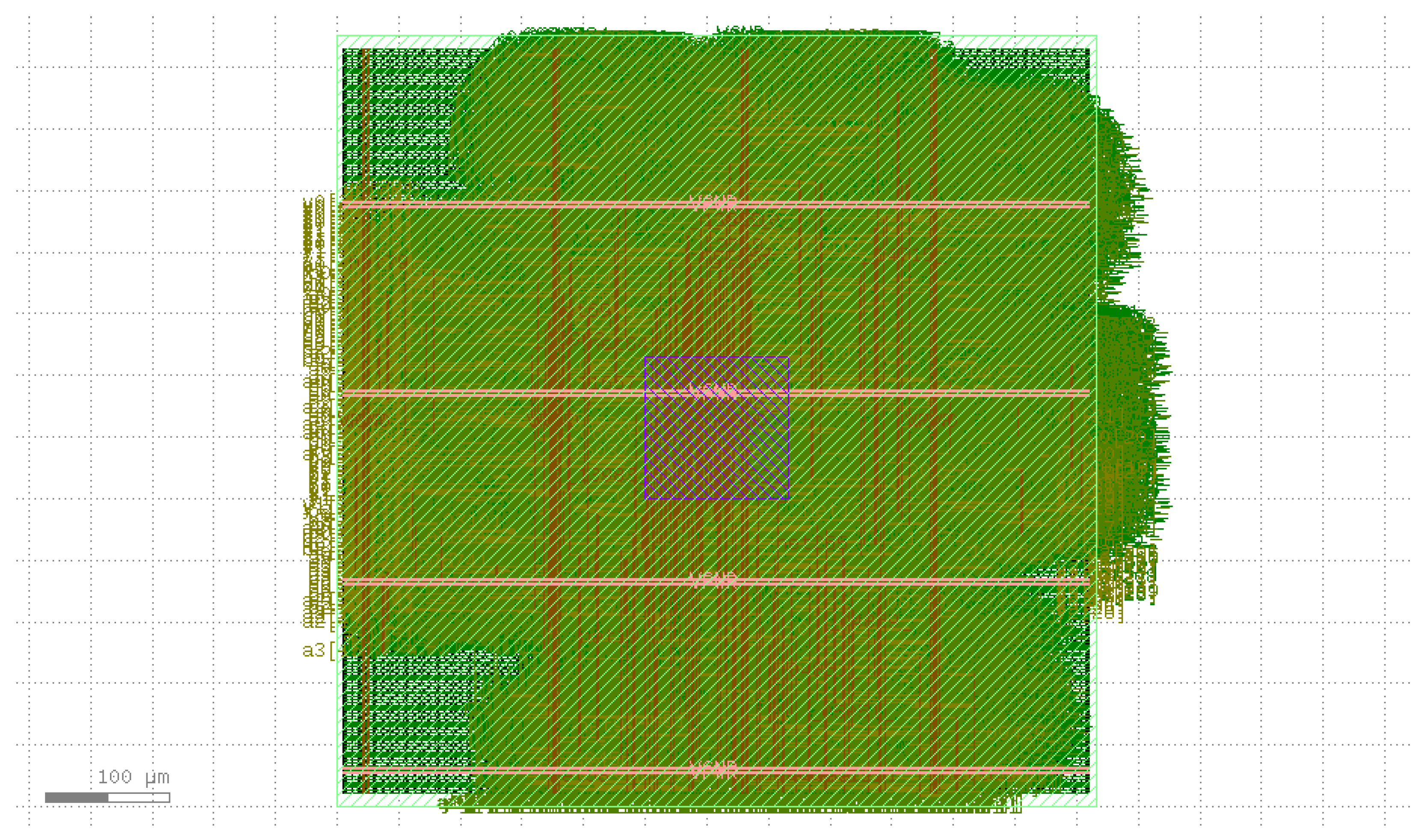

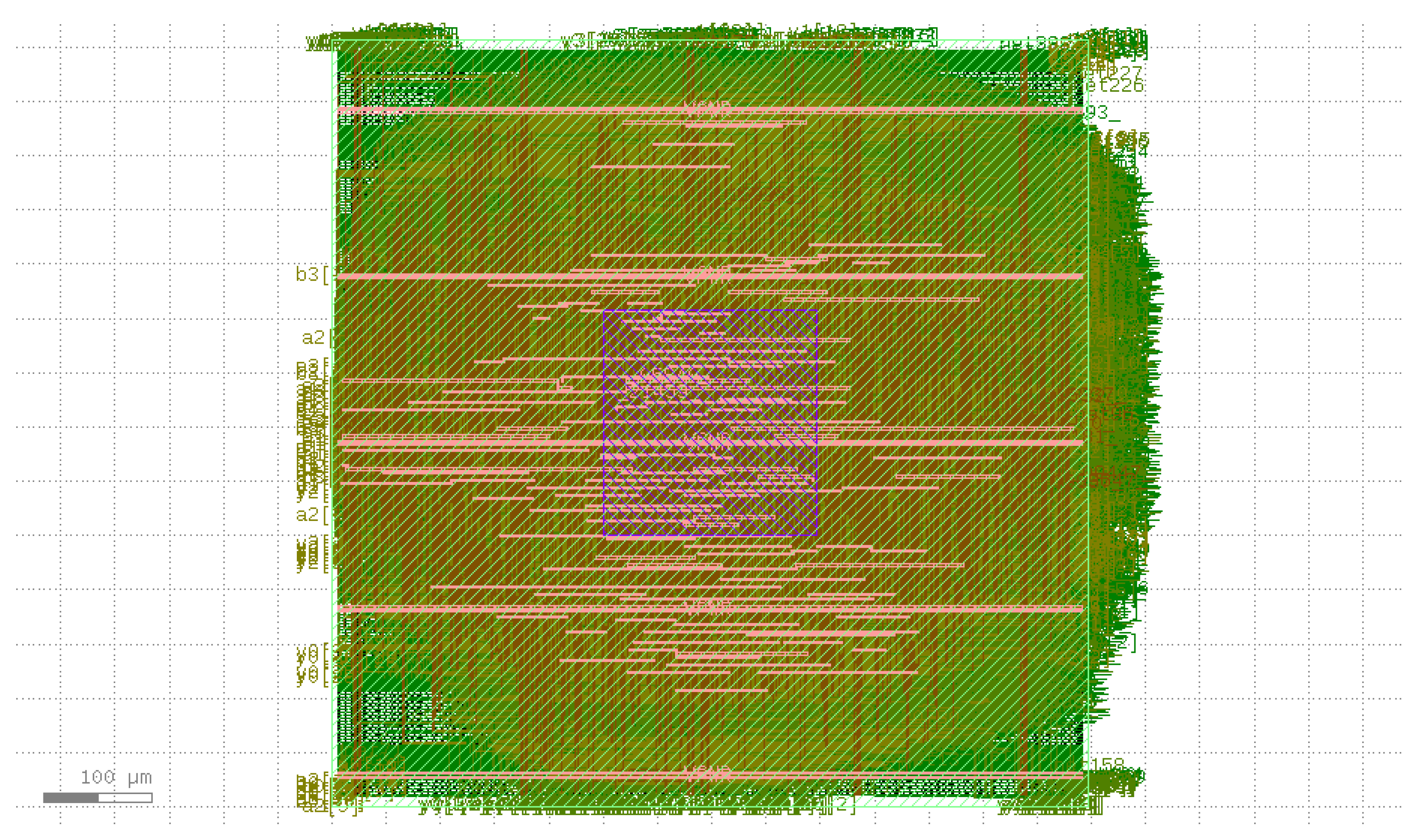

5.2. ASIC Implementation

| Listing 1. Direct implementation of quaternion multiplication |

| library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; architecture Flow of mul is begin process(clk,a0,a1,a2,a3,b0,b1,b2,b3) begin if rising_edge(clk) then y0 <= a0∗b0-a1∗b1-a2∗b2-a3∗b3; y1 <= a0∗b1+a1∗b0+a2∗b3-a3∗b2; y2 <= a0∗b2+a2∗b0+a3∗b1-a1∗b3; y3 <= a0∗b3+a3∗b0+a1∗b2-a2∗b1; end if; end process; end Flow; |

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Vince, J. Quaternions for Computer Graphics; Springer: London, UK, 2011. [Google Scholar]

- Cariow, A.; Cariowa, G.; Majorkowska-Mech, D. An algorithm for quaternion-based 3D rotation. Int. J. Appl. Math. Comput. Sci. 2020, 30, 149–160. [Google Scholar] [CrossRef]

- Schütte, H.D.; Wenzel, J. Hypercomplex numbers in digital signal processing. In Proceedings of the ISCAS ’90, New Orleans, LA, USA, 1–3 May 1990; pp. 1557–1560. [Google Scholar]

- Alfsmann, D.; Göckler, H.G.; Sangwine, S.J.; Ell, T.A. Hypercomplex Algebras in Digital Signal Processing: Benefits and Drawbacks (Tutorial). In Proceedings of the EURASIP 15th European Signal Processing Conference (EUSIPCO 2007), Poznań, Poland, 3–7 September 2007; pp. 1322–1326. [Google Scholar]

- Bülow, T.; Sommer, G. Hypercomplex signals—A novel extension of the analytic signal to the multidimensional case. IEEE Trans. Signal Process. 2001, 49, 2844–2852. [Google Scholar] [CrossRef]

- Moxey, C.E.; Sangwine, S.J.; Ell, T.A. Hypercomplex correlation techniques for vector images. IEEE Trans. Signal Process. 2003, 51, 1941–1953. [Google Scholar] [CrossRef]

- Navarro-Moreno, J.; Ruiz-Molina, J.C.; Oya, A.; Quesada-Rubio, J.M. Detection of continuous-time quaternion signals in additive noise. EURASIP J. Adv. Signal Process. 2012, 2012, 7. [Google Scholar] [CrossRef][Green Version]

- Mayhew, C.; Sanfelice, R.; Sheng, J.; Arcak, M.; Teel, A.R. Quaternion-based hybrid feedback for robust global attitude synchronization. IEEE Trans. Autom. Control 2012, 57, 2122–2227. [Google Scholar] [CrossRef]

- Le Bihan, N.; Sangwine, S.J.; Ell, T.A. Instantaneous frequency and amplitude of orthocomplex modulated signals based on quaternion Fourier transform. Signal Process. 2014, 94, 308–318. [Google Scholar] [CrossRef]

- Witten, B.; Shragge, J. Quaternion-based Signal Processing. In Proceedings of the New Orleans 2006 Annual Meeting, New Orleans, LA, USA, 23–27 June 2006; pp. 2862–2865. [Google Scholar]

- Jahanchahi, C.; Mandic, D. A class of quaternion Kalman filters. IEEE Trans. Neural Netw. Learn. Syst. 2014, 25, 533–544. [Google Scholar] [CrossRef]

- Barthelemy, Q.; Larue, A.; Mars, J. Sparse approximations for quaternionic signals. Adv. Appl. Clifford Algebr. 2014, 24, 383–402. [Google Scholar] [CrossRef]

- Karakasis, E.; Papakostas, G.; Koulouriotis, D.; Tourassis, V. A unified methodology for computing accurate quaternion color moments and moment invariants. IEEE Trans. Image Process. 2014, 23, 596–611. [Google Scholar] [CrossRef]

- Czaplewski, B.; Dzwonkowski, M.; Rykaczewski, R. Digital fingerprinting based on quaternion encryption scheme for gray-tone images. J. Telecommun. Inf. Technol. 2014, 2014, 3–11. [Google Scholar] [CrossRef]

- Wang, G.; Liu, Y.; Zhao, T. A quaternion-based switching filter for colour image denoising. Signal Process. 2014, 102, 216–225. [Google Scholar] [CrossRef]

- Szczȩsna, A.; Słupik, J.; Janiak, M. Motion data denoising based on the quaternion lifting scheme multiresolution transform. Mach. Graph. Vis. 2011, 20, 237–249. [Google Scholar]

- Bayro-Corrochano, E. Multi-resolution image analysis using the quaternion wavelet transform. Numer. Algorithms 2005, 39, 35–55. [Google Scholar] [CrossRef]

- Majorkowska_Mech, D.; Cariow, A. One-Dimensional Quaternion Discrete Fourier Transform and an Approach to Its Fast Computation. Electronics 2023, 12, 4974. [Google Scholar] [CrossRef]

- Cariow, A.; Cariowa, G. Fast Algorithms for Quaternion-Valued Convolutional Neural Networks. IEEE Trans. Neural Netw. Learn. Syst. 2021, 32, 457–462. [Google Scholar] [CrossRef]

- Belardo, F.; Brunetti, M.; Coble, M.J.; Reff, N.; Skogman, H. Spectra of quaternion unit gain graphs. Linear Algebra Its Appl. 2022, 632, 15–49. [Google Scholar] [CrossRef]

- Kyrchei, I.I.; Treister, E.; Pelykh, O. The determinant of the Laplacian matrix of a quaternion unit gain graph. Discret. Math. 2024, 347, 113955. [Google Scholar] [CrossRef]

- Kidambi, S.S.; Guibaly, F.E.; Antoniou, A. Area-Efficient Multipliers for Digital Signal Processing Applications. IEEE Trans. Circuits Syst.-II 1996, 43, 90–95. [Google Scholar] [CrossRef]

- Immareddy, S.; Sundaramoorthy, A. A survey paper on design and implementation of multipliers for digital system applications. Artif. Intell. Rev. 2022, 55, 4575–4603. [Google Scholar]

- Wen, M.C.; Wang, S.J.; Lin, Y.N. Low-power Parallel Multiplier with Column Bypassing. Electron. Lett. 2005, 41, 581–583. [Google Scholar] [CrossRef]

- Berkeman, A.; Öwall, V.; Torkelson, M. A Low Logic Depth Complex Multiplier Using Distributed Arithmetic. IEEE J. Solid-State Circuits 2000, 35, 656–659. [Google Scholar] [CrossRef]

- Mahdy, Y.B.; Ali, S.A.; Shaaban, K.M. Algorithm and two efficient implementations for complex multiplier. In Proceedings of the ICECS ’99. 6th IEEE International Conference on Electronics, Circuits and Systems, Paphos, Cyprus, 5–8 September 1999; pp. 949–952. [Google Scholar]

- Soulas, T.; Villeger, D.; Oklobdzija, V.G. An ASIC macro cell multiplier for complex numbers. In Proceedings of the 1993 European Conference on Design Automation with the European Event in ASIC Design, Paris, France, 22–25 February 1993; pp. 589–593. [Google Scholar]

- Wei, B.W.Y.; Du, H.; Chen, H. A complex-number multiplier using radix-4 digits. In Proceedings of the 12th Symposium on Computer Arithmetic, Washington, DC, USA, 19–21 July 1995; pp. 84–90. [Google Scholar]

- Oklobdzija, V.G.; Villeger, D.; Soulas, T. An Integrated Multiplier for Complex Numbers. J. VLSI Signal Process. 1994, 7, 213–222. [Google Scholar] [CrossRef]

- Sansaloni, T.; Valls, J.; Parhi, K.K. Digit-Serial Complex-Number Multipliers on FPGAs. J. VLSI Signal Process. 2003, 33, 105–115. [Google Scholar] [CrossRef]

- Pascual, A.P.; Valls, J.; Peiro, M.M. Efficient complex-number multipliers mapped on FPGA. In Proceedings of the ICECS ’99. 6th IEEE International Conference on Electronics, Circuits and Systems (Cat. No.99EX357), Paphos, Cyprus, 5–8 September 1999; pp. 1123–1126. [Google Scholar]

- Kong, M.Y.; Langlois, J.M.P.; Al-Khalili, D. Efficient FPGA Implementation of Complex Multipliers using the Logarithmic Number System. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, 18–21 May 2008; pp. 3154–3157. [Google Scholar]

- Perez-Pascual, A.; Sansaloni, T.; Valls, J. FPGA based on-line complex-number multipliers. In Proceedings of the ICECS 2001. 8th IEEE International Conference on Electronics, Circuits and Systems (Cat. No.01EX483), Malta, 2–5 September 2001; pp. 1481–1484. [Google Scholar]

- Ismail, R.C.; Hussin, R. High Performance Complex Number Multiplier Using Booth-Wallace Algorithm. In Proceedings of the IEEE International Conference on Semiconductor Electronics, Kuala Lumpur, Malaysia, 29 October–1 December 2006; pp. 786–790. [Google Scholar]

- He, S.; Torkelson, M. A pipelined bit-serial complex multiplier using distributed arithmetic. In Proceedings of the 1995 IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 30 April–3 May 1995; pp. 2313–2316. [Google Scholar]

- Chang, Y.N.; Parhi, K.K. High-Performance Digit-Serial Complex Multiplier. IEEE Trans. Circuits Syst.-II Analog. Digit. Signal Process. 2000, 47, 570–572. [Google Scholar] [CrossRef]

- Paz, P.; Garrido, M. Efficient Implementation of Complex Multipliers on FPGAs Using DSP Slices. J. Signal Process. Syst. 2023, 95, 543–550. [Google Scholar] [CrossRef]

- Parfieniuk, M.; Petrovsky, A. Quaternion multiplier inspired by the lifting implementation of plane rotations. IEEE Trans. Circuits Syst. I 2010, 57, 2708–2717. [Google Scholar] [CrossRef]

- Parfieniuk, M.; Petrovsky, N.A.; Petrovsky, A.A. Rapid prototyping of quaternion multiplier: From matrix notation to FPGA based circuits. In Rapid Prototyping Technology: Principles and Functional Requirements; InTech: Rijeka, Croatia, 2011; pp. 227–246. [Google Scholar]

- Ţariova, G.; Ţariov, A. Algorithmic aspects of multiplication block number reduction in a two quaternion hardware multiplier. Pomiary. Autom. Kontrola 2010, 56, 688–690. [Google Scholar]

| Resources | Utilization | Available Resources | |

|---|---|---|---|

| Direct Multiplying | Fast Multiplying | ||

| LUT | 640 (1.01%) | 63,400 | |

| FF | 96 (0.08%) | 768 (0.61%) | 12,680 |

| DSP | 16 (6.67%) | 8 (3.33%) | 240 |

| IO | 256 (90.18%) | 257 (90.18%) | 258 |

| BUFG | 1 (3.13%) | 1 (3.13%) | 32 |

| Energy consumption | |||

| clocks | 0.003 W (1%) | 0.01 W (2%) | |

| signals | 0.019 W (5%) | 0.037 W (10%) | |

| logic | <0.001 W (<1%) | 0.016 W (4%) | |

| dsp | 0.04 W (11%) | 0.02 W (5%) | |

| io | 0.302 W (82%) | 0.305 W (79%) | |

| dynamic (sum of the above) | 0.364 W (80%) | 0.388 W (81%) | |

| static | 0.092 W (20%) | 0.092 W (19%) | |

| Resources | Utilization | Available Resources | |

|---|---|---|---|

| Direct Multiplying | Fast Multiplying | ||

| LUT | 62 (0.1%) | 512 (0.81%) | 63,400 |

| FF | 12,680 | ||

| DSP | 17 (7.08%) | 8 (3.33%) | 240 |

| IO | 257 (90.18%) | 257 (90.18%) | 258 |

| BUFG | 1 (3.13%) | 1 (3.13%) | 32 |

| Energy consumption | |||

| clocks | 0.001 W (1%) | 0.001 W (1%) | |

| signals | 0.007 W (5%) | 0.013 W (9%) | |

| logic | <0.001 W (<1%) | <0.005 W (<3%) | |

| dsp | 0.016 W (11%) | 0.008 W (5%) | |

| io | 0.121 W (82%) | 0.122 W (79%) | |

| dynamic (sum of the above) | 0.145 W (61%) | 0.149 W (62%) | |

| static | 0.091 W (39%) | 0.091 W (38%) | |

| Multiplication | Fast | Direct |

|---|---|---|

| Core Area (mm2) | 0.3649850496 | 0.469800576 |

| # Cells | 19,004 | 23,813 |

| AND | 1118 | 4310 |

| NAND | 646 | 802 |

| NOR | 2344 | 1112 |

| OR | 2613 | 3143 |

| XOR | 5061 | 7018 |

| XNOR | 2444 | 2231 |

| Frequency (MHz) | 19.6078 | 19.6078 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cariow, A.; Naumowicz, M.; Handkiewicz, A. Structure and Principles of Operation of a Quaternion VLSI Multiplier. Appl. Sci. 2024, 14, 8123. https://doi.org/10.3390/app14188123

Cariow A, Naumowicz M, Handkiewicz A. Structure and Principles of Operation of a Quaternion VLSI Multiplier. Applied Sciences. 2024; 14(18):8123. https://doi.org/10.3390/app14188123

Chicago/Turabian StyleCariow, Aleksandr, Mariusz Naumowicz, and Andrzej Handkiewicz. 2024. "Structure and Principles of Operation of a Quaternion VLSI Multiplier" Applied Sciences 14, no. 18: 8123. https://doi.org/10.3390/app14188123

APA StyleCariow, A., Naumowicz, M., & Handkiewicz, A. (2024). Structure and Principles of Operation of a Quaternion VLSI Multiplier. Applied Sciences, 14(18), 8123. https://doi.org/10.3390/app14188123