Atomic Layer Deposited SiOX-Based Resistive Switching Memory for Multi-Level Cell Storage

Abstract

:1. Introduction

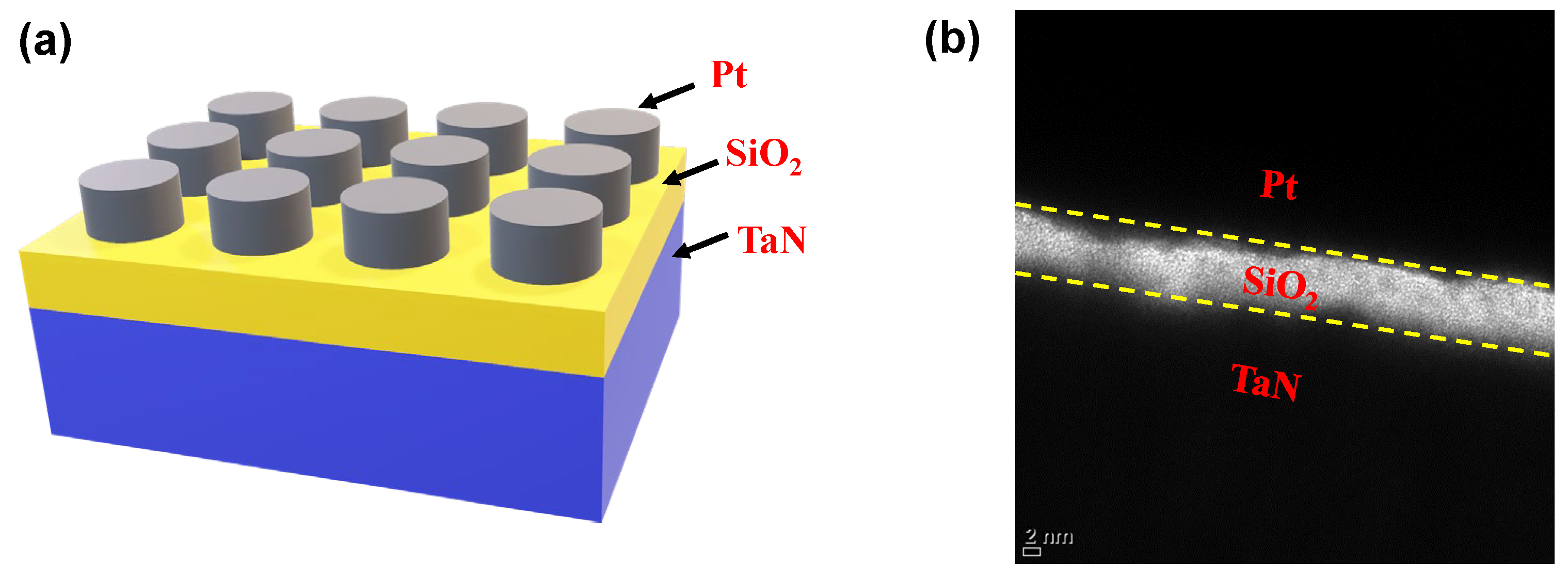

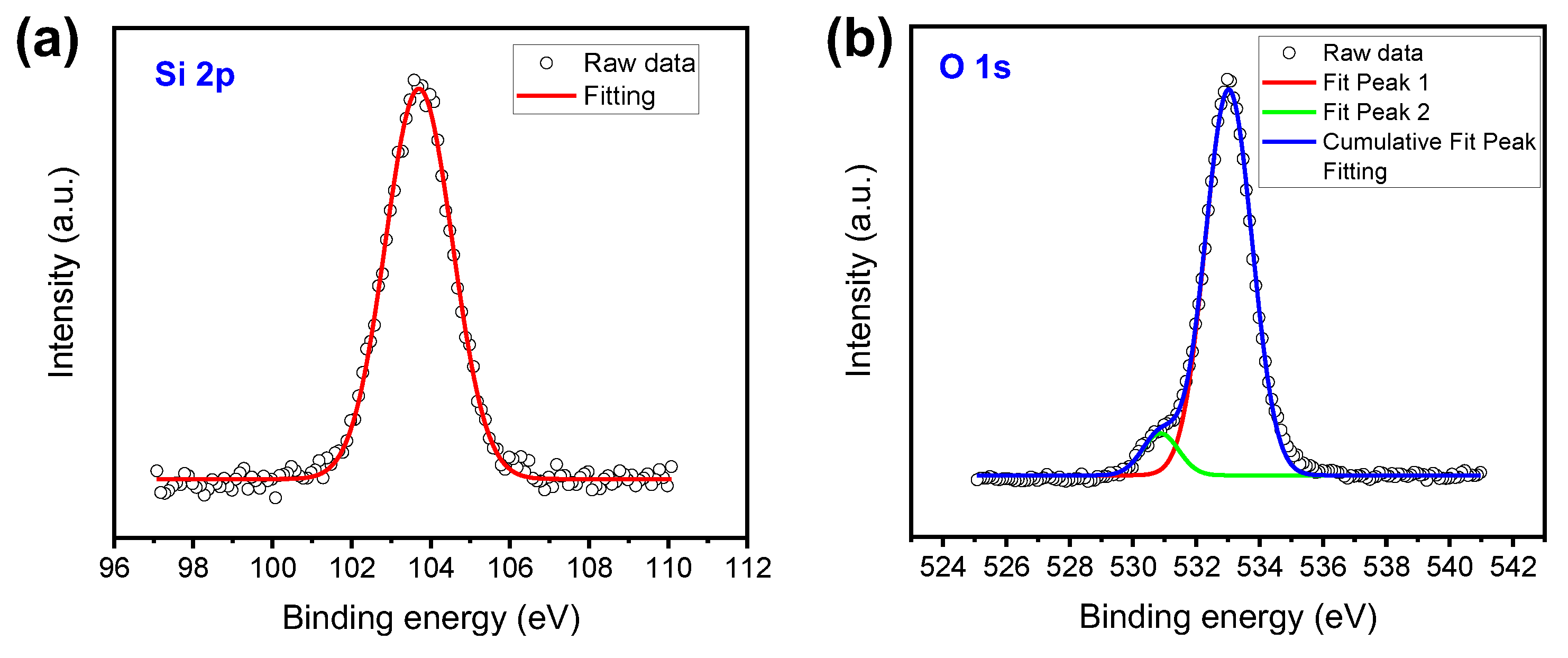

2. Experiments

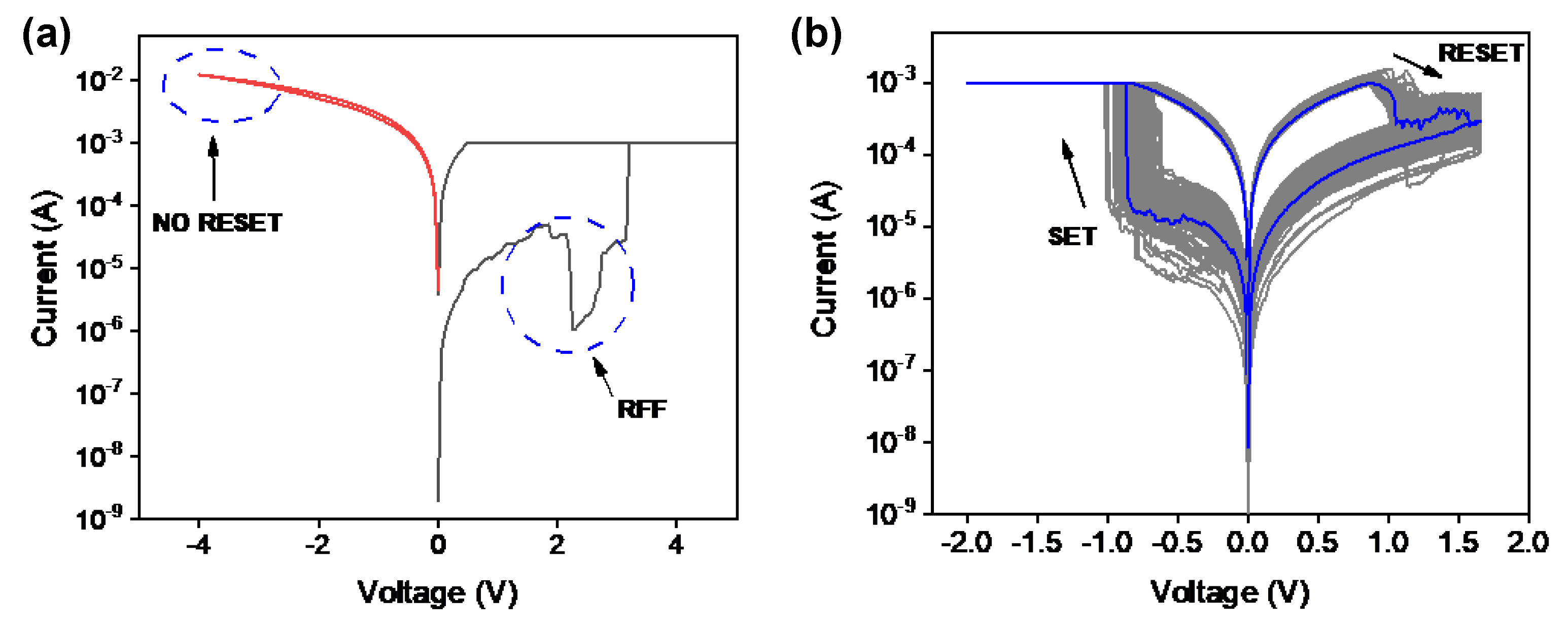

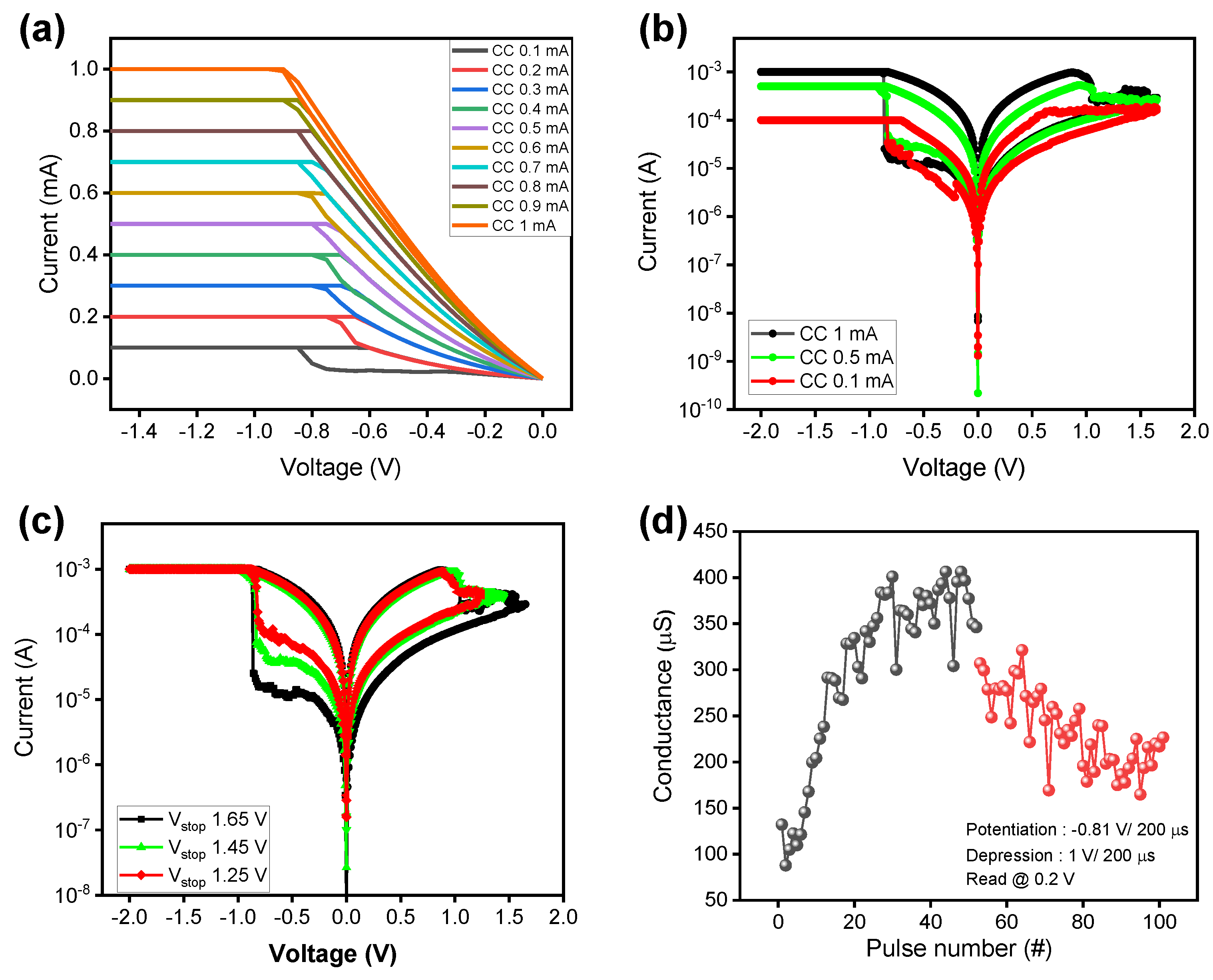

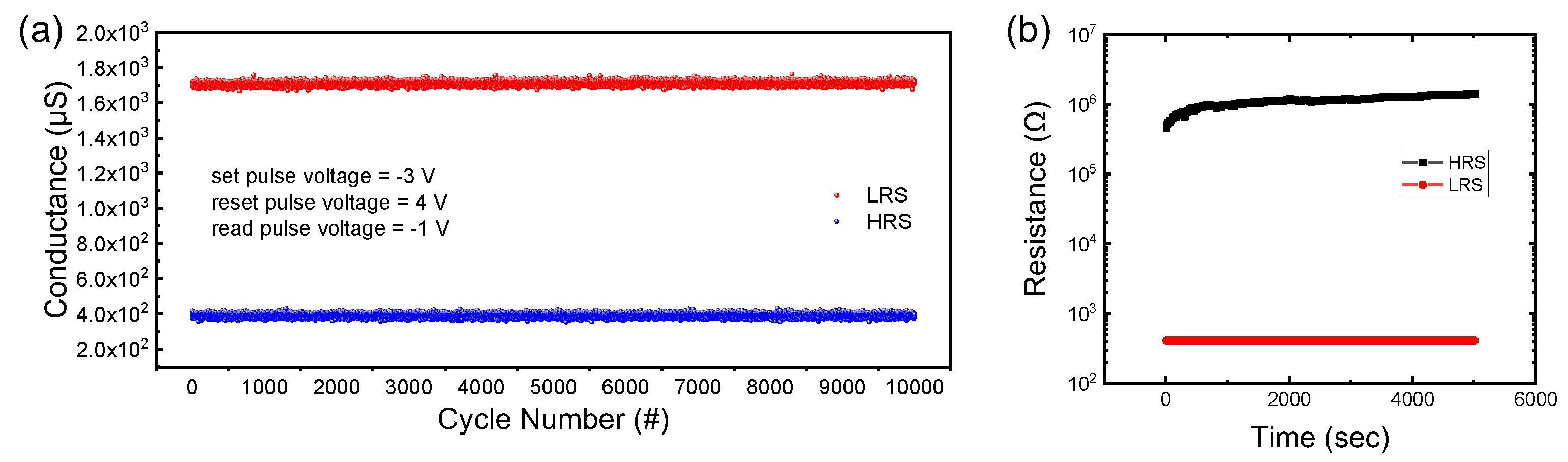

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sawa, A. Resistive switching in transition metal oxides. Mater. Today 2008, 11, 28–36. [Google Scholar] [CrossRef]

- Lee, M.-J.; Lee, C.B.; Lee, D.; Lee, S.R.; Chang, M.; Hur, J.H.; Kim, Y.-B.; Kim, C.-J.; Seo, D.H.; Seo, S.; et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O(5-x)/TaO(2-x) bilayer structures. Nat. Mater. 2011, 10, 625–630. [Google Scholar] [CrossRef] [PubMed]

- Bai, Y.; Wu, H.; Wu, R.; Zhang, Y.; Deng, N.; Yu, Z.; Qian, H. Study of Multi-level Characteristics for 3D Vertical Resistive Switching Memory. Sci. Rep. 2014, 4, 7359. [Google Scholar] [CrossRef]

- Hsu, C.W.; Wang, Y.F.; Wan, C.C.; Wang, I.T.; Chou, C.T.; Lai, W.L.; Lee, Y.J.; Hou, T.H. Homogeneous barrier modulation of TaOX/TiO2 bilayers for ultra-high endurance three-dimensional storage-class memory. Nanotechnology 2014, 25, 165202. [Google Scholar] [CrossRef]

- Mikhaylov, A.; Belov, A.; Korolev, D.; Antonov, I.; Kotomina, V.; Kotina, A.; Gryaznov, E.; Sharapov, A.; Koryazhkina, M.; Kryukov, R.; et al. Multilayer Metal-Oxide Memristive Device with Stabilized Resistive Switching. Adv. Mater. Technol. 2020, 5, 1900607. [Google Scholar] [CrossRef]

- Sun, C.; Lu, S.; Jin, F.; Mo, W.; Song, J.; Dong, K. The Resistive Switching Characteristics of TiN/HfO2/Ag RRAM Devices with Bidirectional Current Compliance. J. Electron. Mater. 2019, 48, 2992–2999. [Google Scholar] [CrossRef]

- Matveyev, Y.; Egorov, K.; Markeev, A.; Zenkevich, A. Resistive switching and synaptic properties of fully atomic layer deposition grown TiN/HfO2/TiN devices. J. Appl. Phys. 2015, 117, 044901. [Google Scholar] [CrossRef]

- Kim, S.; Abbas, Y.; Jeon, Y.R.; Sokolov, A.S.; Ku, B.; Choi, C. Engineering synaptic characteristics of TaOX/HfO2 bi-layered resistive switching device. Nanotechnology 2018, 29, 415204. [Google Scholar] [CrossRef]

- Oh, I.; Pyo, J.; Kim, S. Resistive Switching and Synaptic Characteristics in ZnO/TaON-Based RRAM for Neuromorphic System. Nanomaterials 2022, 12, 2185. [Google Scholar] [CrossRef]

- Kim, S.T.; Cho, W.J. Improvement of multi-level resistive switching characteristics in solution-processed AlOX-based non-volatile resistive memory using microwave irradiation. Semicond. Sci. Technol. 2017, 33, 015009. [Google Scholar] [CrossRef]

- Yang, J.J.; Strukov, D.B.; Stewart, D.R. Memristive devices for computing. Nat. Nanotechnol. 2013, 8, 13. [Google Scholar] [CrossRef] [PubMed]

- Kim, C.-H.; Lim, S.; Woo, S.Y.; Kang, W.M.; Seo, Y.-T.; Lee, S.T.; Lee, S.; Kwon, D.; Oh, S.; Noh, Y. Emerging memory technologies for neuromorphic computing. Nanotechnology 2018, 30, 032001. [Google Scholar] [CrossRef] [PubMed]

- Mikhaylov, A.; Pimashkin, A.; Pigareva, Y.; Gerasimova, S.; Gryaznov, E.; Shchanikov, S.; Zuev, A.; Talanov, M.; Lavrov, I.; Demin, V.; et al. Neurohybrid Memristive CMOS-Integrated Systems for Biosensors and Neuroprosthetics. Front. Mol. Neurosci. 2020, 14, 358. [Google Scholar] [CrossRef] [PubMed]

- Lobov, S.A.; Mikhaylov, A.N.; Shamshin, M.; Makarov, V.A.; Kazantsev, V.B. Spatial Properties of STDP in a Self-Learning Spiking Neural Network Enable Controlling a Mobile Robot. Front. Neurosci. 2020, 14, 88–97. [Google Scholar] [CrossRef] [PubMed]

- Emelyanov, A.V.; Nikiruy, E.K.; Serenko, A.V.; Sitnikov, A.V.; Presnyakov, M.Y.; Rybka, R.B.; Sboev, A.G.; Rylkov, V.V.; Kashkarov, P.K.; Kovalchuk, M.V.; et al. Self-adaptive STDP-based learning of a spiking neuron with nanocomposite memristive weights. Nanotechnology 2019, 31, 045201. [Google Scholar] [CrossRef]

- Demin, V.; Nekhaev, D.; Surazhevsky, I.; Nikiruy, K.; Emelyanov, A.; Nikolaev, S.; Rylkov, V.; Kovalchuk, M. Necessary conditions for STDP-based pattern recognition learning in a memristive spiking neural network. Neural Netw. 2020, 134, 64–75. [Google Scholar] [CrossRef] [PubMed]

- Emelyanov, A.; Nikiruy, K.; Demin, V.; Rylkov, V.; Belov, A.; Korolev, D.; Gryaznov, E.; Pavlov, D.; Gorshkov, O.; Mikhaylov, A.; et al. Yttria-stabilized zirconia cross-point memristive devices for neuromorphic applications. Microelectron. Eng. 2019, 215, 110988. [Google Scholar] [CrossRef]

- Okhonin, S.; Nagoga, M.; Sallese, J.M.; Fazan, P. A capacitor-less 1T-DRAM cell. IEEE Electron. Device Lett. 2002, 23, 85–87. [Google Scholar] [CrossRef]

- Lu, C.-Y.; Hsieh, K.-Y.; Liu, R. Future challenges of flash memory technologies. Microelectron. Eng. 2009, 86, 283–286. [Google Scholar] [CrossRef]

- Jiao, F.; Chen, B.; Ding, K.; Li, K.; Wang, L.; Zeng, X.; Feng, R. Monatomic 2D phase-change memory for precise neuromorphic Computing. Appl. Mat. Today 2020, 20, 100641. [Google Scholar] [CrossRef]

- Bishnoi, R.; Ebrahimi, M.; Oboril, F.; Tahoori, M.B. Improving Write Performance for STT-MRAM. IEEE Trans. Magn. 2016, 52, 1–11. [Google Scholar] [CrossRef]

- Fang, Y.; Yu, Z.; Wang, Z.; Zhang, T.; Yang, Y.; Cai, Y.; Huang, R. Improvement of HfOX-Based RRAM Device Variation by Inserting ALD TiN Buffer Layer. IEEE Electron. Device Lett. 2018, 39, 819–822. [Google Scholar] [CrossRef]

- Arl, D.; Rogé, V.; Adjeroud, N.; Pistillo, B.R.; Sarr, M.; Bahlawane, N.; Lenoble, D. SiO2 thin film growth through a pure atomic layer deposition technique at room temperature. RSC Adv. 2020, 10, 18073–18081. [Google Scholar] [CrossRef] [PubMed]

- Chang, Y.-F.; Fowler, B.; Chen, Y.-C.; Chen, Y.-T.; Wang, Y.; Xue, F.; Zhou, F.; Lee, J.C. Intrinsic SiOx-based unipolar resistive switching memory. II. Thermal effects on charge transport and characterization of multilevel programing. J. Appl. Phys. 2014, 116, 043709. [Google Scholar] [CrossRef]

- Mehonic, A.; Cueff, S.; Wojdak, M.; Hudziak, S.; Jambois, O.; Labbe, C.; Garrido, B.; Rizk, R.; Kenyon, A.J. Resistive switching in silicon suboxide films. J. Appl. Phys. 2012, 111, 074507. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, Y.; Shin, J.; Nam, G.; Chung, D.; Kim, S.; Jeon, J.; Kim, S. Atomic Layer Deposited SiOX-Based Resistive Switching Memory for Multi-Level Cell Storage. Metals 2022, 12, 1370. https://doi.org/10.3390/met12081370

Lee Y, Shin J, Nam G, Chung D, Kim S, Jeon J, Kim S. Atomic Layer Deposited SiOX-Based Resistive Switching Memory for Multi-Level Cell Storage. Metals. 2022; 12(8):1370. https://doi.org/10.3390/met12081370

Chicago/Turabian StyleLee, Yewon, Jiwoong Shin, Giyeong Nam, Daewon Chung, Sungjoon Kim, Joonhyeon Jeon, and Sungjun Kim. 2022. "Atomic Layer Deposited SiOX-Based Resistive Switching Memory for Multi-Level Cell Storage" Metals 12, no. 8: 1370. https://doi.org/10.3390/met12081370

APA StyleLee, Y., Shin, J., Nam, G., Chung, D., Kim, S., Jeon, J., & Kim, S. (2022). Atomic Layer Deposited SiOX-Based Resistive Switching Memory for Multi-Level Cell Storage. Metals, 12(8), 1370. https://doi.org/10.3390/met12081370