Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator

Abstract

1. Introduction

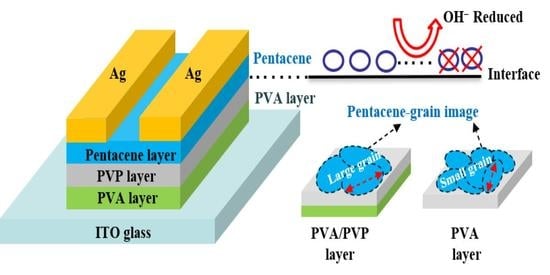

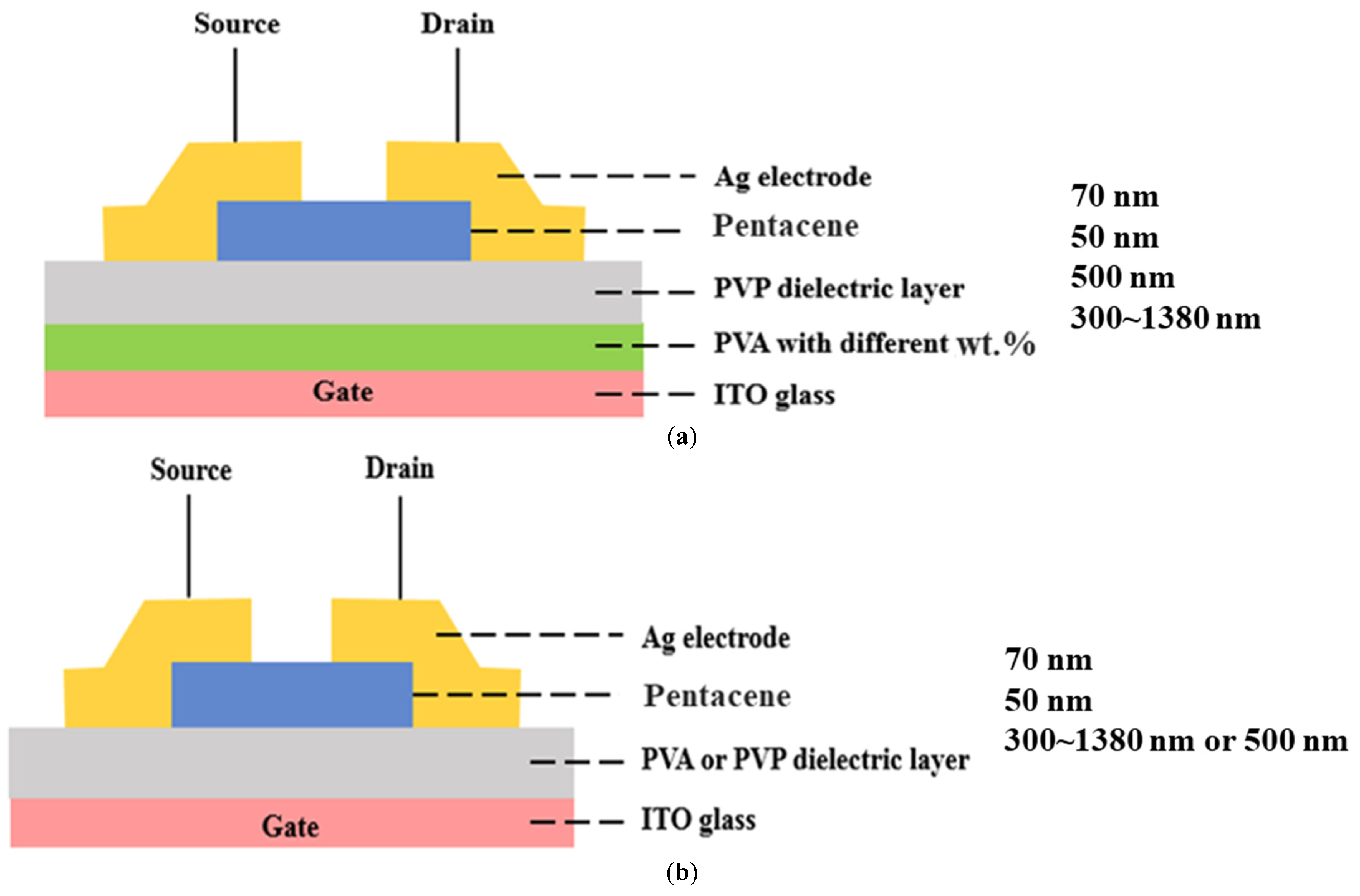

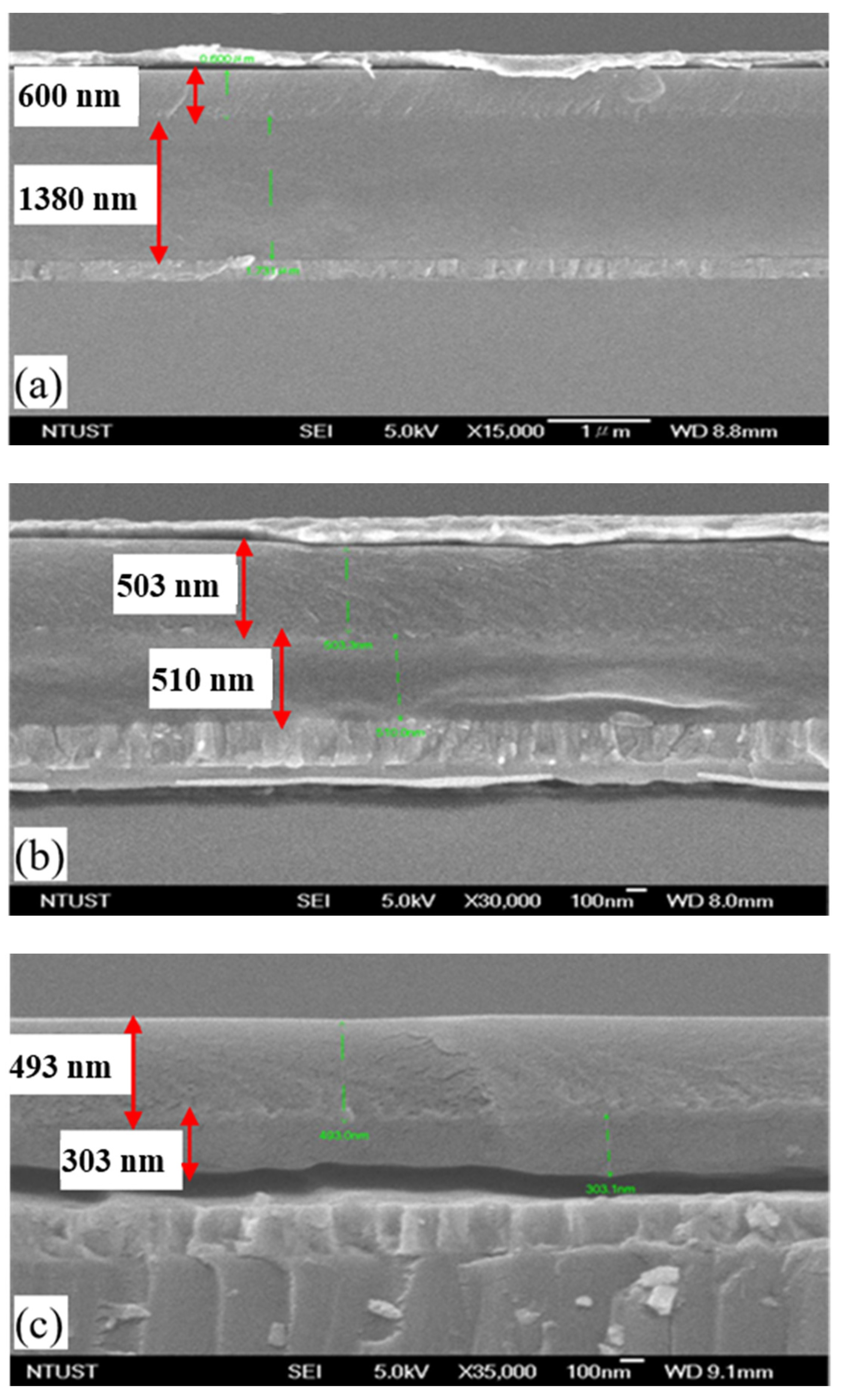

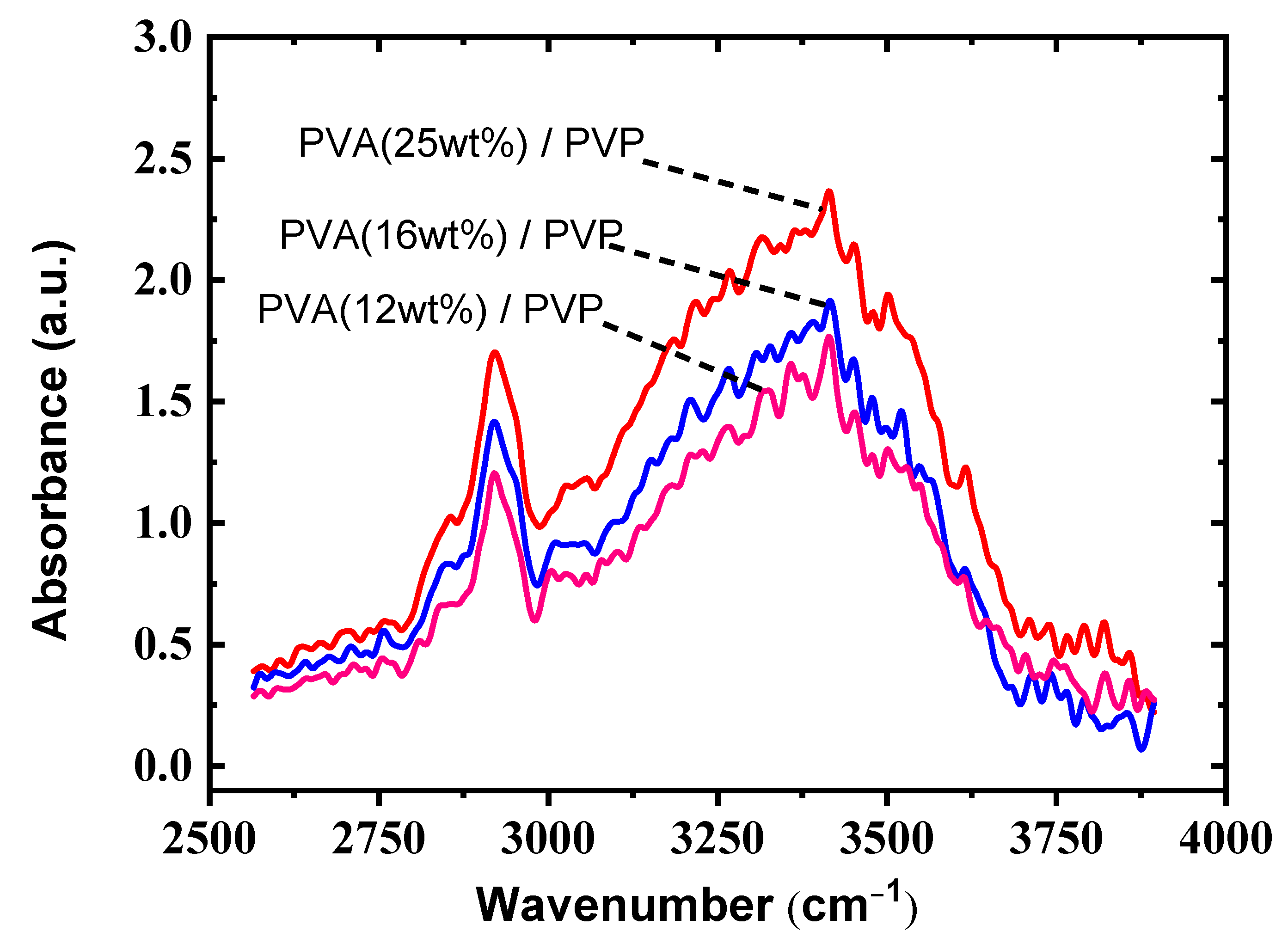

2. Materials and Methods

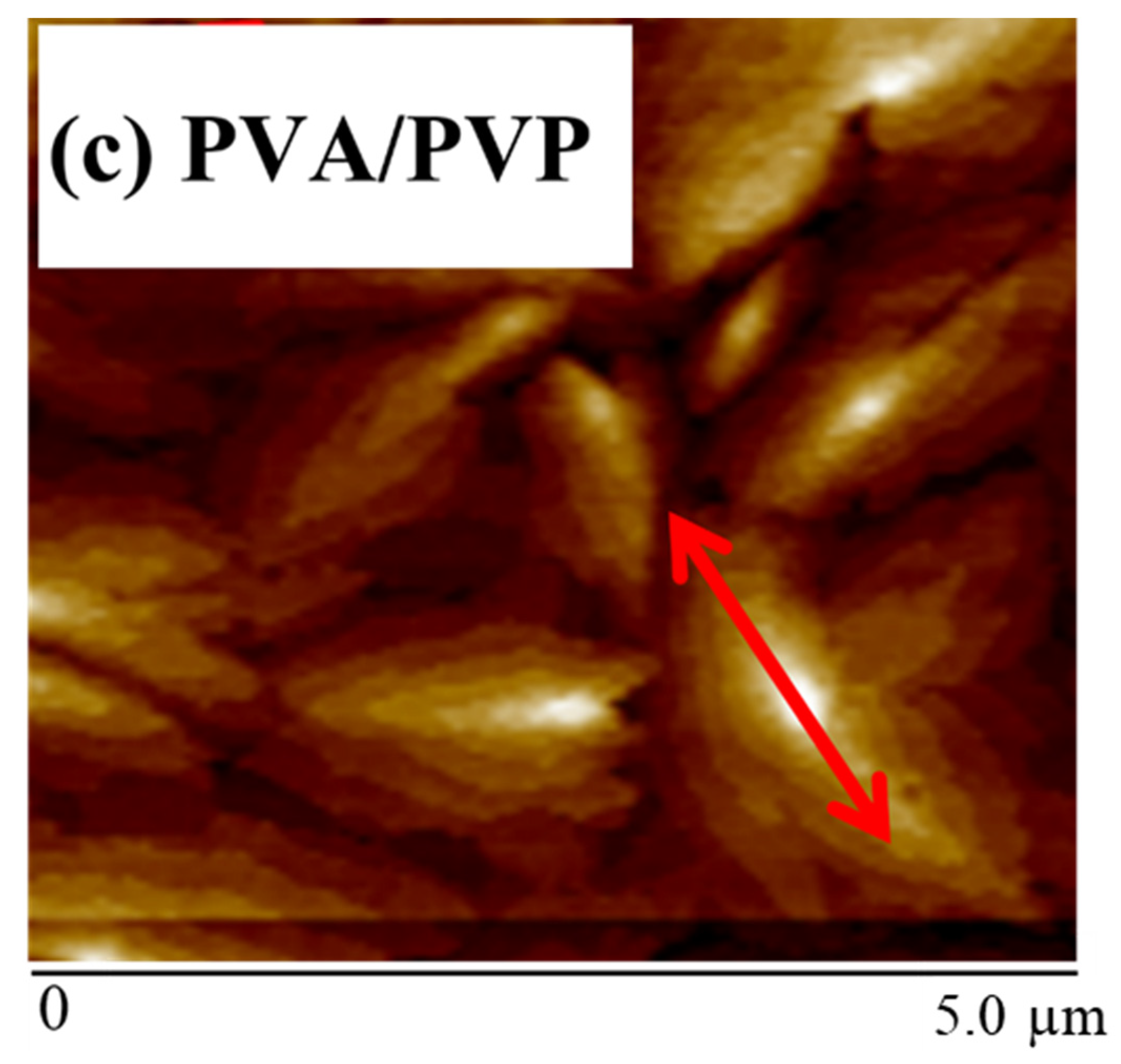

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Fan, C.L.; Chiu, P.C.; Lin, C.C. Low-temperature-deposited SiO2 gate insulator with hydrophobic methyl groups for bottom-contact organic thin-film transistors. IEEE Electron Device Lett. 2010, 31, 1485–1487. [Google Scholar] [CrossRef]

- Fan, C.-L.; Lin, Y.-Z.; Lee, W.-D.; Wang, S.-J.; Huang, C.-H. Improved pentacene growth continuity for enhancing the performance of pentacene-based organic thin-film transistors. Org. Electron. 2012, 13, 2924–2928. [Google Scholar] [CrossRef]

- Wei, C.-Y.; Adriyanto, F.; Lin, Y.-J.; Li, Y.-C.; Huang, T.-J.; Chou, D.-W.; Wang, Y.-H. Pentacene-Based Thin-Film Transistors with a Solution-Process Hafnium Oxide Insulator. IEEE Electron Device Lett. 2009, 30, 1039–1041. [Google Scholar] [CrossRef]

- Kang, B.; Jang, M.J.; Chung, Y.Y.; Kim, H.; Kwak, S.K.; Oh, J.H.; Cho, K.W. Enhancing 2D growth of organic semicon-ductor thin films with macroporous structures via a small-molecule heterointerface. Nat. Commun. 2014, 5, 1–7. [Google Scholar] [CrossRef] [PubMed]

- Jang, K.S.; Kim, W.S.; Won, J.M.; Kim, Y.H.; Myung, S.; Ka, J.W.; Kim, J.S.; Ahn, T.; Yi, M.H. Surface modification of polyimide gate insulators for solution-processed 2,7-didecyl [1]benzothieno[3,2-b][1]benzothiophene (C10-BTBT) thin-film transistors. Phys. Chem. Chem. Phys. 2013, 15, 950–956. [Google Scholar] [CrossRef]

- Klauk, H.; Halik, M.; Zschieschang, U.; Schmid, G.; Radlik, W.; Weber, W. High-mobility polymer gate dielectric pentacene thin film transistors. J. Appl. Phys. 2002, 92, 5259–5263. [Google Scholar] [CrossRef]

- Umeda, T.; Kumaki, D.; Tokito, S. High air stability of threshold voltage on gate bias stress in pentacene TFTs with a hy-droxyl-free and amorphous fluoropolymer as gate insulators. Org. Electron. 2008, 9, 545–549. [Google Scholar] [CrossRef]

- Wilk, G.D.; Wallace, R.M.; Anthony, J.M. High-K gate dielectrics: Current status and materials properties considerations. J. Appl. Phys. 2001, 89, 5243–5275. [Google Scholar] [CrossRef]

- Han, C.Y.; Tang, W.M.; Leung, C.H.; Che, C.M.; Lai, P.T. High-mobility pentacene OTFT with TaLaO gate dielectric passivated by fluorine plasma. Phys. Status Solidi (RRL)—Rapid Res. Lett. 2014, 8, 866–870. [Google Scholar] [CrossRef][Green Version]

- Tsai, T.-D.; Chang, J.-W.; Wen, T.-C.; Guo, T.-F. Manipulating the Hysteresis in Poly(vinyl alcohol)-Dielectric Organic Field-Effect Transistors Toward Memory Elements. Adv. Funct. Mater. 2013, 23, 4206–4214. [Google Scholar] [CrossRef]

- Dimitrakopoulos, C.D.; Malenfant, P.R.L. Organic thin film transistors for large area electronics. Adv. Mater. 2002, 14, 99–117. [Google Scholar] [CrossRef]

- Ortiz, R.P.; Facchetti, A.; Marks, T.J. High-k Organic, Inorganic, and Hybrid Dielectrics for Low-Voltage Organic Field-Effect Transistors. Chem. Rev. 2009, 110, 205–239. [Google Scholar] [CrossRef]

- Hwang, D.K.; Lee, K.; Kim, J.H.; Im, S.; Kim, C.S.; Baik, H.K.; Park, J.H.; Kim, E. Low-voltage high-mobility pentacene thin-film transistors with polymer/high-k oxide double gate dielectrics. Appl. Phys. Lett. 2006, 88, 243513. [Google Scholar] [CrossRef]

- Chang, J.-W.; Hsu, W.-L.; Wu, C.-Y.; Guo, T.-F.; Wen, T.-C. The polymer gate dielectrics and source-drain electrodes on n-type pentacene-based organic field-effect transistors. Org. Electron. 2010, 11, 1613–1619. [Google Scholar] [CrossRef]

- Liu, C.; Zhu, Q.; Jin, W.; Gu, W.; Wang, J. The ultraviolet-ozone effects on organic thin-film transistors with double polymeric dielectric layers. Synth. Met. 2011, 161, 1635–1639. [Google Scholar] [CrossRef]

- Sekine, T.; Fukuda, K.; Kumaki, D.; Tokito, S. Highly stable flexible printed organic thin-film transistor devices under high strain conditions using semiconducting polymers. Jpn. J. Appl. Phys. 2015, 54, 04DK10. [Google Scholar] [CrossRef]

- Mandal, S.; Katiyar, M. Processing and performance of organic insulators as a gate layer in organic thin film transistors fabricated on polyethylene terephthalate substrate. Bull. Mater. Sci. 2013, 36, 653–660. [Google Scholar] [CrossRef][Green Version]

- Wang, N.; Zhao, L.P.; Zhang, C.H.; Li, L. Water states and thermal processability of boric acid modified poly(vinyl alcohol). Appl. Polym. 2016, 133, 43246–43250. [Google Scholar] [CrossRef]

- Seo, J.H.; Kwon, J.-H.; Shin, S.-I.; Suh, K.-S.; Ju, B.-K. Organic thin film transistors with polyvinyl alcohol treated dielectric surface. Semicond. Sci. Technol. 2007, 22, 1039–1043. [Google Scholar] [CrossRef]

- Zhang, H.; Zhang, F.; Sun, J.; Zhang, M.; Hu, Y.; Lou, Z.; Hou, Y.; Teng, F. Solution-processed organic field-effect transistors with cross-linked poly(4-vinylphenol)/polyvinyl alcohol bilayer dielectrics. Appl. Surf. Sci. 2019, 478, 699–707. [Google Scholar] [CrossRef]

- Yoo, S.; Kim, Y.H.; Ka, J.-W.; Kim, Y.S.; Yi, M.H.; Jang, K.-S. Polyimide/polyvinyl alcohol bilayer gate insulator for low-voltage organic thin-film transistors. Org. Electron. 2015, 23, 213–218. [Google Scholar] [CrossRef]

- Ruzgar, S.; Caglar, M. Use of bilayer gate insulator to increase the electrical performance of pentacene based transistor. Synth. Met. 2017, 232, 46–51. [Google Scholar] [CrossRef]

- Singh, V.; Mazhari, B. Impact of scaling of dielectric thickness on mobility in top-contact pentacene organic thin film transistors. J. Appl. Phys. 2012, 111, 034905. [Google Scholar] [CrossRef]

- Egginger, M.; Irimia-Vladu, M.; Schwödiauer, R.; Tanda, A.; Frischauf, I.; Bauer, S.; Sariciftci, N.S. Mobile ionic impurities in poly(vinyl alcohol) gate dielectric: Possible source of the hysteresis in organic field-effect transistors. Adv. Mater. 2008, 20, 1018–1022. [Google Scholar] [CrossRef]

- Zidan, H.M.; El-Ghamaz, N.A.; Abdelghany, A.M.; Lotfy, A. Structural and electrical properties of PVA/PVP blend doped with methylene blue dye. Int. J. Electrochem. Sci. 2016, 11, 9041–9056. [Google Scholar] [CrossRef]

- Kim, T.H.; Han, C.G.; Song, C.K. Instability of threshold voltage under constant bias stress in pentacene thin film transistors employing polyvinylphenol gate dielectric. Thin Solid Films 2008, 516, 1232–1236. [Google Scholar] [CrossRef]

- Fan, C.-L.; Shang, M.-C.; Hsia, M.-Y.; Wang, S.-J.; Huang, B.-R.; Lee, W.-D. Poly(4-vinylphenol) gate insulator with cross-linking using a rapid low-power microwave induction heating scheme for organic thin-film-transistors. APL Mater. 2016, 4, 036105. [Google Scholar] [CrossRef]

- Yu, A.; Qi, Q.; Jiang, P.; Jiang, C. The effects of hydroxyl-free polystyrene buffer layer on electrical performance of pentacene-based thin-film transistors with high-k oxide gate dielectric. Synth. Met. 2009, 159, 1467–1470. [Google Scholar] [CrossRef]

- Matsubara, R.; Ohashi, N.; Sakai, M.; Kudo, K.; Nakamura, M. Analysis of barrier height at crystalline domain boundary and in-domain mobility in pentacene polycrystalline films on SiO2. Appl. Phys. Lett. 2008, 92, 242108. [Google Scholar] [CrossRef]

- Kwak, S.-Y.; Choi, C.G.; Bae, B.-S. Effect of Surface Energy on Pentacene Growth and Characteristics of Organic Thin-Film Transistors. Electrochem. Solid-State Lett. 2009, 12, G37–G39. [Google Scholar] [CrossRef]

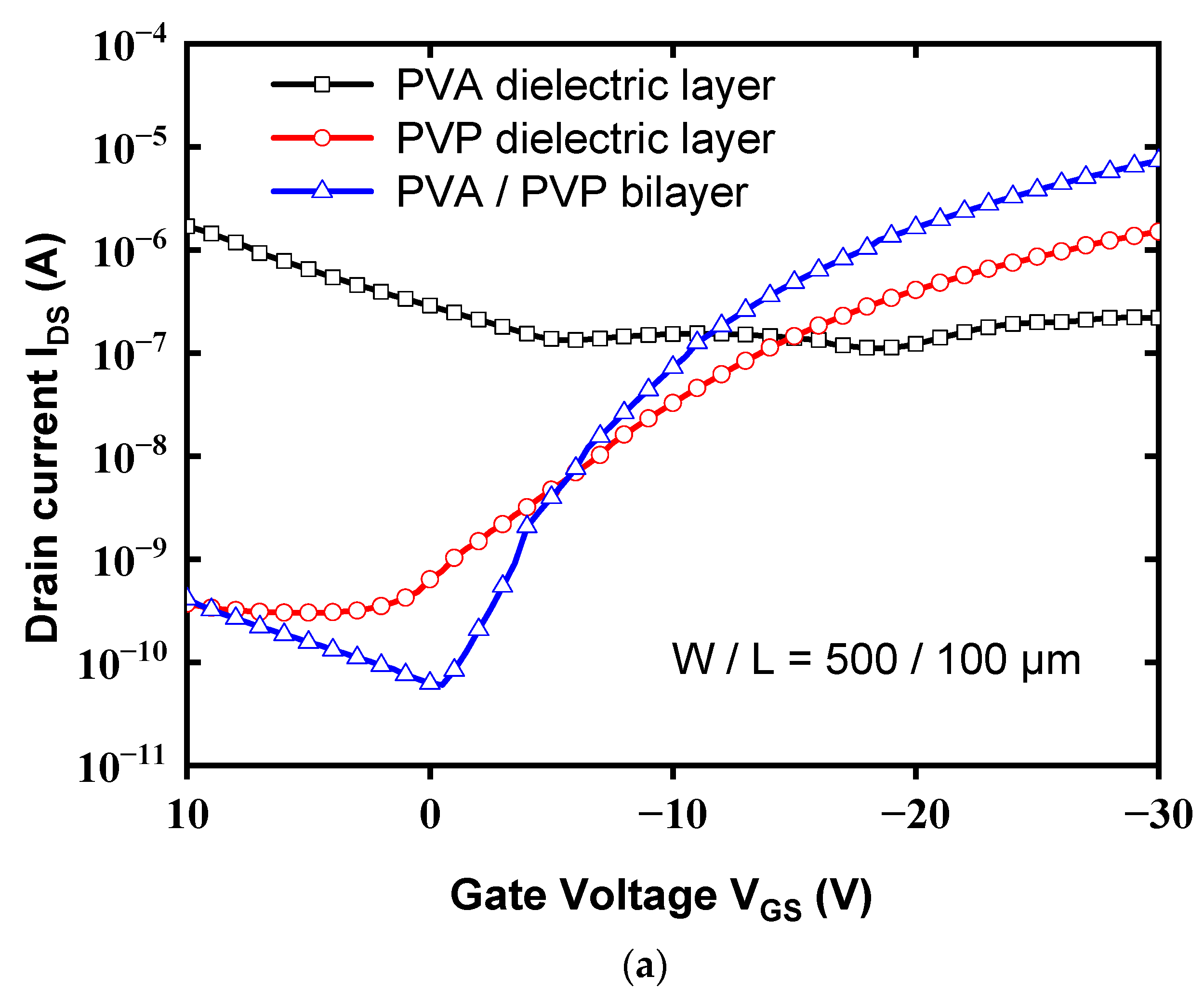

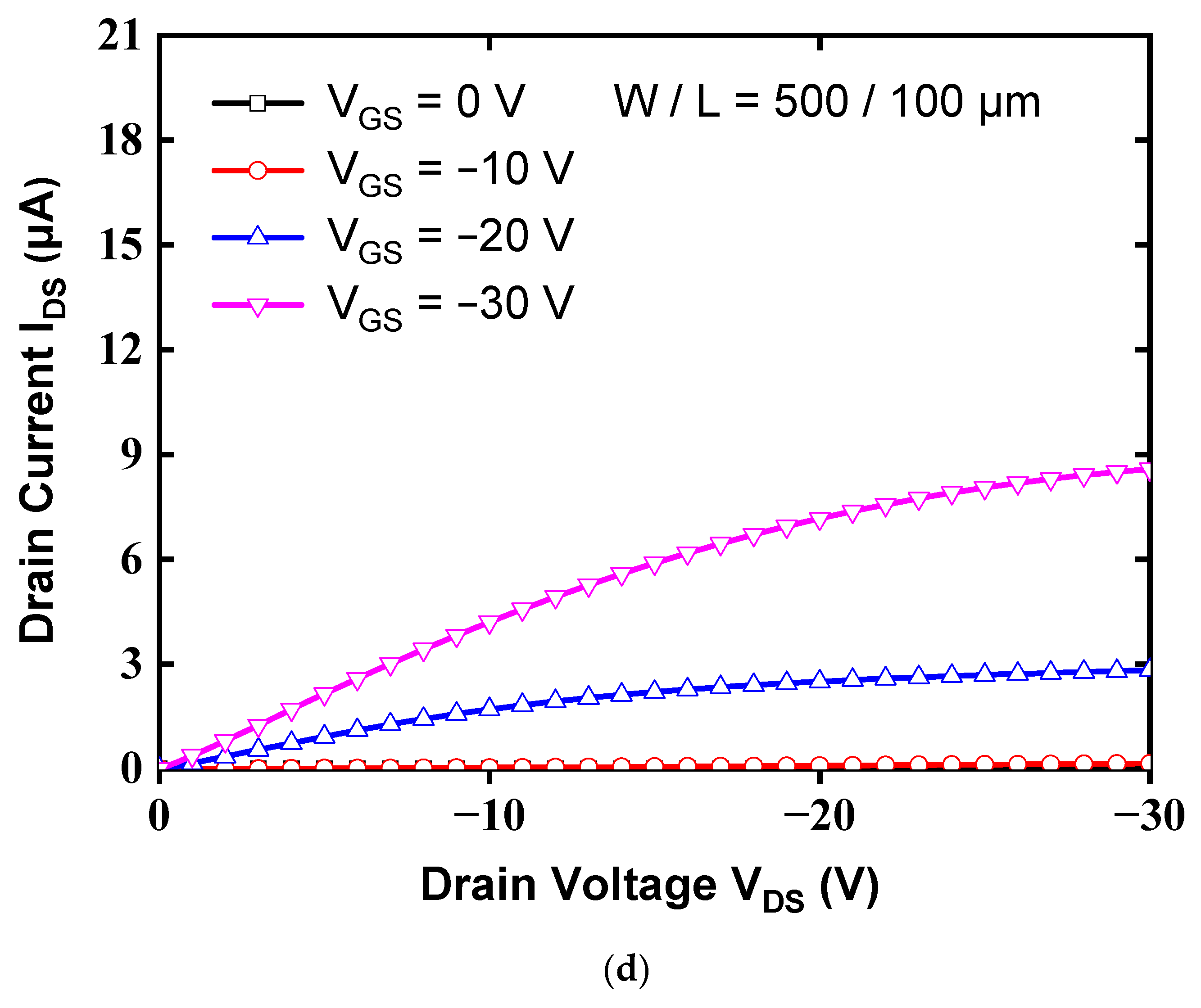

| Insulator Layer | VTH (V) | Mobility (cm2/ Vs) | S.S. (V) | ION/IOFF Ratio |

|---|---|---|---|---|

| PVA | NA | NA | NA | NA |

| PVP | −9.4 | 0.16 | 3.94 | 4.99 × 103 |

| PVA/PVP | −8.6 | 1.12 | 1.41 | 1.21 × 105 |

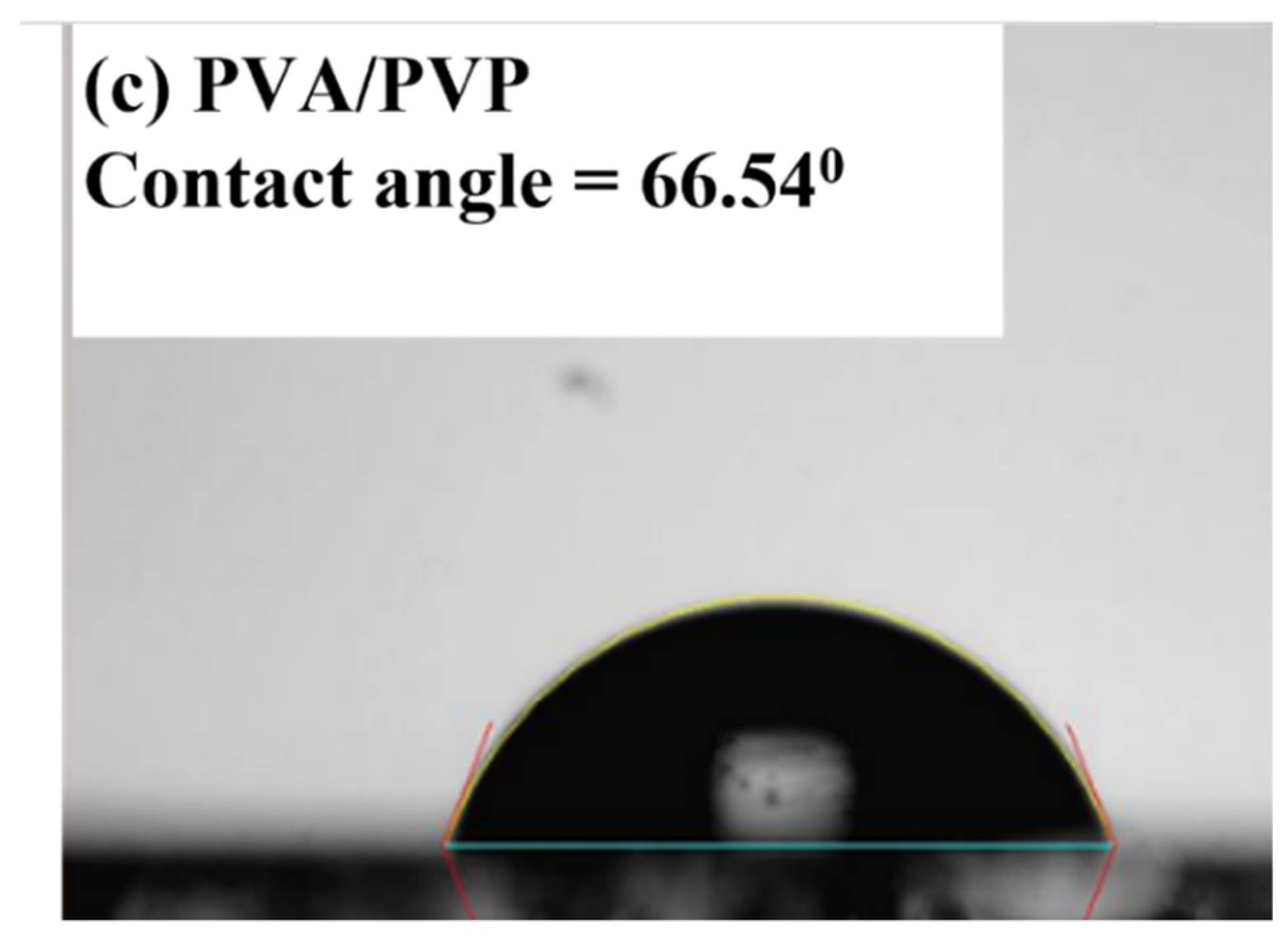

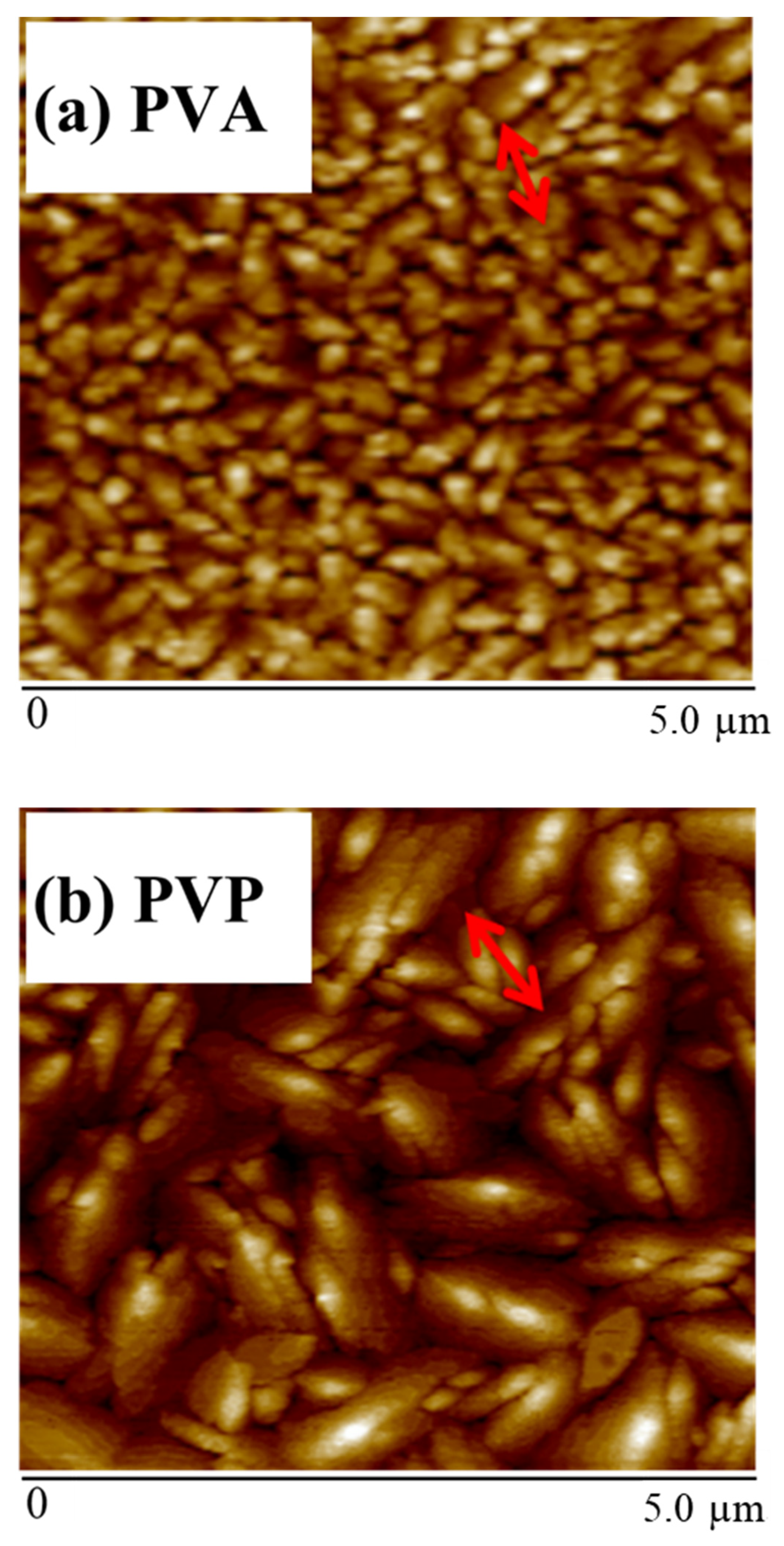

| Contact Angle (°) | |||||

|---|---|---|---|---|---|

| Insulator Layer | DI Water | Diiodomethane | γd (mJ/m2) | γp (mJ/m2) | γ (mJ/m2) |

| PVA | 29.29 | 22.71 | 46.93 | 25.64 | 72.57 |

| PVA/PVP | 66.54 | 26.50 | 45.60 | 7.35 | 52.95 |

| PVP | 69.03 | 29.80 | 44.30 | 6.60 | 50.90 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fan, C.-L.; Tsao, H.-Y.; Shiah, Y.-S.; Yao, C.-W.; Cheng, P.-W. Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator. Polymers 2021, 13, 3941. https://doi.org/10.3390/polym13223941

Fan C-L, Tsao H-Y, Shiah Y-S, Yao C-W, Cheng P-W. Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator. Polymers. 2021; 13(22):3941. https://doi.org/10.3390/polym13223941

Chicago/Turabian StyleFan, Ching-Lin, Hou-Yen Tsao, Yu-Shien Shiah, Che-Wei Yao, and Po-Wei Cheng. 2021. "Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator" Polymers 13, no. 22: 3941. https://doi.org/10.3390/polym13223941

APA StyleFan, C.-L., Tsao, H.-Y., Shiah, Y.-S., Yao, C.-W., & Cheng, P.-W. (2021). Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator. Polymers, 13(22), 3941. https://doi.org/10.3390/polym13223941