Research on the Short-Circuit Characteristics of Trench-Type SiC Power MOSFETs Under Single and Repetitive Pulse Strikes

Abstract

1. Introduction

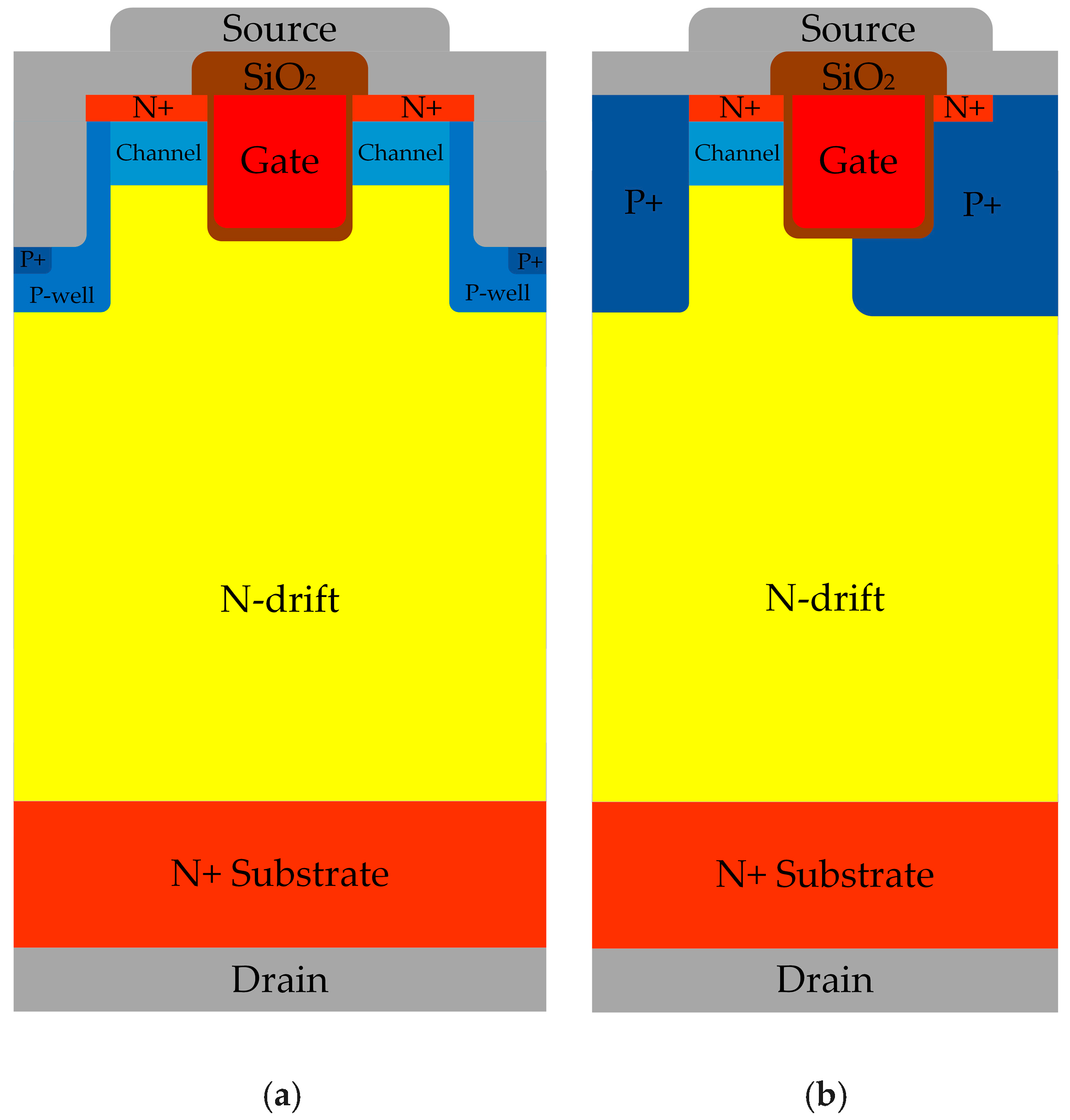

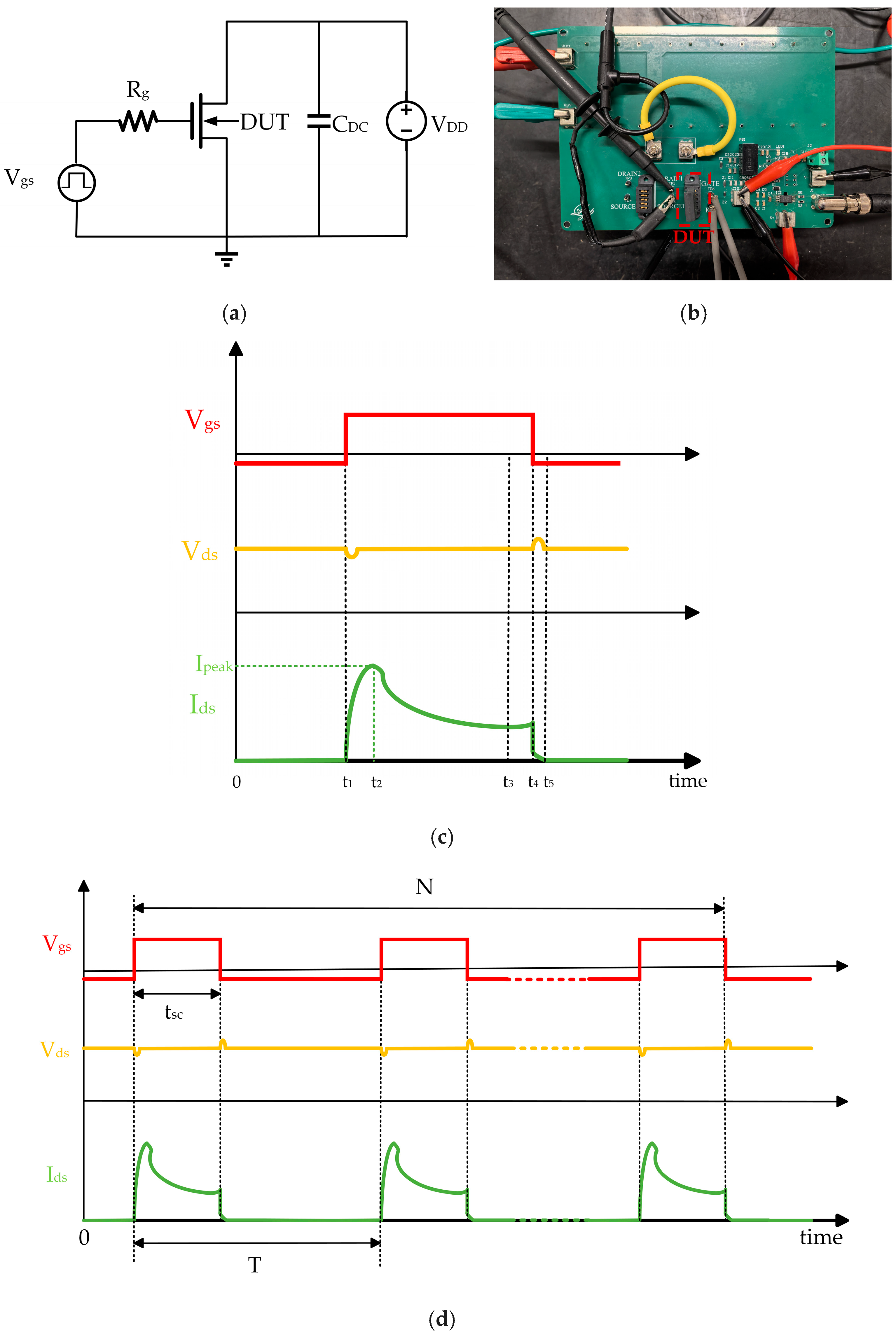

2. Device Structures and Experimental Setup

3. Single Short-Circuit Test Analysis of Trench Power SiC MOSFETs

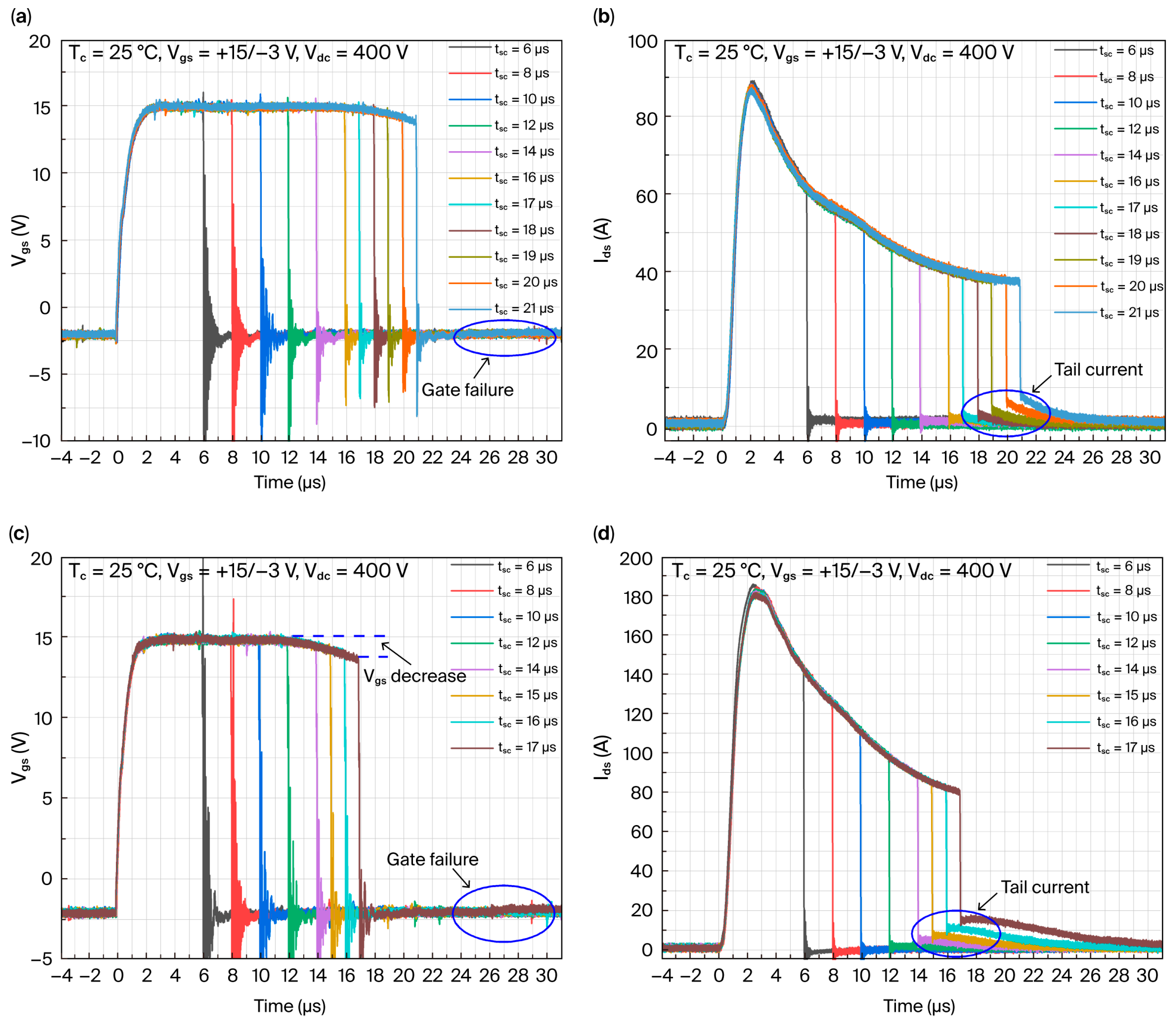

3.1. Single Short-Circuit Test

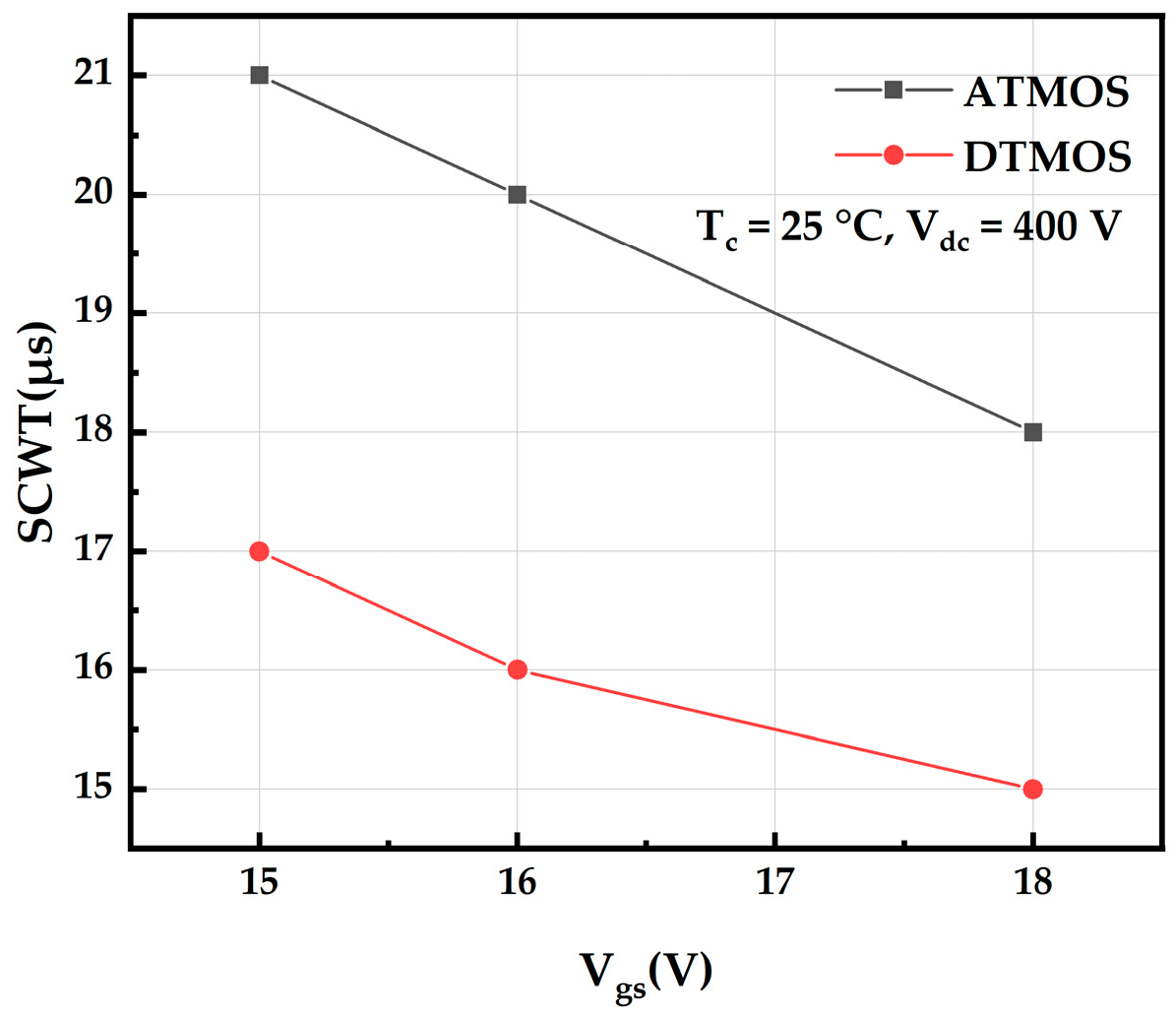

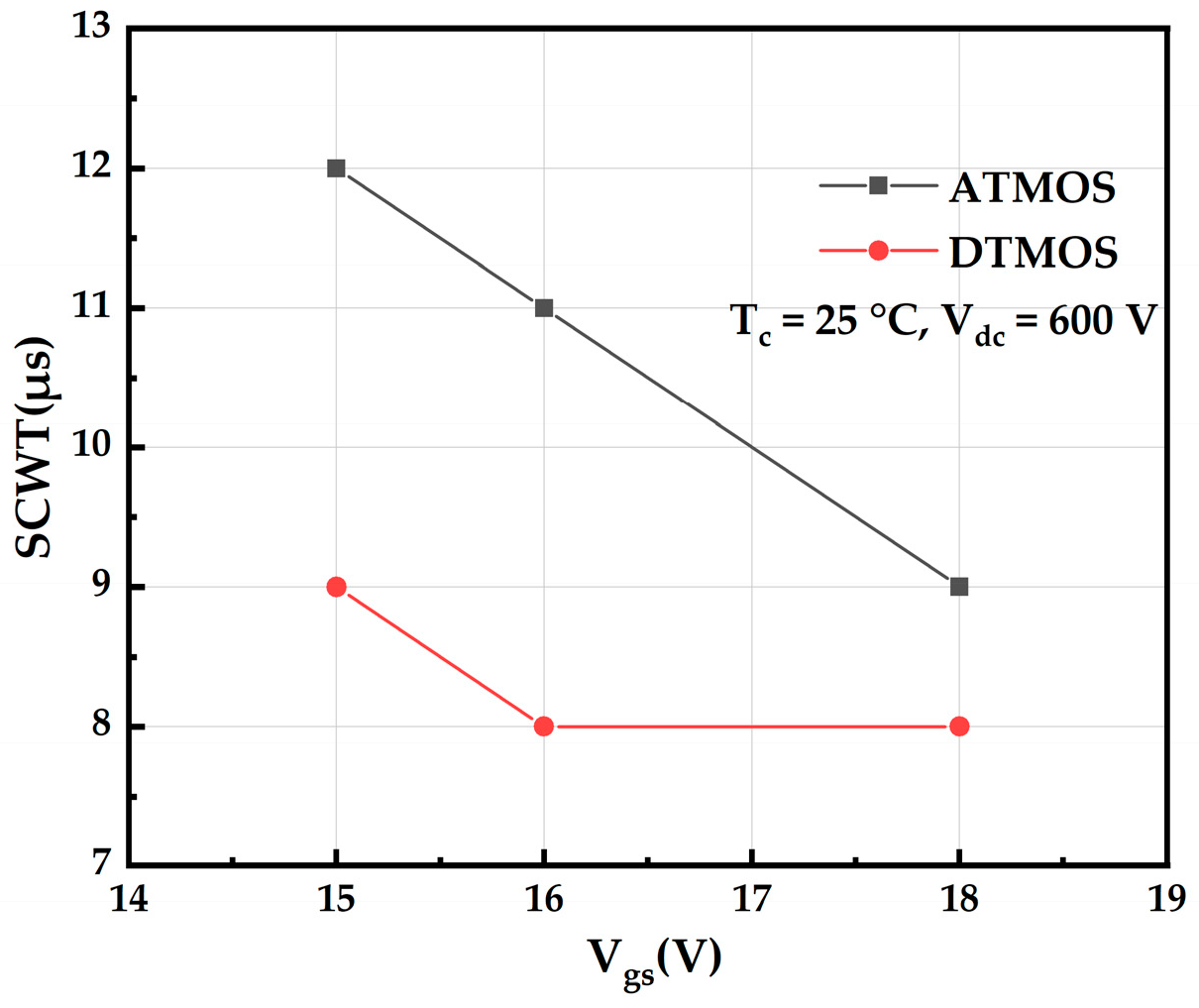

3.1.1. Effect of Gate-Source Voltage

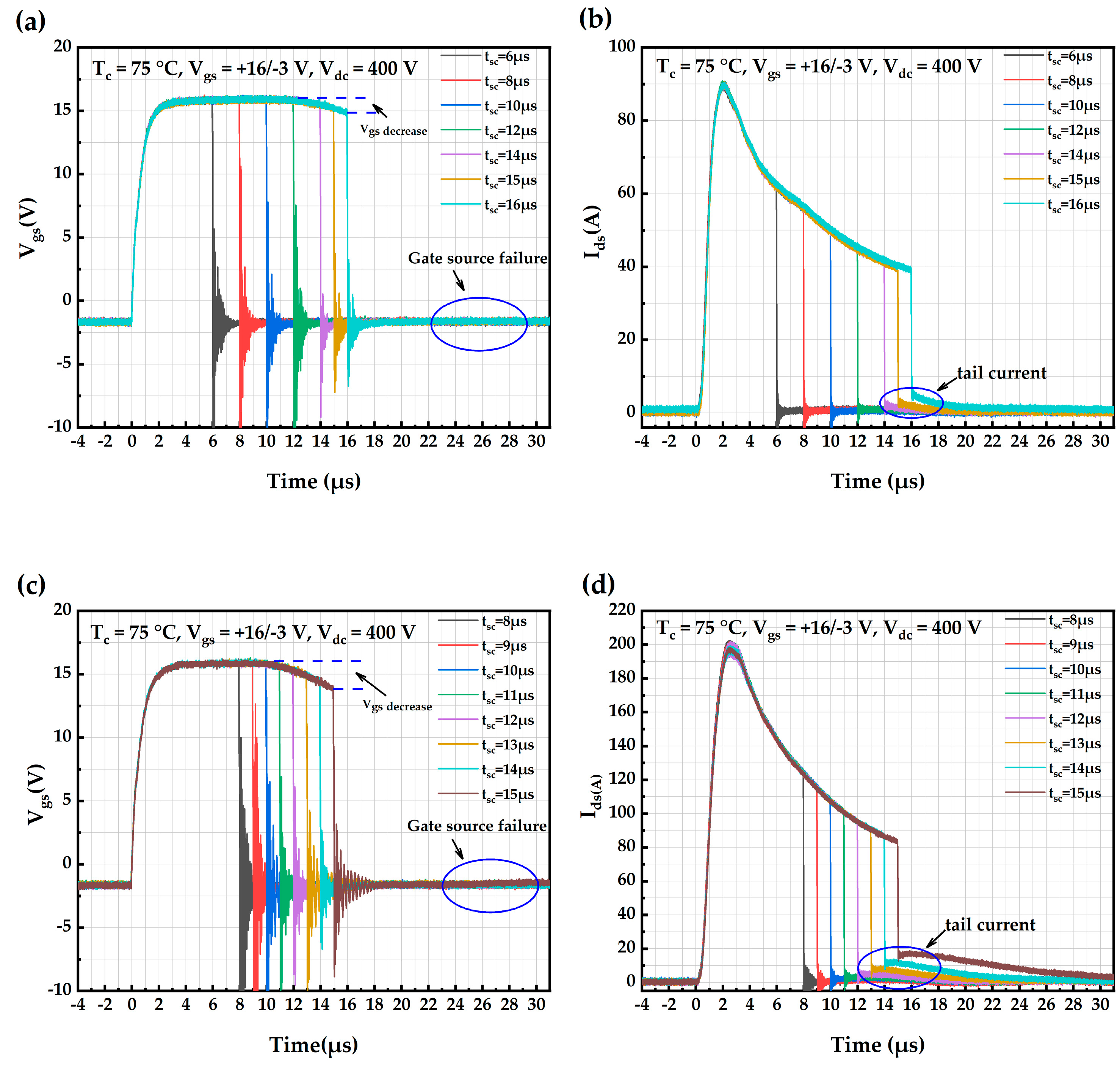

3.1.2. Effect of Temperature

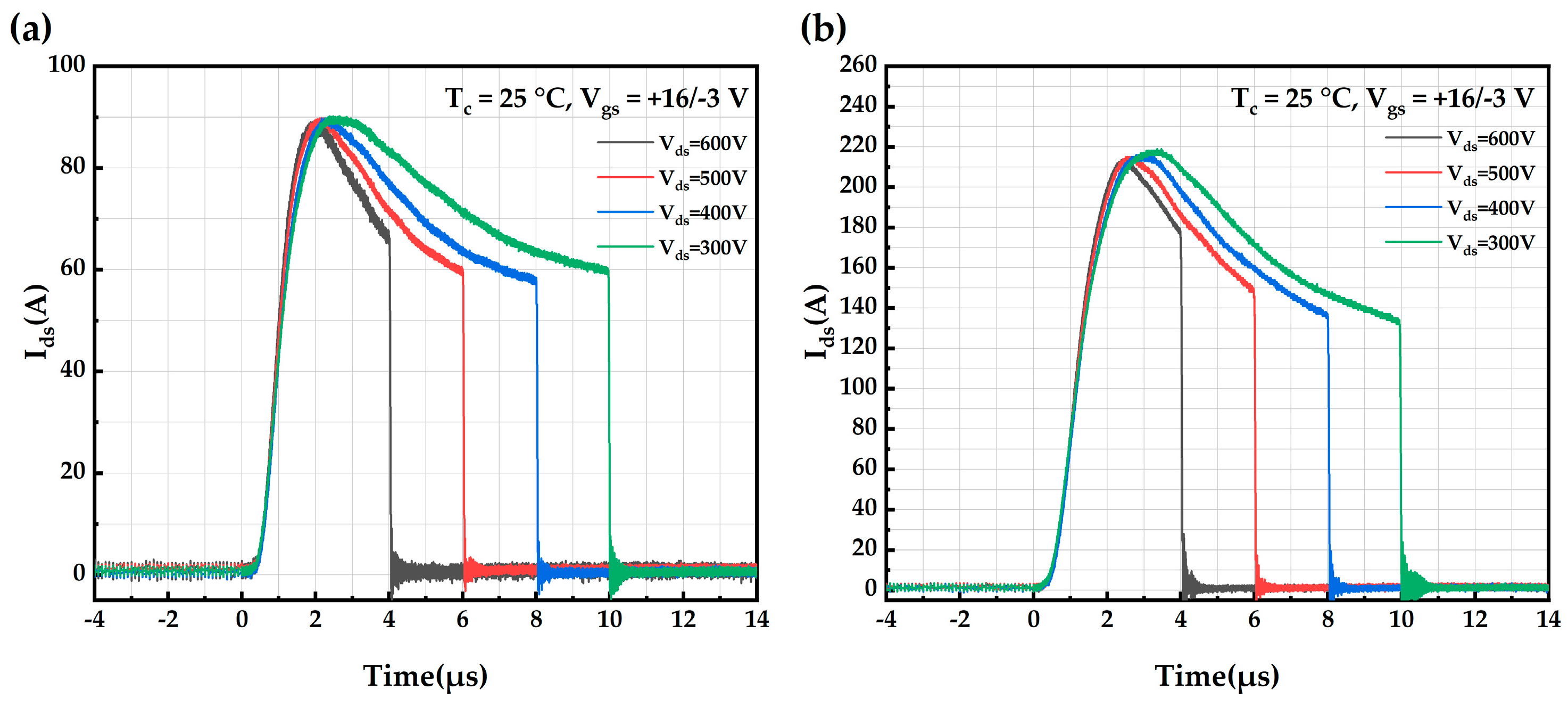

3.1.3. Effect of Drain-Source Voltage

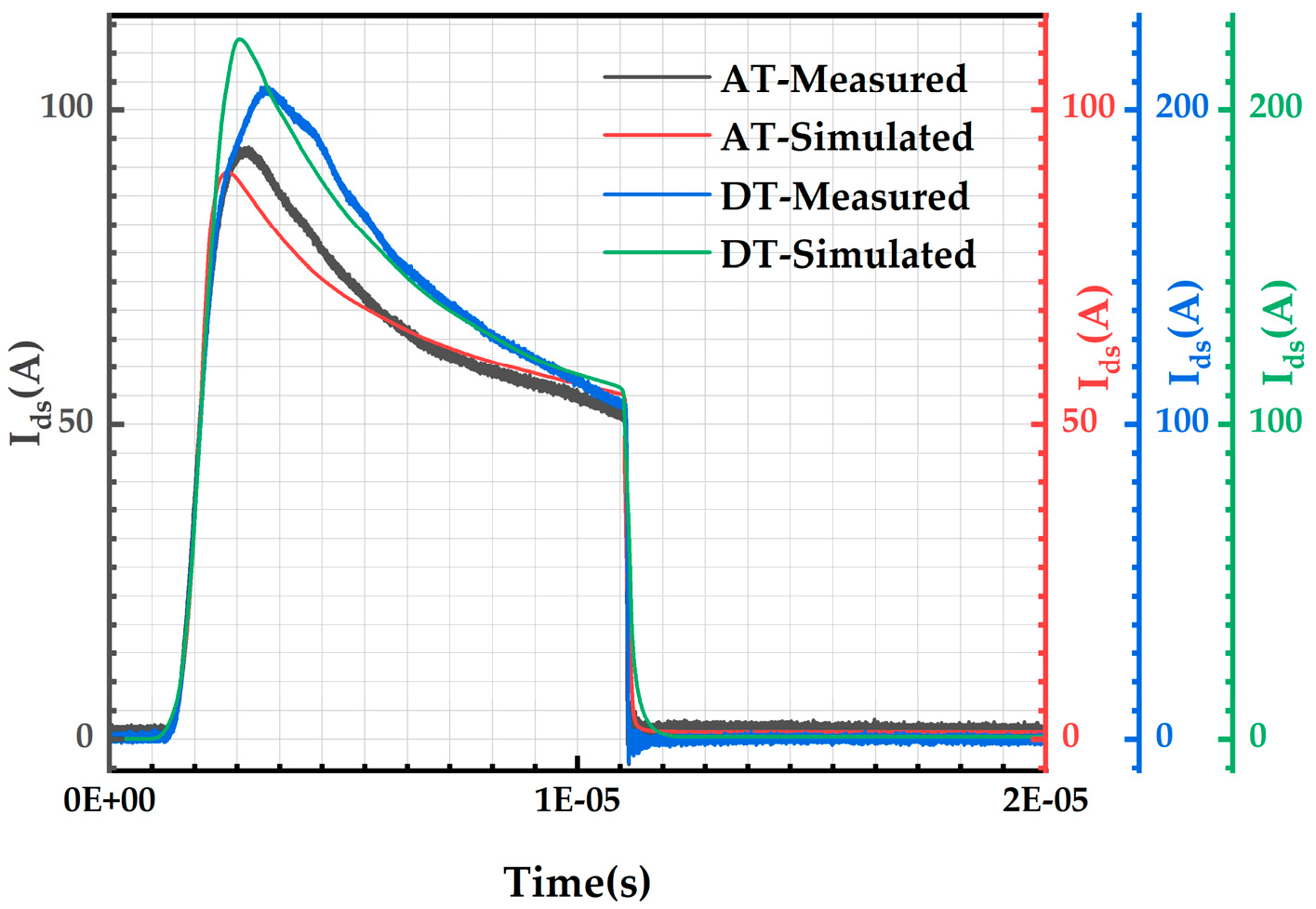

3.2. TCAD Simulation Under Single Short-Circuit Testing

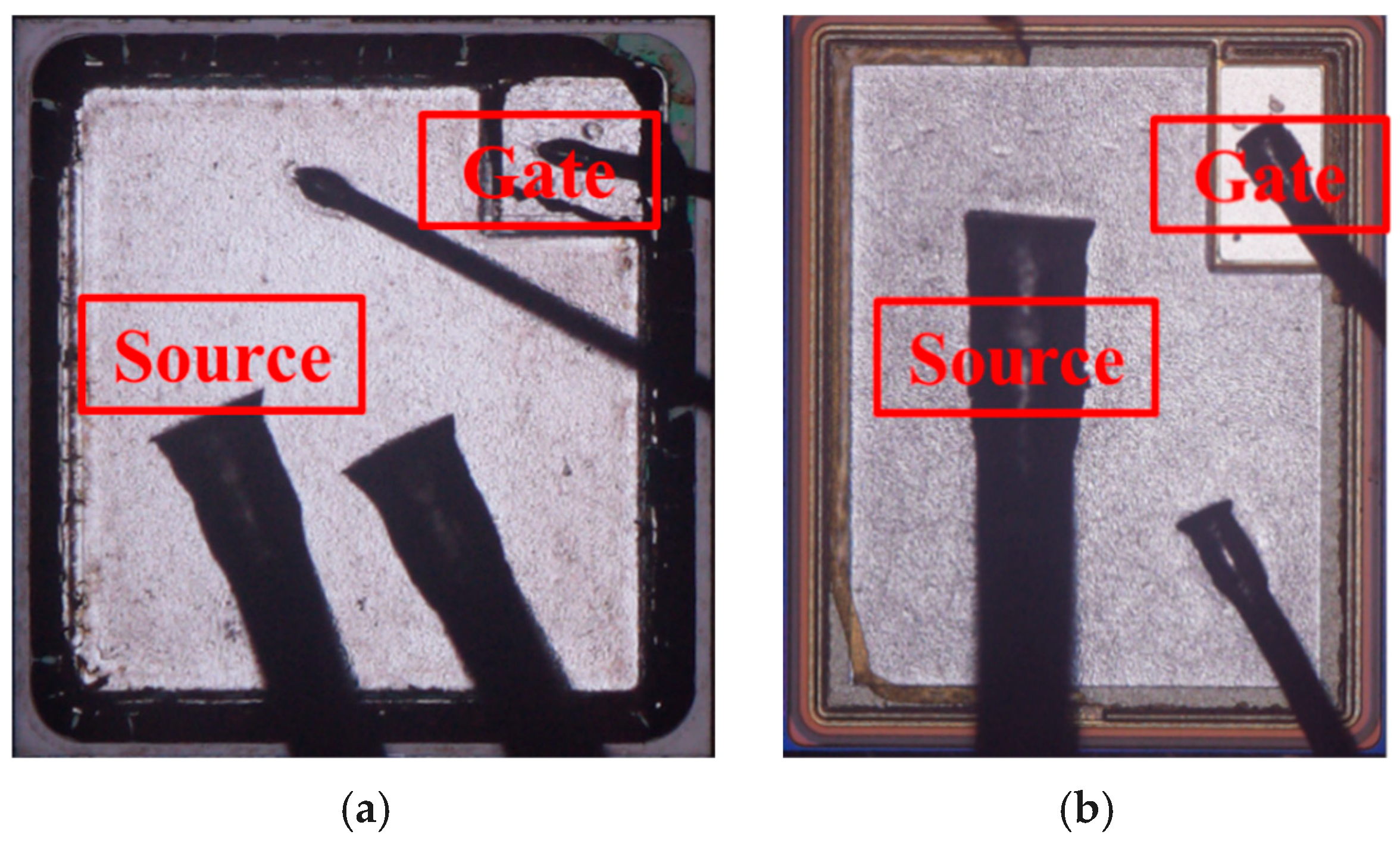

3.3. Failure Analysis Under Single Short-Circuit Testing

4. Repetitive Short-Circuit Testing of Trench Power SiC MOSFETs

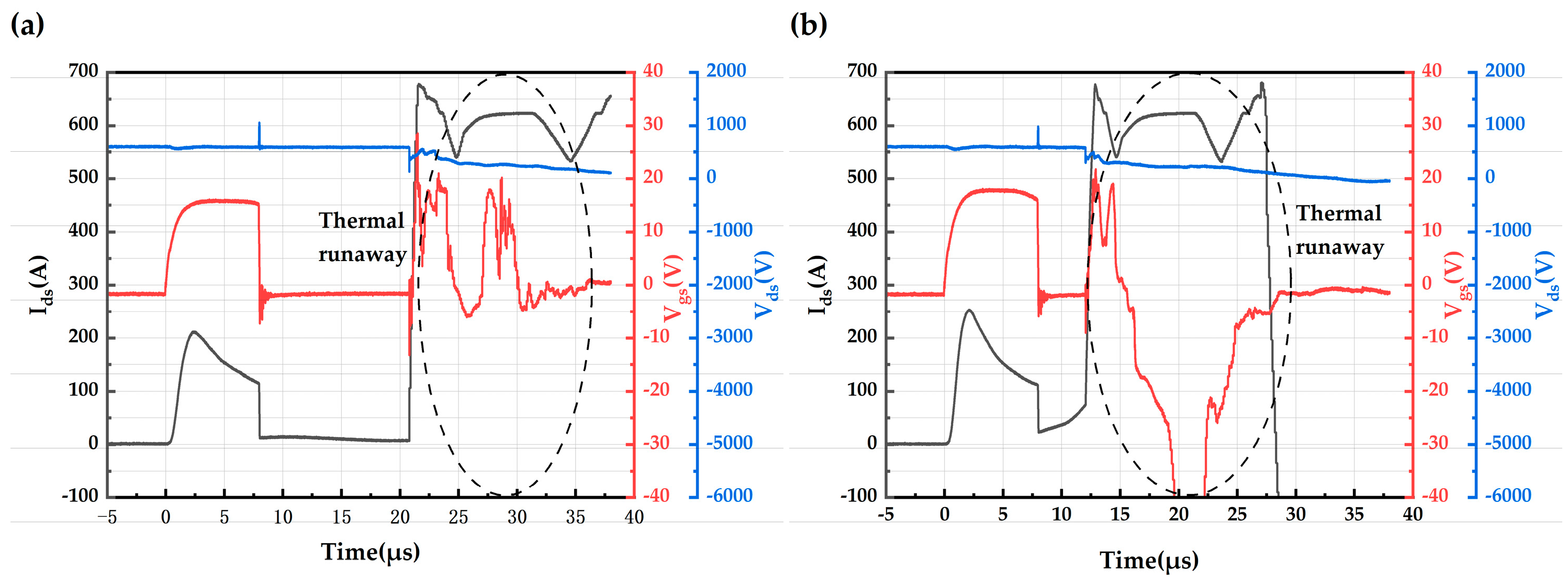

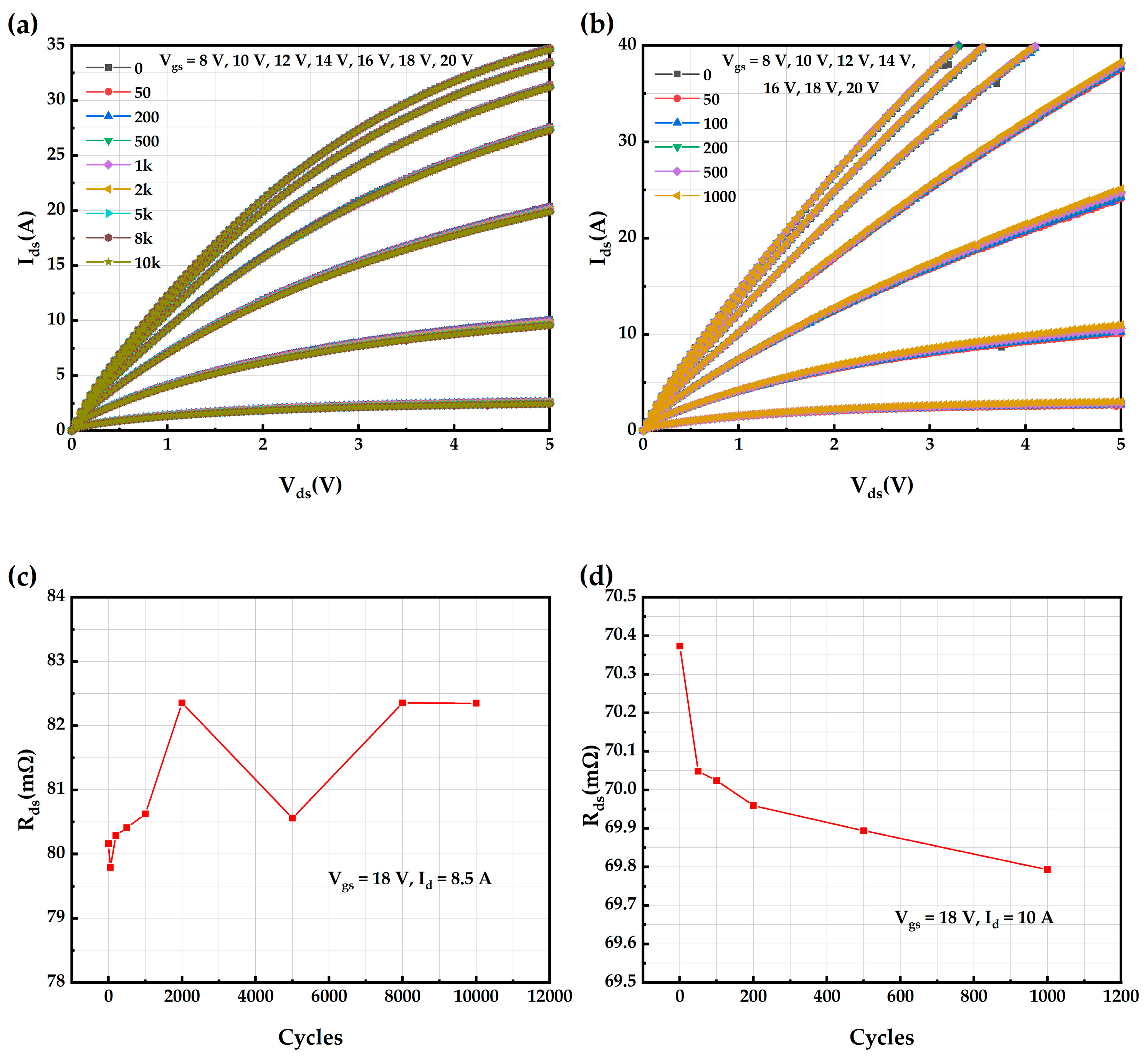

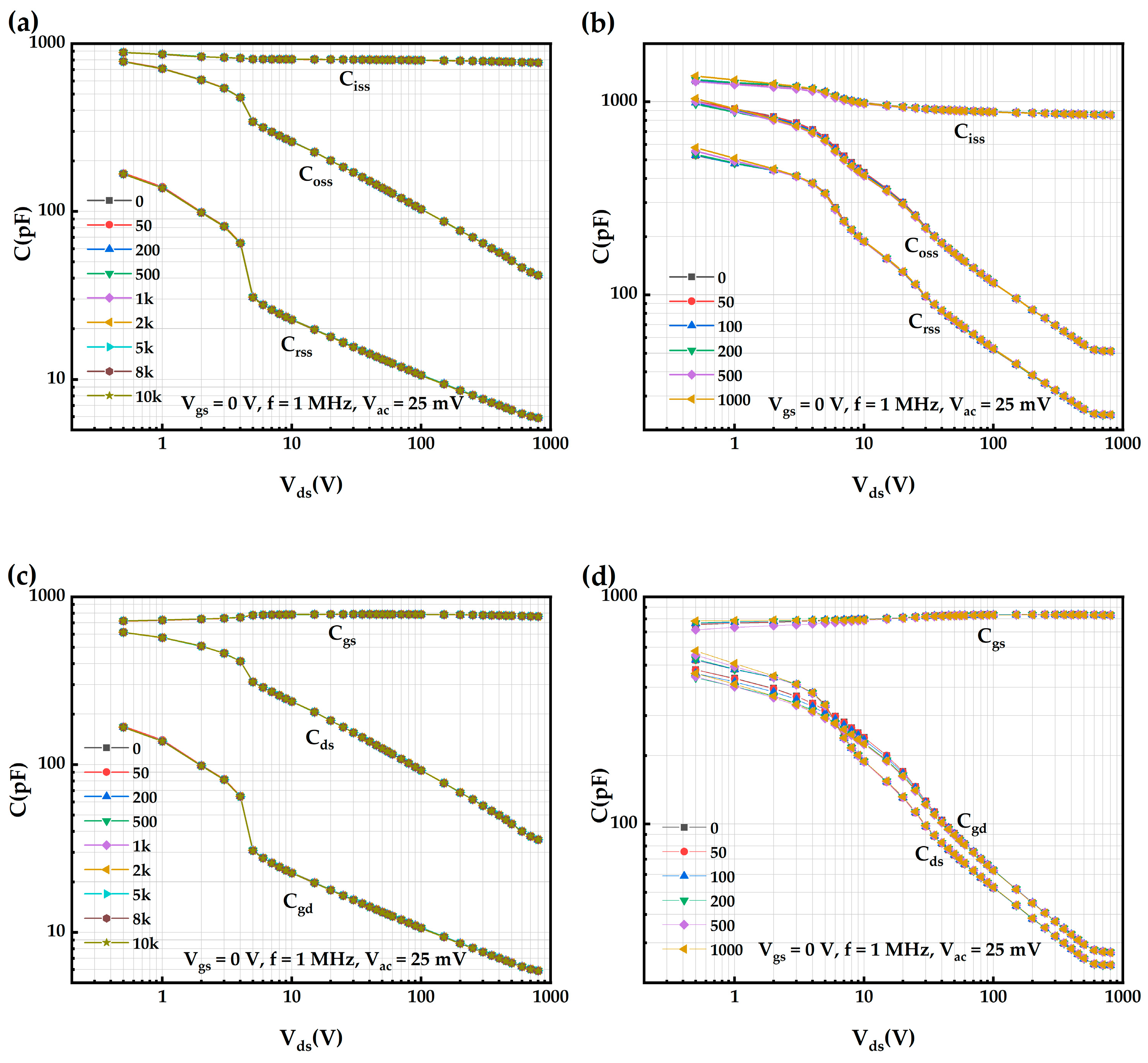

4.1. Repetitive Short-Circuit Test

4.2. Failure Analysis Under Repetitive Short-Circuit Stresses

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhou, W.; Zhong, X.; Sheng, K. High temperature stability and the performance degradation of SiC MOSFETs. IEEE Trans. Power Electron. 2013, 29, 2329–2337. [Google Scholar] [CrossRef]

- Yuan, X.; Laird, I.; Walder, S. Opportunities, challenges, and potential solutions in the application of fast-switching SiC power devices and converters. IEEE Trans. Power Electron. 2020, 36, 3925–3945. [Google Scholar] [CrossRef]

- Xu, S.; Huang, A.Q.; Lucía, Ó.; Ozpineci, B. Review of silicon carbide power devices and their applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar]

- Zhang, L.; Yuan, X.B.; Wu, X.J.; Shi, C.C.; Zhang, J.H.; Zhang, Y.L. Performance evaluation of high-power SiC MOSFET modules in comparison to Si IGBT modules. IEEE Trans. Power Electron. 2018, 34, 1181–1196. [Google Scholar] [CrossRef]

- Hamada, K.; Nagao, M.; Ajioka, M.; Kawai, F. SiC-Emerging power device technology for next-generation electrically powered environmentally friendly vehicles. IEEE Trans. Electron Devices 2014, 62, 278–285. [Google Scholar] [CrossRef]

- Harada, S.; Kobayashi, Y.; Ariyoshi, K.; Kojima, T.; Senzaki, J.; Tanaka, Y.; Okumura, H. 3.3-kV-class 4H-SiC MeV-implanted UMOSFET with reduced gate oxide field. IEEE Electron Device Lett. 2016, 37, 314–316. [Google Scholar] [CrossRef]

- Wang, J.; Jiang, X.; Li, Z.J.; Shen, Z.J. Short-circuit ruggedness and failure mechanisms of Si/SiC hybrid switch. IEEE Trans. Power Electron. 2018, 34, 2771–2780. [Google Scholar] [CrossRef]

- Wang, Z.Q.; Shi, X.J.; Tolbert, L.M.; Wang, F.; Liang, Z.X.; Costinett, D.; Blalock, B.J. Temperature-dependent short-circuit capability of silicon carbide power MOSFETs. IEEE Trans. Power Electron. 2015, 31, 1555–1566. [Google Scholar] [CrossRef]

- Ziemann, T.; Tsibizov, A.; Kakarla, B.; Bort, L.; Grossner, U. Time-Resolved Short Circuit Failure Analysis of SiC MOSFETs. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 219–222. [Google Scholar]

- Wei, J.X.; Liu, S.Y.; Tong, J.H.; Zhang, X.B.; Sun, W.F.; Huang, A.Q. Understanding short-circuit failure mechanism of double-trench SiC power MOSFETs. IEEE Trans. Electron Devices 2020, 67, 5593–5599. [Google Scholar] [CrossRef]

- Deng, X.C.; Li, X.; Li, X.; Zhu, H.; Xu, X.J.; Wen, Y.; Sun, Y.K.; Chen, W.J.; Li, Z.Q.; Zhang, B. Short-circuit capability prediction and failure mode of asymmetric and double trench SiC MOSFETs. IEEE Trans. Power Electron. 2021, 36, 8300–8307. [Google Scholar] [CrossRef]

- Wei, J.X.; Liu, S.Y.; Yang, L.L.; Fang, J.; Li, T.; Li, S.; Sun, W.F. Comprehensive analysis of electrical parameters degradations for SiC power MOSFETs under repetitive short-circuit stress. IEEE Trans. Electron Devices 2018, 65, 5440–5447. [Google Scholar] [CrossRef]

- Jia, X.Q.; Kang, J.; Meng, H.; Xin, Z. Investigations on the Degradation of Different Gate Oxide Regions of SiC MOSFET Under Different Repetitive DC Bus Voltage. In Proceedings of the 2022 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Guangzhou, China, 4–7 November 2022; pp. 909–913. [Google Scholar]

- Yu, R.Z.; Jahdi, S.; Mellor, P.; Liu, L.; Yang, J.F.; Shen, C.J.; Alatise, O.; Ortiz-Gonzalez, J. Degradation analysis of planar, symmetrical and asymmetrical trench SiC MOSFETs under repetitive short circuit impulses. IEEE Trans. Power Electron. 2023, 38, 10933–10946. [Google Scholar] [CrossRef]

- Wei, J.X.; Liu, S.Y.; Yang, L.L.; Tang, L.Z.; Lou, R.C.; Li, T.; Fang, J.F.; Li, S.; Zhang, C.; Sun, W.F. Investigations on the degradations of double-trench SiC power MOSFETs under repetitive avalanche stress. IEEE Trans. Electron Devices 2018, 66, 546–552. [Google Scholar] [CrossRef]

- Peters, D.; Siemieniec, R.; Aichinger, T.; Basler, T.; Esteve, R.; Bergner, W.; Kuech, D. Performance and ruggedness of 1200V SiC-Trench-MOSFET. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 239–242. [Google Scholar]

- Xing, D.; Hu, B.X.; Kang, M.; Zhang, Y.; Nayak, S.; Wang, J.; Agarwal, A.K. 1200-V sic mosfet short-circuit ruggedness evaluation and methods to improve withstand time. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5059–5068. [Google Scholar] [CrossRef]

- Du, H.; Reigosa, P.D.; Ceccarelli, L.; Iannuzzo, F. Impact of Repetitive Short-Circuit Tests on the Normal Operation of SiC MOSFETs Considering Case Temperature Influence. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 195–205. [Google Scholar] [CrossRef]

- Liu, J.C.; Zhang, G.G.; Wang, B.X.; Li, W.P.; Wang, J.H. Gate failure physics of SiC MOSFETs under short-circuit stress. IEEE Electron Device Lett. 2019, 41, 103–106. [Google Scholar] [CrossRef]

- Yao, K.; Yano, H.; Tadano, H.; Iwamuro, N. Investigations of SiC MOSFET short-circuit failure mechanisms using electrical, thermal, and mechanical stress analyses. IEEE Trans. Electron Devices 2020, 67, 4328–4334. [Google Scholar] [CrossRef]

- Snead, L.L.; Nozawa, T.; Katoh, Y.; Byun, T.S.; Kondo, S.; Petti, D.A. Handbook of SiC properties for fuel performance modeling. J. Nucl. Mater. 2007, 371, 329–377. [Google Scholar] [CrossRef]

- Sadik, D.P.; Colmenares, J.; Lim, J.K.; Bakowski, M.; Nee, H.P. Comparison of Thermal Stress During Short-Circuit in Different Types of 1.2-kV SiC Transistors Based on Experiments and Simulations. IEEE Trans. Ind. Electron. 2020, 68, 2608–2616. [Google Scholar] [CrossRef]

- Boige, F.; Trémouilles, D.; Richardeau, F. Physical origin of the gate current surge during short-circuit operation of SiC MOSFET. IEEE Electron Device Lett. 2019, 40, 666–669. [Google Scholar] [CrossRef]

- Namai, M.; An, J.J.; Yano, H.; Iwamuro, N. Investigation of short-circuit failure mechanisms of SiC MOSFETs by varying DC bus voltage. Jpn. J. Appl. Phys. 2018, 57, 074102. [Google Scholar] [CrossRef]

- Jouha, W.; Richardeau, F.; Azzopardi, S. Towards a safe failure mode under short-circuit operation of power SiC MOSFET using optimal gate source voltage depolarization. Microelectron. Reliab. 2021, 126, 114258. [Google Scholar] [CrossRef]

- Yao, K.; Yano, H.; Iwamuro, N. Investigations of short-circuit failure in double trench SiC MOSFETs through three-dimensional electro-thermal-mechanical stress analysis. Microelectron. Reliab. 2021, 122, 114163. [Google Scholar] [CrossRef]

- Romano, G.; Fayyaz, A.; Riccio, M.; Maresca, L.; Breglio, G.; Castellazzi, A.; Irace, A. A comprehensive study of short-circuit ruggedness of silicon carbide power MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 978–987. [Google Scholar] [CrossRef]

- Sun, J.; Wei, J.X.; Zheng, Z.; Wang, Y.; Chen, K.J. Short circuit capability and short circuit induced VTH instability of a 1.2 kV SiC power MOSFET. IEEE J. Emerg. Sel. Topics Power Electron. 2019, 7, 1539–1546. [Google Scholar] [CrossRef]

- Li, Y.; Zhou, X.T.; Zhao, Y.F.; Jia, Y.P.; Hu, D.Q.; Wu, Y.; Zhang, L.Q.; Chen, Z.B.; Huang, A.Q. Gate bias dependence of VTH degradation in planar and trench SiC MOSFETs under repetitive short circuit tests. IEEE Trans. Electron Devices 2022, 69, 2521–2527. [Google Scholar] [CrossRef]

- Wang, J.L.; Chen, Y.Q.; Feng, J.T.; Xu, X.B.; En, Y.F.; Hou, B.; Gao, R.; Chen, Y.; Huang, Y.; Geng, K.W. Trap analysis based on low-frequency noise for SiC power MOSFETs under repetitive short-circuit stress. IEEE J. Electron Devices Soc. 2020, 8, 145–151. [Google Scholar] [CrossRef]

- Zhou, X.; Su, H.; Wang, Y.; Yue, R.; Dai, G.; Li, J. Investigations on the degradation of 1.2-kV 4H-SiC MOSFETs under repetitive short-circuit tests. IEEE Trans. Electron Devices 2016, 63, 4346–4351. [Google Scholar] [CrossRef]

- Kang, J.; Liu, Q.; Luo, H.; Cao, H.; Zhang, Z.H.; Xin, Z. Investigation of off-state stress induced degradation of sic mosfets under short-circuit condition. IEEE Trans. Ind. Electron. 2022, 70, 5224–5234. [Google Scholar] [CrossRef]

- Ugur, E.; Yang, F.; Pu, S.; Zhao, S.; Akin, B. Degradation assessment and precursor identification for SiC MOSFETs under high temp cycling. IEEE Trans. Ind. Appl. 2019, 55, 2858–2867. [Google Scholar] [CrossRef]

- Mbarek, S.; Dherb’ecourt, P.; Latry, O.; Fouquet, F. Short-circuit robustness test and in depth microstructural analysis study of SiC MOSFET. Microelectron. Reliab. 2017, 76, 527–531. [Google Scholar] [CrossRef]

- Yu, R.Z.; Jahdi, S.; Alatise, O.; Gonzalez, O.J.; Munagala, S.P.; Simpson, N.; Mellor, P. Measurements and Review of Failure Mechanisms and Reliability Constraints of 4H-SiC Power MOSFETs Under Short Circuit Events. IEEE Trans. Device Mater. Reliab. 2023, 23, 544–563. [Google Scholar] [CrossRef]

- Yu, R.Z.; Jahdi, S.; Yang, J.F.; Mellor, P.; Gonzalez, J.O.; Alatise, O. Degradation Pattern of Parallel Symmetrical and Asymmetrical Double-Trench SiC MOSFETs under Repetitive Short Circuits. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 9–11 May 2023; pp. 1–6. [Google Scholar]

| IMW120R090M1H | SCT3080KR | |

|---|---|---|

| Vth (V) | 4.20~4.35 | 3.85~4.05 |

| Rds,on (mΩ) | 79~83 | 70~72 |

| Vsd (V) | 3.89~3.93 | 3.12~3.19 |

| Igss (nA) | 0.20~0.40 | 0.15~0.60 |

| Ciss (nF) | 0.7691~0.7823 | 0.8260~0.8425 |

| Coss (nF) | 0.0415~0.0417 | 0.0511~0.0512 |

| Crss (nF) | 0.0059~0.0061 | 0.0237~0.0240 |

| Component | AT-MOSFET | DT-MOSFET | ||||

|---|---|---|---|---|---|---|

| Vgs (V) | 15 | 16 | 18 | 15 | 16 | 18 |

| Short-circuit time (μs) | 21 | 20 | 18 | 17 | 16 | 15 |

| Ig decrease (A) | 1.29 | 0.92 | 1.39 | 1.4 | 1.8 | 2.8 |

| Ipeak (A) | 88.9 | 94.5 | 102.7 | 174 | 204 | 250 |

| Itrail (A) | 7.9 | 7.9 | 9.3 | 14 | 16 | 14.97 |

| Rgs (Ω) | 1.1 | 1.8 | 2.8 | 1.5 | 1.9 | 3.2 |

| Short-circuit critical energy (J) | 0.4306 | 0.4327 | 0.3974 | 0.7984 | 0.7884 | 0.7972 |

| Component | AT-MOSFET | DT-MOSFET | ||||

|---|---|---|---|---|---|---|

| Temperature (°C) | 25 | 75 | 125 | 25 | 75 | 125 |

| Short-circuit time (μs) | 20 | 16 | 15 | 16 | 15 | 14 |

| Ig decrease (A) | 0.92 | 1.19 | 1 | 1.8 | 2.1 | 1.9 |

| Ipeak (A) | 94.5 | 89.3 | 85.5 | 204 | 197.6 | 190.8 |

| Itrail (A) | 7.9 | 5.2 | 4.2 | 16 | 15.9 | 13.3 |

| Rgs (Ω) | 1.8 | 0.7 | 0.4 | 1.9 | 2.1 | 1.0 |

| Short-circuit critical energy (J) | 0.4327 | 0.3548 | 0.3253 | 0.7884 | 0.7454 | 0.6765 |

| Before Failure Waveform | Failure Waveform | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| Component | Vgs (V) | Time (μs) | Vg decrease (V) | Ids increases (A) | Itrail (A) | Vg decrease (V) | Itrail (A) | SCWTmax (μs) | Tgate failure (μs) |

| AT-MOSFET | 15 | 11 | 0.6 | 78.9 | 6.59 | 1.2 | 12.35 | 12 | 3.9 |

| 16 | 10 | 1 | 87.9 | 9.18 | 2 | 17.8 | 11 | 9.85 | |

| 18 | 8 | 0.8 | 105.1 | 7.18 | 2.7 | 15.4 | 9 | 2.1 | |

| DT-MOSFET | 15 | 8 | 0.3 | 184 | 7.29 | 0.7 | 14.1 | 9 | 12.2 |

| 16 | 7 | 0.4 | 213 | 7.06 | 0.8 | 12.7 | 8 | 12.8 | |

| 18 | 7 | 0.7 | 252 | 7.76 | 2 | 22.6 | 8 | 4 | |

| Component | AT-MOSFET | DT-MOSFET |

|---|---|---|

| Cell width (μm) | 3 | 3.6 |

| Gate oxide thickness (nm) | 75 | 50 (sidewall), 100 (bottom) |

| Channel length (nm) | 500 | 500 |

| N-drift thicknesss (μm) | 11 | 10 |

| N+ Substrate thicknesss (μm) | 1 | 1 |

| Doping of N+ (cm−3) | 1 × 1020 | 1 × 1020 |

| Doping of Channel (cm−3) | 5 × 1017 | 8 × 1017 |

| Doping of P-well (cm−3) | 5 × 1018 | - |

| Doping of N-drift (cm−3) | 1 × 1016 | 7.5 × 1015 |

| Doping of N+ Substrate (cm−3) | 1 × 1020 | 1 × 1020 |

| Component | Factor | - | Etrench-gate oxide (MV/cm) | αcorners (cm−3s−1) | Tlattice (K) |

|---|---|---|---|---|---|

| AT-MOSFET | Vgs(Vds 400 V) | 15 V | 1.49 | 1.86 × 1015 | 691 |

| 16 V | 1.58 | 5.61 × 1014 | 747 | ||

| 18 V | 1.82 | 5.00 × 1013 | 837 | ||

| Temperature (Vds 400 V, Vgs 16 V) | 300 K | 1.584 | 5.61 × 1014 | 747 | |

| 350 K | 1.588 | 2.00 × 1014 | 813 | ||

| 400 K | 1.604 | 1.02 × 1014 | 862 | ||

| Vgs(Vds 600 V) | 15 V | 1.46 | 1.12 × 1017 | 912 | |

| 16 V | 1.56 | 3.26 × 1016 | 958 | ||

| 18 V | 1.80 | 2.26 × 1015 | 1029 | ||

| DT-MOSFET | Vgs(Vds 400 V) | 15 V | 2.07 | 3.29 × 1014 | 1080 |

| 16 V | 2.27 | 3.29 × 1011 | 1127 | ||

| 18 V | 2.72 | 2.20 × 105 | 1172 | ||

| Temperature (Vds 400 V, Vgs 16 V) | 300 K | 2.27 | 3.29 × 1011 | 1127 | |

| 350 K | 2.30 | 2.22 × 1011 | 1162 | ||

| 400 K | 2.32 | 8.76 × 1010 | 1182 | ||

| Vgs(Vds 600 V) | 15 V | 2.04 | 6.45 × 1018 | 1261 | |

| 16 V | 2.23 | 7.09 × 1016 | 1289 | ||

| 18 V | 2.65 | 4.14 × 1015 | 1309 |

| Component | AT-MOSFET | DT-MOSFET | ||||||

|---|---|---|---|---|---|---|---|---|

| Parameters | ΔVth | ΔRds | Cgs,Cds | Cgd | ΔVth | ΔRds | Cgs,Cds | Cgd |

| 5 μs | +0.11 V | +2.19 mΩ | ↑ * | ↓ * | −0.33 V | −0.58 mΩ | ↓ | ↑ |

| 10 μs | +0.12 V | +2.26 mΩ | ↑ | ↓ | −0.04 V | −0.66 mΩ | ↓ | ↑ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, L.; Pang, B.; Li, S.; Zhen, Y.; Li, G. Research on the Short-Circuit Characteristics of Trench-Type SiC Power MOSFETs Under Single and Repetitive Pulse Strikes. Micromachines 2025, 16, 768. https://doi.org/10.3390/mi16070768

Liu L, Pang B, Li S, Zhen Y, Li G. Research on the Short-Circuit Characteristics of Trench-Type SiC Power MOSFETs Under Single and Repetitive Pulse Strikes. Micromachines. 2025; 16(7):768. https://doi.org/10.3390/mi16070768

Chicago/Turabian StyleLiu, Li, Bo Pang, Siqiao Li, Yulu Zhen, and Gangpeng Li. 2025. "Research on the Short-Circuit Characteristics of Trench-Type SiC Power MOSFETs Under Single and Repetitive Pulse Strikes" Micromachines 16, no. 7: 768. https://doi.org/10.3390/mi16070768

APA StyleLiu, L., Pang, B., Li, S., Zhen, Y., & Li, G. (2025). Research on the Short-Circuit Characteristics of Trench-Type SiC Power MOSFETs Under Single and Repetitive Pulse Strikes. Micromachines, 16(7), 768. https://doi.org/10.3390/mi16070768