Temperature-Dependent Reverse-Recovery Behavior Analysis and Circuit-Level Mitigation of Superjunction MOSFETs

Abstract

1. Introduction

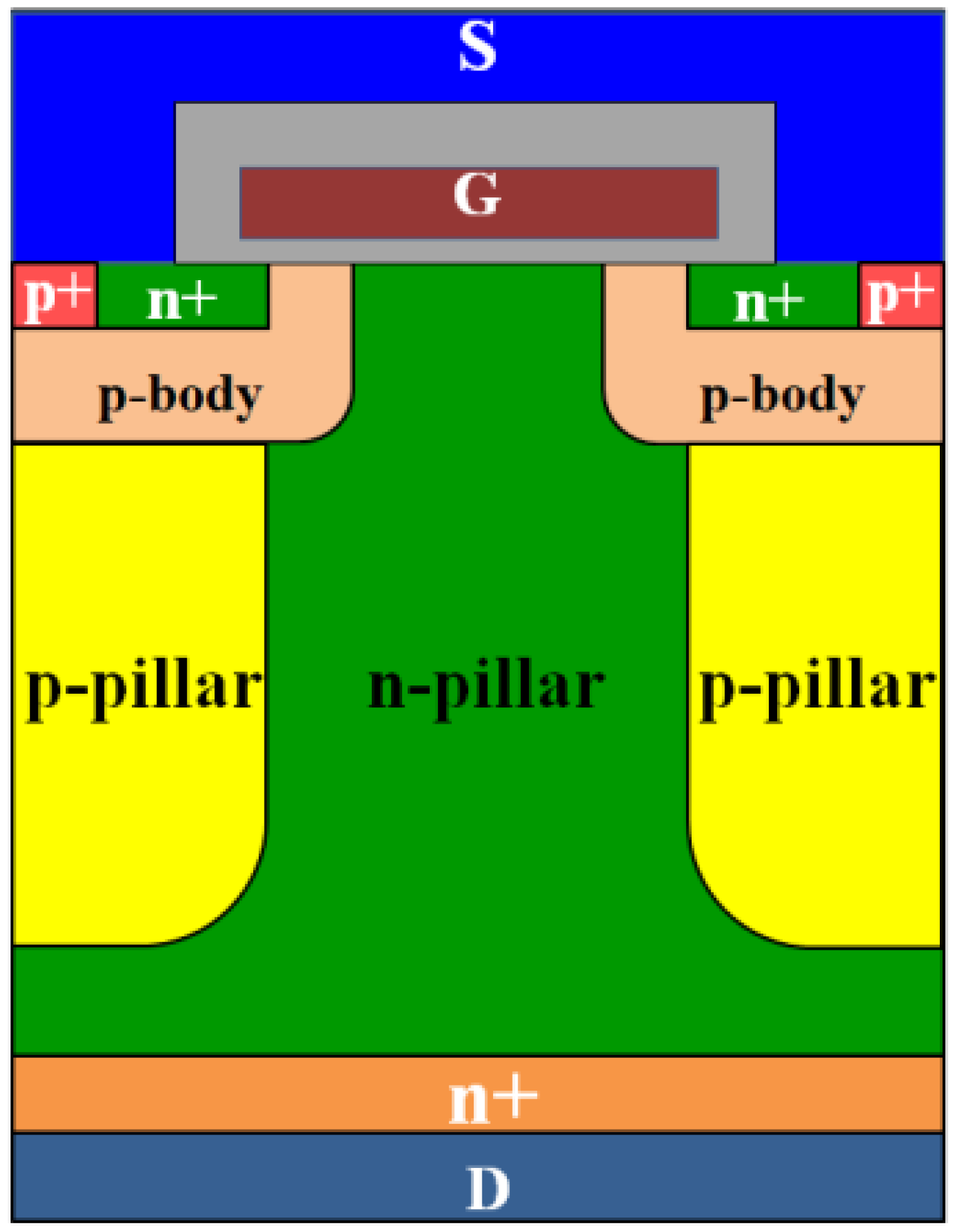

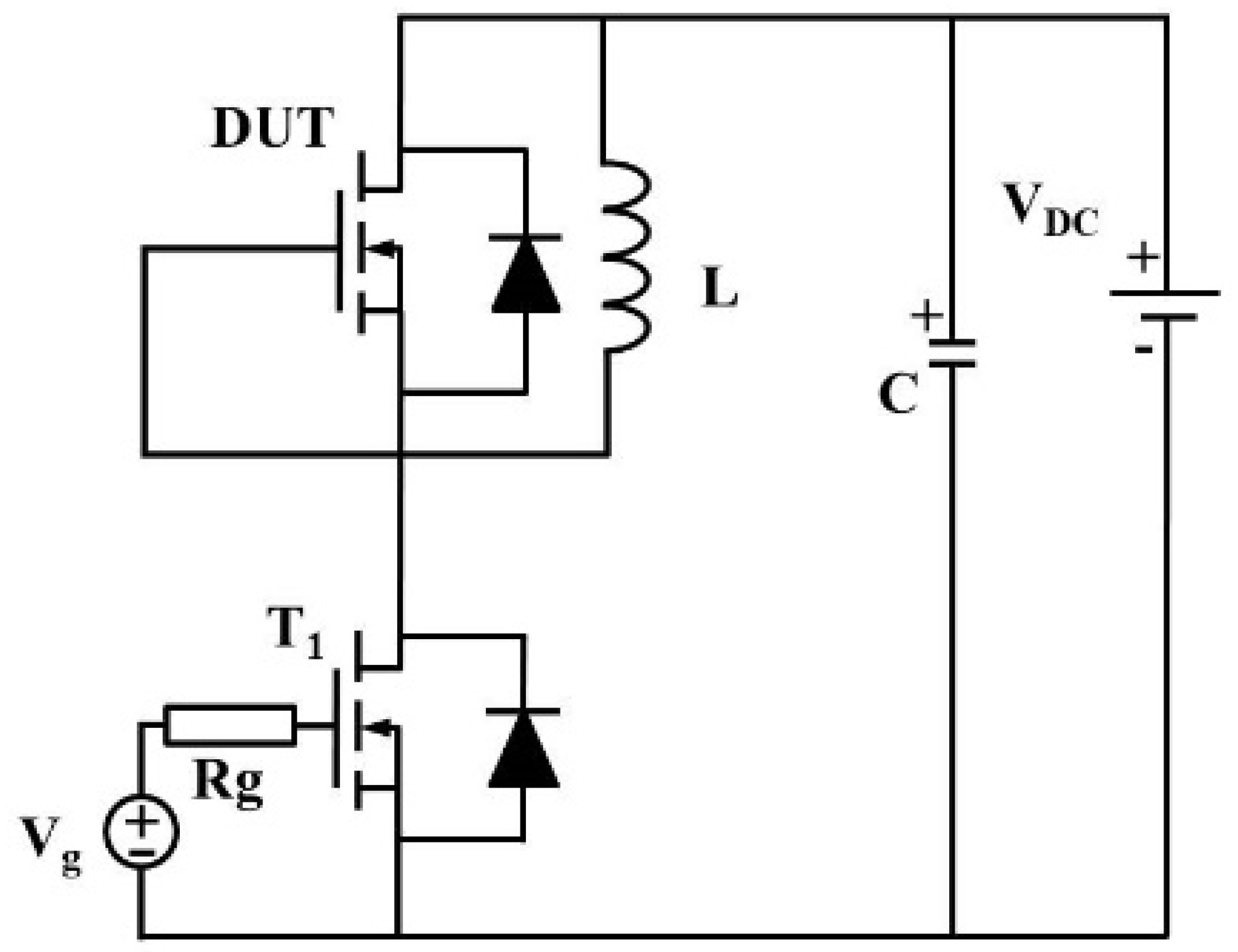

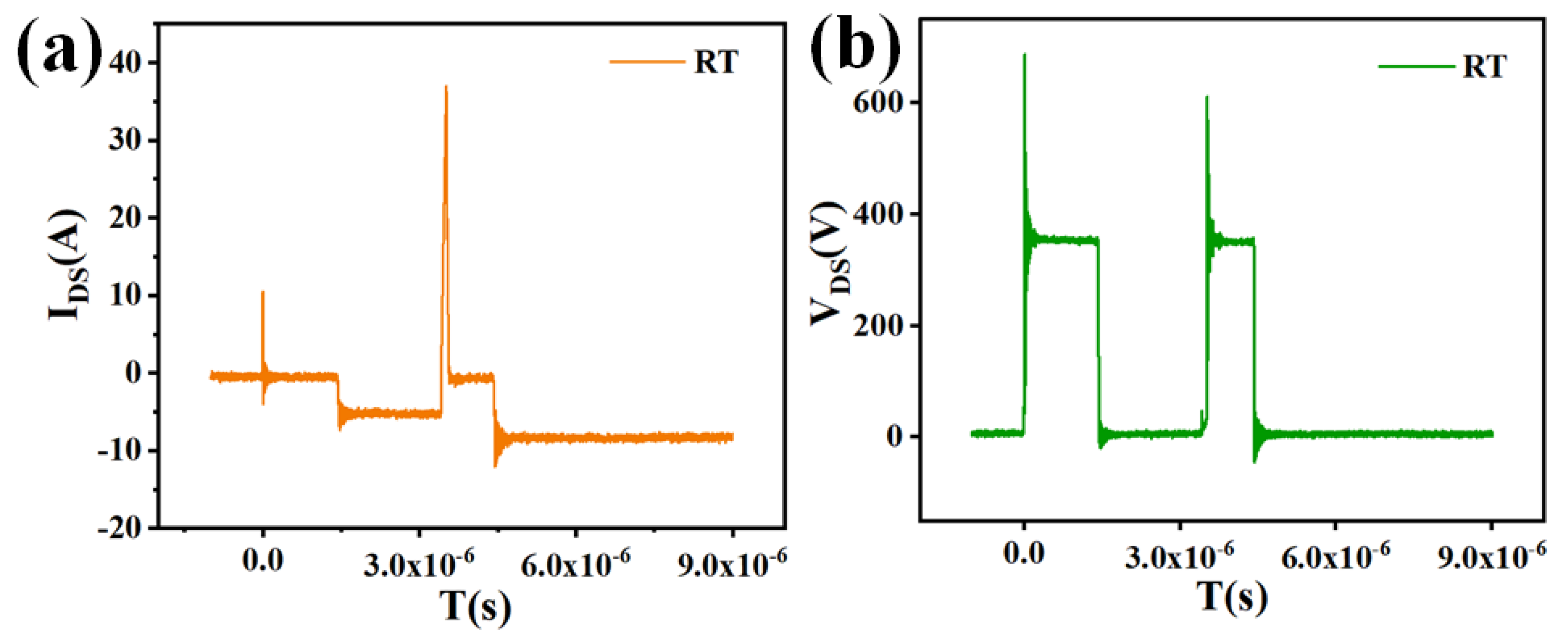

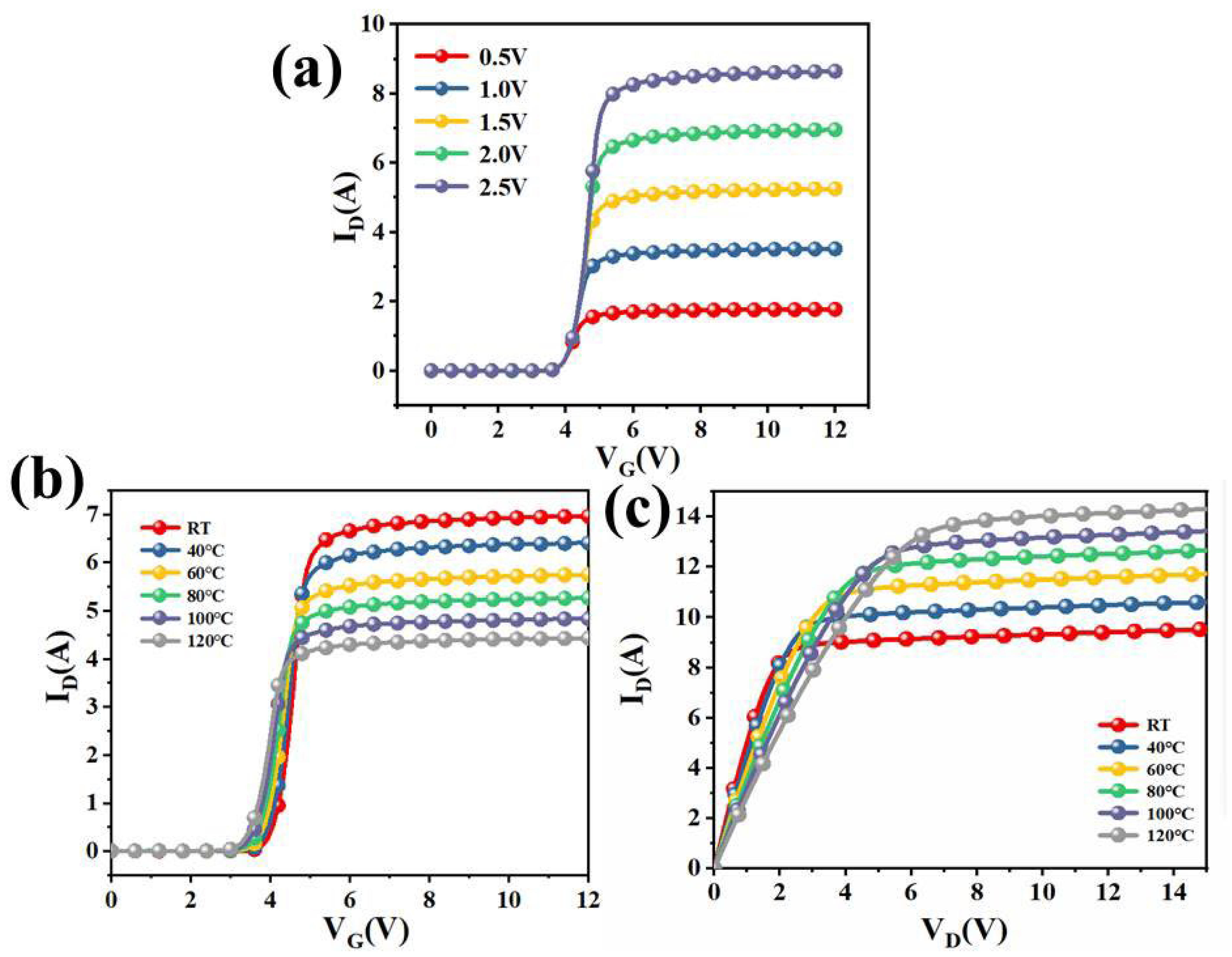

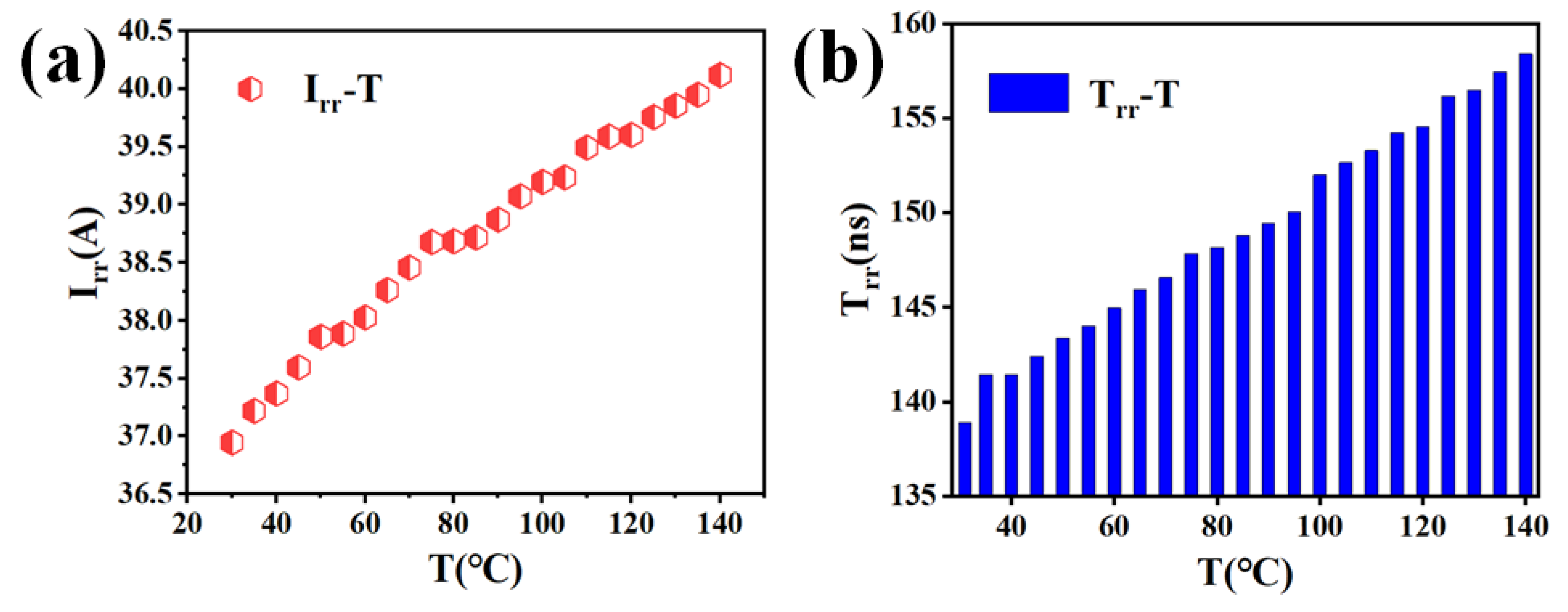

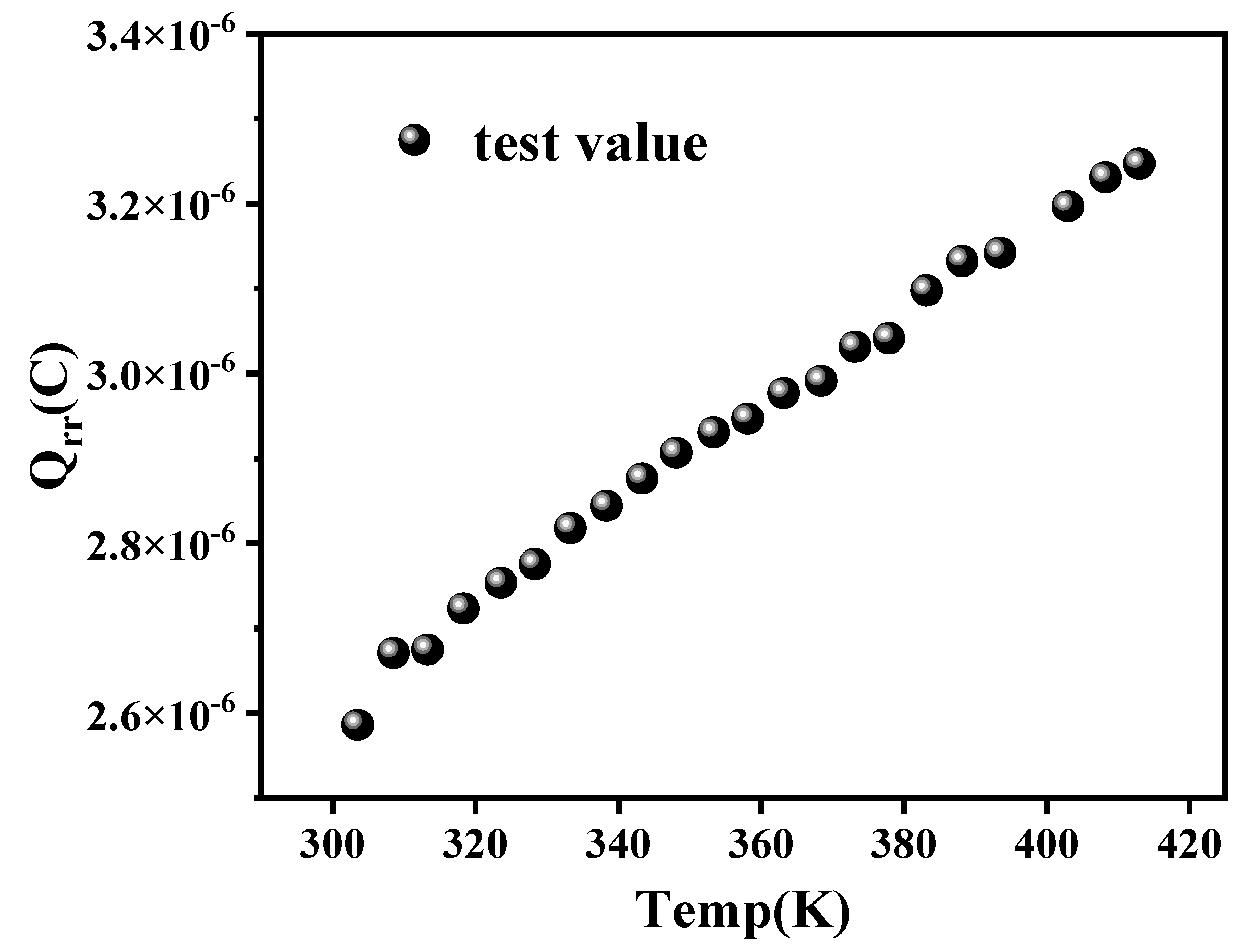

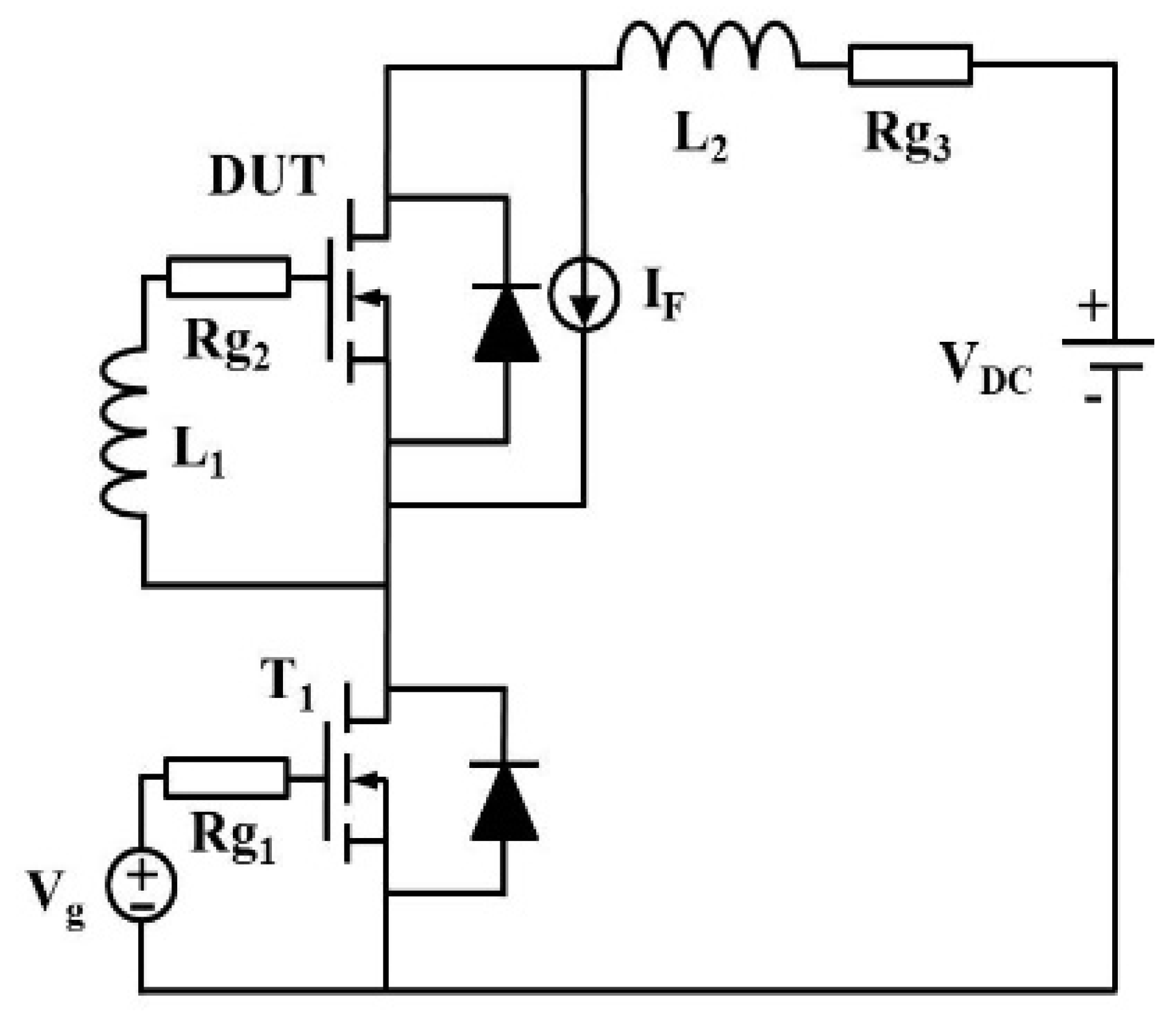

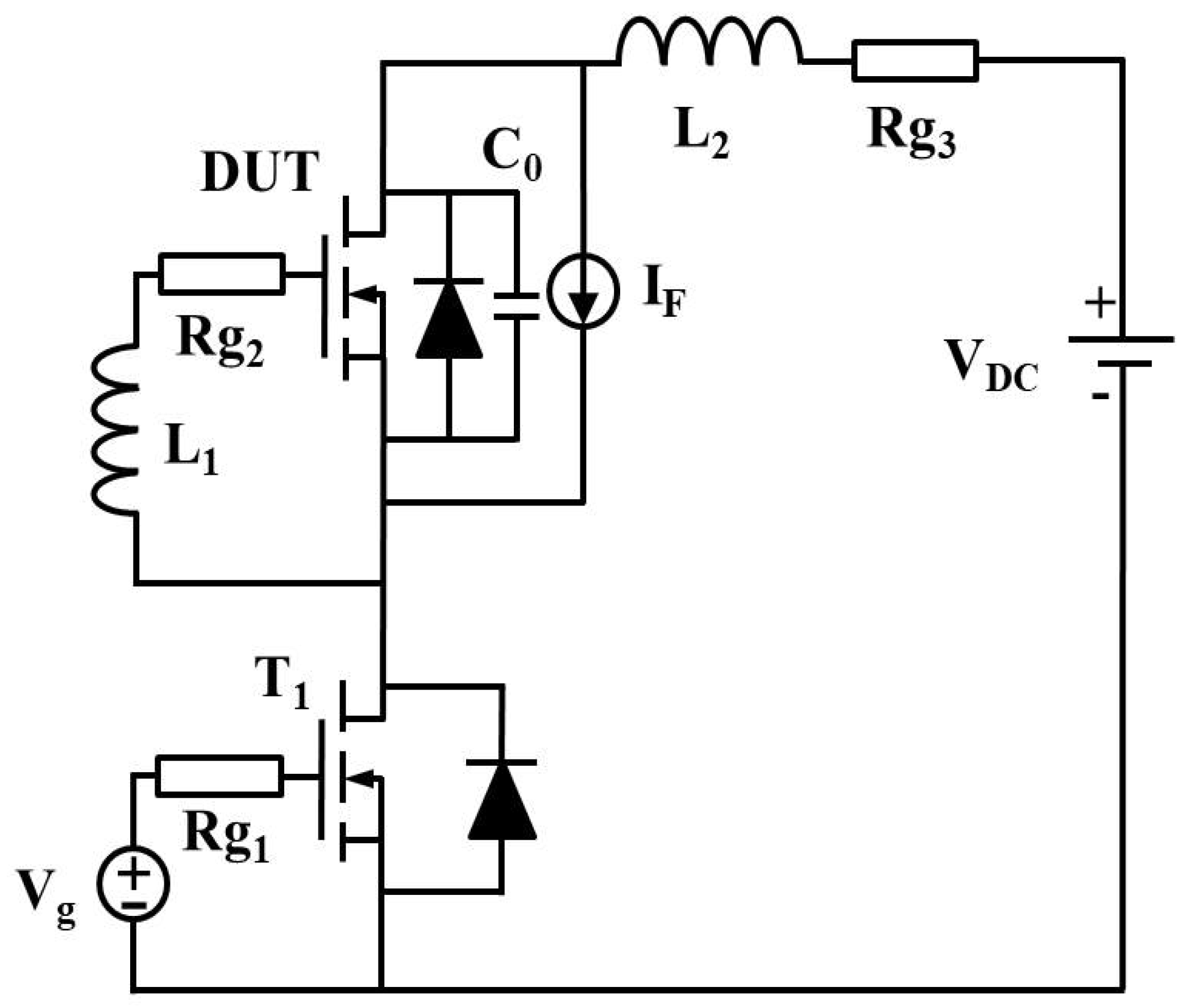

2. Experimental Measurements

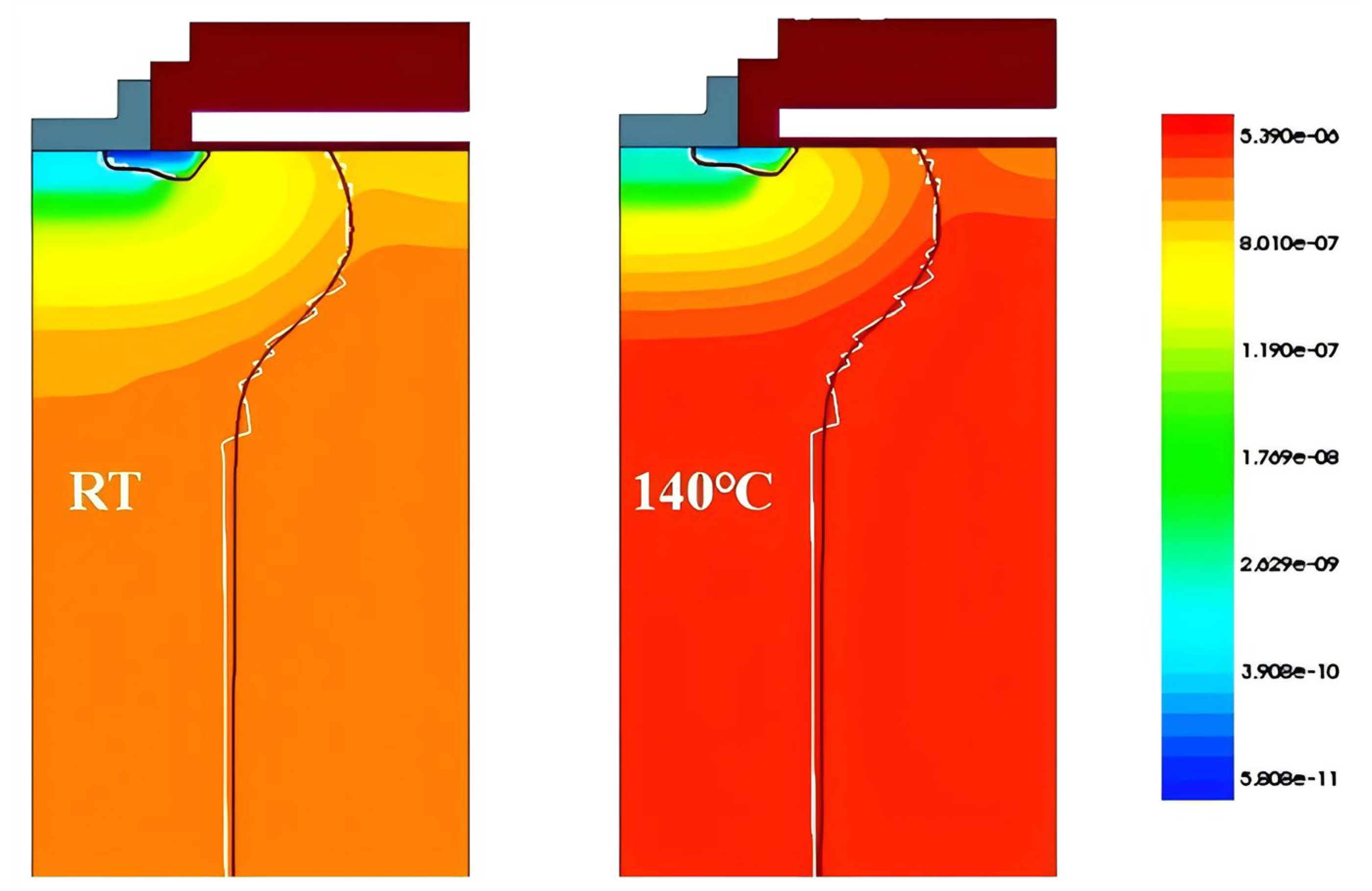

3. Simulation Results and Discussion

4. Conclusions

- When the junction temperature reaches 145 °C, device failure occurs during the switching process, indicating that high temperatures can severely compromise the safe operating range and switching reliability of superjunction MOSFETs.

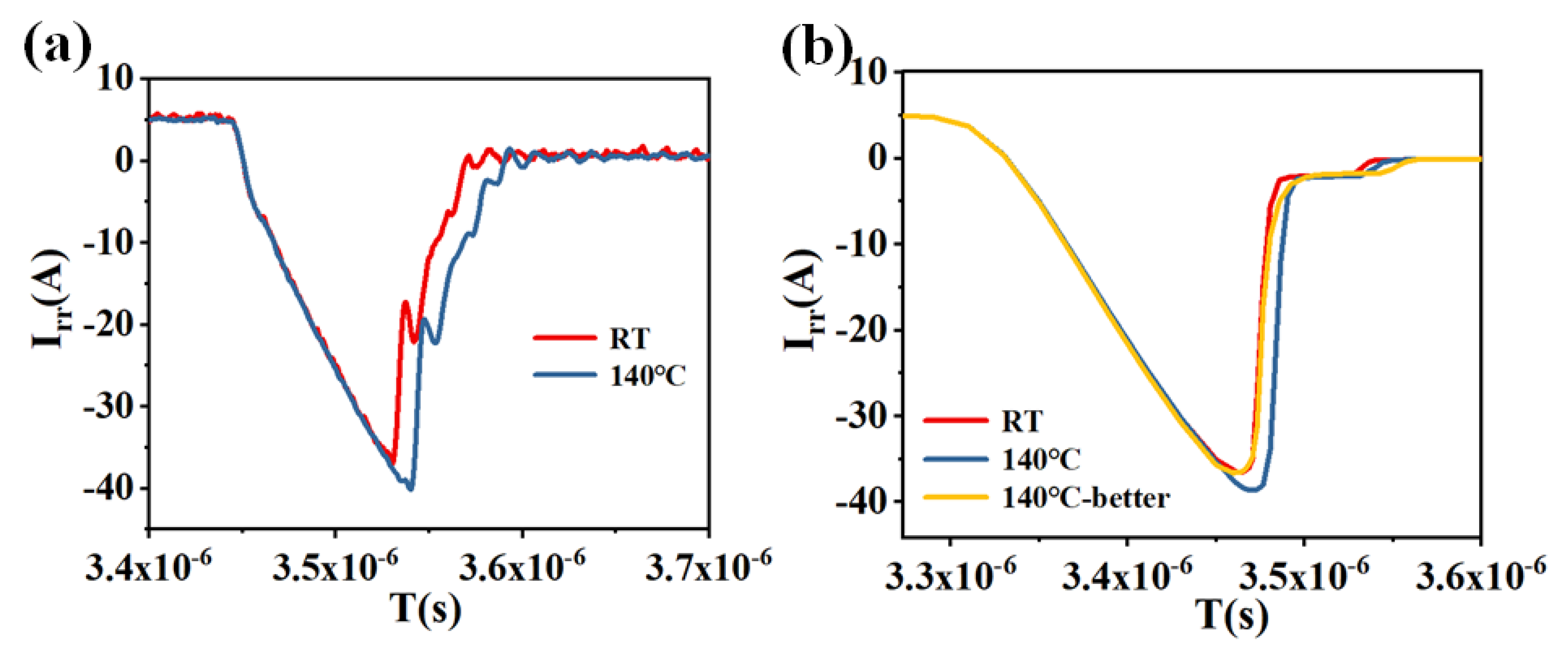

- The variation in carrier lifetime with temperature is identified as the primary mechanism responsible for the degradation of reverse-recovery performance. As temperature increases, the carrier lifetime extends, leading to increased reverse-recovery charge, higher peak reverse current, and longer reverse-recovery time.

- The reverse-recovery performance of superjunction MOSFETs can be effectively improved by connecting a small snubber capacitor in parallel with the device. This modification reduces the reverse-recovery current, reverse-recovery charge, and reverse-recovery time, thereby enhancing device reliability under high-temperature operation.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, Y.; Xu, L.; Miao, Z. A Superjunction Schottky Barrier Diode with Trench Metal–Oxide–Semiconductor Structure. IEEE Electron Device Lett. 2012, 33, 1744–1746. [Google Scholar] [CrossRef]

- Ye, Z.Y.; Liu, L.; Yao, Y.; Lin, M.Z.; Wang, P.F. Fabrication of a 650 V Superjunction MOSFET with Built-In MOS-Channel Diode for Fast Reverse Recovery. IEEE Electron Device Lett. 2019, 40, 1159–1162. [Google Scholar] [CrossRef]

- Li, R.; Huang, M.; Zhang, X.; Hu, M.; Yang, Z.; Ma, Y.; Gong, M. Superjunction MOSFET with a Trench Contact on Partly Relatively Lightly Doped P-Pillar for Excellent Reverse Recovery. Semicond. Sci. Technol. 2021, 36, 105002. [Google Scholar] [CrossRef]

- Yamashita, H.; Ono, S.; Ichijo, H.; Tsuji, M.; Saito, W. Low-Noise Superjunction MOSFET with Integrated Snubber Structure. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Las Vegas, NV, USA, 1–5 June 2025; IEEE: New York, NY, USA, 2018; pp. 32–35. [Google Scholar]

- Park, J.; Lee, J.H. A 650 V Super-Junction MOSFET with Novel Hexagonal Structure for Superior Static Performance and High BV Resilience to Charge Imbalance: A TCAD Simulation Study. IEEE Electron Device Lett. 2017, 38, 111–114. [Google Scholar] [CrossRef]

- Udrea, F.; Deboy, G.; Fujihira, T. Superjunction Power Devices: History, Development, and Future Prospects. IEEE Trans. Electron Devices 2017, 64, 720–734. [Google Scholar] [CrossRef]

- Xia, Y.; Chen, W.; Sun, R.; Li, Z.; Zhang, B. A Superjunction MOSFET with Ultralow Reverse Recovery Charge and Low Switching Losses. J. Electron. Mater. 2021, 50, 6297–6306. [Google Scholar] [CrossRef]

- Arai, D.; Yamaji, M.; Murakami, K.; Honda, M.; Kunori, S. Effect of Charge Imbalance and Edge Structure on the Reverse Recovery Waveform in Superjunction Body Diode. In Proceedings of the IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; IEEE: New York, NY, USA, 2018; pp. 180–183. [Google Scholar]

- Yuan, X.; Oswald, N.; Mellor, P. Superjunction MOSFETs in Voltage-Source Three-Level Converters: Experimental Investigation of Dynamic Behavior and Switching Losses. IEEE Trans. Power Electron. 2015, 30, 6495–6501. [Google Scholar] [CrossRef]

- Zhuo, Y.; Jing, Z.; Xin, T.; Sun, W.; Bo, H. Investigations of Inhomogeneous Reverse-Recovery Behavior of the Body Diode in Superjunction MOSFET. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sapporo, Japan, 28 May–1 June 2017; IEEE: New York, NY, USA, 2017; pp. 155–158. [Google Scholar]

- Rodriguez, J.; Roig, J.; Rodriguez, A.; Lamar, D.G.; Bauwens, F. Evaluation of Superjunction MOSFETs in Cascode Configuration for Hard-Switching Operation. IEEE Trans. Power Electron. 2017, 32, 7021–7037. [Google Scholar] [CrossRef]

- Cheng, X.; Liu, X.; Sin, J.; Kang, B. Improving the CoolMOS Body-Diode Switching Performance with Integrated Schottky Contacts. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Cambridge, UK, 14–17 April 2003; IEEE: New York, NY, USA, 2003; pp. 304–307. [Google Scholar]

- Lin, Z.; Yuan, Q.; Hu, S.; Zhou, X.; Zhou, J.; Tang, F. A Simulation Study of a Novel Superjunction MOSFET Embedded with an Ultrasoft Reverse-Recovery Body Diode. IEEE Trans. Electron Devices 2019, 66, 2333–2338. [Google Scholar] [CrossRef]

- Lin, Z.; Hu, S.; Yuan, Q.; Zhou, X.; Tang, F. Low-Reverse-Recovery-Charge Superjunction MOSFET with a P-Type Schottky Body Diode. IEEE Electron Device Lett. 2017, 38, 1059–1062. [Google Scholar] [CrossRef]

- Li, P.; Guo, J.; Hu, S.; Lin, Z.; Tang, F. A Low Reverse-Recovery Charge Superjunction MOSFET with an Integrated Tunneling Diode. IEEE Trans. Electron Devices 2019, 66, 4309–4313. [Google Scholar] [CrossRef]

- Saito, W.; Ono, S.; Yamashita, H. Influence of Carrier Lifetime Control Process in Superjunction MOSFET Characteristics. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; IEEE: New York, NY, USA, 2014; pp. 87–90. [Google Scholar]

- Schmitt, M.; Schulze, H.J.; Schlogl, A.; Vosseburger, A.; Willmeroth, A.; Deboy, G.; Wachutka, G. A Comparison of Electron, Proton and Helium Ion Irradiation for the Optimization of the CoolMOS Body Diode. In Proceedings of the 14th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sante Fe, NM, USA, 7 June 2002; IEEE: New York, NY, USA, 2002; pp. 229–232. [Google Scholar]

- Xue, P.; Maresca, L.; Riccio, M.; Breglio, G.; Irace, A. Investigation on the Self-Sustained Oscillation of Superjunction MOSFET Intrinsic Diode. IEEE Trans. Electron Devices 2019, 66, 605–612. [Google Scholar] [CrossRef]

- Kao, Y.C.; Davis, J.R. Correlations between Reverse-Recovery Time and Lifetime of p–n Junction Driven by a Current Ramp. IEEE Trans. Electron Devices 1970, 17, 652–657. [Google Scholar] [CrossRef]

- Tyagi, M.S.; van Overstraeten, R. Minority Carrier Recombination in Heavily Doped Silicon. Solid-State Electron. 1983, 26, 577–597. [Google Scholar] [CrossRef]

- Goebel, H.; Hoffmann, K. Full Dynamic Power Diode Model Including Temperature Behavior for Use in Circuit Simulators. In Proceedings of the 4th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Tokyo, Japan, 19–21 May 1992; IEEE: New York, NY, USA, 1992; pp. 130–135. [Google Scholar]

- Liao, X.F.; Yang, Y.T.; Liu, Y.; Xu, C.Q. Simulation-Aided Hardening of Power Diodes to Prevent Single-Event Burnout. IEEE Trans. Electron Devices 2022, 69, 5088–5095. [Google Scholar] [CrossRef]

- Synopsys, Inc. TCAD Sentaurus Device Manual; Synopsys, Inc.: Mountain View, CA, USA, 2016. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cui, W.; Liao, P.; Wang, Y.; Guo, J.; Yang, Y.; Zhang, D.W.; Xu, H. Temperature-Dependent Reverse-Recovery Behavior Analysis and Circuit-Level Mitigation of Superjunction MOSFETs. Micromachines 2025, 16, 1252. https://doi.org/10.3390/mi16111252

Cui W, Liao P, Wang Y, Guo J, Yang Y, Zhang DW, Xu H. Temperature-Dependent Reverse-Recovery Behavior Analysis and Circuit-Level Mitigation of Superjunction MOSFETs. Micromachines. 2025; 16(11):1252. https://doi.org/10.3390/mi16111252

Chicago/Turabian StyleCui, Wenrong, Peng Liao, Yanghao Wang, Jianbin Guo, Yafen Yang, David Wei Zhang, and Hang Xu. 2025. "Temperature-Dependent Reverse-Recovery Behavior Analysis and Circuit-Level Mitigation of Superjunction MOSFETs" Micromachines 16, no. 11: 1252. https://doi.org/10.3390/mi16111252

APA StyleCui, W., Liao, P., Wang, Y., Guo, J., Yang, Y., Zhang, D. W., & Xu, H. (2025). Temperature-Dependent Reverse-Recovery Behavior Analysis and Circuit-Level Mitigation of Superjunction MOSFETs. Micromachines, 16(11), 1252. https://doi.org/10.3390/mi16111252