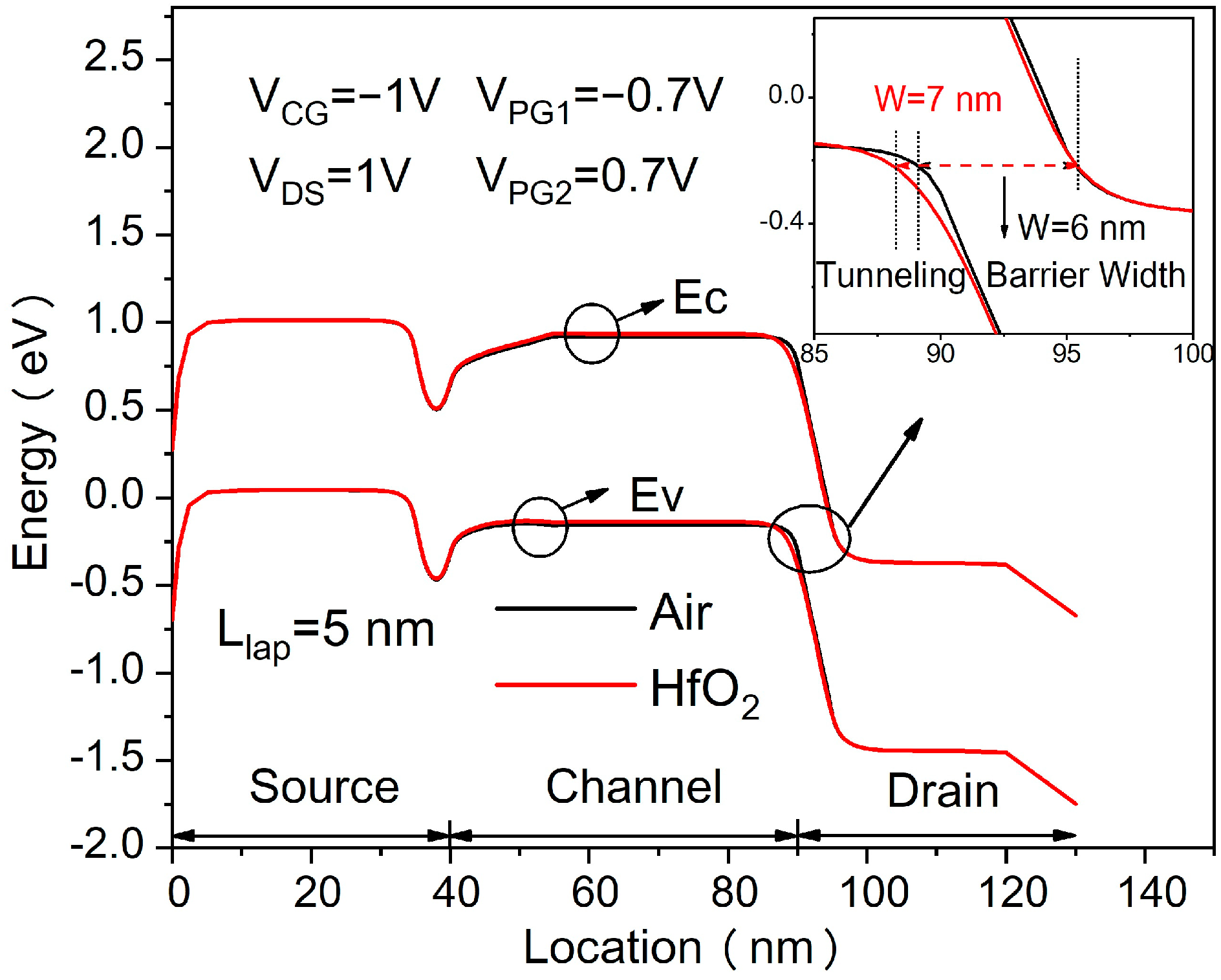

Controlling Drain Side Tunneling Barrier Width in Electrically Doped PNPN Tunnel FET

Abstract

1. Introduction

2. Simulation Parameters and Approach

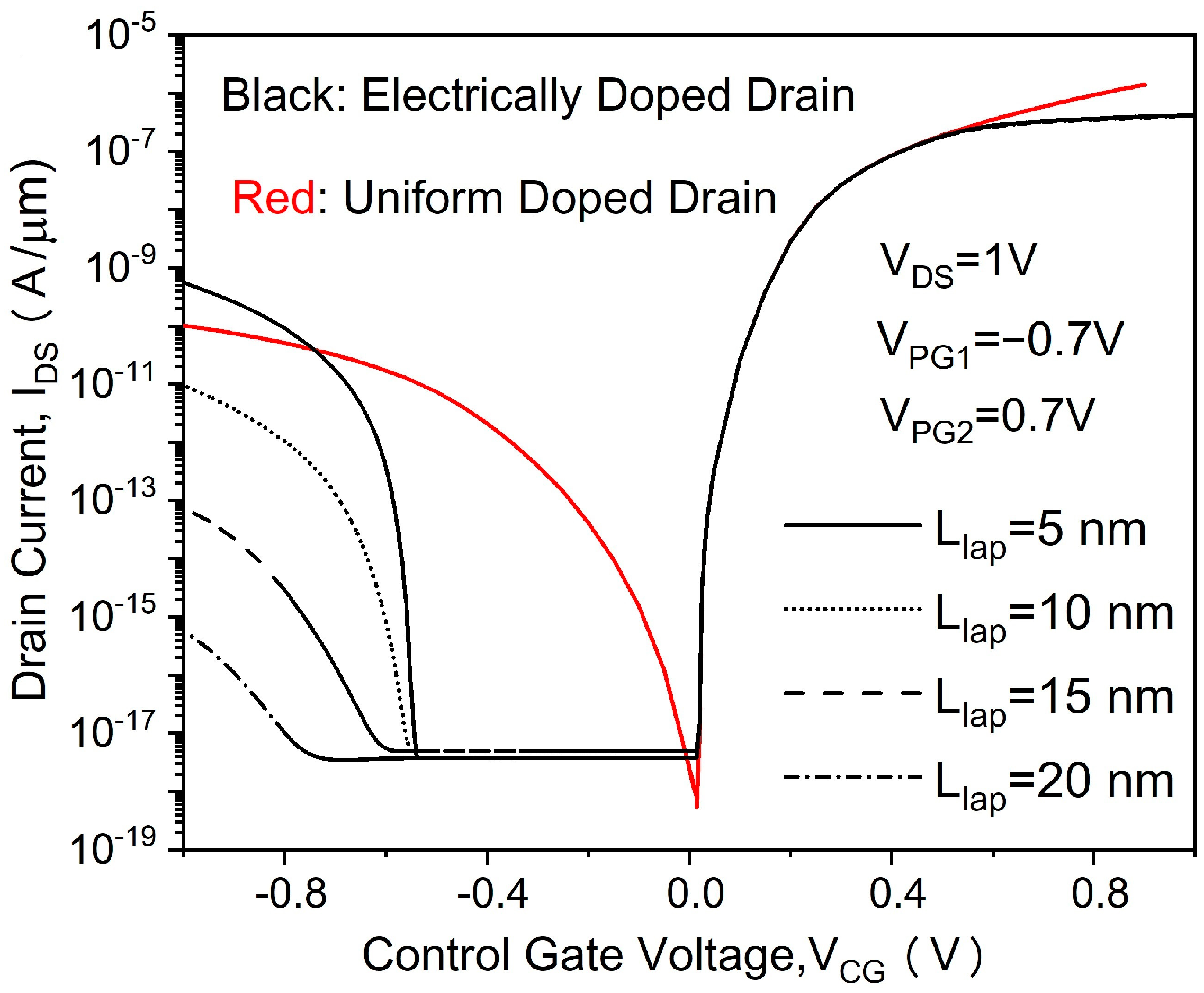

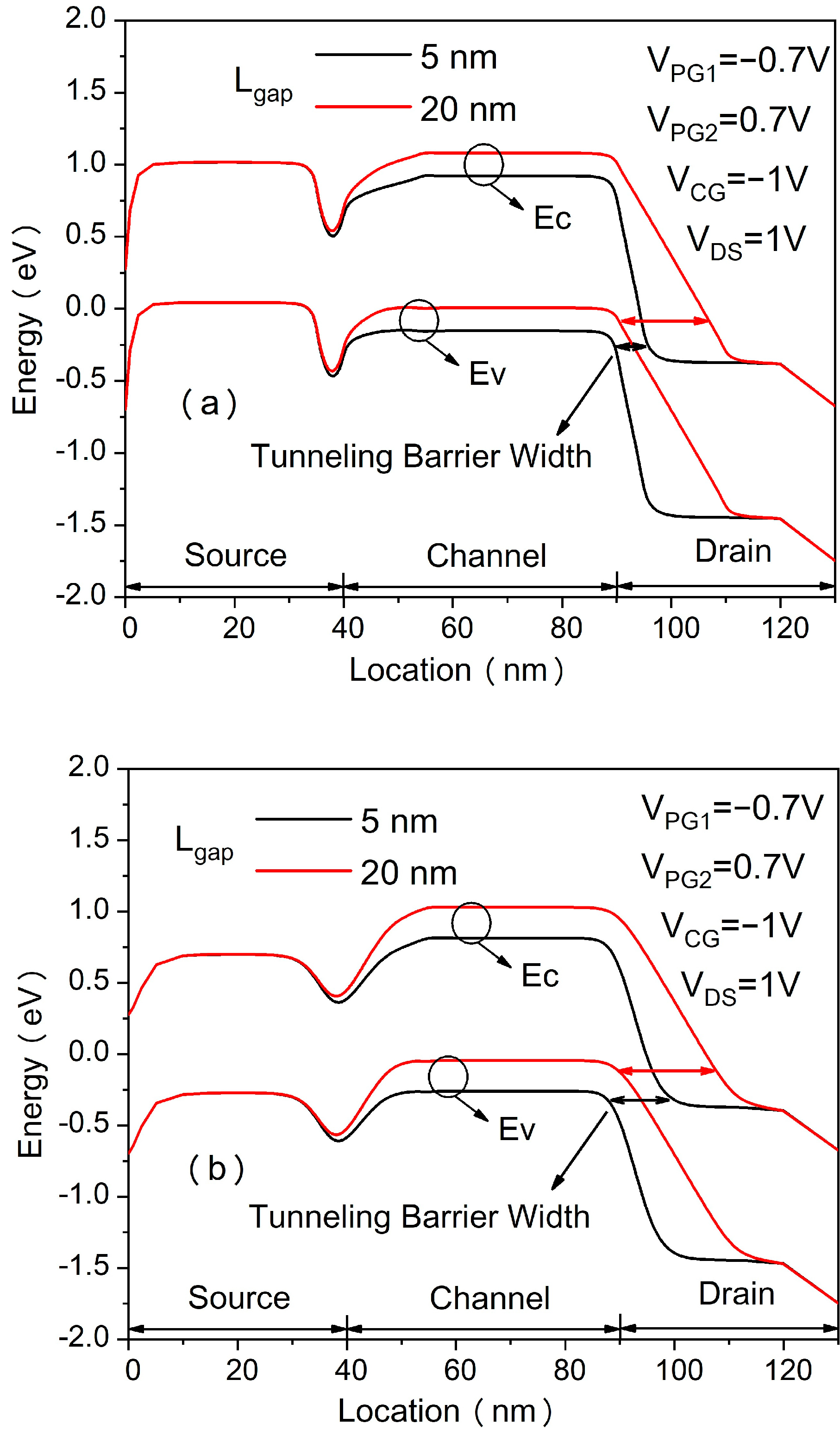

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Saurabh, S.; Kumar, M.J. Basics of Tunnel Field-Effect Transistors. In Fundamentals of Tunnel Field-Effect Transistors, 1st ed.; CRC Press: Boca Raton, USA, 2016; Volume 3, pp. 44–45. [Google Scholar] [CrossRef]

- Vishnoi, R.; Kumar, M.J. An accurate compact analytical model for the drain current of a TFET from subthreshold to strong inversion. IEEE Trans. Electron Dev. 2015, 62, 478–484. [Google Scholar] [CrossRef]

- Ma, W.C.Y.; Luo, S.M. Impacts of stress voltage and channel length on hot-carrier characteristics of tunnel fifield-effect thin-film transistor. IEEE Trans. Electron Dev. 2020, 67, 5243–5246. [Google Scholar] [CrossRef]

- Boucart, K.; Ionescu, A.M. Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Dev. 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- Kumar, M.J.; Janardhanan, S. Doping-less tunnel field effect transistor: Design and investigation. IEEE Trans. Electron Dev. 2013, 60, 3285–3290. [Google Scholar] [CrossRef]

- Liu, K.M.; Cheng, C.P. Investigation on the effects of gate-source overlap/underlap and source doping gradient of n-type Si cylindrical gate-all-around tunnel field-effect transistors. IEEE Trans. Nanotechnol. 2020, 19, 382–389. [Google Scholar] [CrossRef]

- Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. Double-Gate Strained-Ge Heterostructure Tunneling FET (TFET) With record high drive currents and ≪60 mV/dec subthreshold slope. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008. [Google Scholar] [CrossRef]

- Vladimirescu, A.; Amara, A.; Anghel, C. An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid State Electron. 2012, 70, 67–72. [Google Scholar] [CrossRef]

- Abdi, D.B.; Kumar, M.J. Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Dev. Soc. 2014, 2, 187–190. [Google Scholar] [CrossRef]

- Nagavarapu, N.V.; Jhaveri, R.; Woo, J.C.S. The tunnel source (PNPN) n-MOSFET: A novel high performance transistor. IEEE Trans. Electron Dev. 2008, 55, 1013–1019. [Google Scholar] [CrossRef]

- Narang, R.; Saxena, M.; Gupta, R.S.; Gupta, M. Impact of temperature variations on the device and circuit performance of tunnel FET: A simulation study. IEEE Trans. Nanotechnol. 2013, 12, 951–957. [Google Scholar] [CrossRef]

- Cui, N.; Liang, R.; Wang, J.; Zhou, W.; Xu, J. A PNPN tunnel field-effect transistor with high-k gate and low-k fringe dielectrics. J. Semicond. 2012, 33, 084004. [Google Scholar] [CrossRef]

- Cao, W.; Yao, C.J.; Jiao, G.F.; Huang, D.; Yu, H.Y.; Li, M.F. Improvement in reliability of tunneling field-effect transistor with p-n-i-n structure. IEEE Trans. Electron Dev. 2011, 58, 2122–2126. [Google Scholar] [CrossRef]

- Cho, S.; Kang, I.M. Design optimization of tunneling field-effect transistor based on silicon nanowire PNPN structure and its radio frequency characteristics. Curr. Appl. Phys. 2012, 12, 673–677. [Google Scholar] [CrossRef]

- Jhaveri, R.; Nagavarapu, N.V.; Woo, J.C.S. Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron Dev. 2011, 58, 80–86. [Google Scholar] [CrossRef]

- Tura, A.; Zhang, Z.; Liu, P.; Xie, Y.H.; Woo, J.C.S. Vertical silicon p-n-p-n tunnel nMOSFET with MBE-grown tunneling junction. IEEE Trans. Electron Dev. 2011, 58, 1907–1913. [Google Scholar] [CrossRef]

- Chang, H.Y.; Adams, B.; Chien, P.Y.; Li, J.; Woo, J.C.S. Improved subthreshold and output characteristics of source-pocket Si tunnel FET by the application of laser annealing. IEEE Trans. Electron Dev. 2013, 60, 92–96. [Google Scholar] [CrossRef]

- Zhang, Y.; Chu, H. Tunneling Field Effect Transistor (TFET) with Ultra-Shallow Pockets Formed by Asymmetric ion Implantation and Method of Making Same. U.S. Patent 20140158990, June 2014. [Google Scholar]

- Li, J.; Liu, Y.; Wei, S.F.; Shan, C. In-Built N+ Pocket Electrically Doped Tunnel FET With Improved DC and Analog/RF Performance. Micromachines 2020, 11, 960. [Google Scholar] [CrossRef] [PubMed]

- De Marchi, M.; Zhang, J.; Frache, S.; Sacchetto, D.; Gaillardon, P.E.; Leblebici, Y.; De Micheli, G. Configurable logic gates using polarity-controlled silicon nanowire gate-all-around FETs. IEEE Electron Device Lett. 2014, 35, 880–882. [Google Scholar] [CrossRef]

- Lahgere, A.; Sahu, C.; Singh, J. PVT-aware design of dopingless dynamically configurable tunnel FET. IEEE Trans. Electron Dev. 2015, 62, 2404–2409. [Google Scholar] [CrossRef]

- Kondekar, P.N.; Nigam, K.; Pandey, S.; Sharma, D. Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans. Electron Dev. 2016, 64, 412–418. [Google Scholar] [CrossRef]

- De Marchi, M.; Sacchetto, D.; Frache, S.; Zhang, J.; Gaillardon, P.-E.; Leblebici, Y.; De Micheli, G. Polarity control in double-gate, gate-all-around vertically stacked silicon nanowire FETs. In Proceedings of the IEEE Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012. [Google Scholar] [CrossRef]

- Haynes, W.M. Electron Work Function of the Elements. In CRC Handbook of Chemistry and Physics, 95th ed.; Lide, D.R., Bruno, T.J., Eds.; CRC Press: New York, NY, USA, 2008; pp. 12–1014. [Google Scholar]

- ATLAS Device Simulation Software, version 5.19.20.R; Silvaco: Santa Clara, CA, USA, 2018.

- Musalgaonkar, G.; Sahay, S.; Saxena, R.S.; Kumar, M.J. A line tunneling field-effect transistor based on misaligned Core–Shell gate architecture in emerging nanotube FETs. IEEE Trans. Electron Dev. 2019, 66, 2809–2816. [Google Scholar] [CrossRef]

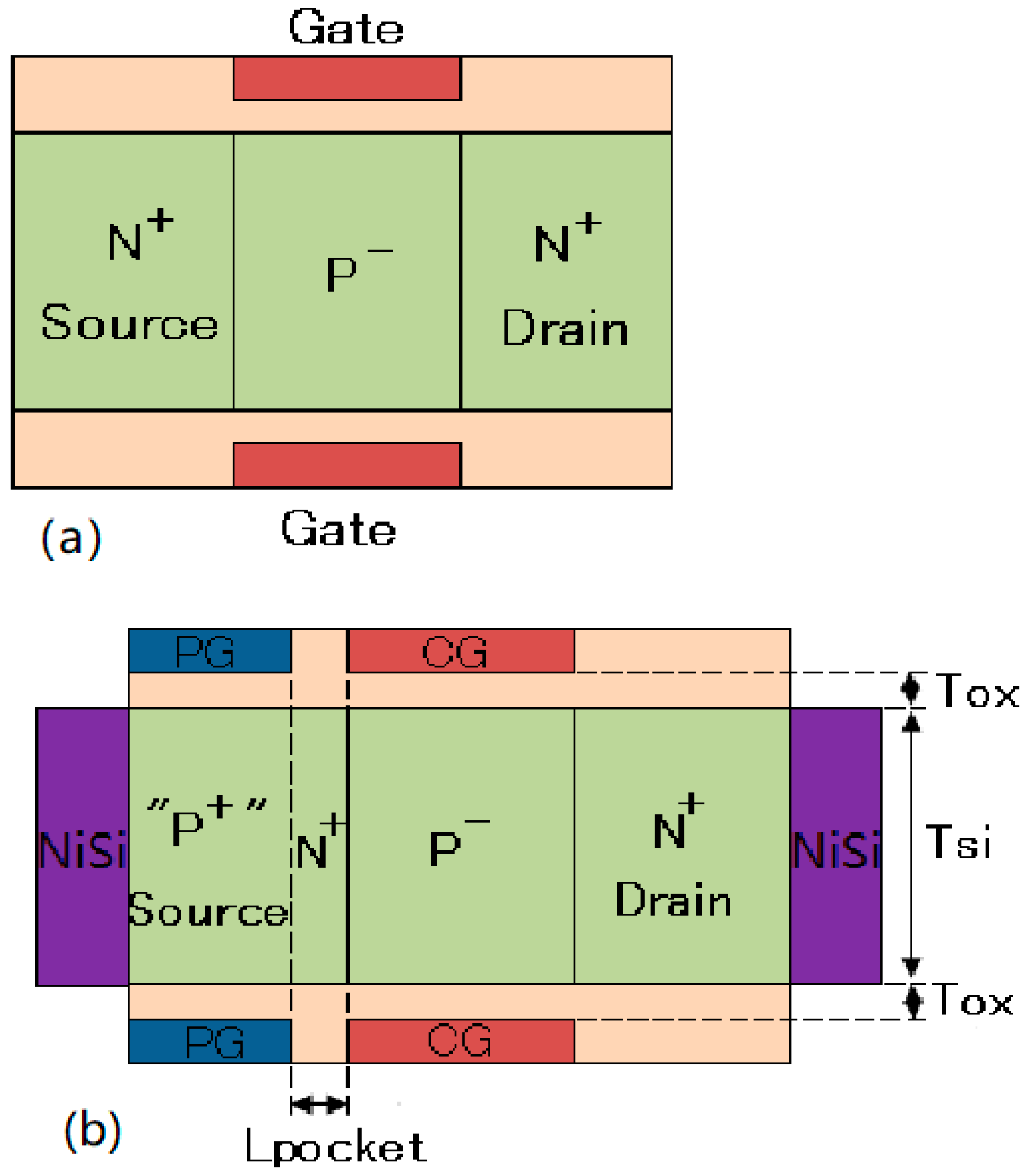

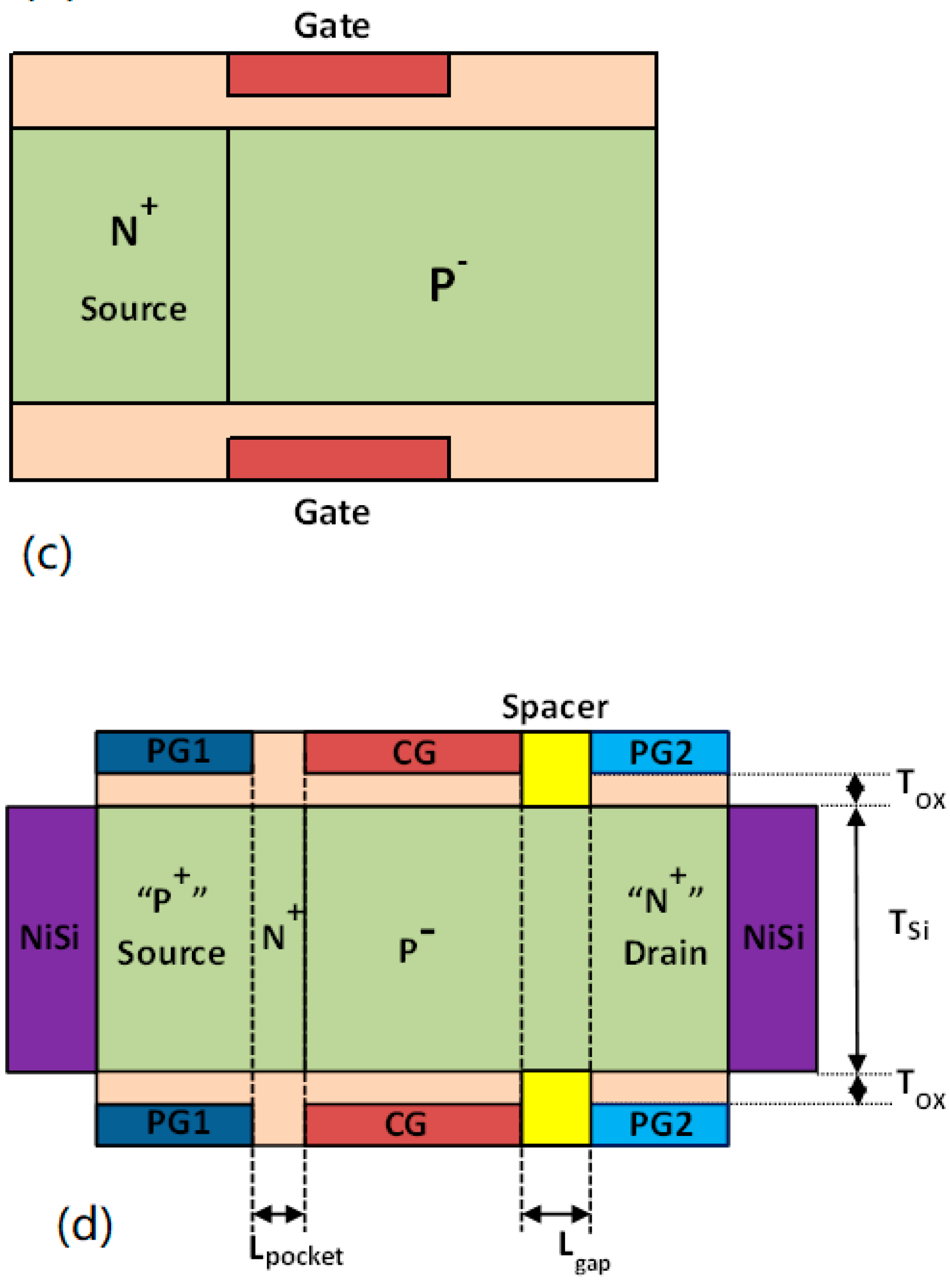

| Device Design | Conventional ED-TFET | Conventional In-Built N+ Pocket ED-TFET with Uniform Doped Drain [19] | Proposed In-Built N+ Pocket ED-TFET with an ED Drain |

|---|---|---|---|

| Doping Profile of Beginning Structure (From Source to Drain) | N+-N+-N+ | N+-P−-N+ | N+-P− |

| Doping Profile of Final Stucture (From Source to Drain) | “P+”-N+-N+-N+ | “P+”-N+-P− -N+ | “P+”-N+-P−-“N+” |

| Number of Polarity Gate | 1 | 1 | 2 |

| Location of Polarity Gate | Source Region | Source Region | Source and Drain Region |

| Parameter | Conventional In-Built N+ Pocket ED-TFET [19] | In-Built N+ Pocket ED-TFET with an ED Drain |

|---|---|---|

| Effective Gate Oxide Thickness (EOT) | 0.8 nm | 0.8 nm |

| Silicon Film Thickness (TSi) | 10 nm | 10 nm |

| Control Gate Length | 50 nm | 50 nm |

| Length of pocket (Lpocket) | 5 nm | 5 nm |

| Length of gap (Lgap) | - | 5~25 nm |

| Source Doping | 4 × 1019 cm−3 (N+) | 4 × 1019 cm−3 (N+) |

| Channel Doping | 1 × 1017 cm−3 (P− | 1 × 1017 cm−3 (P−) |

| Drain Doping | 1 × 1017 cm−3 (P−) | 5 × 1018 cm−3 (N+) |

| CG Work function | 4.74 eV | 4.74 eV |

| PG1 Work function | 4.33 eV | 4.33 eV |

| PG2 Work function | - | 4.5 eV |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shan, C.; Yang, L.; Liu, Y.; Liu, Z.-M.; Zheng, H. Controlling Drain Side Tunneling Barrier Width in Electrically Doped PNPN Tunnel FET. Micromachines 2023, 14, 301. https://doi.org/10.3390/mi14020301

Shan C, Yang L, Liu Y, Liu Z-M, Zheng H. Controlling Drain Side Tunneling Barrier Width in Electrically Doped PNPN Tunnel FET. Micromachines. 2023; 14(2):301. https://doi.org/10.3390/mi14020301

Chicago/Turabian StyleShan, Chan, Lan Yang, Ying Liu, Zi-Meng Liu, and Han Zheng. 2023. "Controlling Drain Side Tunneling Barrier Width in Electrically Doped PNPN Tunnel FET" Micromachines 14, no. 2: 301. https://doi.org/10.3390/mi14020301

APA StyleShan, C., Yang, L., Liu, Y., Liu, Z.-M., & Zheng, H. (2023). Controlling Drain Side Tunneling Barrier Width in Electrically Doped PNPN Tunnel FET. Micromachines, 14(2), 301. https://doi.org/10.3390/mi14020301