Improved Fixed-Frequency SOGI Based Single-Phase PLL

Abstract

:1. Introduction

1.1. Motivation

1.2. Literature Review

1.3. Contribution and Paper Organization

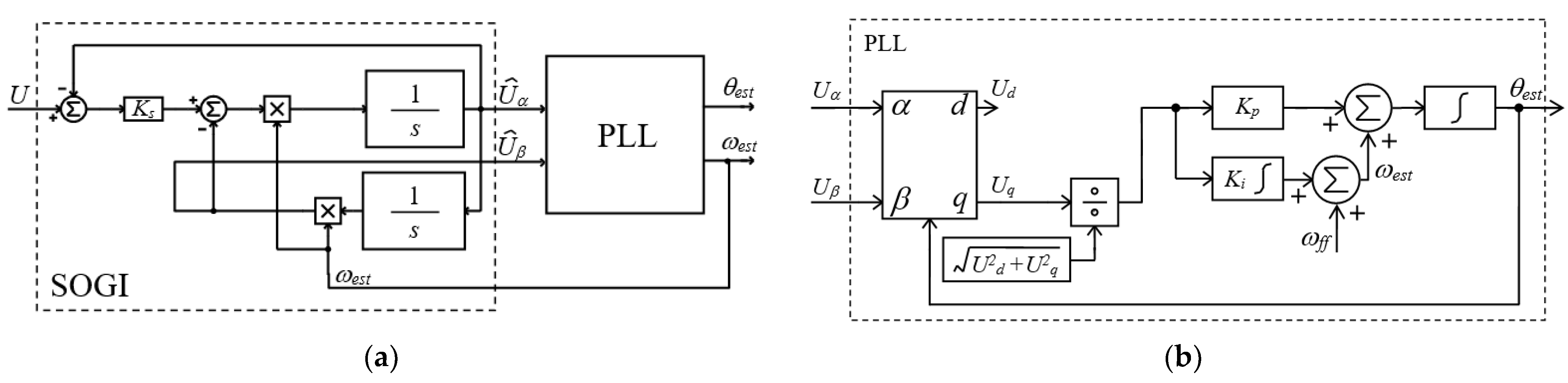

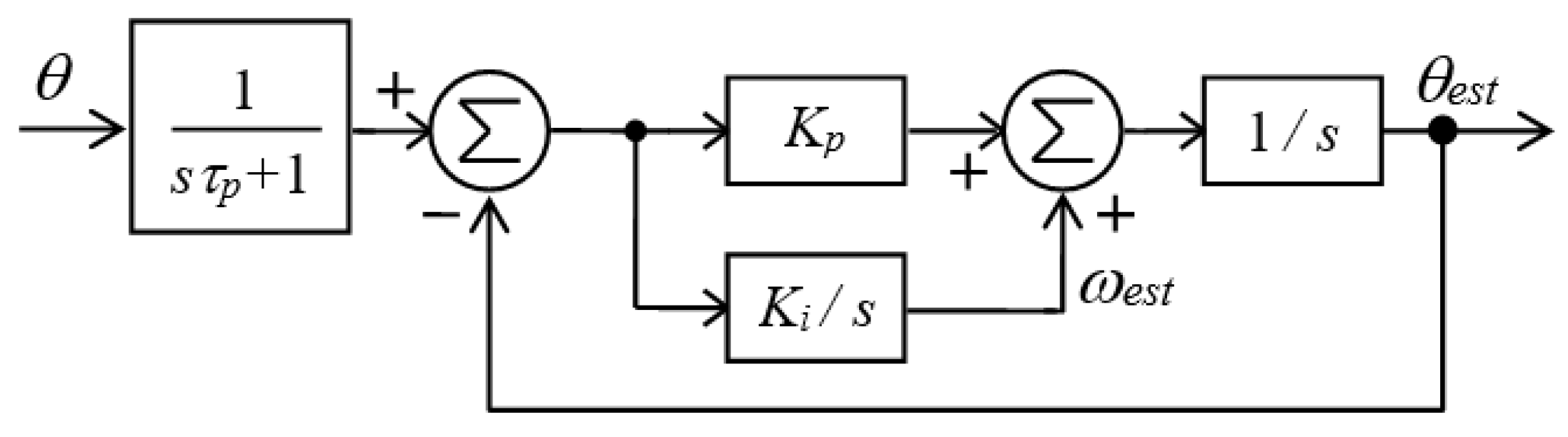

2. Fixed-Frequency PLL

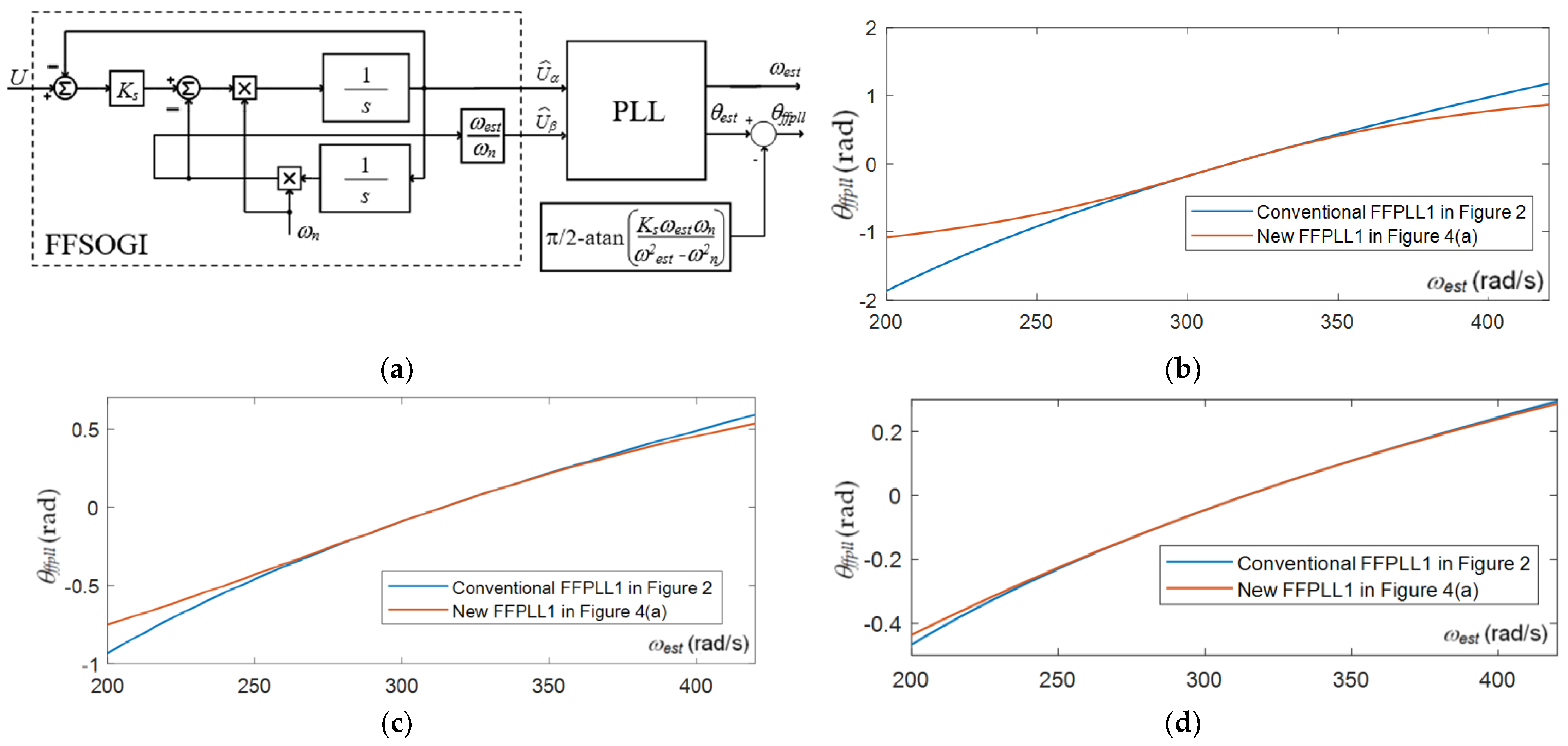

3. Improved FFPLL1 Structure

3.1. Improved Correction of the Phase Angle Estimated by FFPLL1

3.2. FFPLL1 Parameter Tuning Procedure

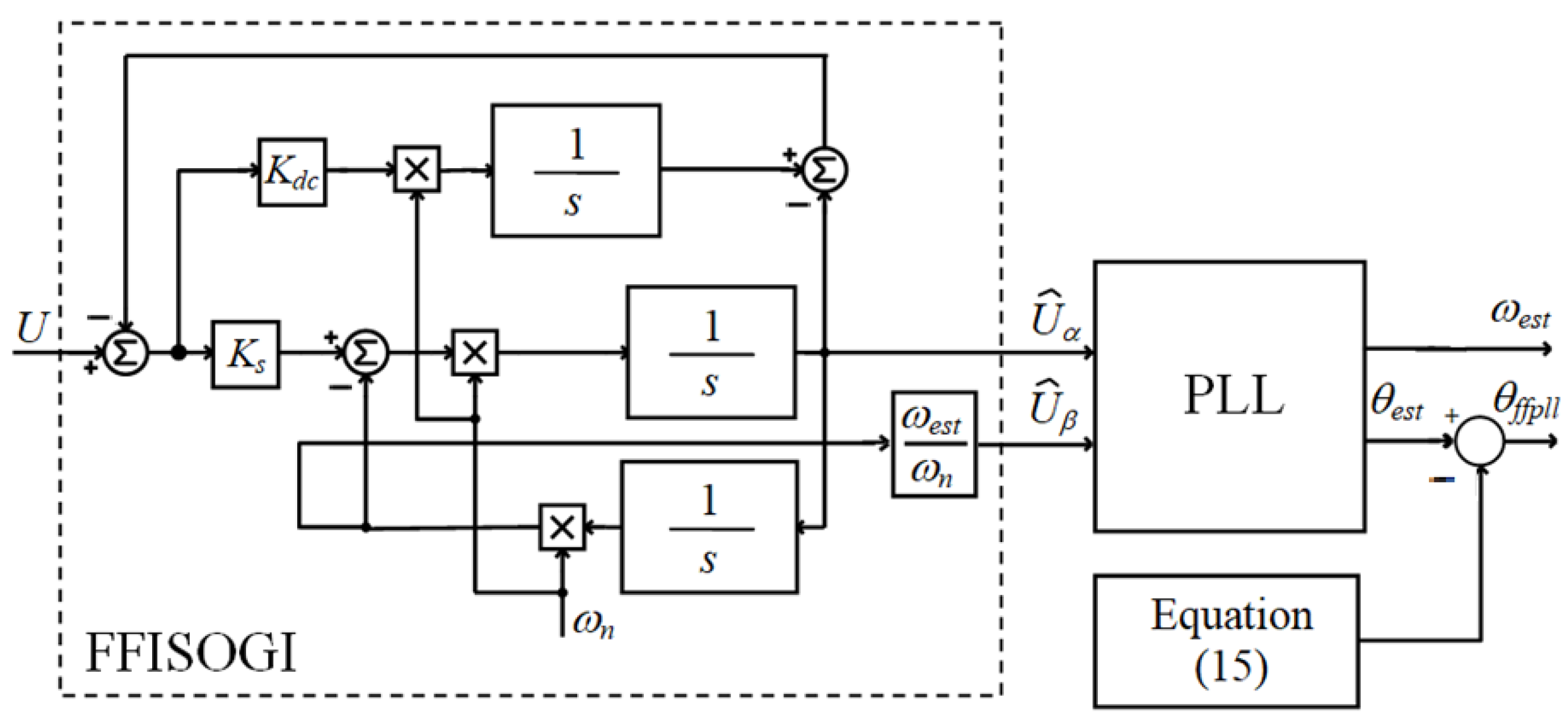

3.3. The FFPLL Modification with the DC Offset Compensation

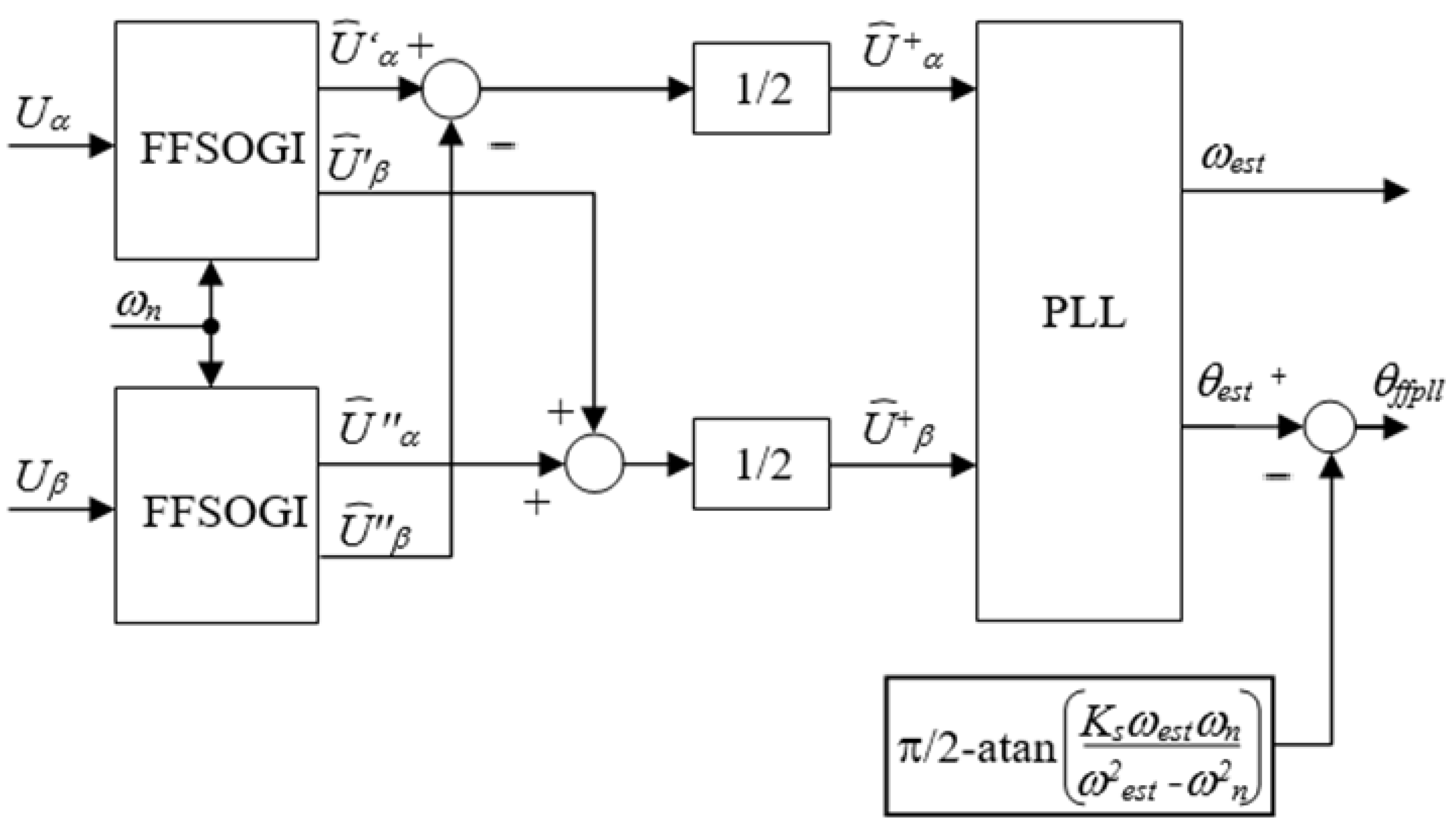

3.4. The FFPLL Based Synchronization with the Positive Sequence

4. Results of Simulation Runs

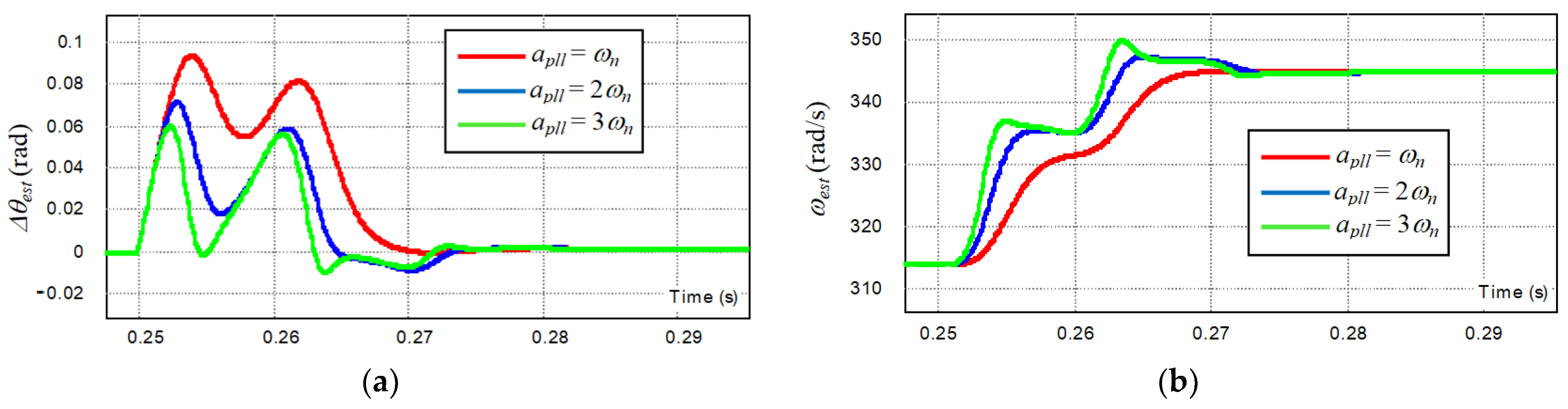

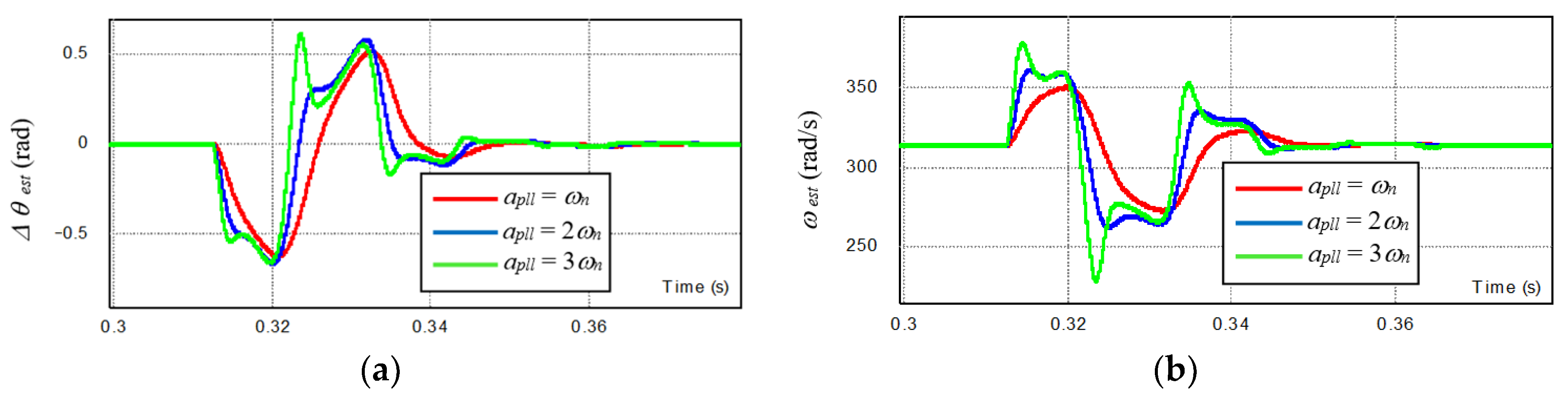

4.1. Simulation of the Improved FFPLL1

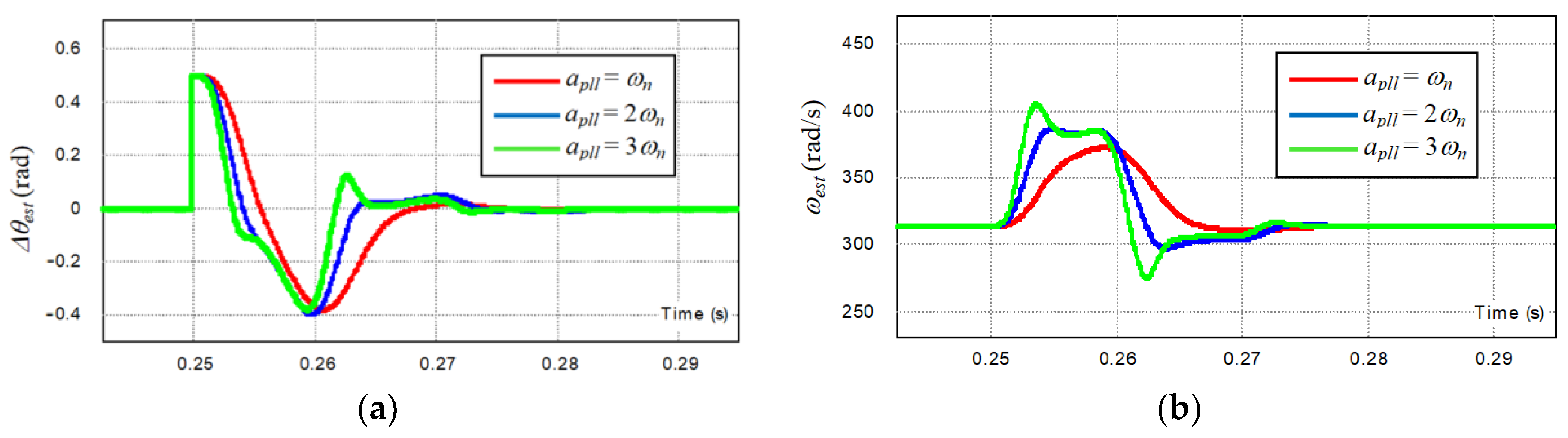

4.2. Simulation of the Improved FFPLL1 with DC Offset Compensation

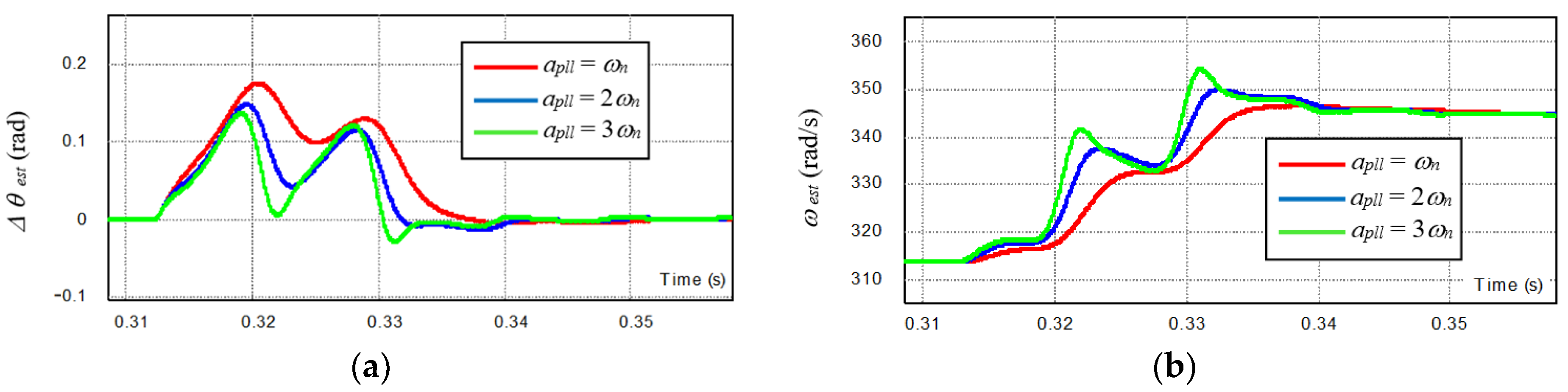

4.3. Simulation of the Improved FFPLL with the Input Signal Positive Sequence Separation

5. Experimental Tests

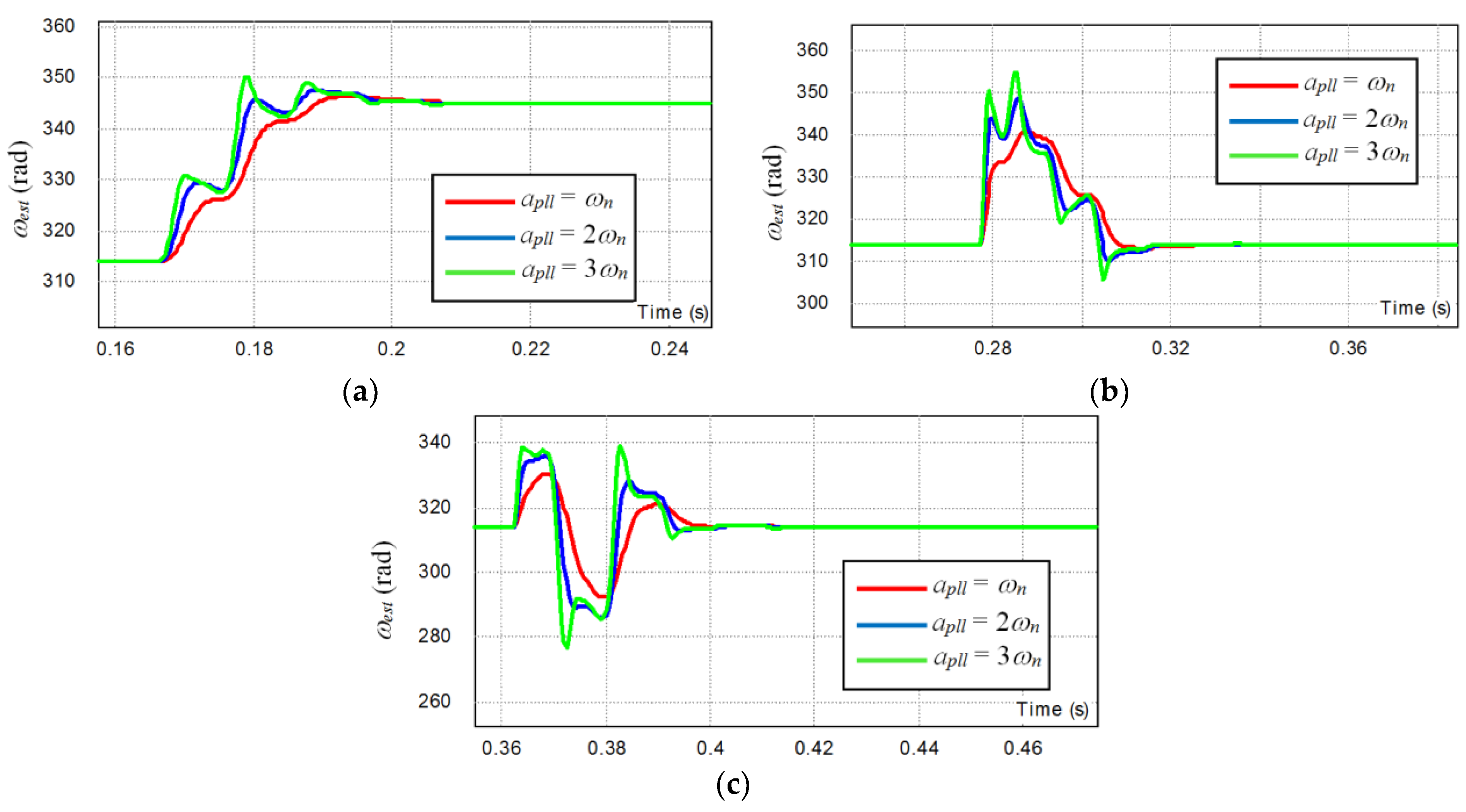

5.1. Experimental Tests of the FFPLL1 in Figure 4

5.2. Experimental Tests of the FFPLL1 in Figure 7

5.3. Experimental Tests of the FFPLL1 in Figure 8

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Golestan, S.; Guerrero, J.M.; Vasquez, J.C. Single-phase PLLs: A review of recent advances. IEEE Trans. Power Electron. 2017, 32, 9013–9030. [Google Scholar] [CrossRef]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Dynamics assessment of advanced single-phase PLL structures. IEEE Trans. Ind. Electron. 2013, 60, 2167–2177. [Google Scholar] [CrossRef]

- Santos Filho, R.M.; Seixas, P.F.; Cortizo, P.C.; Torres, L.A.; Souza, A.F. Comparison of three single-phase PLL algorithms for UPS applications. IEEE Trans. Ind. Electron. 2008, 55, 2923–2932. [Google Scholar] [CrossRef]

- Xie, M.; Wen, H.; Zhu, C.; Yang, Y. DC offset rejection improvement in single-phase SOGI-PLL algorithms: Methods review and experimental evaluation. IEEE Access 2017, 5, 12810–12819. [Google Scholar] [CrossRef]

- Ciobotaru, M.; Teodorescu, R.; Agelidis, V.G. Offset rejection for PLL based synchronization in grid-connected converters. In Proceedings of the 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, Austin, TX, USA, 24–28 February 2008. [Google Scholar]

- Cai, X.; Wang, C.; Kennel, R. A Fast and Precise Grid Synchronization Method Based on Fixed-Gain Filter. IEEE Trans. Ind. Electron. 2018, 65, 7119–7128. [Google Scholar] [CrossRef]

- Xiao, F.; Dong, L.; Li, L.; Liao, X. A frequency-fixed SOGI-based PLL for single-phase grid-connected converters. IEEE Trans. Power Electron. 2017, 32, 1713–1719. [Google Scholar] [CrossRef]

- Golestan, S.; Mousazadeh, S.Y.; Guerrero, J.M.; Vasquez, J.C. A critical examination of frequency-fixed second-order generalized integrator-based phase-locked loops. IEEE Trans. Power Electron. 2017, 32, 6666–6672. [Google Scholar] [CrossRef]

- Reza, M.S.; Ciobotaru, M.; Agelidis, V.G. Estimation of single-phase grid voltage fundamental parameters using fixed frequency tuned second-order generalized integrator based technique. In Proceedings of the 2013 4th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Rogers, AR, USA, 8–11 July 2013. [Google Scholar]

- Nazib, A.A.; Holmes, D.G.; McGrath, B.P. Decoupled DSOGI-PLL for Improved Three Phase Grid Synchronisation. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018. [Google Scholar]

- Goldsmith, J.; Ramsay, C.; Northcote, D.; Barlee, K.W.; Crockett, L.H.; Stewart, R.W. Control and visualisation of a software defined radio system on the Xilinx RFSoC platform using the PYNQ framework. IEEE Access 2020, 8, 129012–129031. [Google Scholar] [CrossRef]

- Breems, L.J.; van Sinderen, J.; Fric, T.; Stoffels, H.; Fritschij, F.; Brekelmans, H.; van der Ploeg, H.; Moehlmann, U.; Rutten, R.; Bolatkale, M.; et al. A Full-Band Multi-Standard Global Analog & Digital Car Radio SoC with a Single Fixed-Frequency PLL. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019. [Google Scholar]

- Guan, Q.; Zhang, Y.; Kang, Y.; Guerrero, J.M. Single-phase phase-locked loop based on derivative elements. IEEE Trans. Power Electron. 2017, 32, 4411–4420. [Google Scholar] [CrossRef]

- Xu, J.; Qian, H.; Hu, Y.; Bian, S.; Xie, S. Overview of SOGI-based single-phase phase-locked loops for grid synchronization under complex grid conditions. IEEE Access 2021, 9, 39275–39291. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M.; Khajehoddin, S.A.; Jain, P.K.; Bakhshai, A.; Mojiri, M. Addressing DC component in PLL and notch filter algorithms. IEEE Trans. Power Electron. 2012, 27, 78–86. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Stojic, D.; Tarczewski, T.; Niewiara, L.J.; Grzesiak, L.M. Improved Fixed-Frequency SOGI Based Single-Phase PLL. Energies 2022, 15, 7297. https://doi.org/10.3390/en15197297

Stojic D, Tarczewski T, Niewiara LJ, Grzesiak LM. Improved Fixed-Frequency SOGI Based Single-Phase PLL. Energies. 2022; 15(19):7297. https://doi.org/10.3390/en15197297

Chicago/Turabian StyleStojic, Djordje, Tomasz Tarczewski, Lukasz J. Niewiara, and Lech M. Grzesiak. 2022. "Improved Fixed-Frequency SOGI Based Single-Phase PLL" Energies 15, no. 19: 7297. https://doi.org/10.3390/en15197297

APA StyleStojic, D., Tarczewski, T., Niewiara, L. J., & Grzesiak, L. M. (2022). Improved Fixed-Frequency SOGI Based Single-Phase PLL. Energies, 15(19), 7297. https://doi.org/10.3390/en15197297