A Modified SOGI-PLL with Adjustable Refiltering for Improved Stability and Reduced Response Time

Abstract

:1. Introduction

2. Development of the Improved PLL

2.1. The PLL Performance Evaluation Criteria

2.2. Proposed ARF-SOGI-QSG Structure

- The value of the single gain k of the adaptive prefilter affects all the characteristics of the SOGI-QSG;

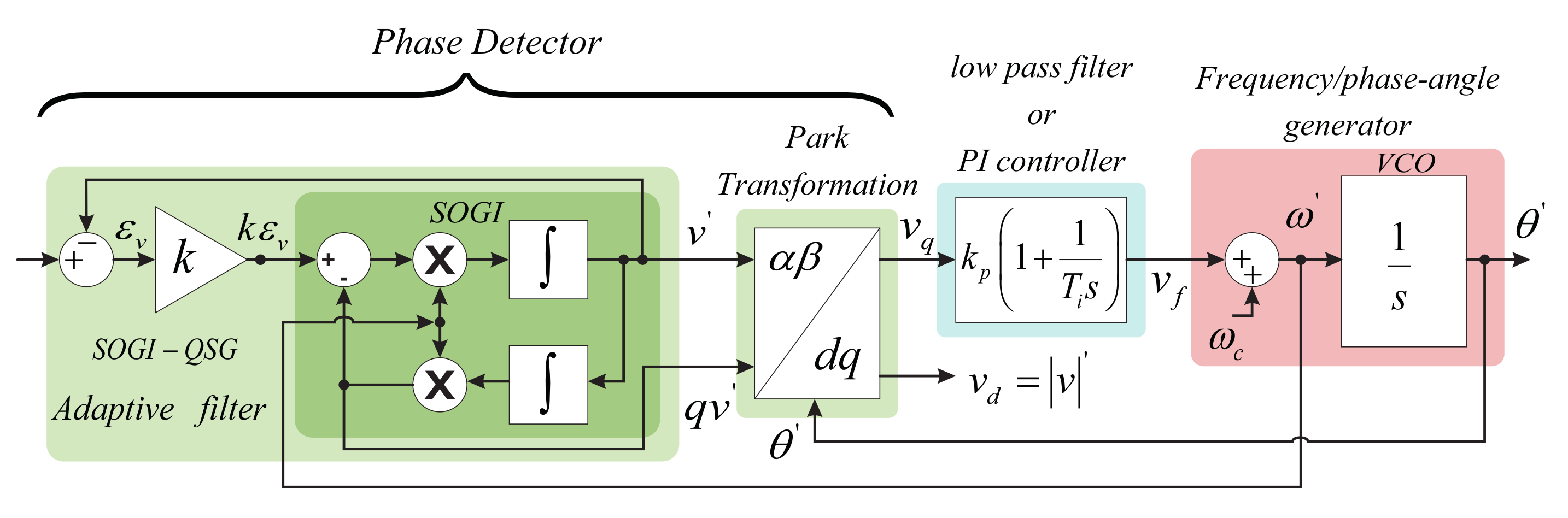

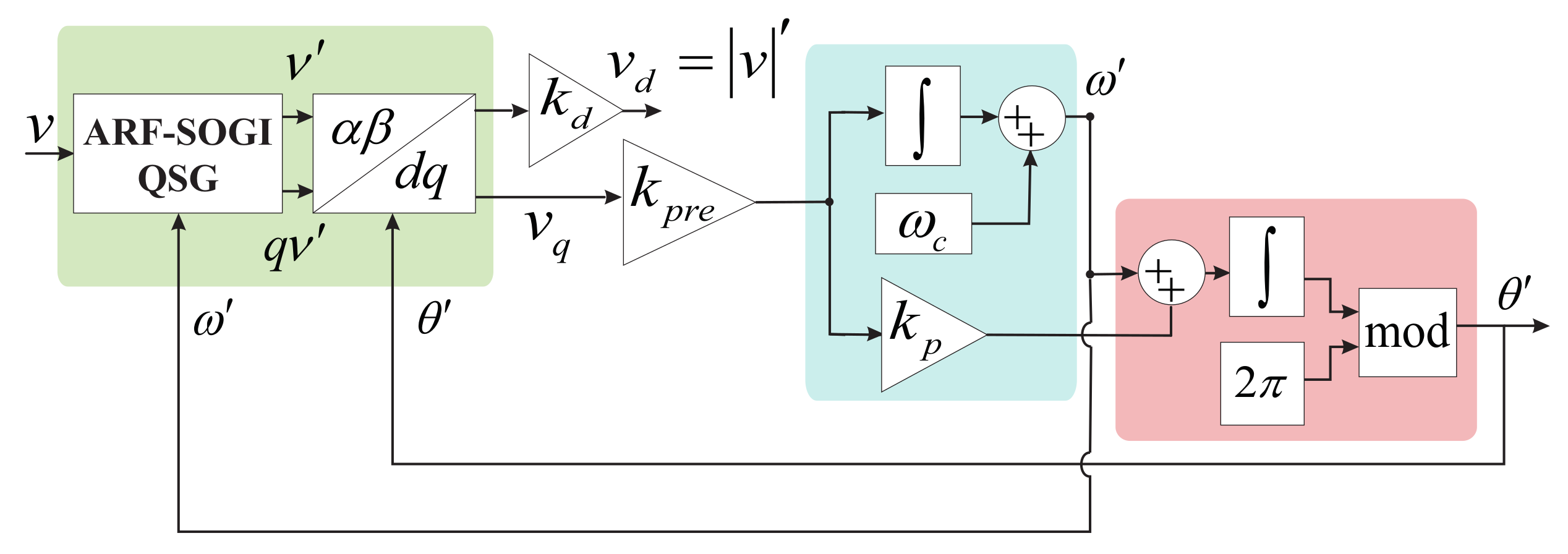

- The magnitude of the line voltage is calculated by the Park transformation and reported as , as shown in Figure 1;

- The frequency calculated by the PLL is fed back to the SOGI block;

- The angle is calculated by the integrator or VCO and fed back to the Park transformation block.

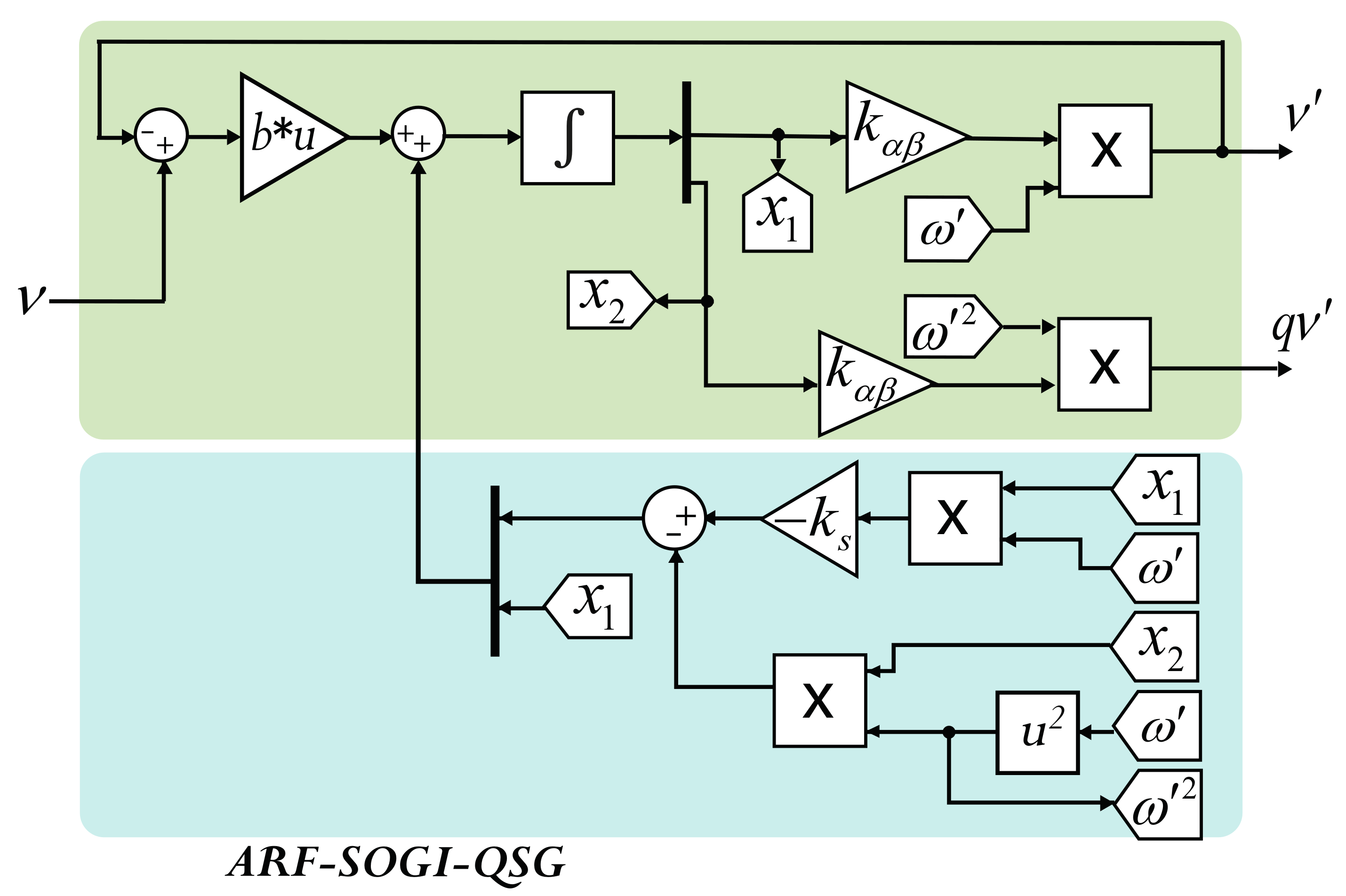

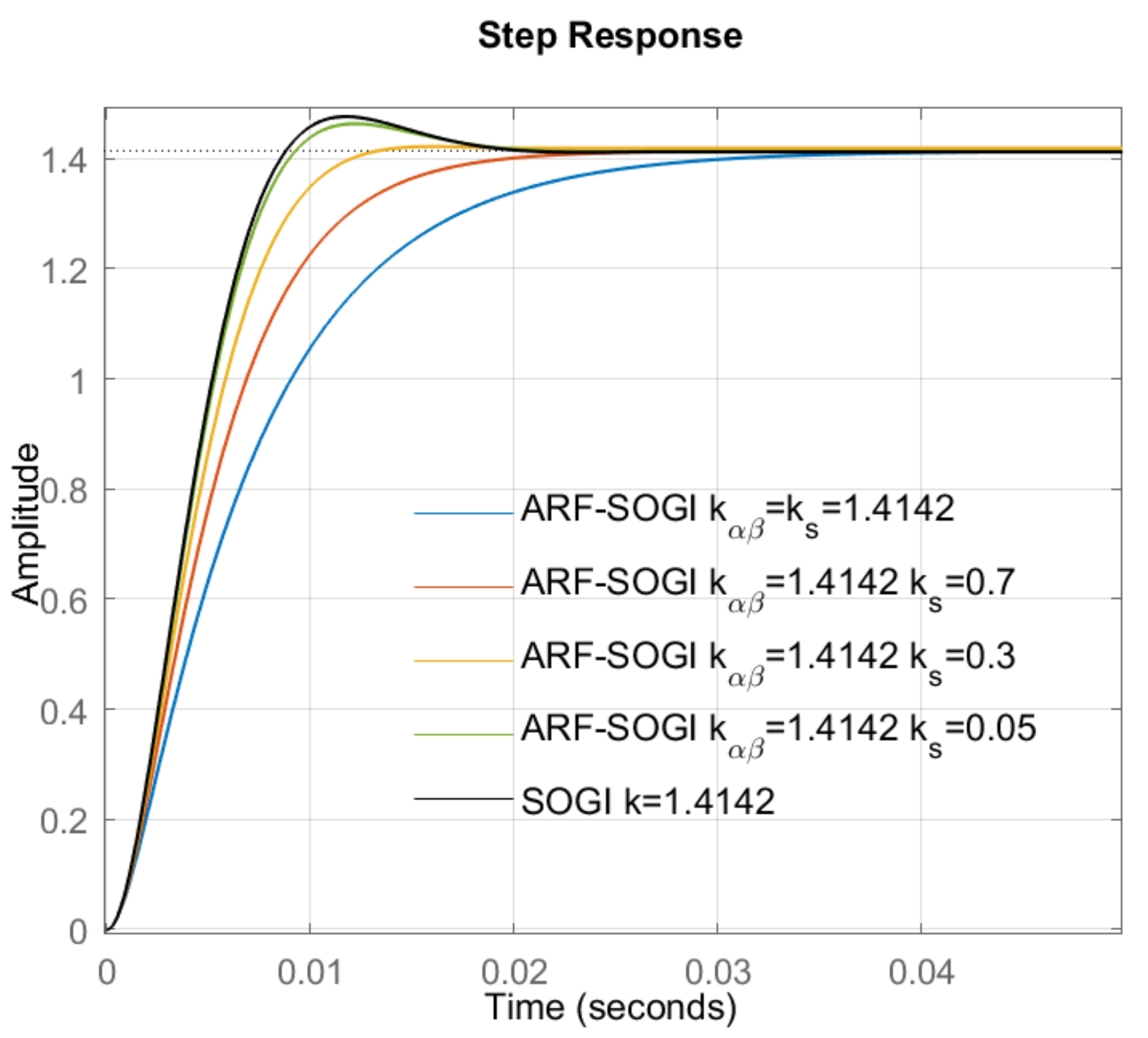

- Since the gain in Figure 2 can be adjusted in value without unbalancing the magnitude of the responses and , the change in the value of this gain does not affect the orthogonality of the two signals;

- Using different gain values at the outputs and of the filtering could only be possible with very slight differences (of the order of ). Greater differences cause a different attenuation in the magnitude of signals and , which can produce imbalances and, therefore, oscillations at the PLL output (at twice the fundamental frequency of the input signal). Hence, it is recommended that these two gains from the ARF-SOGI-QSG output are equal, and from now on, the single gain is called , as seen in Figure 2;

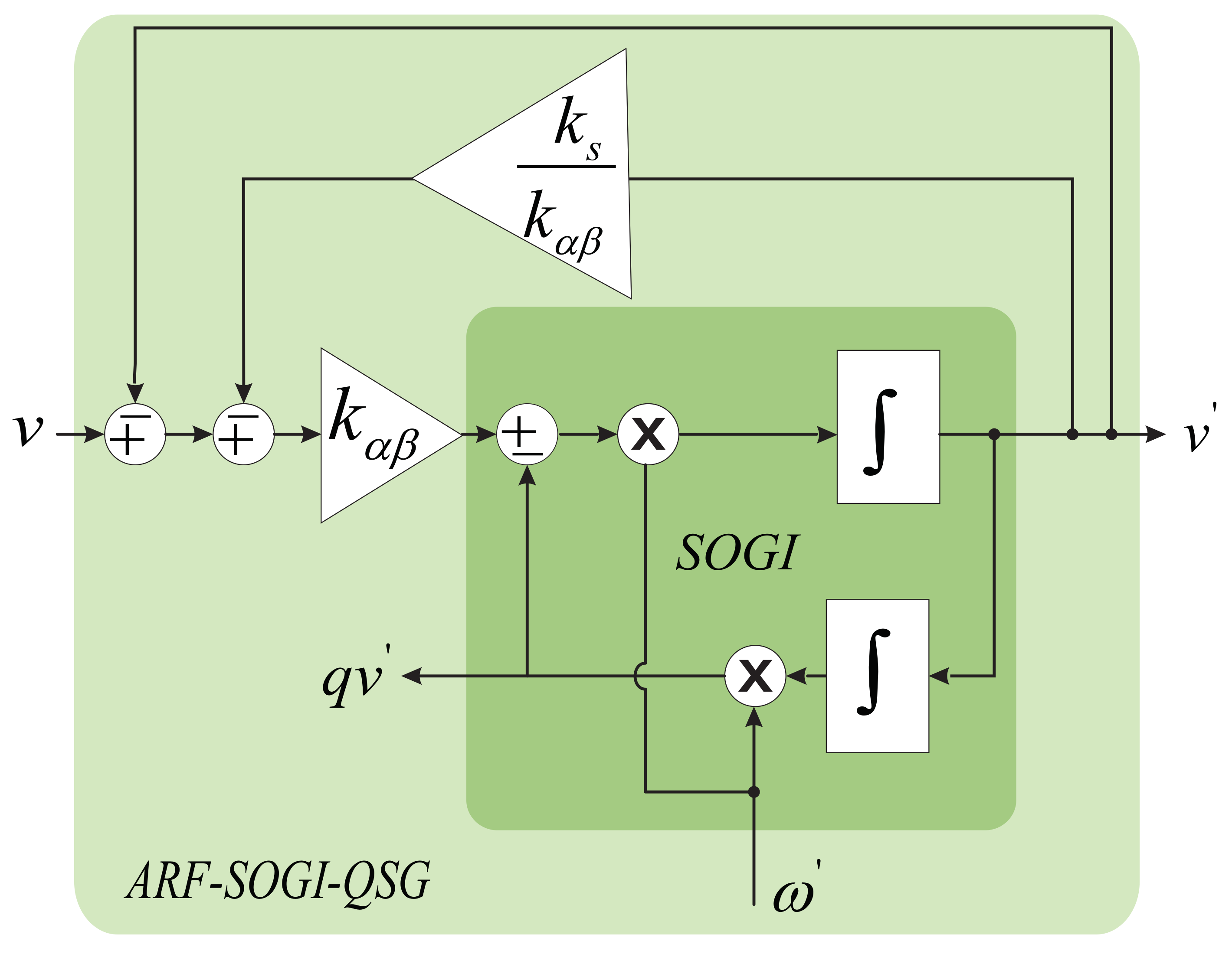

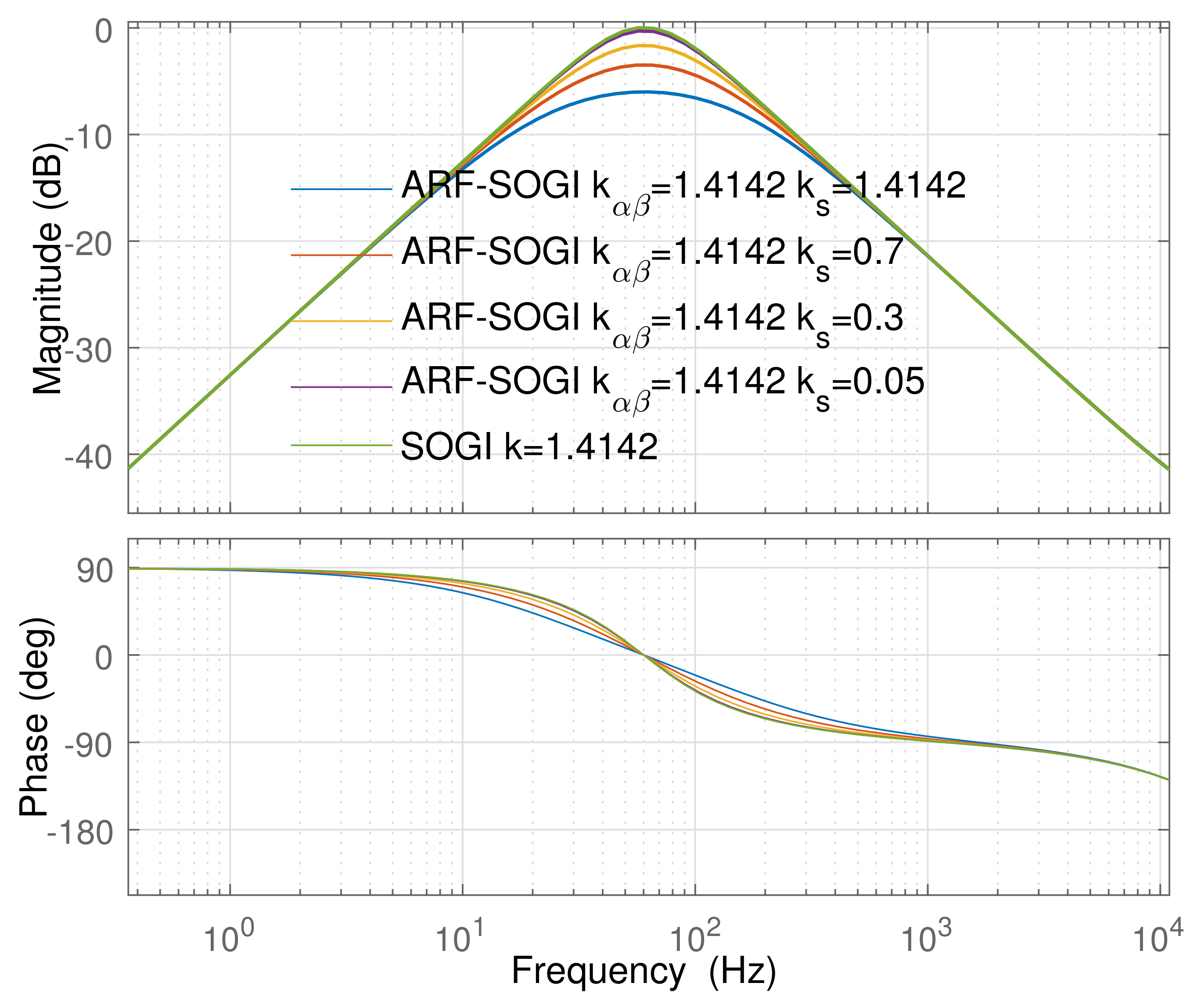

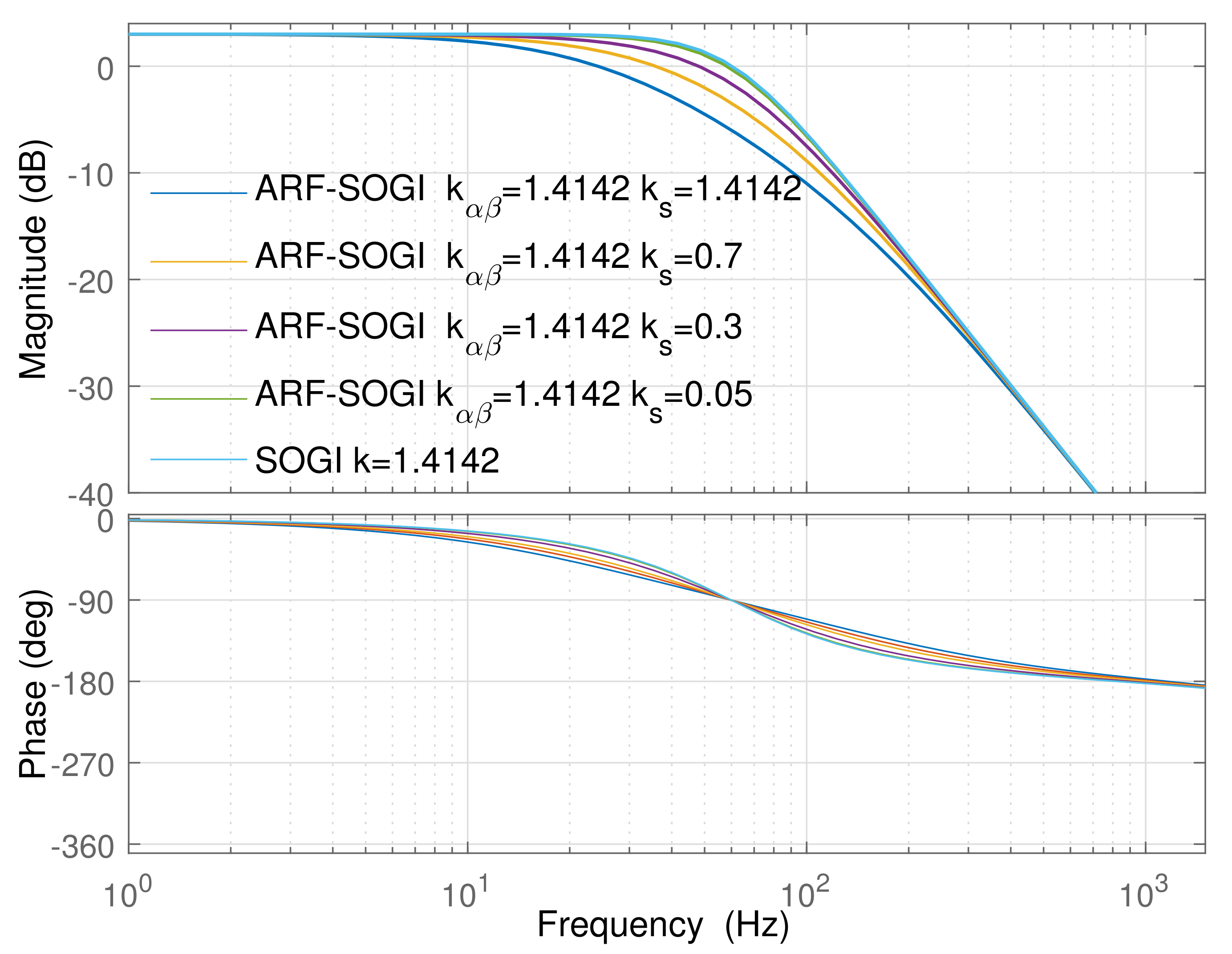

- If , the attenuation suffered by the 30 Hz and 120 Hz signals is approximately 3.9 dB; this is an advantage over the traditional SOGI, but the cost is an attenuation of approximately 6 dB in the fundamental frequency signal. However, adjustment of the gain corrects this attenuation, as discussed in Section 3.5;

- The smaller the value of , the closer the ARF-SOGI-QSG is to the traditional SOGI-QSG;

- The greater the , the greater the attenuation suffered by the fundamental frequency of the voltage signal.

2.3. ARF-SOGI-QSG Transfer Functions

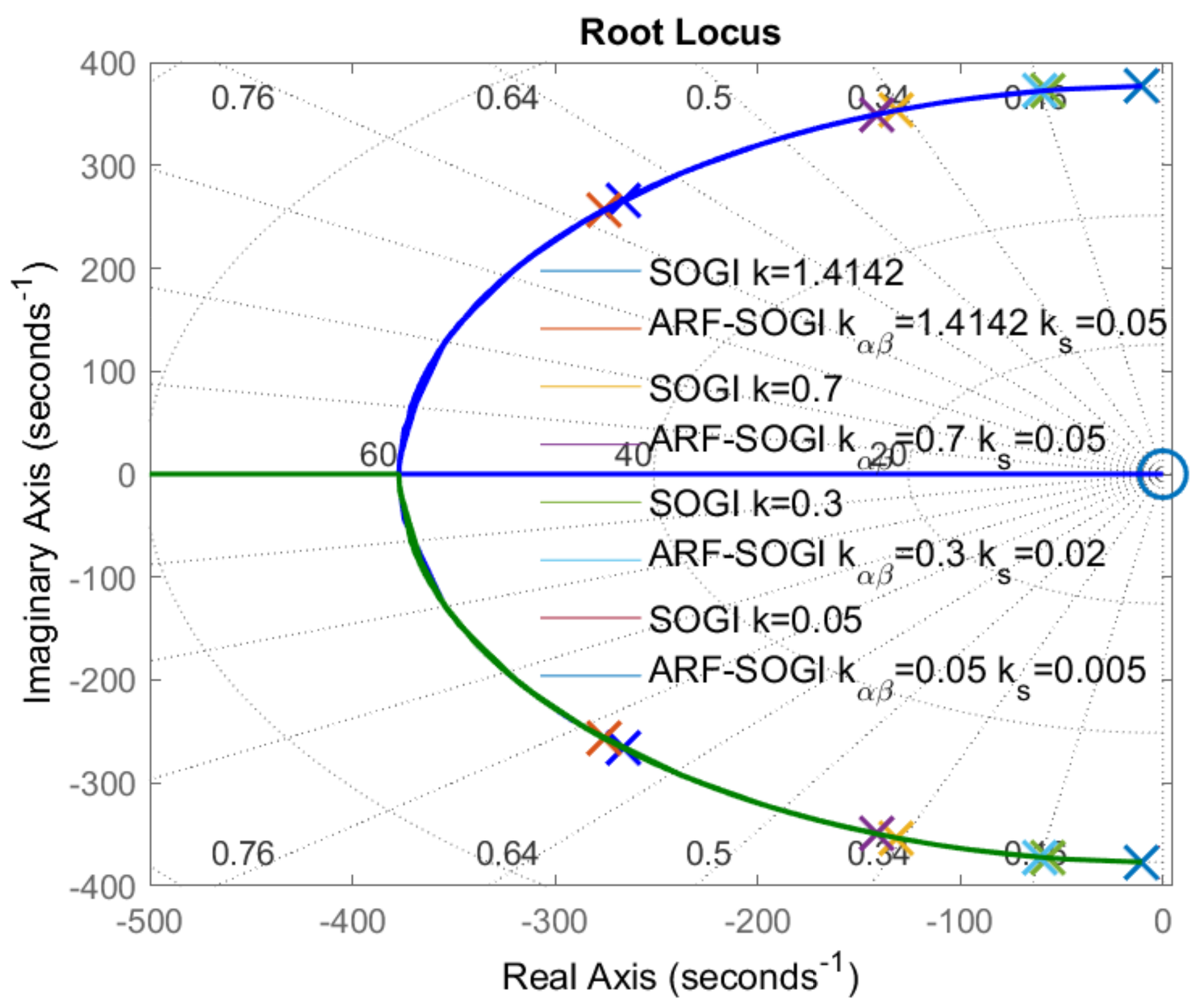

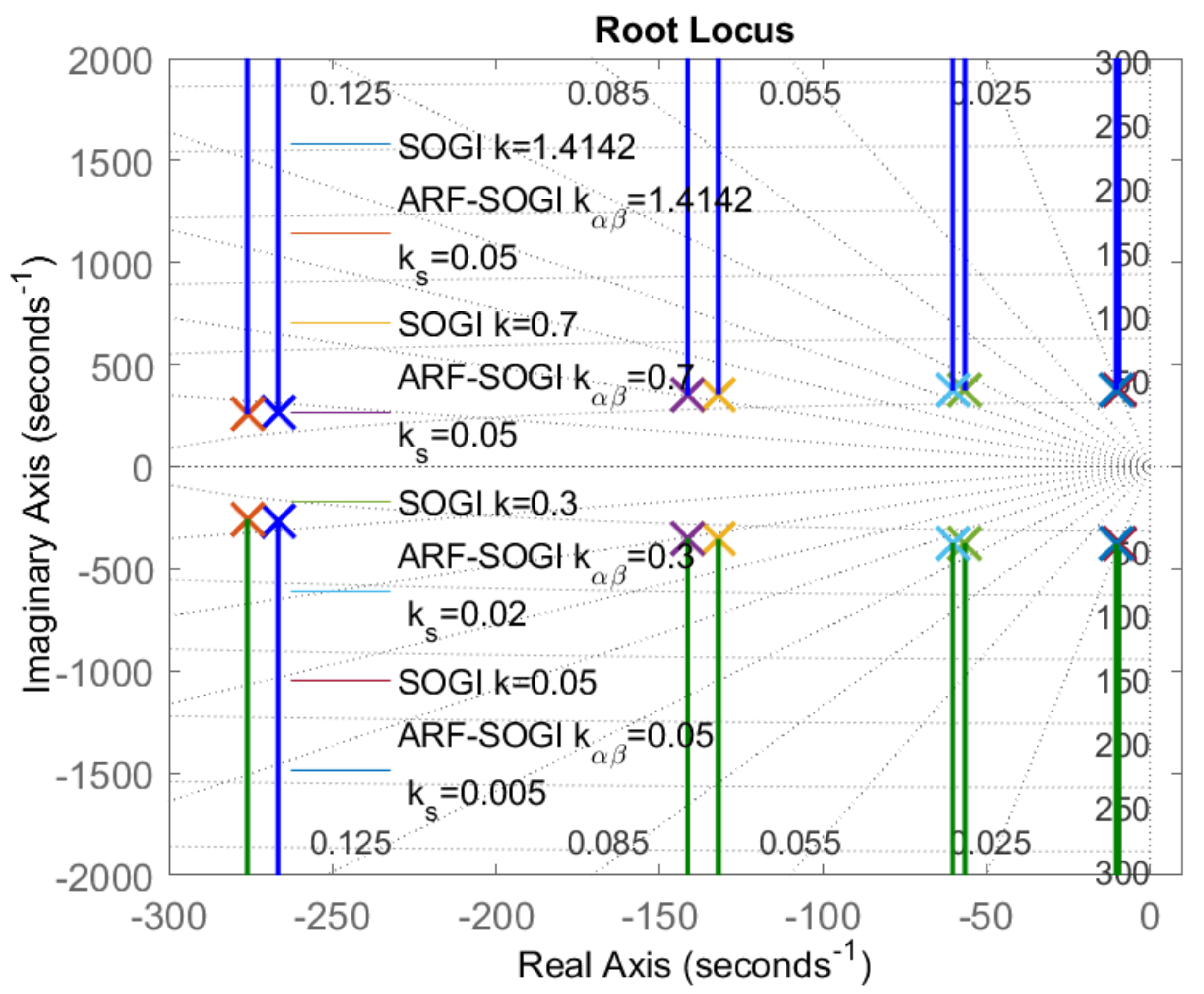

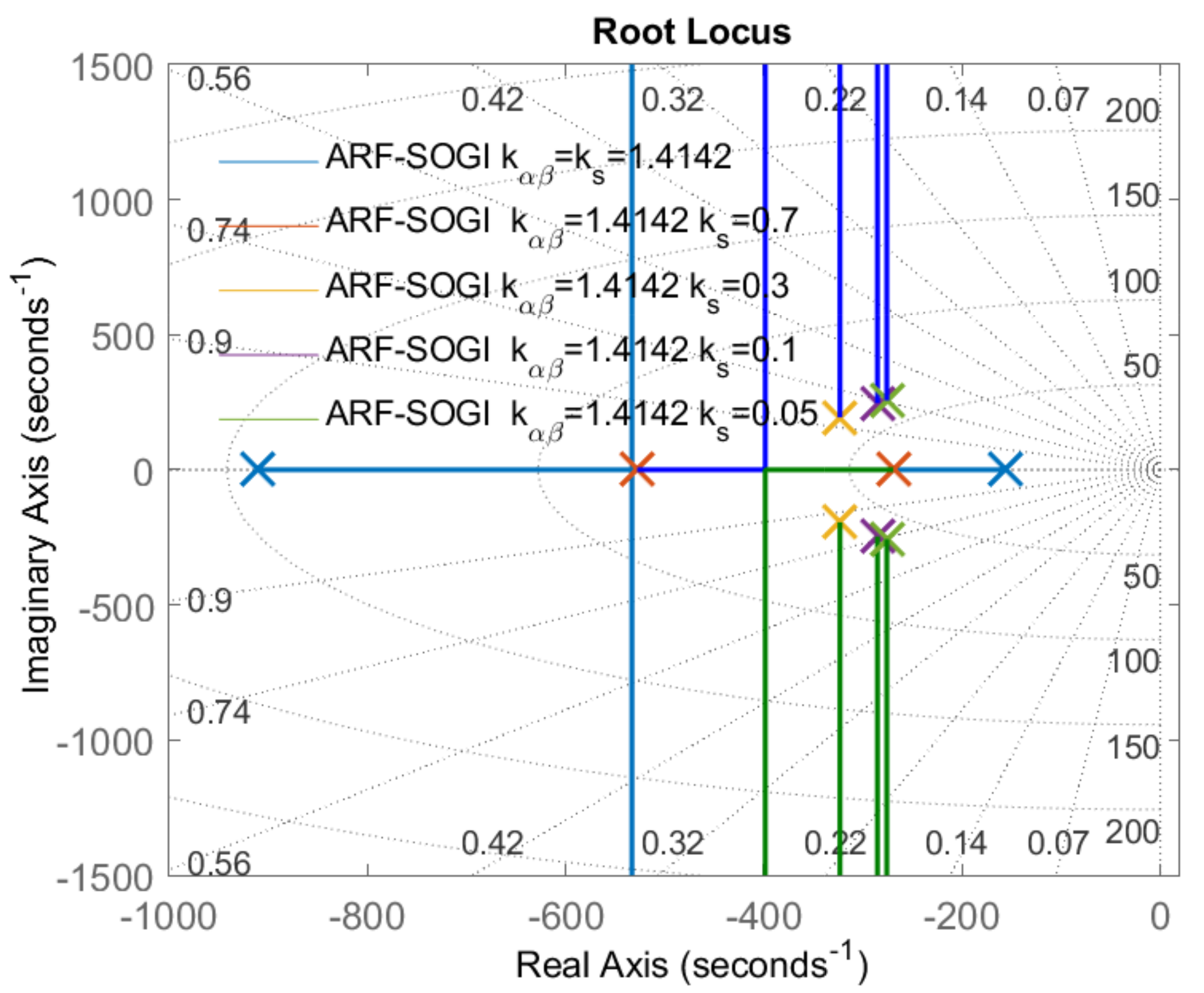

2.4. Comparative Analysis of SOGI-QSG and ARF-SOGI-QSG

2.5. The ARF-SOGI-PLL

- The modified SOGI-QSG block (ARF-SOGI-QSG);

- The gain, which compensates for the extra attenuation caused by the ARF-SOGI and increases the loop bandwidth of the SRF-PLL embedded in the PLL;

- An SRF-PLL with frequency extraction using an integral controller.

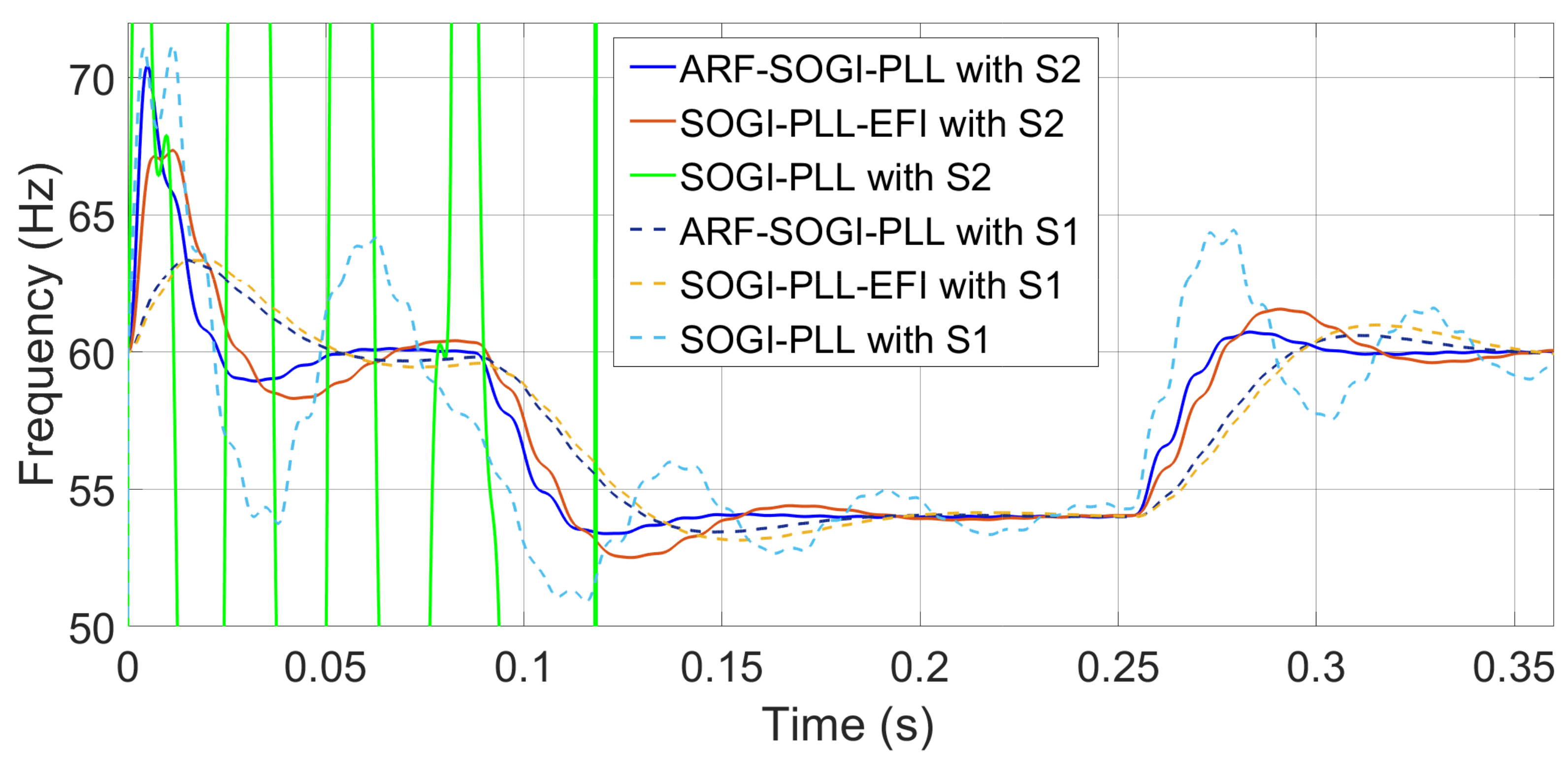

- Frequency deviations of −6 Hz and −14 Hz;

- Harmonic content: 0.04 pu of the fifth harmonic and 0.0295 pu of the seventh harmonic, for a THD = ;

- Phase jump of ;

- Voltage sag of ;

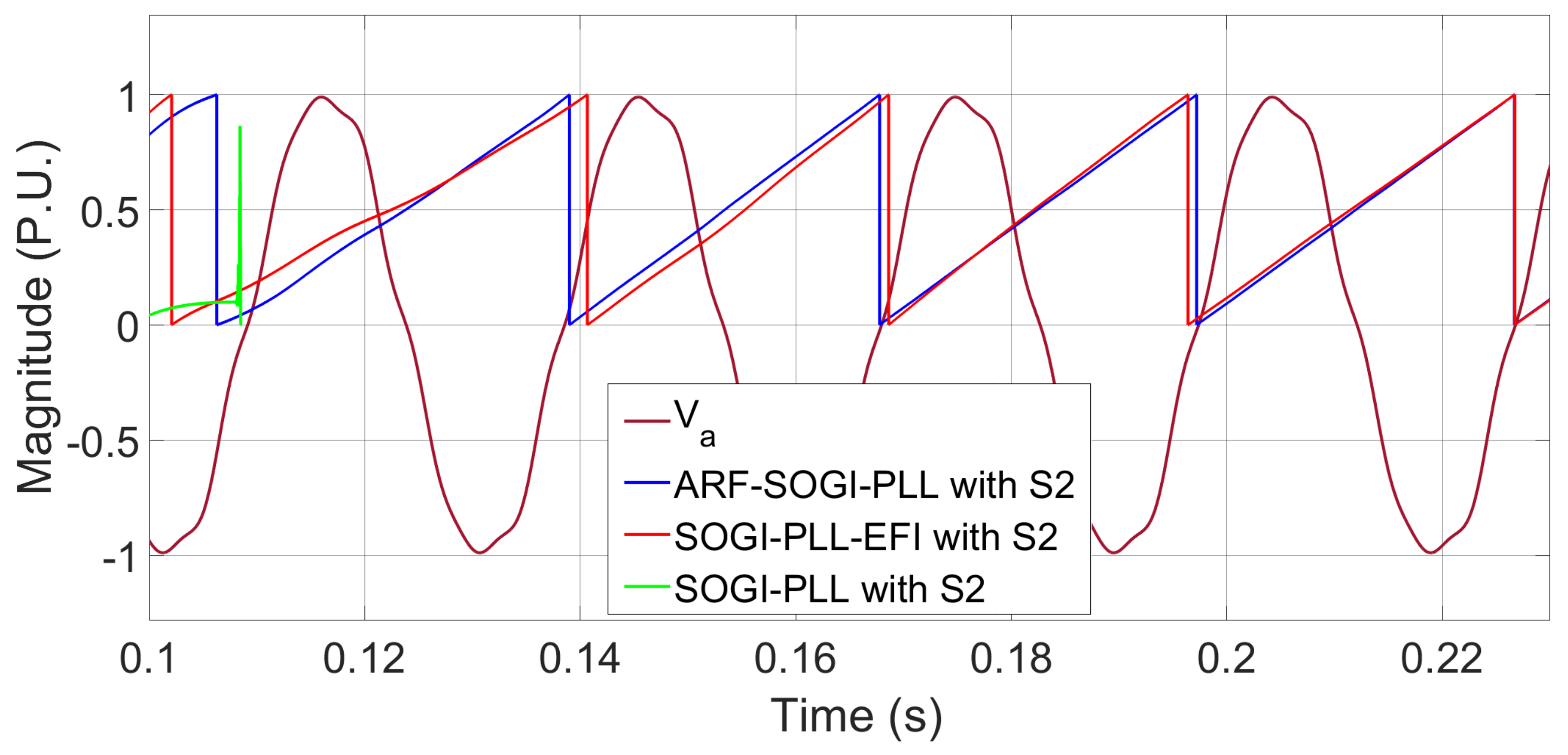

- Phase-to-ground short-circuit;

- Gain , to reduce the bandwidth of the SOGIs and better deal with the harmonic content.

3. Results

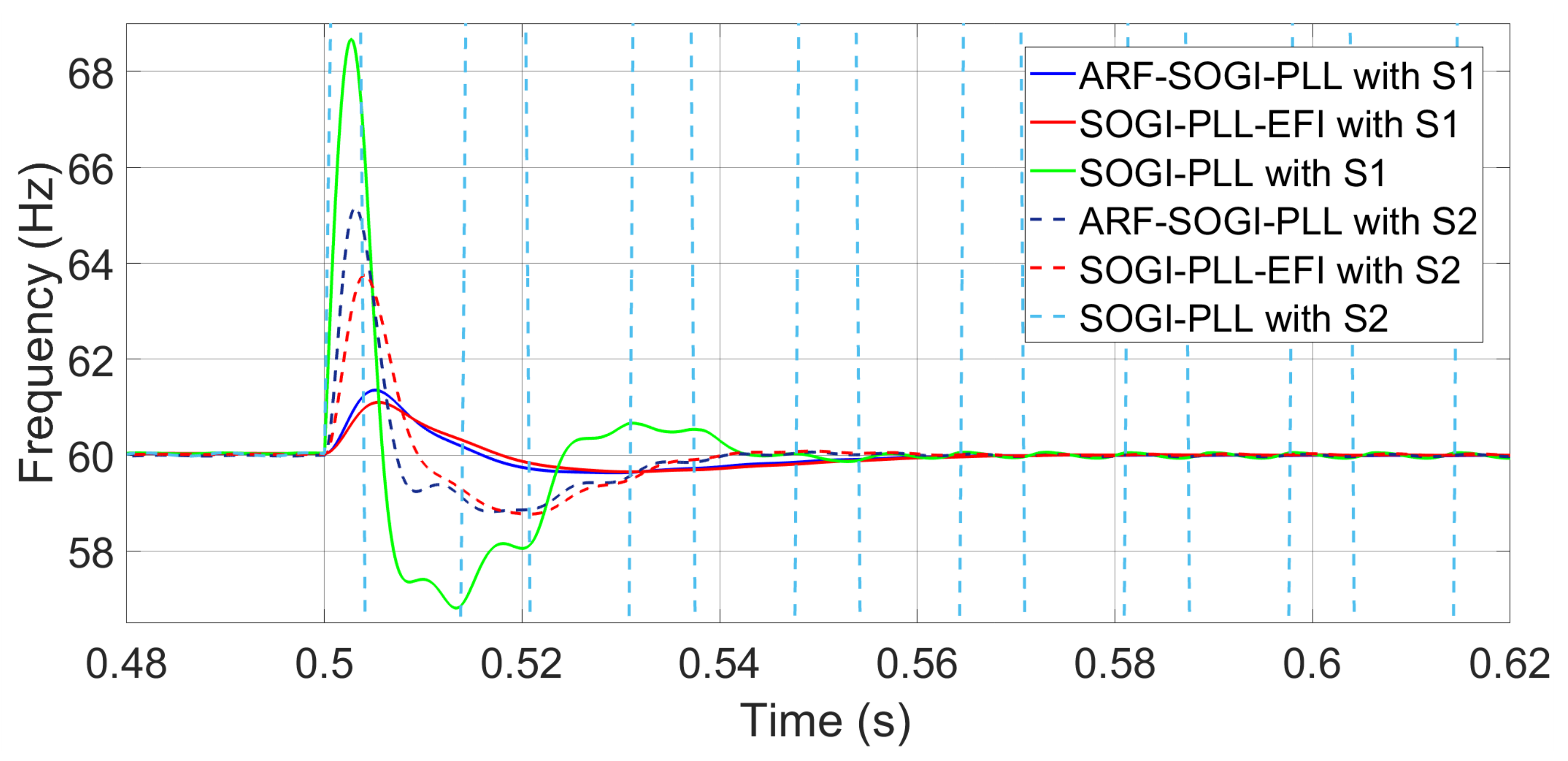

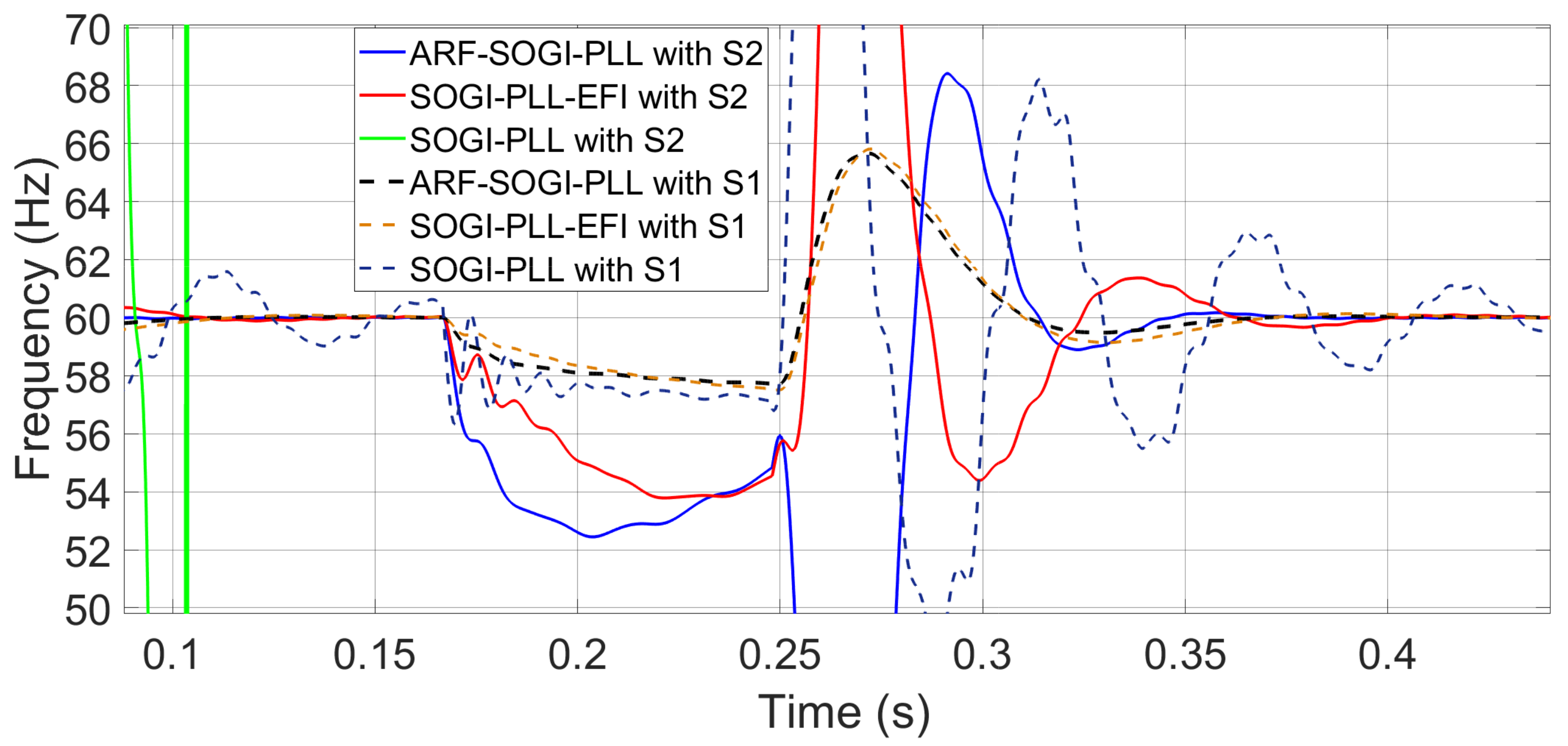

3.1. Response to Frequency Deviation

3.2. Response to Voltage Sag

3.3. Response to Ground Fault

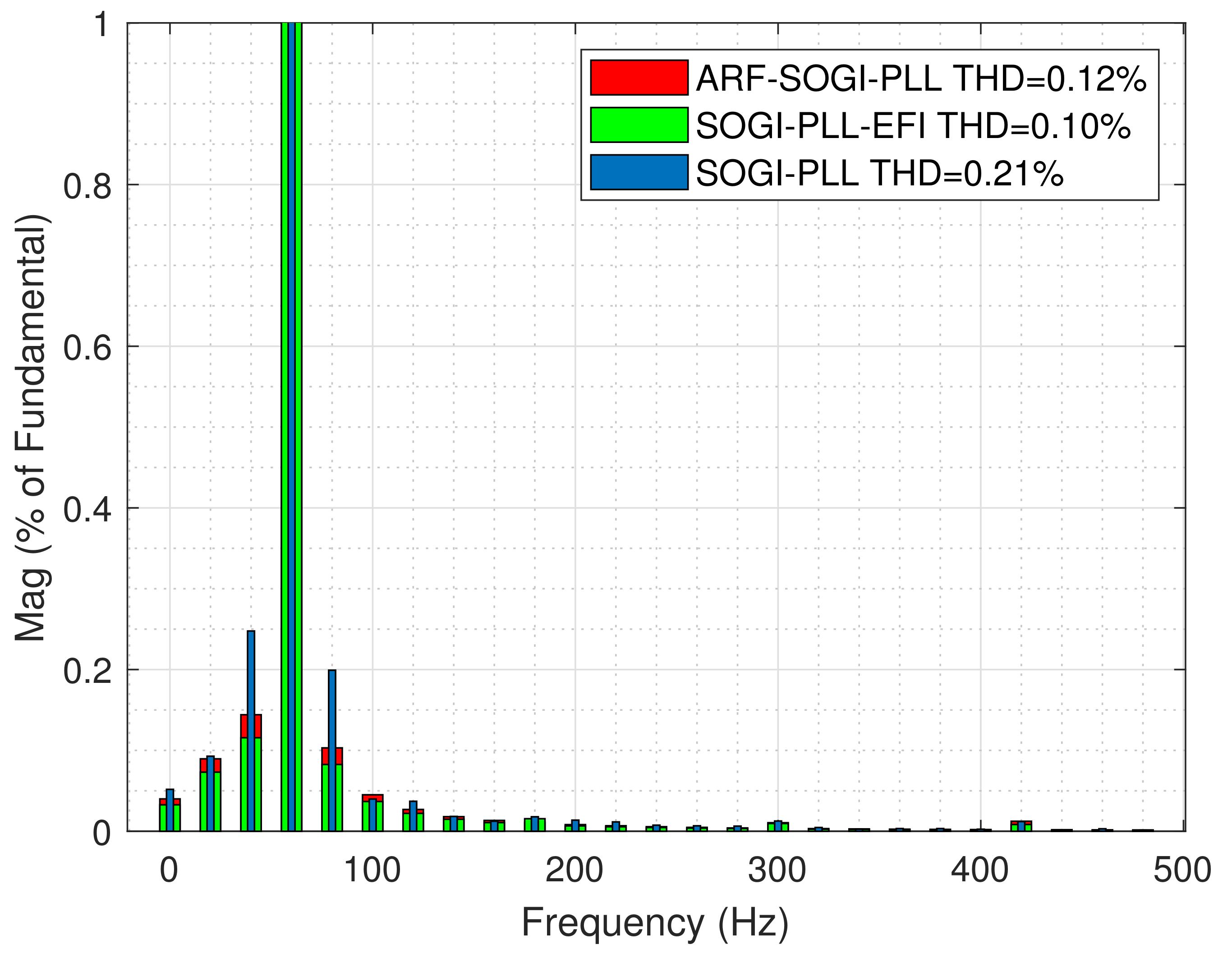

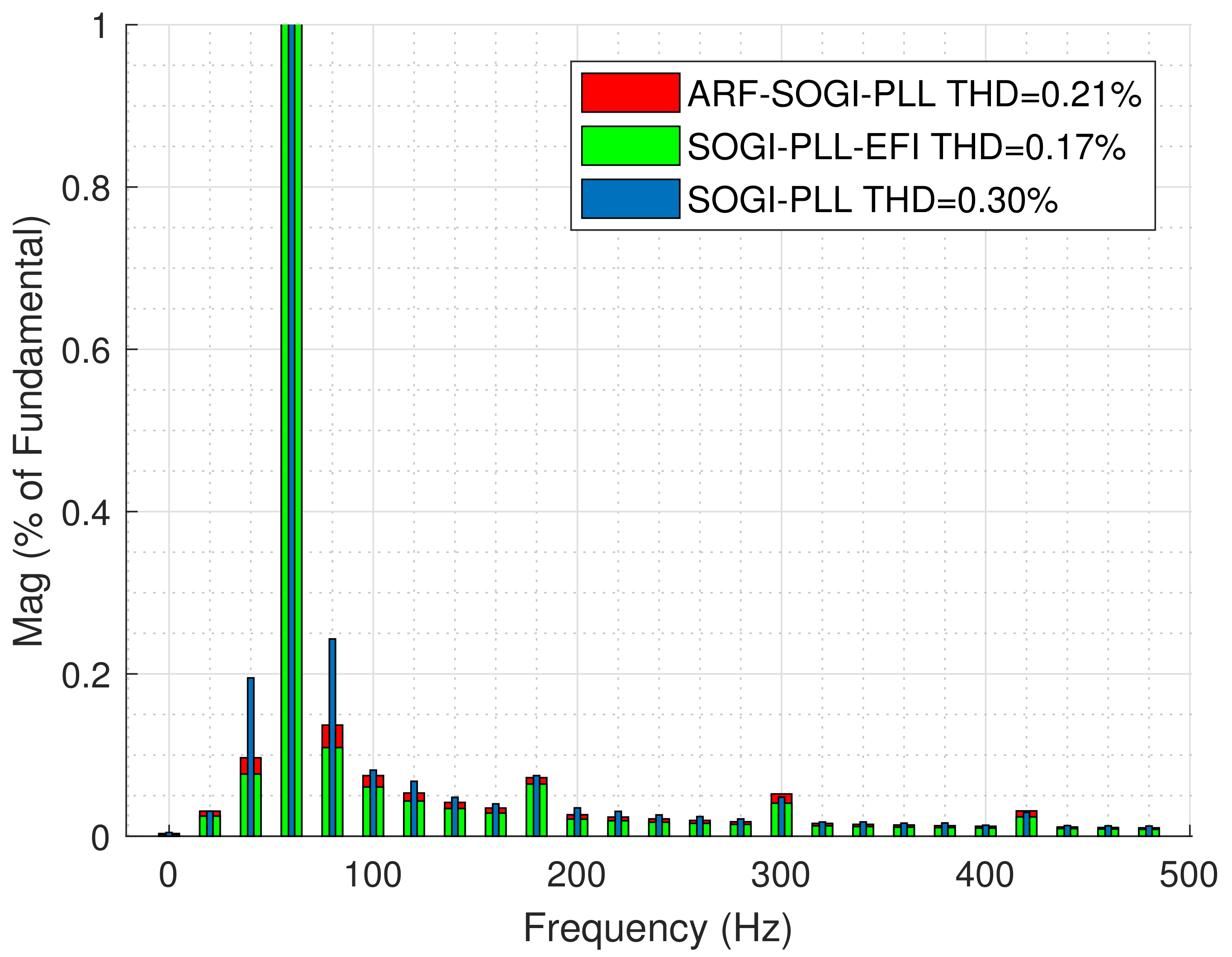

3.4. Harmonic Content Rejection Capability of Large Bandwidth SOGI Versions

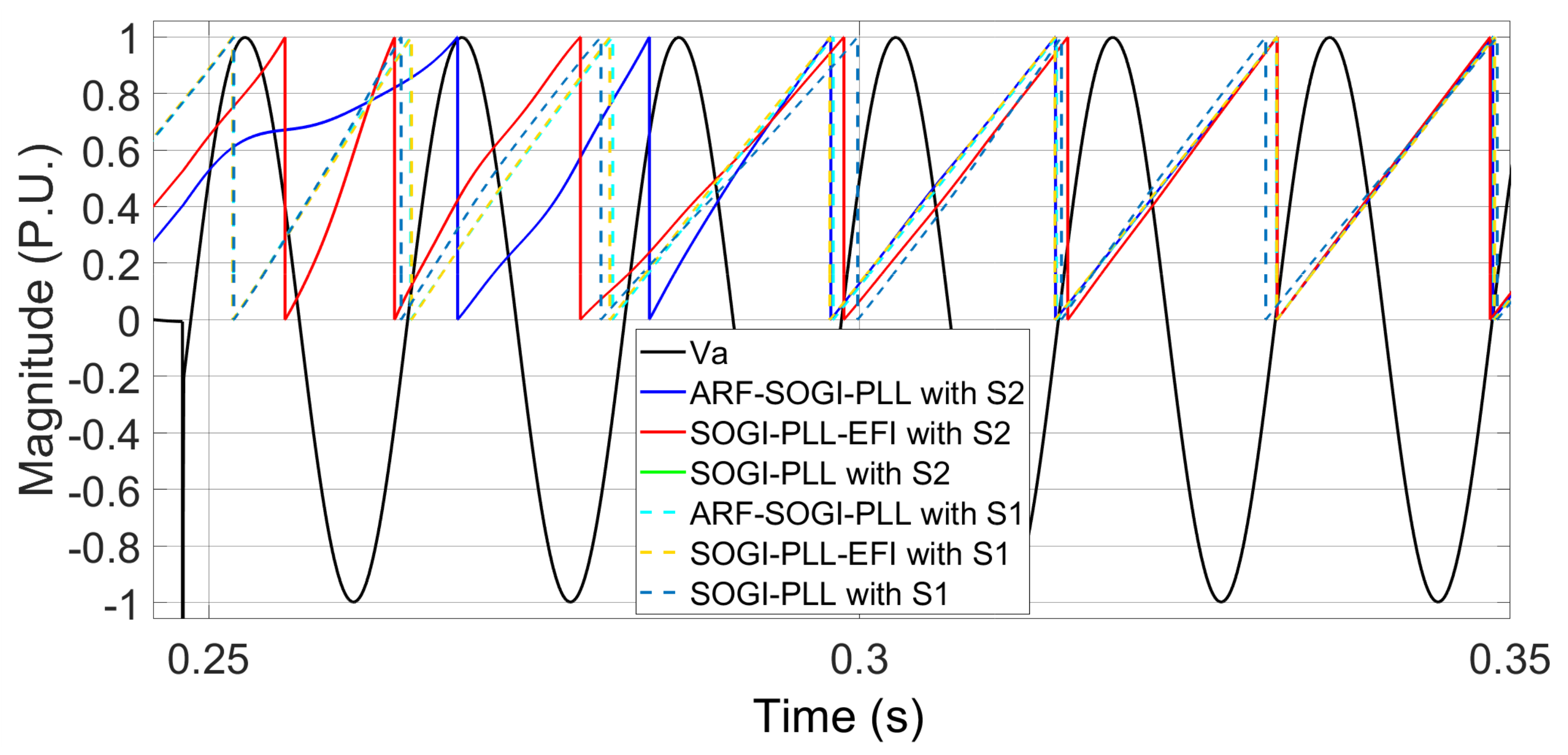

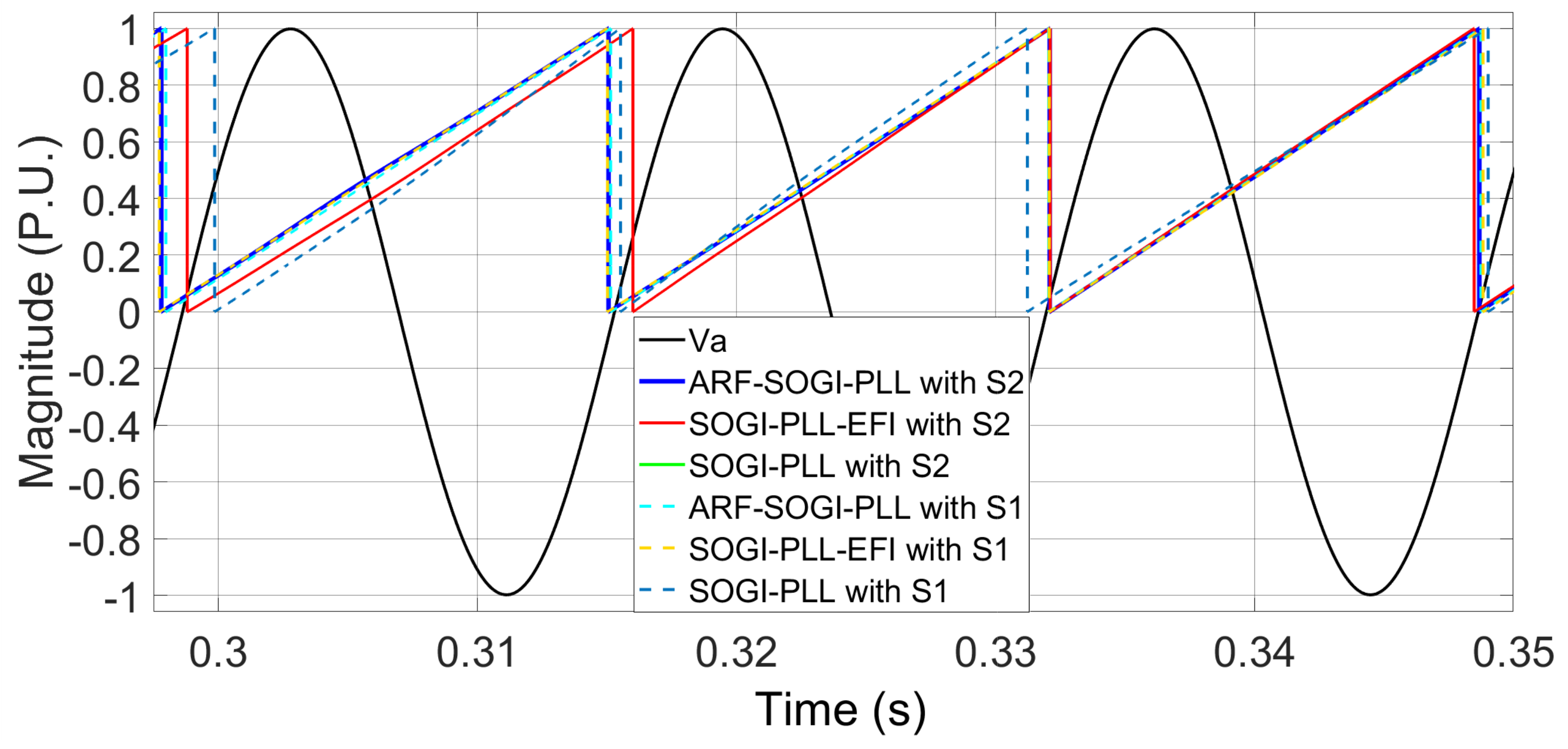

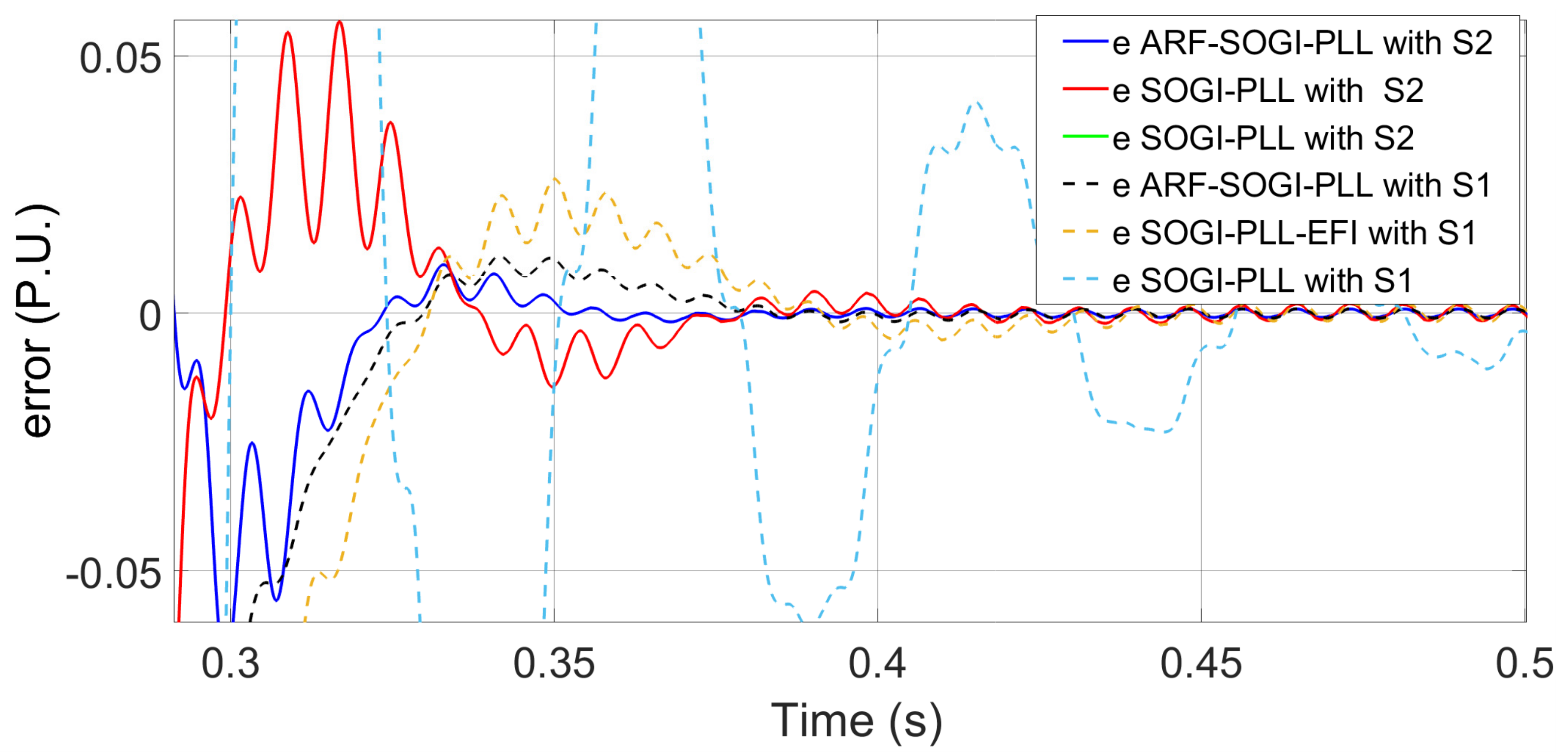

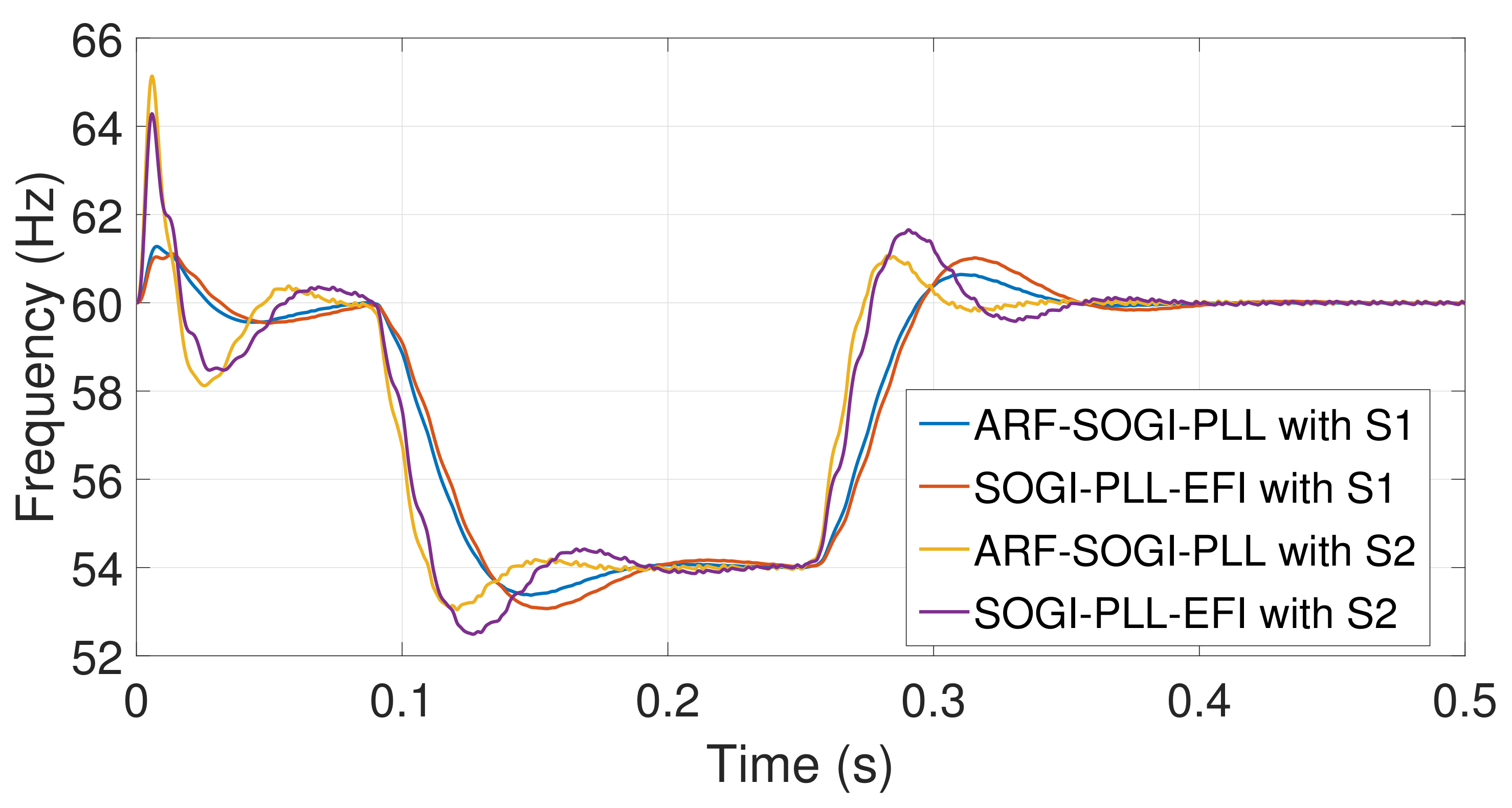

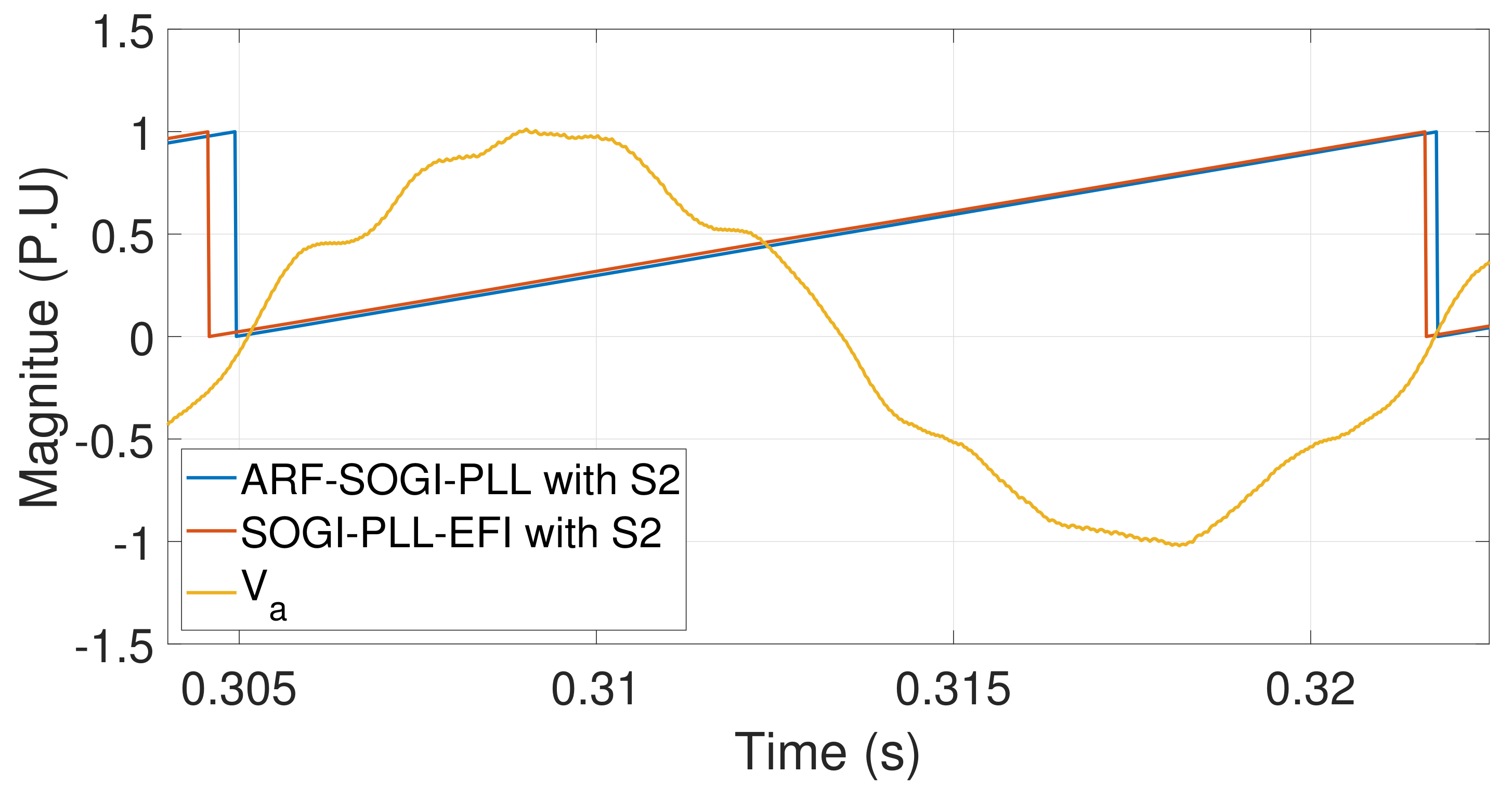

3.5. Synchronization of a Single-Phase Inverter

3.6. Resources and Computing Times

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| ARF | Adjustable re-filtering |

| DG | Distributed generation |

| EPS | Electrical power system |

| PLL | Phase-locked loop |

| QSG | Quadrature signal generator |

| SOGI | Second-order generalized integrator |

| THD | Total harmonic distortion |

References

- Best, R.E. Phase-Locked Loops: Design, Simulation, and Applications, 5th ed.; McGraw-Hill: New York, NY, USA, 2003. [Google Scholar]

- Timbus, A.; Liserre, M.; Teodorescu, R.; Blaabjerg, F. Synchronization methods for three phase distributed power generation systems—An overview and evaluation. In Proceedings of the 2005 IEEE 36th Power Electronics Specialists Conference, Recife, Brazil, 16 June 2005; pp. 2474–2481. [Google Scholar]

- Best, R.E. Phase-Locked Loops: Design, Simulation, and Applications, 6th ed.; McGraw-Hill Education: New York, NY, USA, 2007. [Google Scholar]

- Yazdani, A.; Iravani, R. Voltage-Sourced Converters in Power Systems: Modeling, Control, and Applications; John Wiley & Sons: Hoboken, NJ, USA, 2010. [Google Scholar]

- Golestan, S.; Guerrero, J.M.; Vasquez, J.C. Three-Phase PLLs: A Review of Recent Advances. IEEE Trans. Power Electron. 2017, 32, 1894–1907. [Google Scholar] [CrossRef] [Green Version]

- Rodríguez, P.; Teodorescu, R.; Candela, I.; Timbus, A.V.; Liserre, M.; Blaabjerg, F. New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–7. [Google Scholar] [CrossRef]

- Chung, S.K. Phase-locked loop for grid-connected three-phase power conversion systems. IEE Proc.-Electr. Power Appl. 2000, 147, 213–219. [Google Scholar] [CrossRef]

- Gao, S.; Barnes, M. Phase-locked loop for AC systems: Analyses and comparisons. In Proceedings of the 6th IET International Conference on Power Electronics, Machines and Drives (PEMD 2012), Bristol, UK, 27–29 March 2012; pp. 1–6. [Google Scholar] [CrossRef] [Green Version]

- Mahdian, H.; Hashemi, M.; Ghadimi, A.A. Improvement in the synchronization process of the voltage-sourced converters connected to the Grid by PLL in order to Detect and Block the Double Frequency Disturbance Term. Indian J. Sci. Technol. 2013, 6, 4940–4952. [Google Scholar] [CrossRef]

- Jauch, C.; Matevosyan, J.; Ackermann, T.; Bolik, S. International comparison of requirements for connection of wind turbines to power systems. Wind Energy 2005, 8, 295–306. [Google Scholar] [CrossRef]

- Rodriguez, P.; Luna, A.; Ciobotaru, M.; Teodorescu, R.; Blaabjerg, F. Advanced Grid Synchronization System for Power Converters under Unbalanced and Distorted Operating Conditions. In Proceedings of the IECON 2006—32nd Annual Conference on IEEE Industrial Electronics, Paris, France, 7–10 November 2006; pp. 5173–5178. [Google Scholar] [CrossRef]

- Teodorescu, R.; Liserre, M.; Rodriguez, P. Grid Converters for Photovoltaic and Wind Power Systems; John Wiley & Sons: New Delhi, India, 2011. [Google Scholar]

- Karimi Ghartemani, M.; Khajehoddin, S.A.; Jain, P.K.; Bakhshai, A. Problems of Startup and Phase Jumps in PLL Systems. IEEE Trans. Power Electron. 2012, 27, 1830–1838. [Google Scholar] [CrossRef]

- Abdali Nejad, S.; Matas, J.; Martín, H.; de la Hoz, J.; Al-Turki, Y.A. New SOGI-FLL Grid Frequency Monitoring with a Finite State Machine Approach for Better Response in the Face of Voltage Sag and Swell Faults. Electronics 2020, 9, 612. [Google Scholar] [CrossRef] [Green Version]

- Abdali Nejad, S.; Matas, J.; Elmariachet, J.; Martín, H.; de la Hoz, J. SOGI-FLL Grid Frequency Monitoring with an Error-Based Algorithm for a Better Response in Face of Voltage Sag and Swell Faults. Electronics 2021, 10, 1414. [Google Scholar] [CrossRef]

- Bollen, M.H. Understanding power quality problems. In Voltage Sags and Interruptions; IEEE Press: Piscataway, NJ, USA, 2000. [Google Scholar]

- Rodríguez, P.; Luna, A.; Muñoz-Aguilar, R.S.; Etxeberria-Otadui, I.; Teodorescu, R.; Blaabjerg, F. A Stationary Reference Frame Grid Synchronization System for Three-Phase Grid-Connected Power Converters Under Adverse Grid Conditions. IEEE Trans. Power Electron. 2012, 27, 99–112. [Google Scholar] [CrossRef]

- Velasco, J.A.M. Power System Transients: Parameter Determination; CRC Press: London, UK, 2010. [Google Scholar]

- Green, T.; Marks, J. Control techniques for active power filters. IEE Proc.-Electr. Power Appl. 2005, 152, 369–381. [Google Scholar] [CrossRef] [Green Version]

- Subramanian, C.; Kanagaraj, R. Rapid Tracking of Grid Variables Using Prefiltered Synchronous Reference Frame PLL. IEEE Trans. Instrum. Meas. 2015, 64, 1826–1836. [Google Scholar] [CrossRef]

- Chung, S.K. A phase tracking system for three phase utility interface inverters. IEEE Trans. Power Electron. 2000, 15, 431–438. [Google Scholar] [CrossRef] [Green Version]

- Arricibita, D.; Marroyo, L.; Barrios, E.L. Simple and robust PLL algorithm for accurate phase tracking under grid disturbances. In Proceedings of the 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, USA, 9–12 July 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Nos, O.V.; Abramushkina, E.E.; Kharitonov, S.A. Control Design of Fast Response PLL for FACTS Applications. In Proceedings of the 2019 International Ural Conference on Electrical Power Engineering (UralCon), Chelyabinsk, Russia, 1–3 October 2019; pp. 301–305. [Google Scholar] [CrossRef]

- Luhtala, R.; Alenius, H.; Roinila, T. Practical Implementation of Adaptive SRF-PLL for Three-Phase Inverters Based on Sensitivity Function and Real-Time Grid-Impedance Measurements. Energies 2020, 13, 1173. [Google Scholar] [CrossRef] [Green Version]

- Golestan, S.; Ramezani, M.; Guerrero, J.M. An Analysis of the PLLs With Secondary Control Path. IEEE Trans. Ind. Electron. 2014, 61, 4824–4828. [Google Scholar] [CrossRef] [Green Version]

- Cao, Y.; Yu, J.; Xu, Y.; Li, Y.; Yu, J. An Efficient Phase-Locked Loop for Distorted Three-Phase Systems. Energies 2017, 10, 280. [Google Scholar] [CrossRef] [Green Version]

- Aldbaiat, B.; Nour, M.; Radwan, E.; Awada, E. Grid-Connected PV System with Reactive Power Management and an Optimized SRF-PLL Using Genetic Algorithm. Energies 2022, 15, 2177. [Google Scholar] [CrossRef]

- Ciobotaru, M.; Teodorescu, R.; Blaabjerg, F. A new single-phase PLL structure based on second order generalized integrator. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–6. [Google Scholar] [CrossRef]

- Ciobotaru, M.; Agelidis, V.G.; Teodorescu, R.; Blaabjerg, F. Accurate and Less-Disturbing Active Antiislanding Method Based on PLL for Grid-Connected Converters. IEEE Trans. Power Electron. 2010, 25, 1576–1584. [Google Scholar] [CrossRef]

- Guerrero-Rodríguez, N.; Rey-Boué, A.B.; Bueno, E.; Ortiz, O.; Reyes-Archundia, E. Synchronization algorithms for grid-connected renewable systems: Overview, tests and comparative analysis. Renew. Sustain. Energy Rev. 2017, 75, 629–643. [Google Scholar] [CrossRef]

- IEEE Std 1547a-2020 (Amendment to IEEE Std 1547-2018); IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces—Amendment 1: To Provide More Flexibility for Adoption of Abnormal Operating Performance Category III. IEEE: Piscataway, NJ, USA, 2020; pp. 1–16. [CrossRef]

- IEC61727; Photovoltaic (PV) Systems-Characteristics of the Utility Interface. International Electrotechnical Commission: Geneva, Switzerland, 2004.

- Motahhir, S.; Ghzizal, A.E.; Sebti, S.; Derouich, A. MIL and SIL and PIL tests for MPPT algorithm. Cogent Eng. 2017, 4, 1378475. [Google Scholar] [CrossRef]

- Krishna Srinivasan, M.; Daya John Lionel, F.; Subramaniam, U.; Blaabjerg, F.; Madurai Elavarasan, R.; Shafiullah, G.M.; Khan, I.; Padmanaban, S. Real-Time Processor-in-Loop Investigation of a Modified Non-Linear State Observer Using Sliding Modes for Speed Sensorless Induction Motor Drive in Electric Vehicles. Energies 2020, 13, 4212. [Google Scholar] [CrossRef]

- Golestan, S.; Guerrero, J.M.; Vasquez, J.C. Single-Phase PLLs: A Review of Recent Advances. IEEE Trans. Power Electron. 2017, 32, 9013–9030. [Google Scholar] [CrossRef]

- Kulkarni, A.; John, V. Analysis of Bandwidth–Unit-Vector-Distortion Tradeoff in PLL During Abnormal Grid Conditions. IEEE Trans. Ind. Electron. 2013, 60, 5820–5829. [Google Scholar] [CrossRef]

| ARF-SOGI | PLL | |||

| 0.5 | 0.5 | 1.4 | 184.7 | 8479.16 |

| SOGI | PLL | |||

| k | ||||

| 0.5 | 184.7 | 8479.16 |

| ARF-SOGI | PLL | |||

| 0.5 | 0.5 | 1.4 | 563.67 | 50,116.247 |

| SOGI | PLL | |||

| k | ||||

| 0.5 | 563.67 | 50,116.247 |

| ARF-SOGI | PLL | |||

| 1.4142 | 0.5 | 1.4 | 184.7 | 8479.16 |

| SOGI | PLL | |||

| k | ||||

| 1.4142 | 184.7 | 8479.16 |

| Algorithm | Flash Memory | Average Execution Time | Maximum Execution Time |

|---|---|---|---|

| SOGI-PLL | 4030 bytes (1%) | 12,861 ns | 14,887 ns |

| SOGI-PLL-EFI | 4013 bytes (1%) | 15,136 ns | 17,187 ns |

| ARF-SOGI-PLL in state space | 4090 bytes (1%) | 13,392 ns | 15,307 ns |

| ARF-SOGI-PLL | 4049 bytes (1%) | 15,451 ns | 17,787 ns |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Herrejón-Pintor, G.A.; Melgoza-Vázquez, E.; Chávez, J.d.J. A Modified SOGI-PLL with Adjustable Refiltering for Improved Stability and Reduced Response Time. Energies 2022, 15, 4253. https://doi.org/10.3390/en15124253

Herrejón-Pintor GA, Melgoza-Vázquez E, Chávez JdJ. A Modified SOGI-PLL with Adjustable Refiltering for Improved Stability and Reduced Response Time. Energies. 2022; 15(12):4253. https://doi.org/10.3390/en15124253

Chicago/Turabian StyleHerrejón-Pintor, Gilberto A., Enrique Melgoza-Vázquez, and Jose de Jesús Chávez. 2022. "A Modified SOGI-PLL with Adjustable Refiltering for Improved Stability and Reduced Response Time" Energies 15, no. 12: 4253. https://doi.org/10.3390/en15124253

APA StyleHerrejón-Pintor, G. A., Melgoza-Vázquez, E., & Chávez, J. d. J. (2022). A Modified SOGI-PLL with Adjustable Refiltering for Improved Stability and Reduced Response Time. Energies, 15(12), 4253. https://doi.org/10.3390/en15124253