A Bimodal Multichannel Battery Pack Equalizer Based on a Quasi-Resonant Two-Transistor Forward Converter

Abstract

1. Introduction

- 1.

- Full-switching-cycle (FSC) equalization, which was verified by simulation and experimental waveforms, was innovatively realized by a quasi-resonant, two-transistor forward converter. This structure can not only limit the forward transformer’s induced EMF without the forward transformer’s magnetic reset coil, but also obtain three balancing channels in each switching cycle.

- 2.

- The bimodal hybrid control strategy was designed to achieve a tradeoff between balancing efficiency and speed, which can select the best operation mode according to the status of battery pack group.

- 3.

- The experimental data of the prototype, which was in good agreement with theoretical and simulation analysis, confirmed the proposed pack equalizer’s ability to prevent pack-level over-discharge.

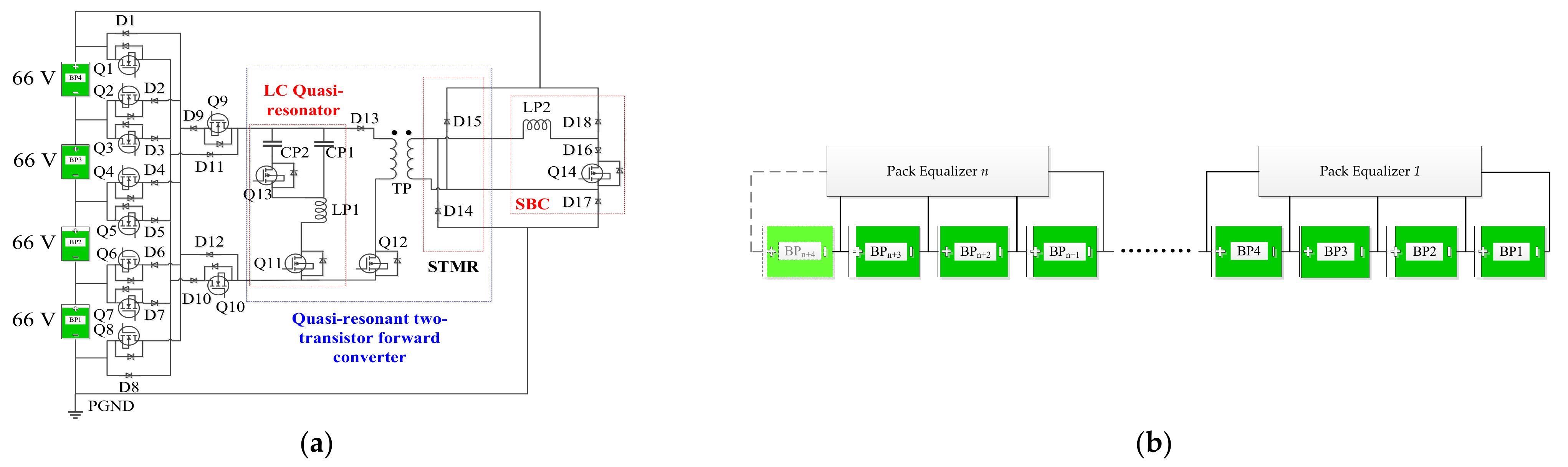

2. Proposed Pack Equalizer

2.1. Pack Equalizer Configuration and Operation Principles

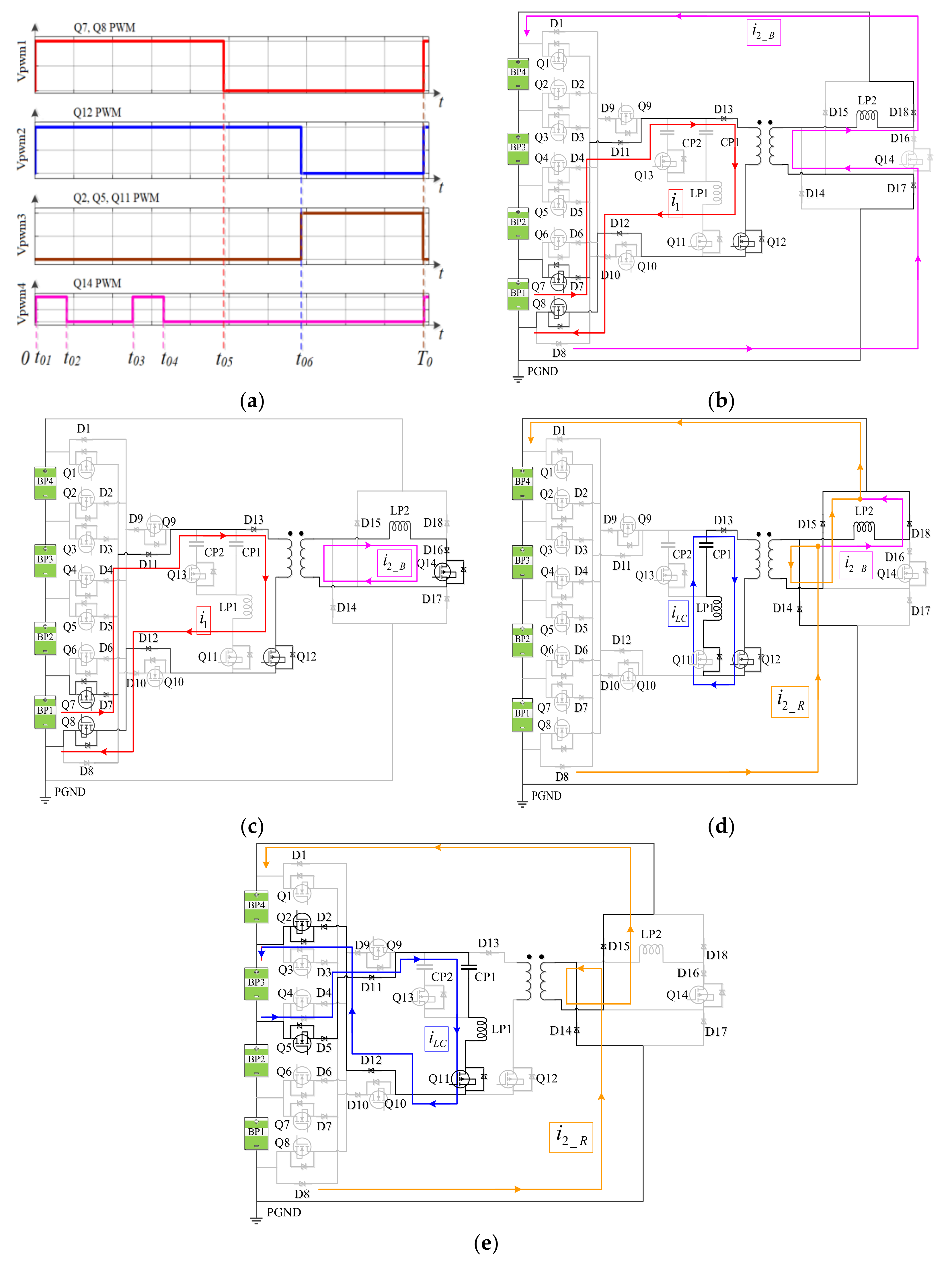

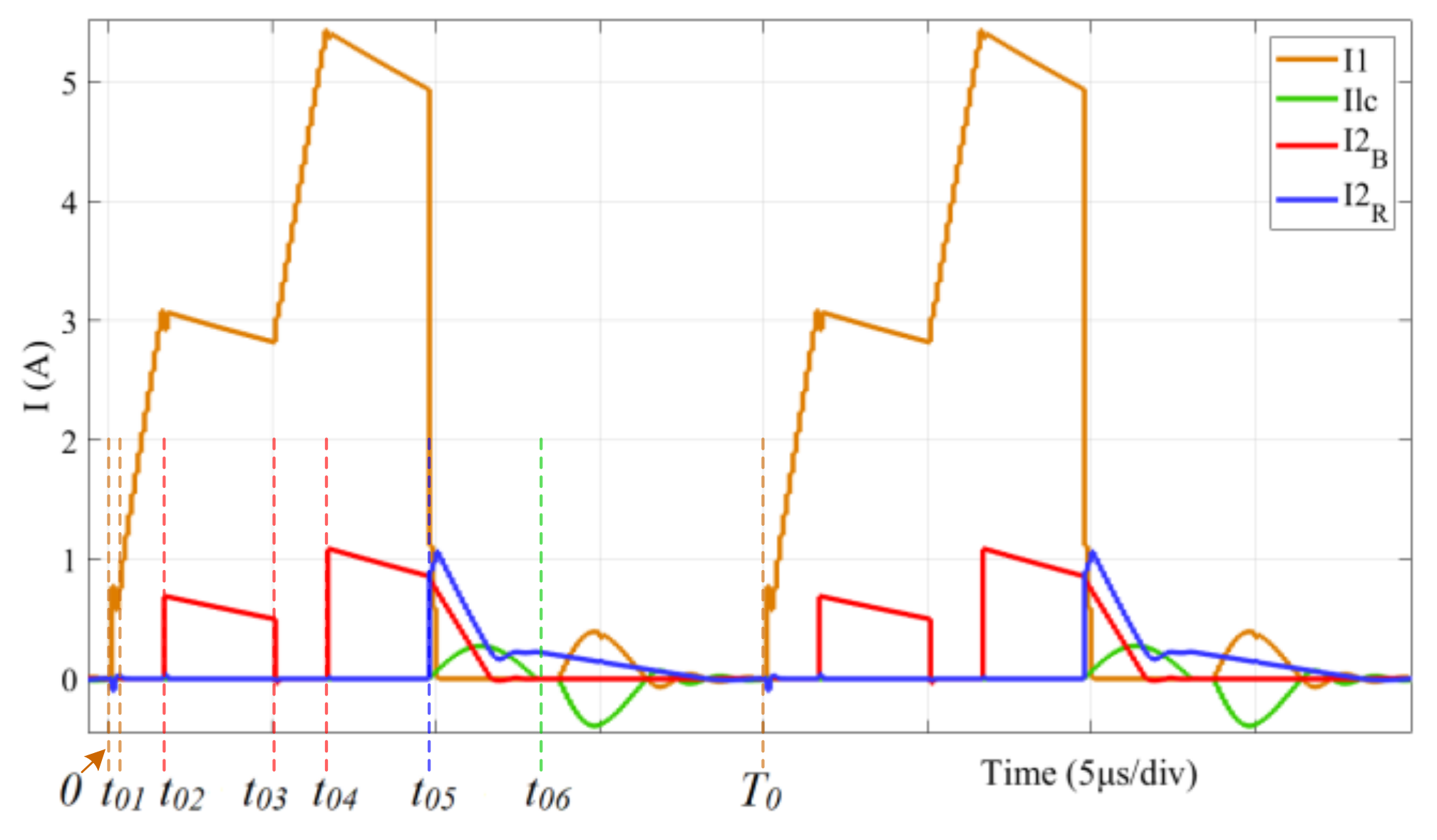

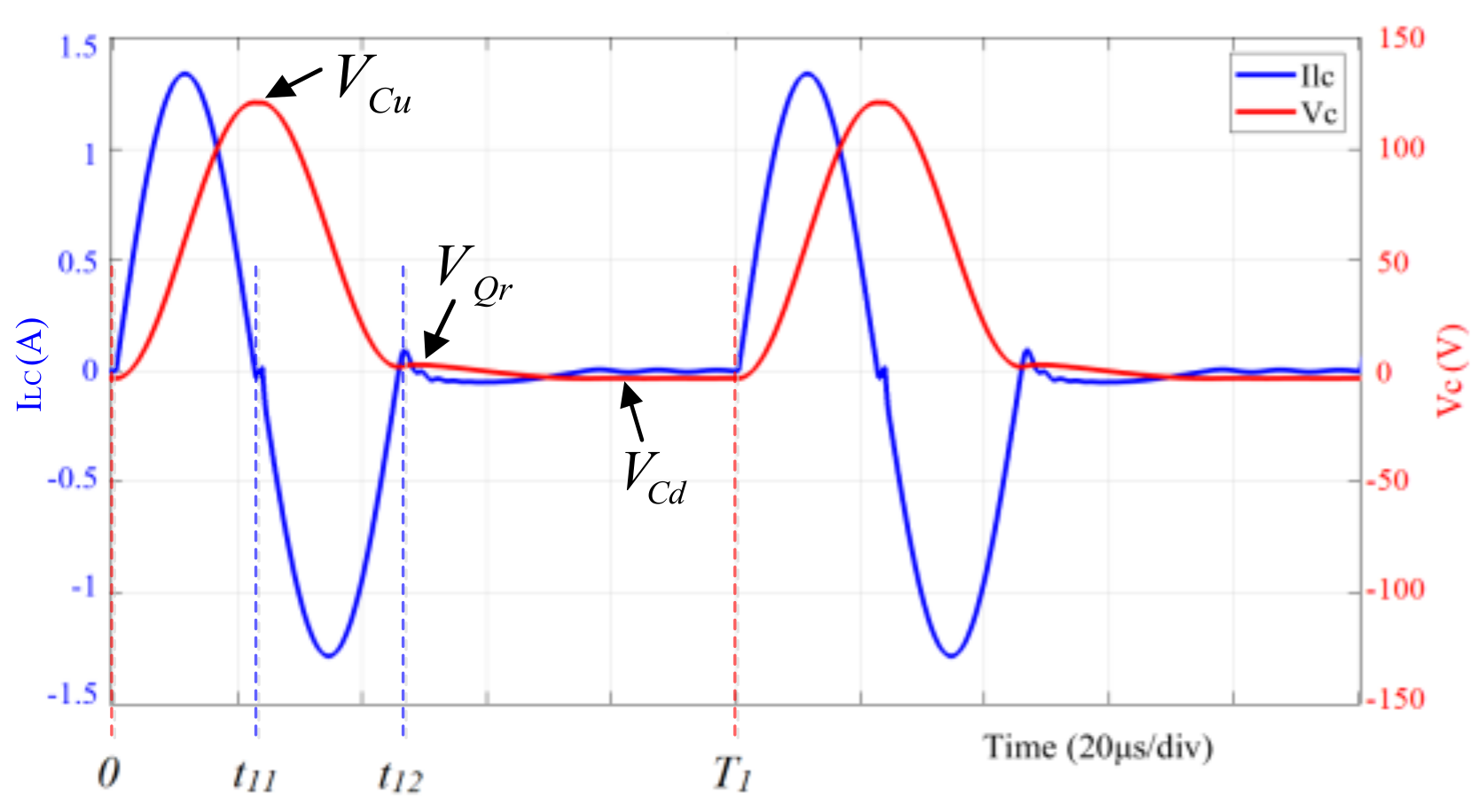

2.2. Operation Principles, Modeling, and Analysis of P2PG&AP Mode

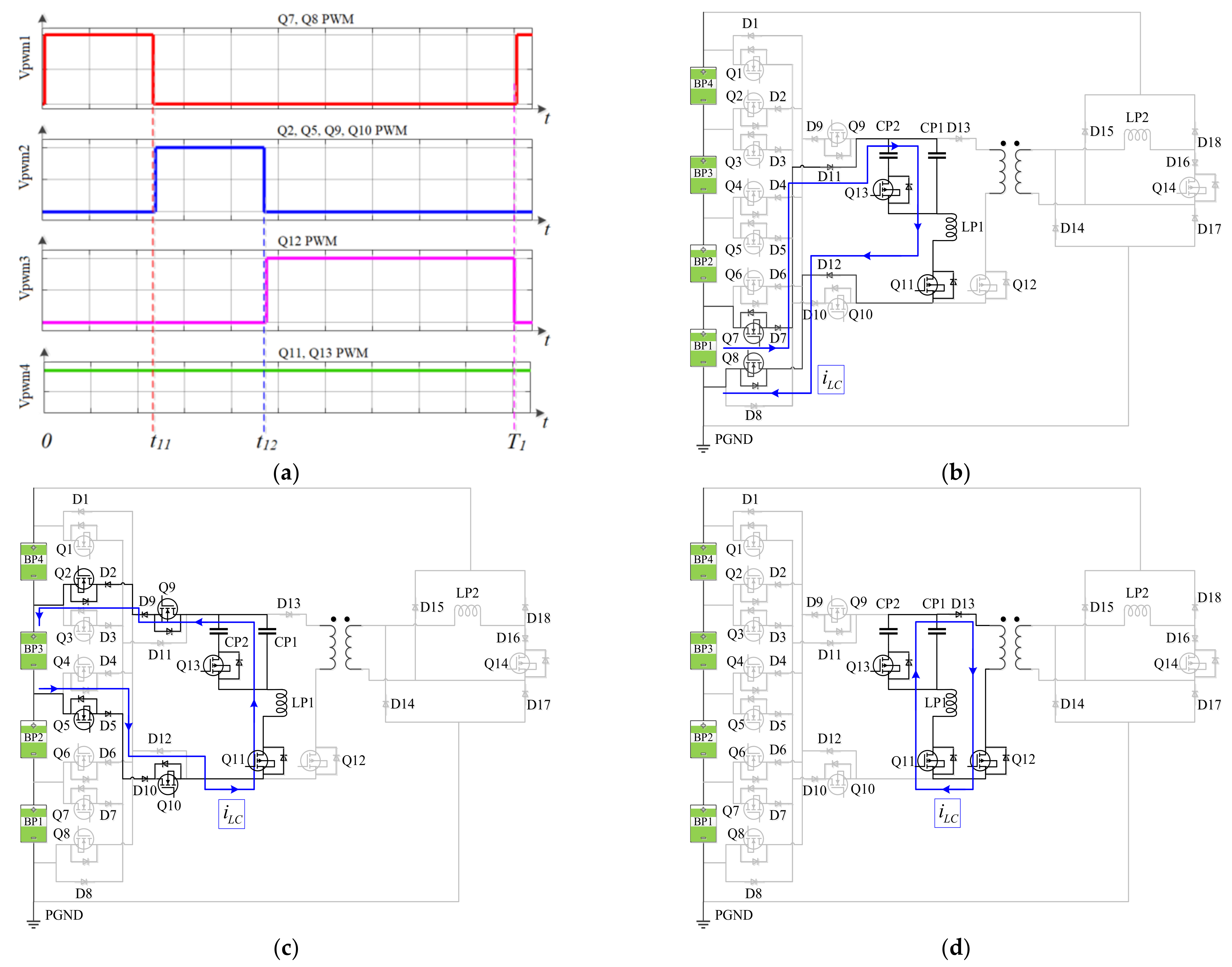

2.3. Operation Principles, Modelling, and Analysis of DP2P Mode

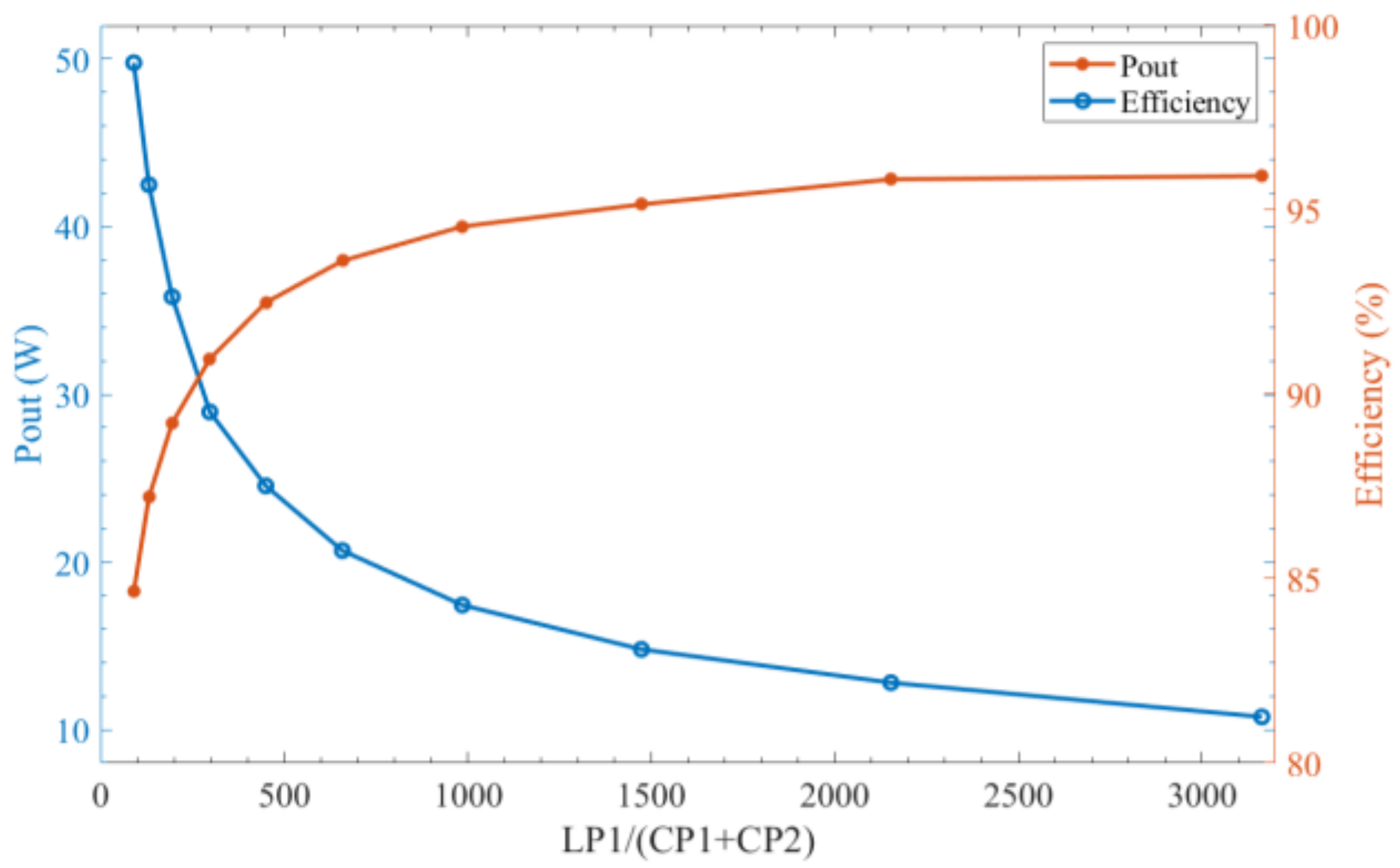

2.4. Equalizer Efficiency and Loss Analysis of P2PG&AP Mode

2.5. Equalizer Efficiency and Loss Analysis of DP2P Mode

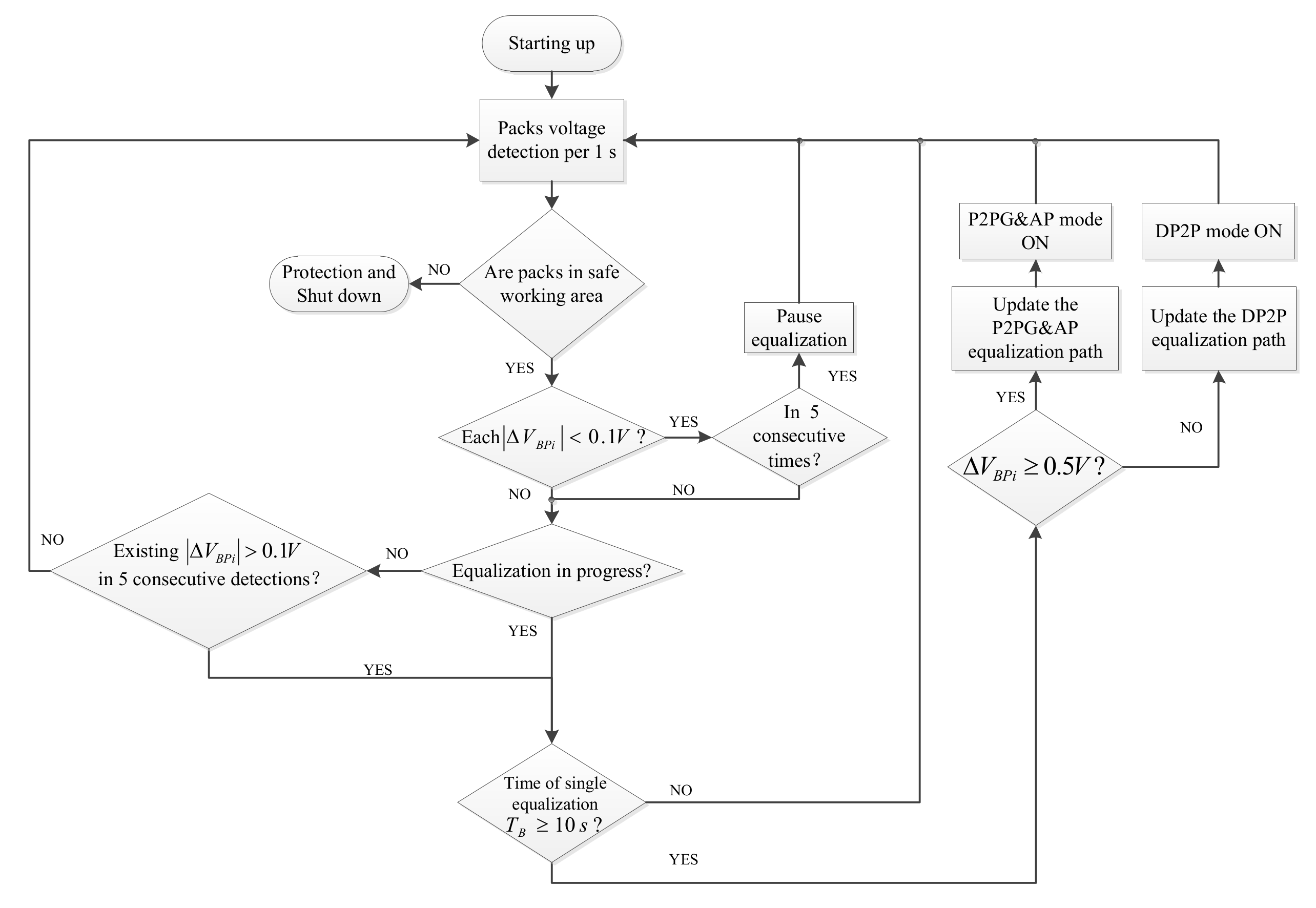

3. The Bimodal Hybrid Control Strategy

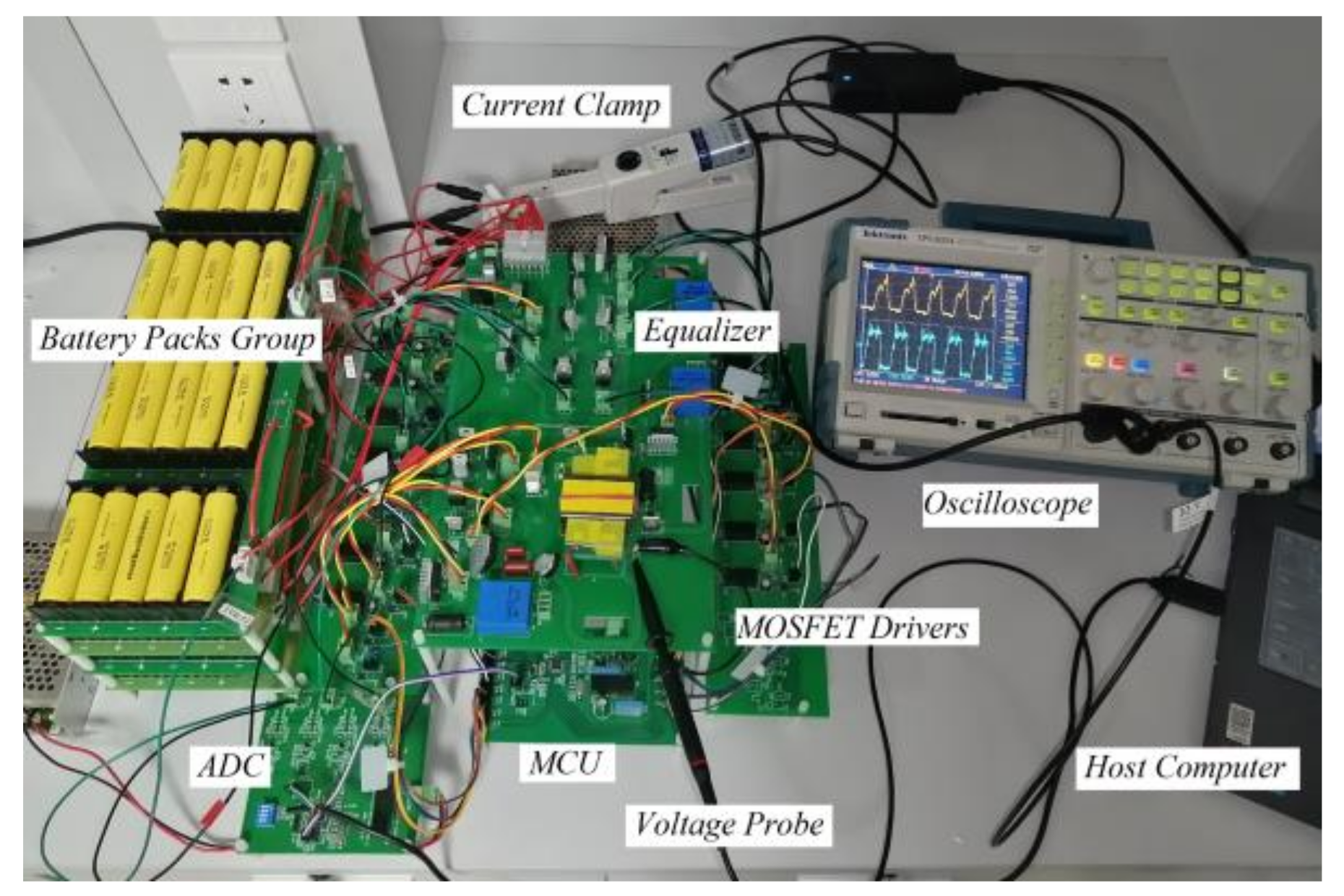

4. Experiment Results

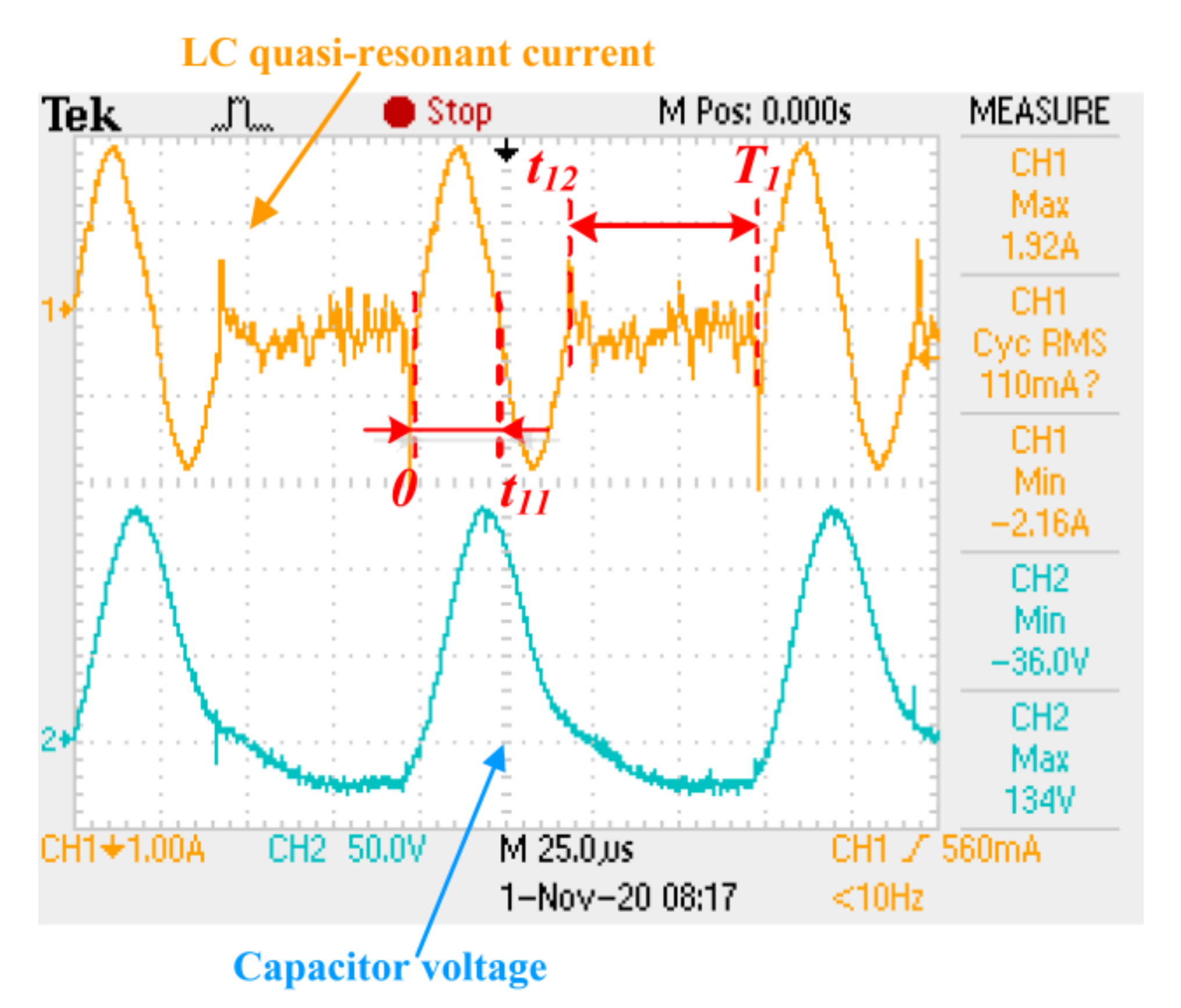

4.1. P2PG&AP Mode

4.2. DP2P Mode

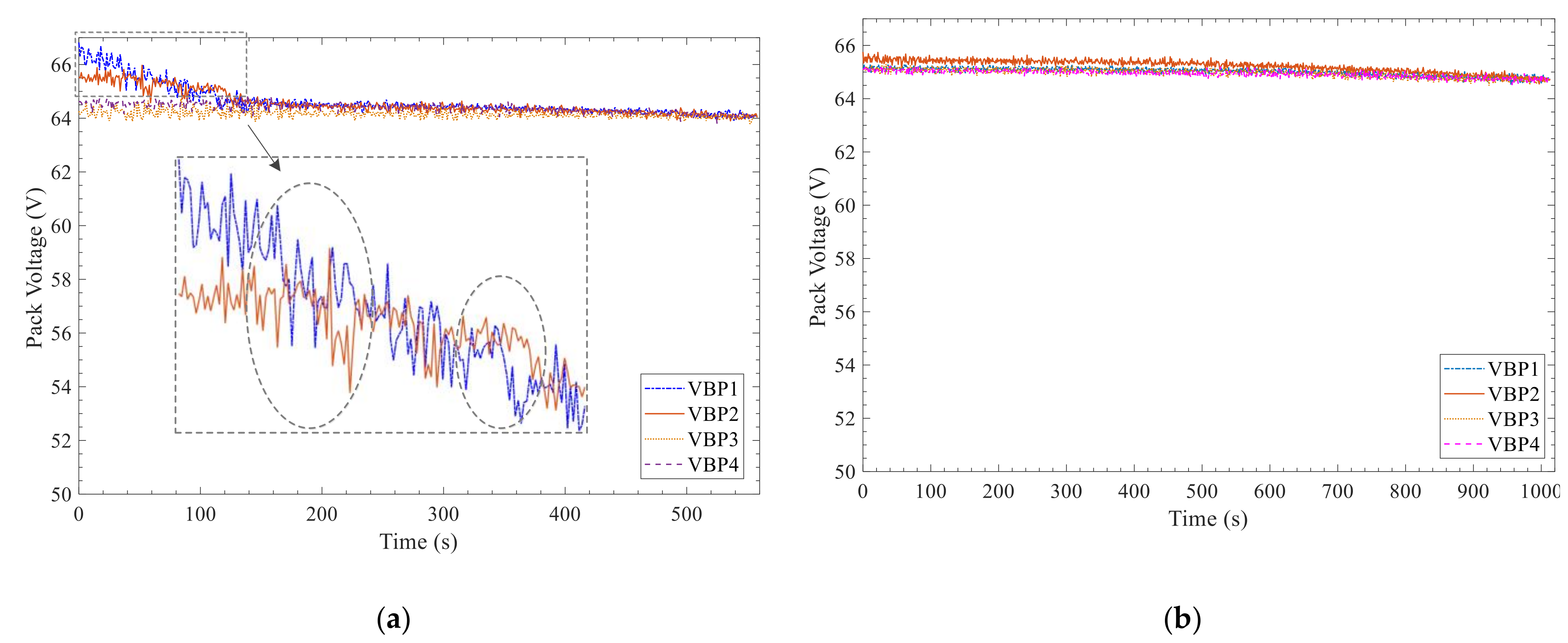

4.3. The Bimodal Hybrid Mode

5. Comparison with Conventional Pack Equalizers

6. Conclusions

- (1)

- (2)

- An inter-pack equalization with minute level balancing time and more than 89.66% efficiency can be achieved through the bimodal hybrid control strategy, which can also effectively prevent the repeated equalization.

- (3)

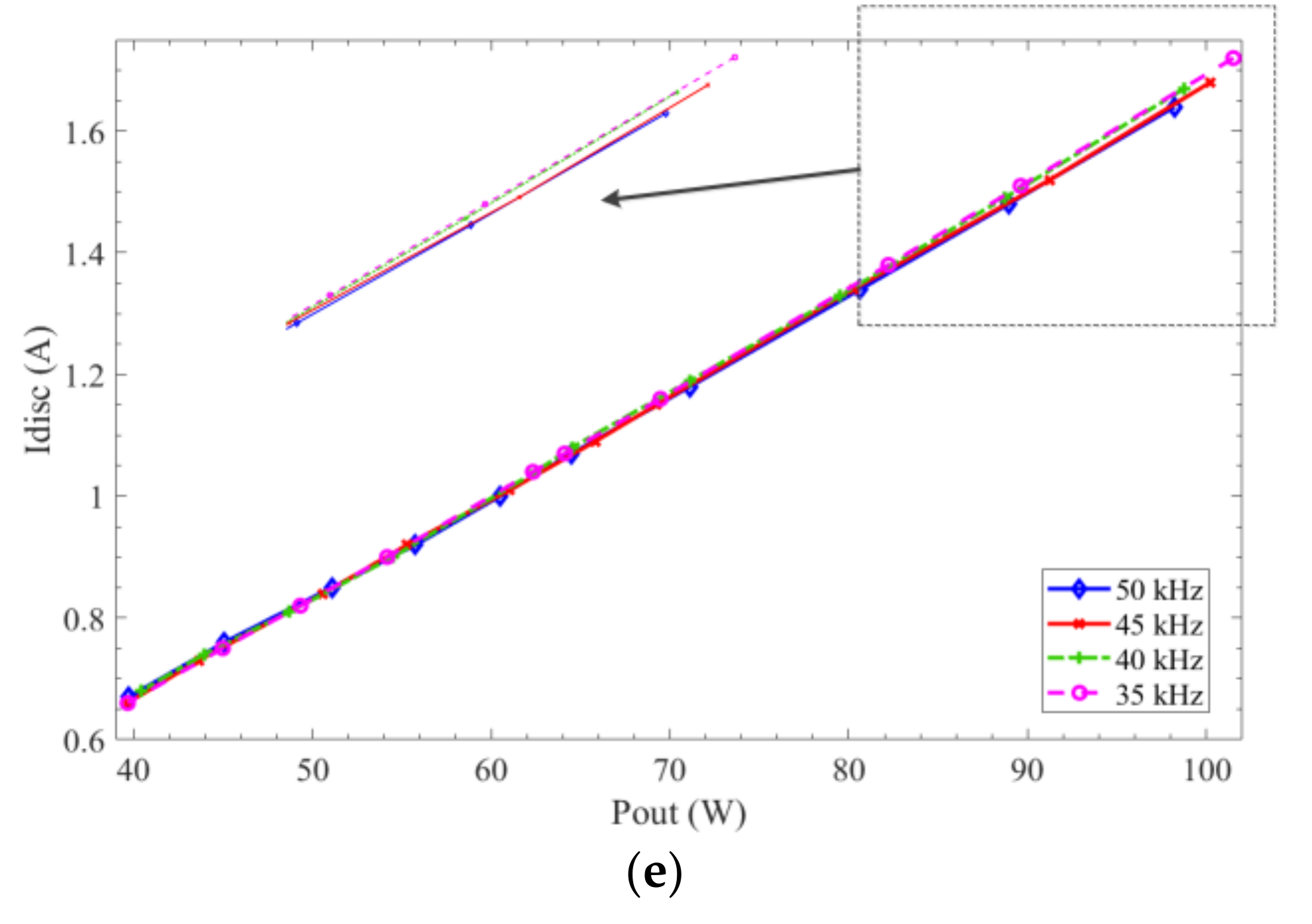

- The equalizer is robust to different switching frequencies and different initial pack voltage distributions.

- (4)

- The proposed pack equalizer, which can cooperate with passive equalizer chips, provides a solution to simplify the structure of numerous cell equalizers in a long series battery group. This two-stage equalization scheme—which can be applied to electric vehicles, clean energy storage equipment and other fields—reduces the total number of power switches (including MOSFETs and power diodes) by at least 60%, and the total numbers of transformers and transformer coils by at least 75% and 97.5% respectively, as shown in Table 9.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Frost, D.F.; Howey, D.A. Completely Decentralized Active Balancing Battery Management System. IEEE Trans. Power Electron. 2018, 33, 729–738. [Google Scholar] [CrossRef]

- Wen, S. Cell Balancing Buys Extra Run Time and Battery Life. 2009. Available online: http://focus.ti.com/lit/an/slyt322/slyt322.pdf (accessed on 10 October 2019).

- Gallardo-Lozano, J.; Romero-Cadaval, E.; Isabel Milanes-Montero, M.; Guerrero-Martinez, M.A. Battery equalization active methods. J. Power Sources 2014, 246, 934–949. [Google Scholar] [CrossRef]

- Imtiaz, A.M.; Khan, F.H. “Time Shared Flyback Converter” Based Regenerative Cell Balancing Technique for Series Connected Li-Ion Battery Strings. IEEE Trans. Power Electron. 2013, 28, 5960–5975. [Google Scholar] [CrossRef]

- McCurlie, L.; Preindl, M.; Emadi, A. Fast Model Predictive Control for Redistributive Lithium-Ion Battery Balancing. IEEE Trans. Ind. Electron. 2017, 64, 1350–1357. [Google Scholar] [CrossRef]

- Shang, Y.; Zhao, S.; Fu, Y.; Han, B.; Hu, P.; Mi, C.C. A Lithium-Ion Battery Balancing Circuit Based on Synchronous Rectification. IEEE Trans. Power Electron. 2020, 35, 1637–1648. [Google Scholar] [CrossRef]

- Min, G.; Ha, J. Inner Supply Data Transmission in Quasi-Resonant Flyback Converters for Li-Ion Battery Applications Using Multiplexing Mode. IEEE Trans. Power Electron. 2019, 34, 64–73. [Google Scholar] [CrossRef]

- Shang, Y.; Cui, N.; Zhang, Q.; Zhang, C. A battery equalizer with zero-current switching and zero-voltage gap among cells based on three-resonant-state LC converters. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 1647–1651. [Google Scholar]

- Ouyang, Q.; Chen, J.; Zheng, J.; Hong, Y. SOC Estimation-Based Quasi-Sliding Mode Control for Cell Balancing in Lithium-Ion Battery Packs. IEEE Trans. Ind. Electron. 2018, 65, 3427–3436. [Google Scholar] [CrossRef]

- Cao, X.; Zhong, Q.; Qiao, Y.; Deng, Z. Multilayer Modular Balancing Strategy for Individual Cells in a Battery Pack. IEEE Trans. Energy Convers. 2018, 33, 526–536. [Google Scholar] [CrossRef]

- Yuanmao, Y.; Cheng, K.W.E.; Yeung, Y.P.B. Zero-Current Switching Switched-Capacitor Zero-Voltage-Gap Automatic Equalization System for Series Battery String. IEEE Trans. Power Electron. 2012, 27, 3234–3242. [Google Scholar] [CrossRef]

- Shang, Y.; Zhang, Q.; Cui, N.; Duan, B.; Zhou, Z.; Zhang, C. Multicell-to-Multicell Equalizers Based on Matrix and Half-Bridge LC Converters for Series-Connected Battery Strings. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1755–1766. [Google Scholar] [CrossRef]

- Chen, Y.; Liu, X.; Cui, Y.; Zou, J.; Yang, S. A MultiWinding Transformer Cell-to-Cell Active Equalization Method for Lithium-Ion Batteries With Reduced Number of Driving Circuits. IEEE Trans. Power Electron. 2016, 31, 4916–4929. [Google Scholar] [CrossRef]

- Ye, Y.; Cheng, K.W.E. Modeling and Analysis of Series–Parallel Switched-Capacitor Voltage Equalizer for Battery/Supercapacitor Strings. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 3, 977–983. [Google Scholar] [CrossRef]

- Lee, K.; Chung, Y.; Sung, C.; Kang, B. Active Cell Balancing of Li-Ion Batteries Using $LC$ Series Resonant Circuit. IEEE Trans. Ind. Electron. 2015, 62, 5491–5501. [Google Scholar] [CrossRef]

- Park, S.; Park, K.; Kim, H.; Moon, G.; Youn, M. Single-Magnetic Cell-to-Cell Charge Equalization Converter with Reduced Number of Transformer Windings. IEEE Trans. Power Electron. 2012, 27, 2900–2911. [Google Scholar] [CrossRef]

- Mestrallet, F.; Kerachev, L.; Crebier, J.; Collet, A. Multiphase Interleaved Converter for Lithium Battery Active Balancing. IEEE Trans. Power Electron. 2014, 29, 2874–2881. [Google Scholar] [CrossRef]

- Hannan, M.A.; Hoque, M.M.; Peng, S.E.; Uddin, M.N. Lithium-Ion Battery Charge Equalization Algorithm for Electric Vehicle Applications. IEEE Trans. Ind. Appl. 2017, 53, 2541–2549. [Google Scholar] [CrossRef]

- Sauzé, C.; Neal, M. Artificial Endocrine Controller for Power Management in Robotic Systems. IEEE Trans. Neural Netw. Learn. Syst. 2013, 24, 1973–1985. [Google Scholar] [CrossRef]

- Govar, C.J.; Banner, J.A. Safety testing of lithium ion batteries for navy devices. IEEE Aerosp. Electron. Syst. Mag. 2003, 18, 17–20. [Google Scholar] [CrossRef]

- Sanguino, T.D.J.M.; Ramos, J.E.G. Smart Host Microcontroller for Optimal Battery Charging in a Solar-Powered Robotic Vehicle. IEEE/Asme Trans. Mechatron. 2013, 18, 1039–1049. [Google Scholar] [CrossRef]

- Yu, Y.; Saasaa, R.; Khan, A.A.; Eberle, W. A Series Resonant Energy Storage Cell Voltage Balancing Circuit. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 3151–3161. [Google Scholar] [CrossRef]

- Tear Down of 85 kWh Tesla Battery Pack Shows It Could Actually Only Be a 81 kWh Pack. Available online: https://electrek.co/2016/02/03/tesla-battery-tear&–85-kwh/Online (accessed on 12 January 2018).

- Gallardo-Lozano, J.; Romero-Cadaval, E.; Isabel Milanes-Montero, M.; Guerrero-Martinez, M.A. A novel active battery equalization control with on-line unhealthy cell detection and cell change decision. J. Power Sources 2015, 299, 356–370. [Google Scholar] [CrossRef]

- Shang, Y.; Xia, B.; Zhang, C.; Cui, N.; Yang, J.; Mi, C. A Modularization Method for Battery Equalizers Using Multiwinding Transformers. IEEE Trans. Veh. Technol. 2017, 66, 8710–8722. [Google Scholar] [CrossRef]

- Moghaddam, A.F.; Van den Bossche, A. Forward Converter Current Fed Equalizer for Lithium Based Batteries in Ultralight Electrical Vehicles. Electronics 2019, 8, 408. [Google Scholar] [CrossRef]

- Gong, Z.; van de Ven, B.A.; Gupta, K.M.; da Silva, C.; Amon, C.H.; Bergveld, H.J.; Donkers, M.T.; Trescases, O. Distributed Control of Active Cell Balancing and Low-Voltage Bus Regulation in Electric Vehicles Using Hierarchical Model-Predictive Control. IEEE Trans. Ind. Electron. 2020, 67, 10464–10473. [Google Scholar] [CrossRef]

- Park, H.; Kim, C.; Park, K.; Moon, G.; Lee, J. Design of a Charge Equalizer Based on Battery Modularization. IEEE Trans. Veh. Technol. 2009, 58, 3216–3223. [Google Scholar] [CrossRef]

- Dong, B.; Li, Y.; Han, Y. Parallel Architecture for Battery Charge Equalization. IEEE Trans. Power Electron. 2015, 30, 4906–4913. [Google Scholar] [CrossRef]

- Cai, H.; Hu, G. Distributed Control Scheme for Package-Level State-of-Charge Balancing of Grid-Connected Battery Energy Storage System. IEEE Trans. Ind. Inform. 2016, 12, 1919–1929. [Google Scholar] [CrossRef]

- Yuancheng, R.; Ming, X.; Jinghai, Z.; Lee, F.C. Analytical loss model of power MOSFET. IEEE Trans. Power Electron. 2006, 21, 310–319. [Google Scholar] [CrossRef]

- Roshen, W.A. A practical, accurate and very general core loss model for nonsinusoidal waveforms. In Proceedings of the Twentieth Annual IEEE Applied Power Electronics Conference and Exposition, APEC, Austin, TX, USA, 6–10 March 2005; Volume 1302, pp. 1308–1314. [Google Scholar]

| Abbreviations | Explanations |

|---|---|

| P2PG&AP | pack-to-pack-group and pack-to- any-pack |

| DP2P | direct-pack-to-pack |

| STMR | secondary side two-transistor magnetic reset structure |

| SBC | secondary side boost converter |

| FSC | full-switching-cycle |

| ZVG | zero voltage gap |

| LC2AP | LC quasi-resonator to any pack |

| Parameters | Explanations |

|---|---|

| the EMF value of TP’s primary coil | |

| the EMF value of TP’s secondary coil | |

| the excitation impedance value of TP | |

| the current value of primary side electrified circuit under different switching states | |

| the output current value of secondary coil under different switching states | |

| the SBC current | |

| the quasi-resonator current | |

| the STMR output current | |

| the excitation inductance of TP | |

| the voltage value of the battery pack BPi | |

| the leakage inductance of TP’s primary coil | |

| the leakage inductance of TP’s secondary coil | |

| the total equivalent resistance of the primary side electrified circuit in Figure 2b,c | |

| the total equivalent resistance of the primary side circuit in Figure 2d | |

| the total equivalent resistance of the primary side circuit in Figure 2e | |

| the sum of the forward voltage drop of diodes on the energized circuit | |

| the inductance value of LC quasi-resonator | |

| the boost inductance value of the secondary side | |

| the capacitance value of LC quasi-resonator | |

| The output capacitance of MOSFET | |

| The junction capacitance of power diode | |

| The equivalent resistance of quasi-resonator | |

| the total equivalent resistance of the secondary side electrified circuit in Figure 2b | |

| the total equivalent resistance of the secondary side electrified circuit in Figure 2c | |

| the equivalent resistance of SBC circuit in Figure 2d | |

| the equivalent resistance of STMR in both Figure 2d, e |

| Parameter | Value |

|---|---|

| 0.485 | |

| 0.08 | |

| 0.315 | |

| 360 μH | |

| 330 μH | |

| 3.3 nF | |

| 330 μH | |

| 150 nF | |

| Turns ratio of TP | 1/4 |

| Parameters | Explanations |

|---|---|

| The total input power of pack equalizer | |

| the conduction and switching loss of all primary lines | |

| the average power loss of LC quasi-resonator caused by output capacitance of Q11 in 0−t05 | |

| the primary input power of transformer TP | |

| the total output power of pack equalizer | |

| the average power output from SBC to the whole pack group in 0−t05 | |

| the average power output from STMR to the whole group in t05−T0 | |

| the average power of the LC quasi-resonator reversely charging into the acceptor battery pack in t06–T0 | |

| the equalizer energy efficiency of P2PG&AP mode | |

| the ratios of output powers from SBC to input power of equalizer | |

| the ratios of output powers from STMR to input power of equalizer | |

| the ratios of output powers from LC quasi-resonator to input power of equalizer | |

| The circuit conduction loss of equalizer | |

| the total equivalent resistance of the primary side circuit in Figure 4b | |

| the total equivalent resistance of the primary side circuit in Figure 4c | |

| the total equivalent resistance of the primary side circuit in Figure 4d | |

| The switching loss of equalizer | |

| The core loss of equalizer’s transformer | |

| the turn-on losses of power switch | |

| the turn-off losses of power switch | |

| the switching frequency | |

| the withstand voltage of the power switch before it turns on | |

| the withstand voltage of the power switch before it turns on | |

| the turnoff current of MOSFET | |

| the falling time of MOSFET | |

| the reverse recovery current of power diode | |

| the reverse recovery time of power diode |

| Component | Product |

|---|---|

| Q1,Q8,Q14 | STW32NM50N,, |

| Q2-Q7,Q12 | SIHP25N40D-GE3, , |

| Q9,Q10 | PTW40N50, , |

| Q11,Q13 | IRFP4768PBF, , |

| D1-D10 | BYV29-400, , |

| D11,D12 | MBR20H150CTG, (Schottky diodes) |

| D13 | PFR20V300CTF, (Schottky diodes) |

| D14, D15,D18 | B1D04065K, (SiC schottky diodes) |

| D16,D17 | ES2GB, , |

| CP1 | Film capacitor, 3.3 nF |

| CP2 | Film capacitor, 150 nF |

| LP1,LP2 | Inductors, 330 μH |

| MOSFET optocoupler driver | TLP152 |

| Parameter | Value |

|---|---|

| 10 | |

| 40 | |

| 346.07 μH | |

| 1.28 μH | |

| 0.90 μH | |

| 183.81 mΩ | |

| 613.64 mΩ |

| Quantity | Equalization Experiments | |

|---|---|---|

| Figure 12a | Figure 12b | |

| 66.82 V | 65.19 V | |

| 65.53 V | 65.76 V | |

| 64.26 V | 65.12 V | |

| 64.61 V | 65.09 V | |

| Balancing Time (s) | 558 s | 1013 s |

| Equalizers | Power | Efficiency | Speed | MOSFET Withstand Voltage | |

|---|---|---|---|---|---|

| Cooperative | Integrated equalizer based on multiwinding transformers [25] | <2.8 W (Small) | AP2P ≤ 91.3% | Hour level (Slow) | No MOSFET used in pack equalization |

| Buck and forward converter equalizer [26] | <40 W (Medium) | PG2P ≤ 83.84% | Second level (Fast) | ||

| Independent | Switch capacitor direct pack equalizer [28] | No specific data | AP2P No specific data | Hour level (Extremely Slow) | |

| Inductor adjacent pack equalizer [29] | <0.2 W (Small) | AP2P No specific data | Hour level (Medium) | ||

| Proposed pack equalizer | ≤98 W (Large) | Bimodal ≥ 89.66% | Minute level (Fast) | ||

| Equalizers | Component Number | Total Size | Total Cost | |||||||||||

| Pack Level | Cell Level | |||||||||||||

| M | D | W | T | L | C | M | D | W | T | L | ||||

| Cooperative | Integrated equalizer based on multiwinding transformers [25] | 0 | 0 | 6 | SH | 0 | 0 | 80 | 0 | 80 | 4 | 0 | Large | High |

| Buck and forward converter equalizer [26] | 1 | 1 | 0 | SH | 1 | 1 | 4 | 80 | 84 | 4 | 0 | Large | Low | |

| Independent | Switch capacitor direct pack equalizer [28] | 12 | 0 | 0 | 0 | 0 | 3 | 4 | 80 | 84 | 4 | 0 | Large | Medium |

| Inductor adjacent pack equalizer [29] | 6 | 0 | 0 | 0 | 3 | 0 | 152 | 0 | 0 | 0 | 76 | Small | High | |

| Proposed pack equalizer | 14 | 18 | 2 | 1 | 2 | 2 | 16 five-series chip level cell equalizers | Small | Medium | |||||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, Q.; Gao, M.; Lin, H.; Dong, Z. A Bimodal Multichannel Battery Pack Equalizer Based on a Quasi-Resonant Two-Transistor Forward Converter. Energies 2021, 14, 1112. https://doi.org/10.3390/en14041112

Wu Q, Gao M, Lin H, Dong Z. A Bimodal Multichannel Battery Pack Equalizer Based on a Quasi-Resonant Two-Transistor Forward Converter. Energies. 2021; 14(4):1112. https://doi.org/10.3390/en14041112

Chicago/Turabian StyleWu, Qixing, Mingyu Gao, Huipin Lin, and Zhekang Dong. 2021. "A Bimodal Multichannel Battery Pack Equalizer Based on a Quasi-Resonant Two-Transistor Forward Converter" Energies 14, no. 4: 1112. https://doi.org/10.3390/en14041112

APA StyleWu, Q., Gao, M., Lin, H., & Dong, Z. (2021). A Bimodal Multichannel Battery Pack Equalizer Based on a Quasi-Resonant Two-Transistor Forward Converter. Energies, 14(4), 1112. https://doi.org/10.3390/en14041112