Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter

Abstract

:1. Introduction

- A detailed derivation of the quasi-steady state equivalent model of the system;

- An accurate AC small-signal mathematical modeling of the system considering the component parasitic;

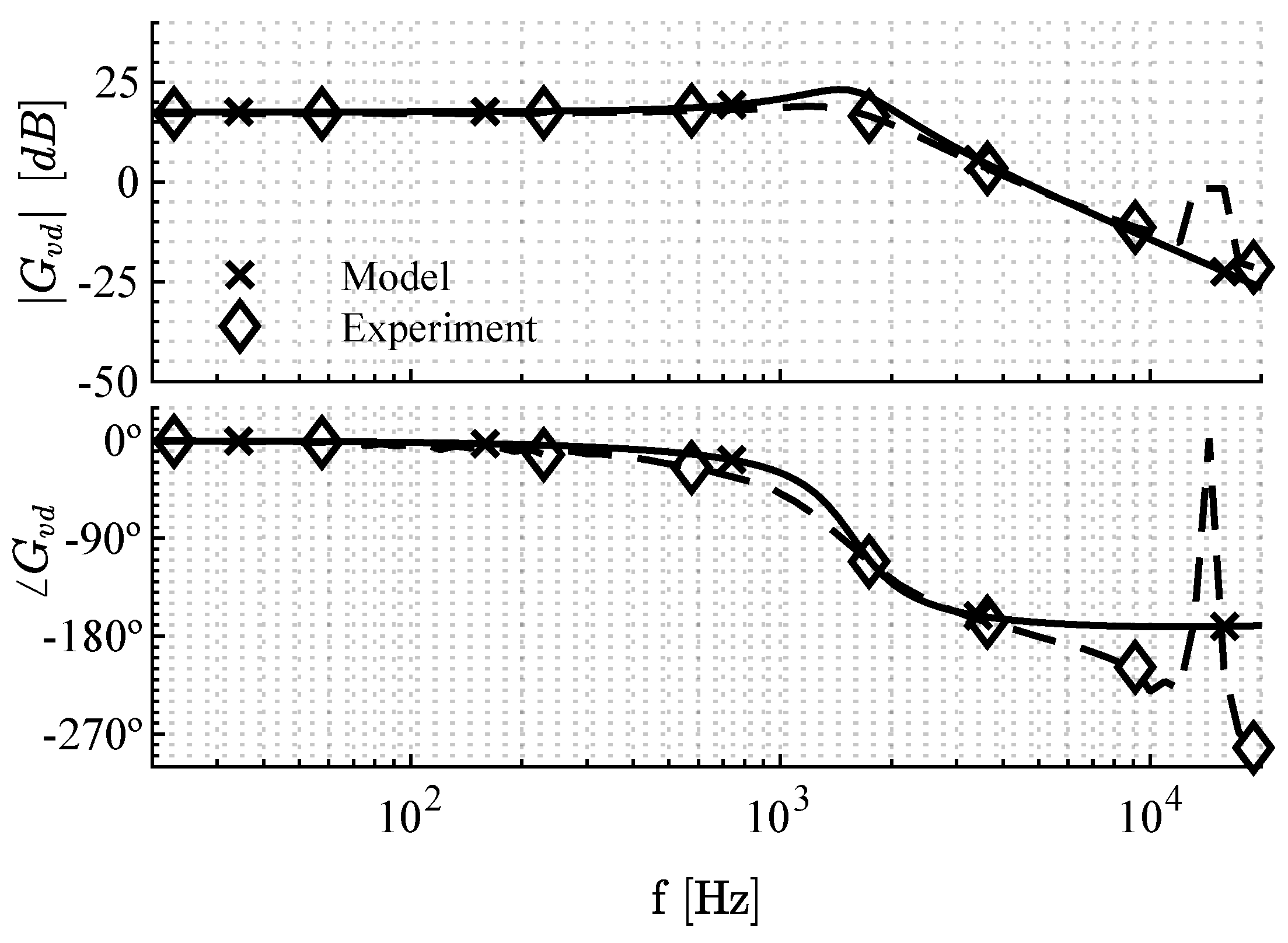

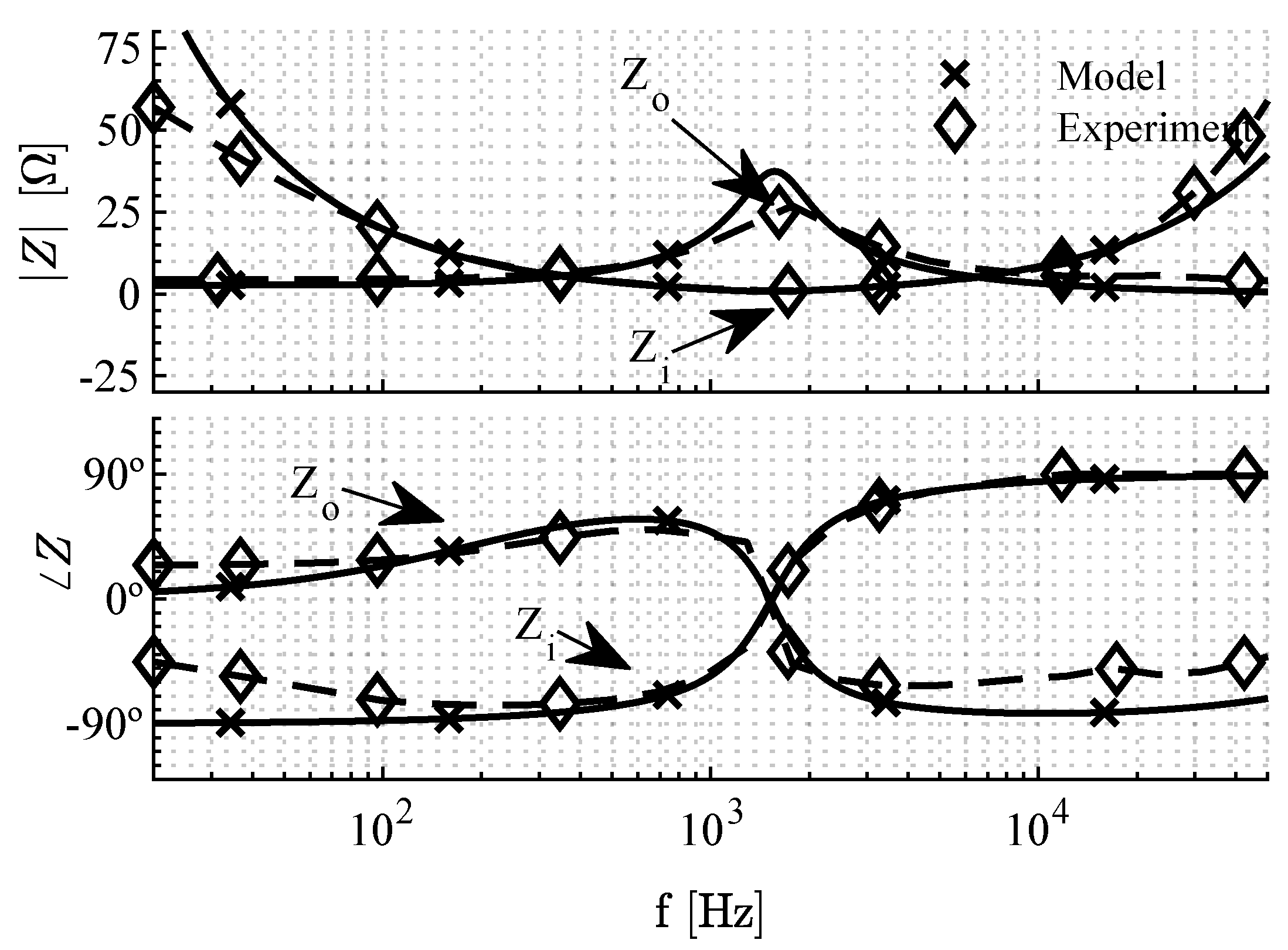

- Experimental verification of the line-to-output transfer function, control-to-output transfer function, open-loop input impedance, and open-loop output impedance;

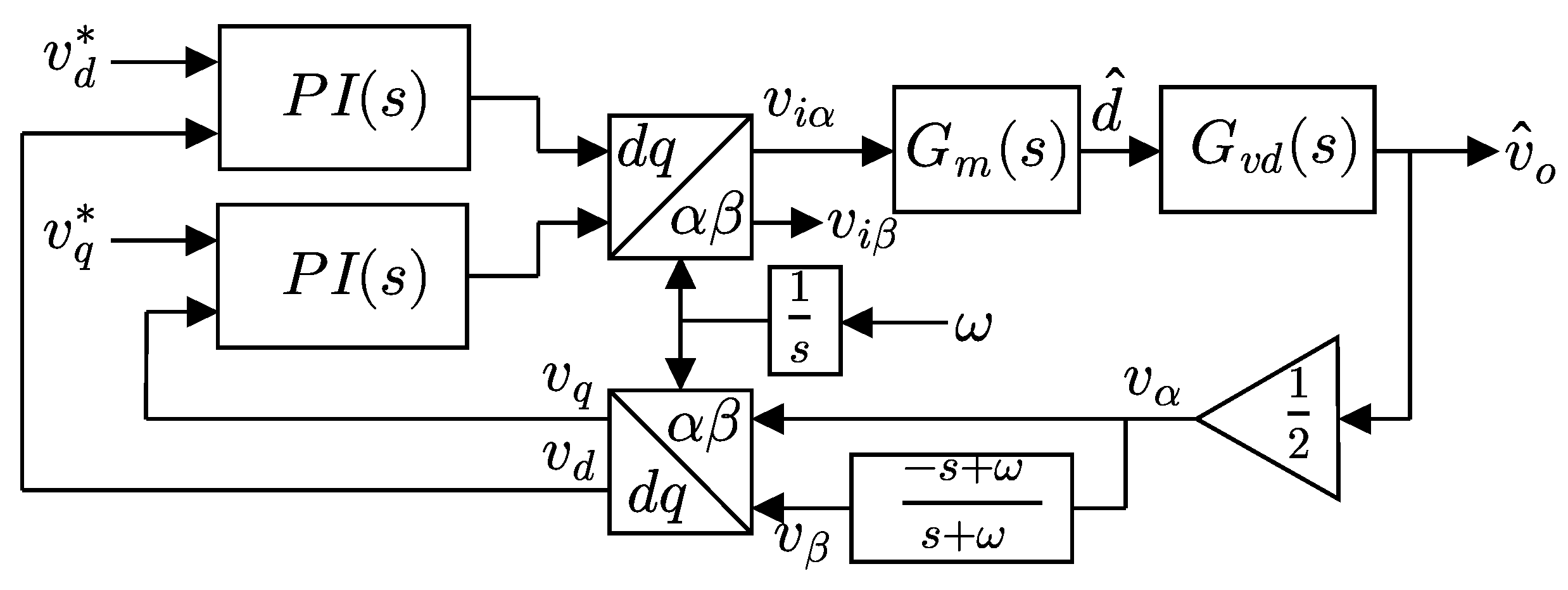

- Design of a voltage mode controller in the synchronous reference frame and selection of controller parameters;

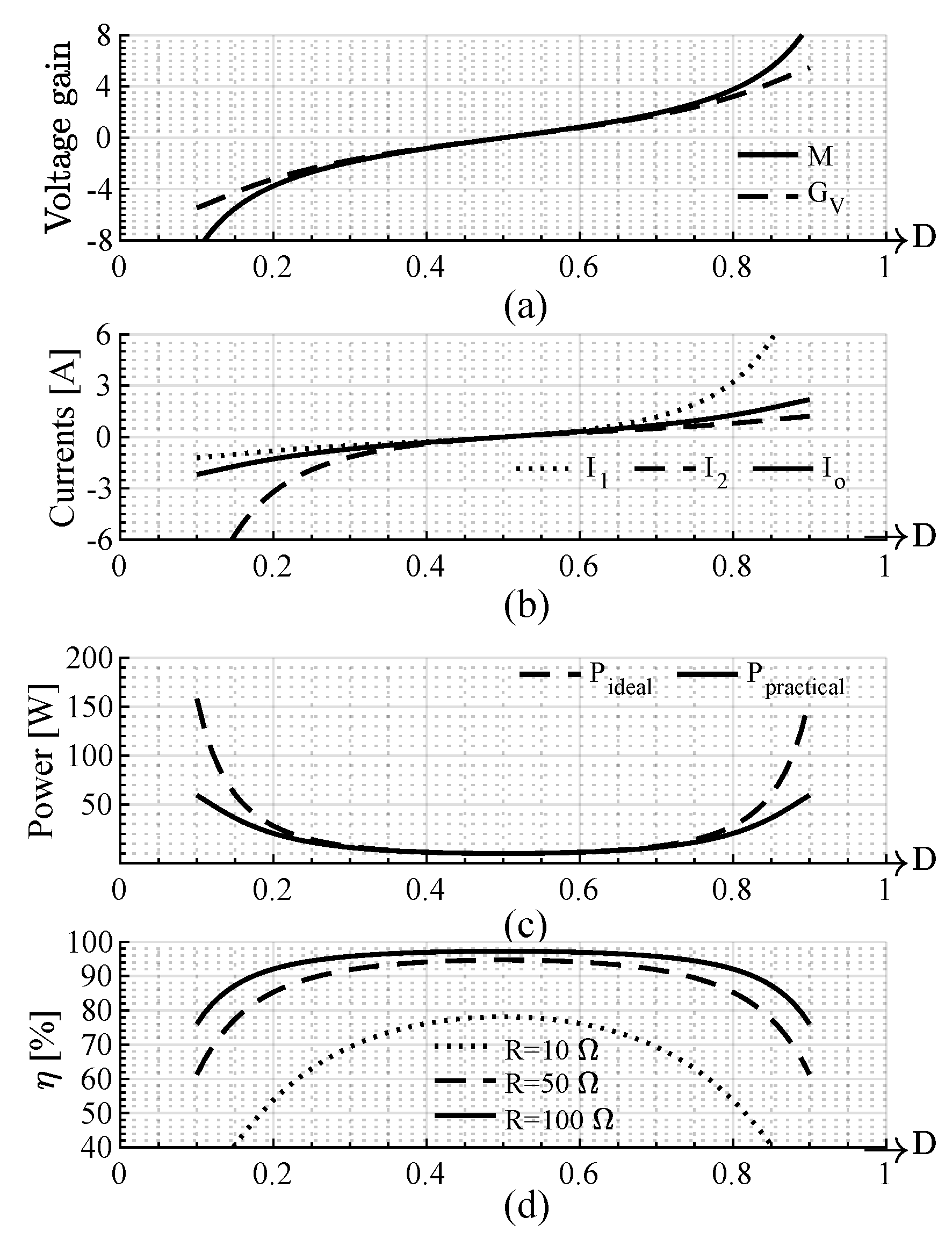

- Estimation of loss and efficiency of the system.

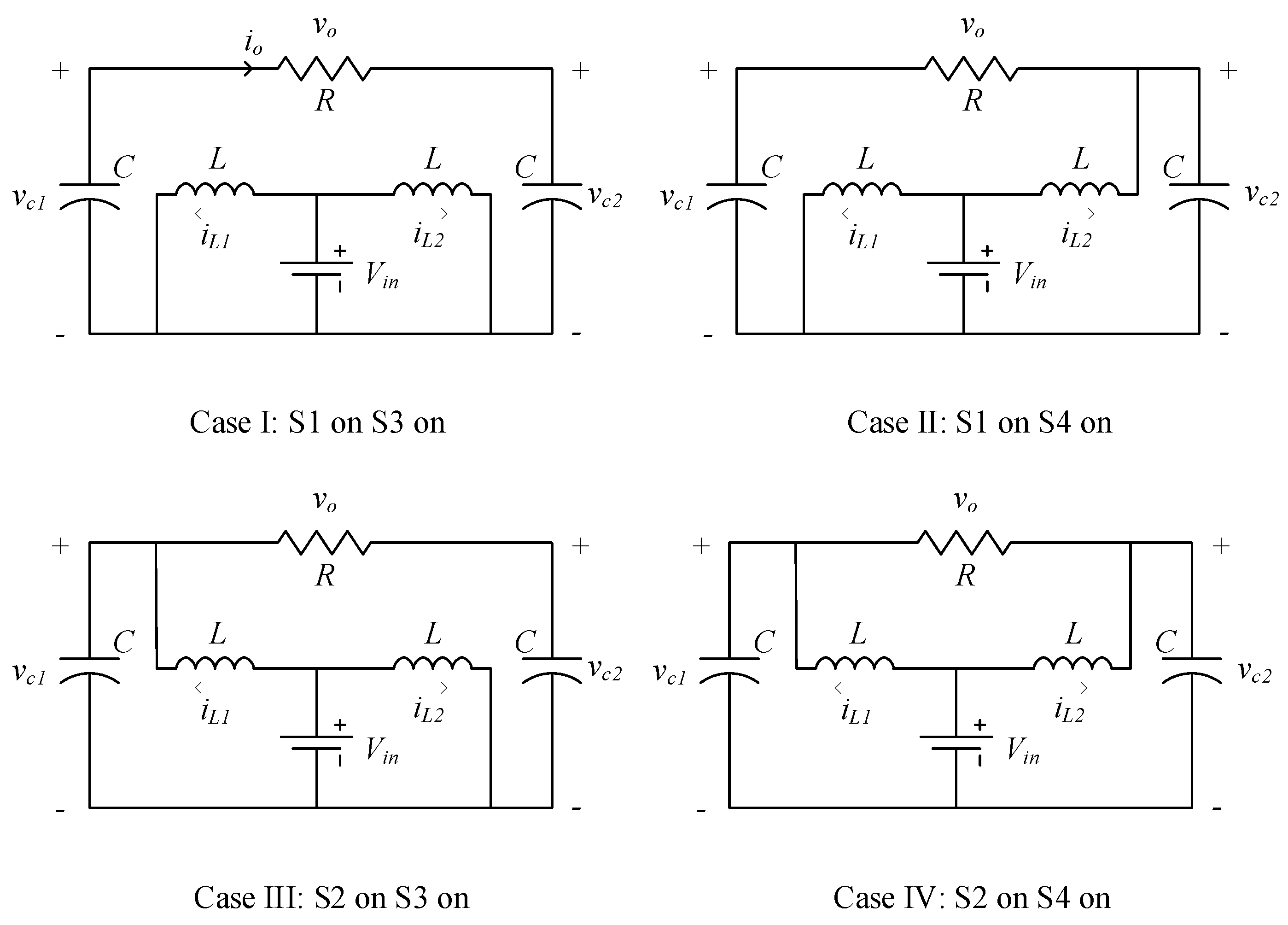

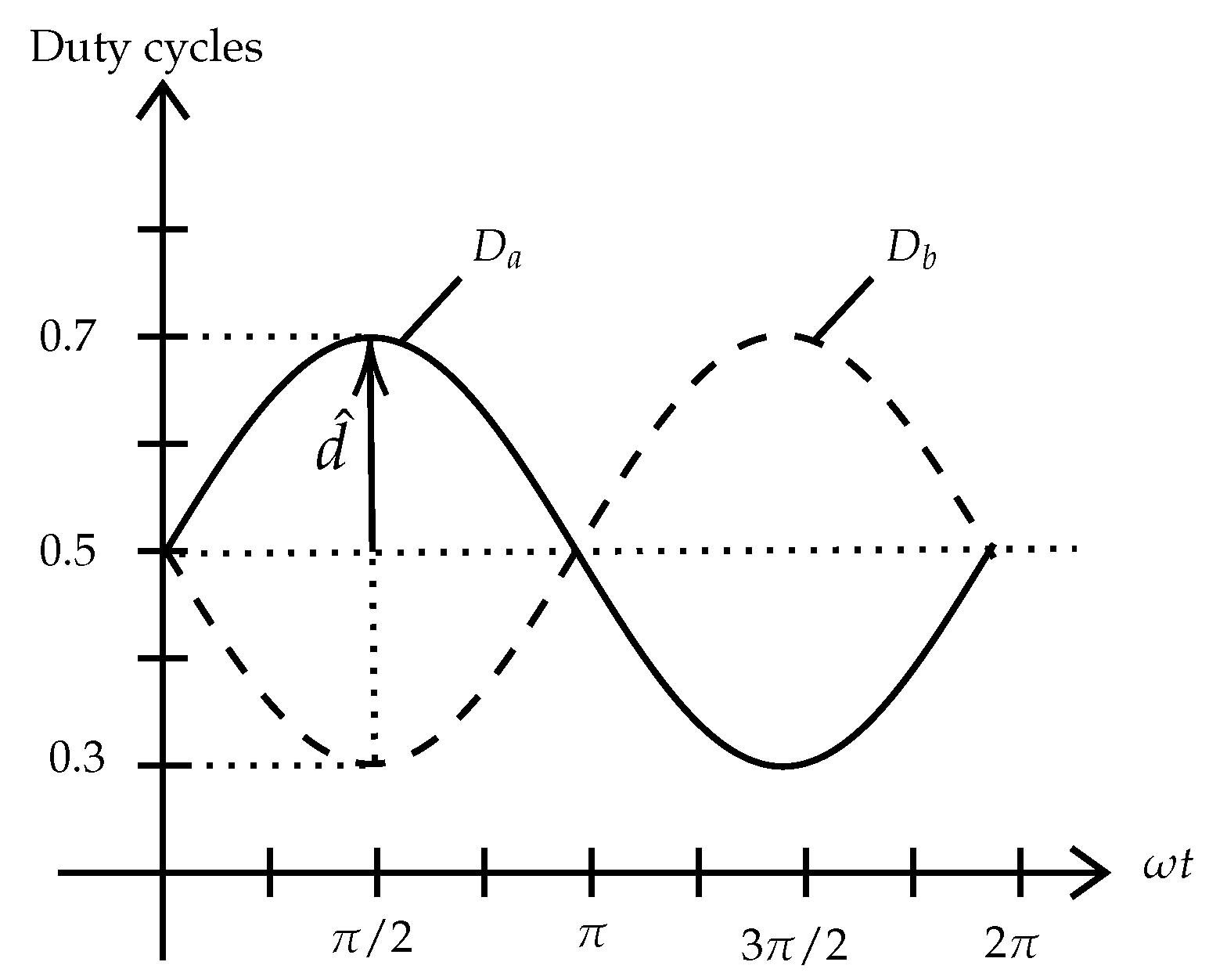

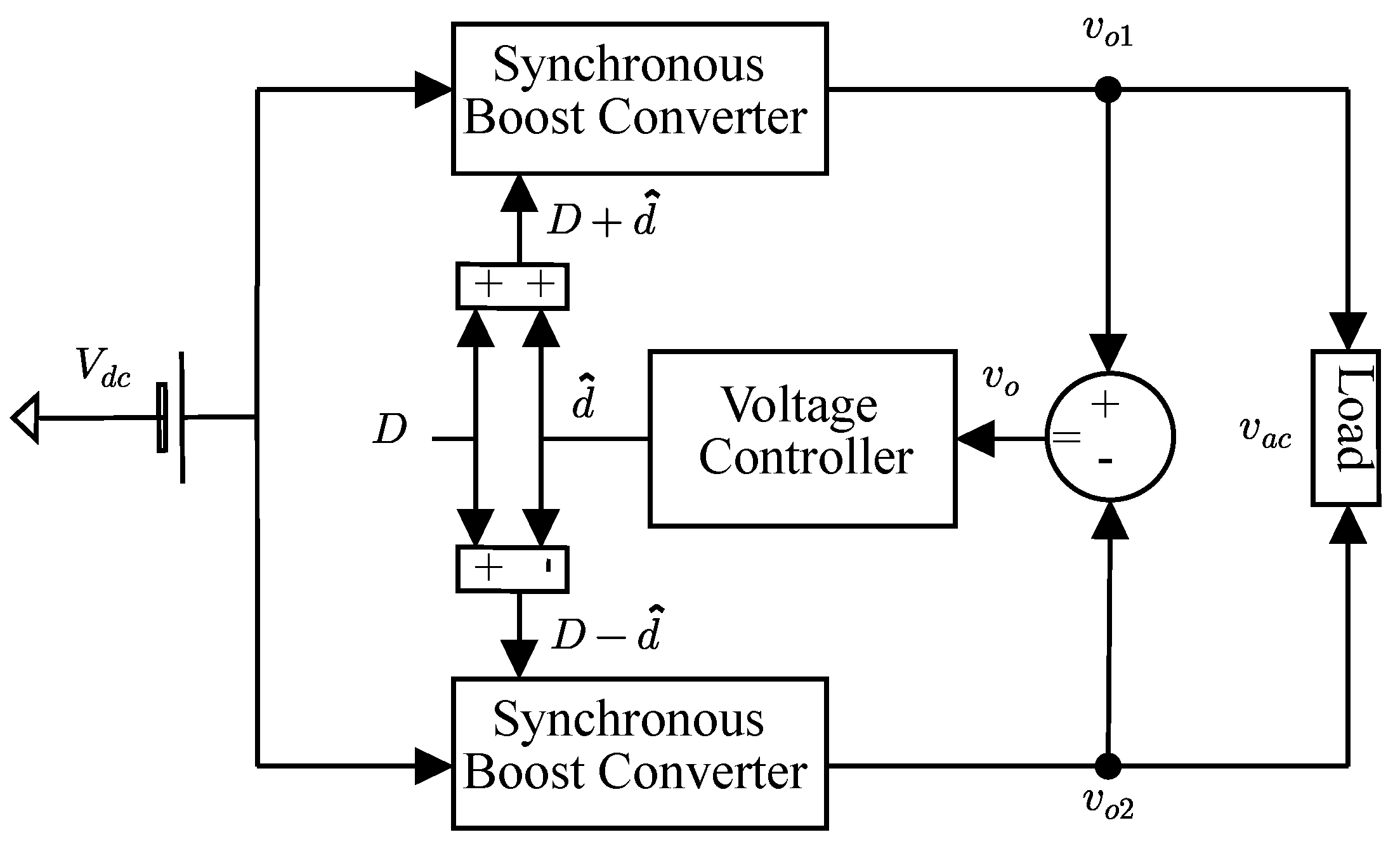

2. Basics of a Boost Inverter

3. Mathematical Modeling of the System

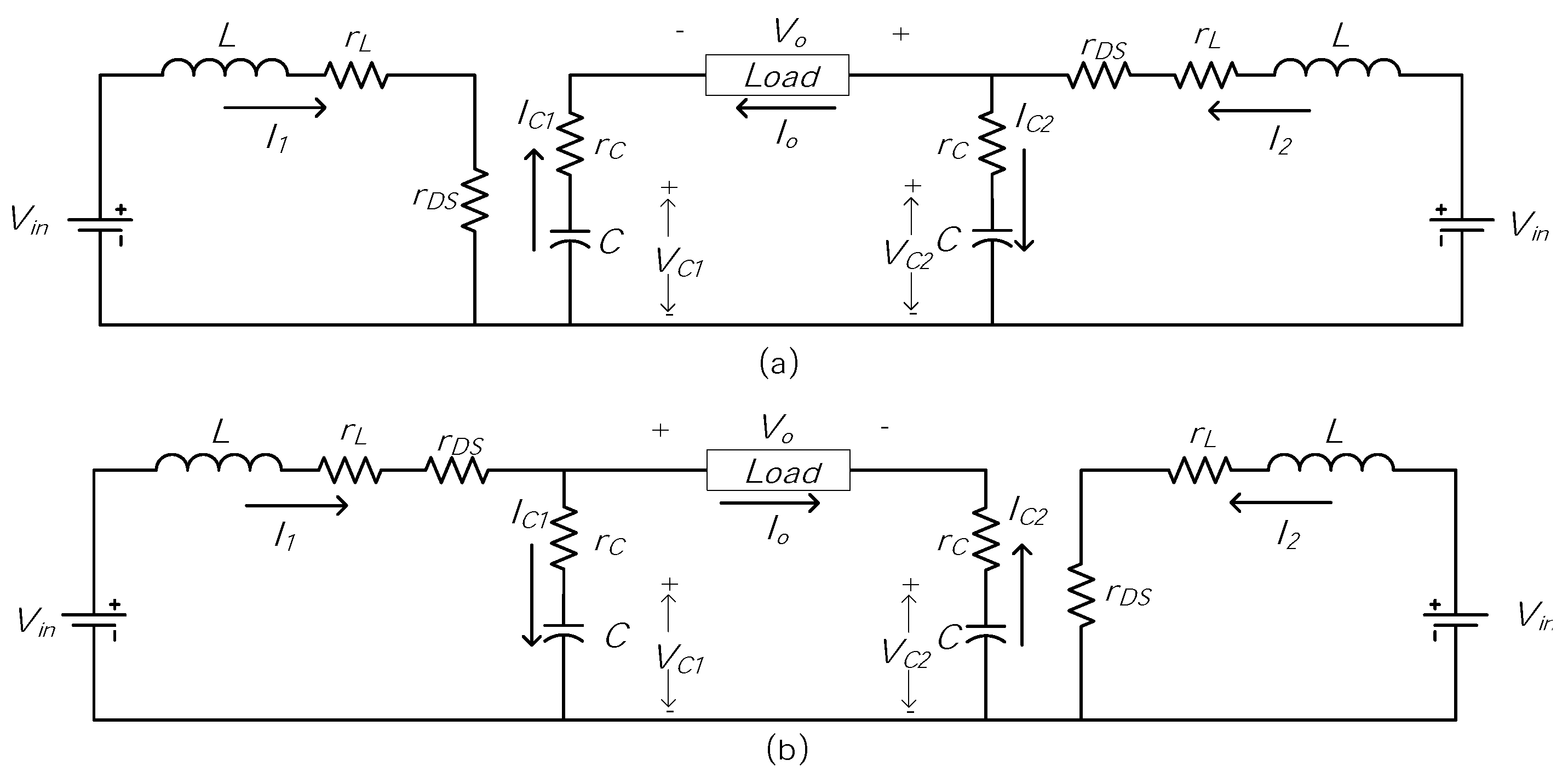

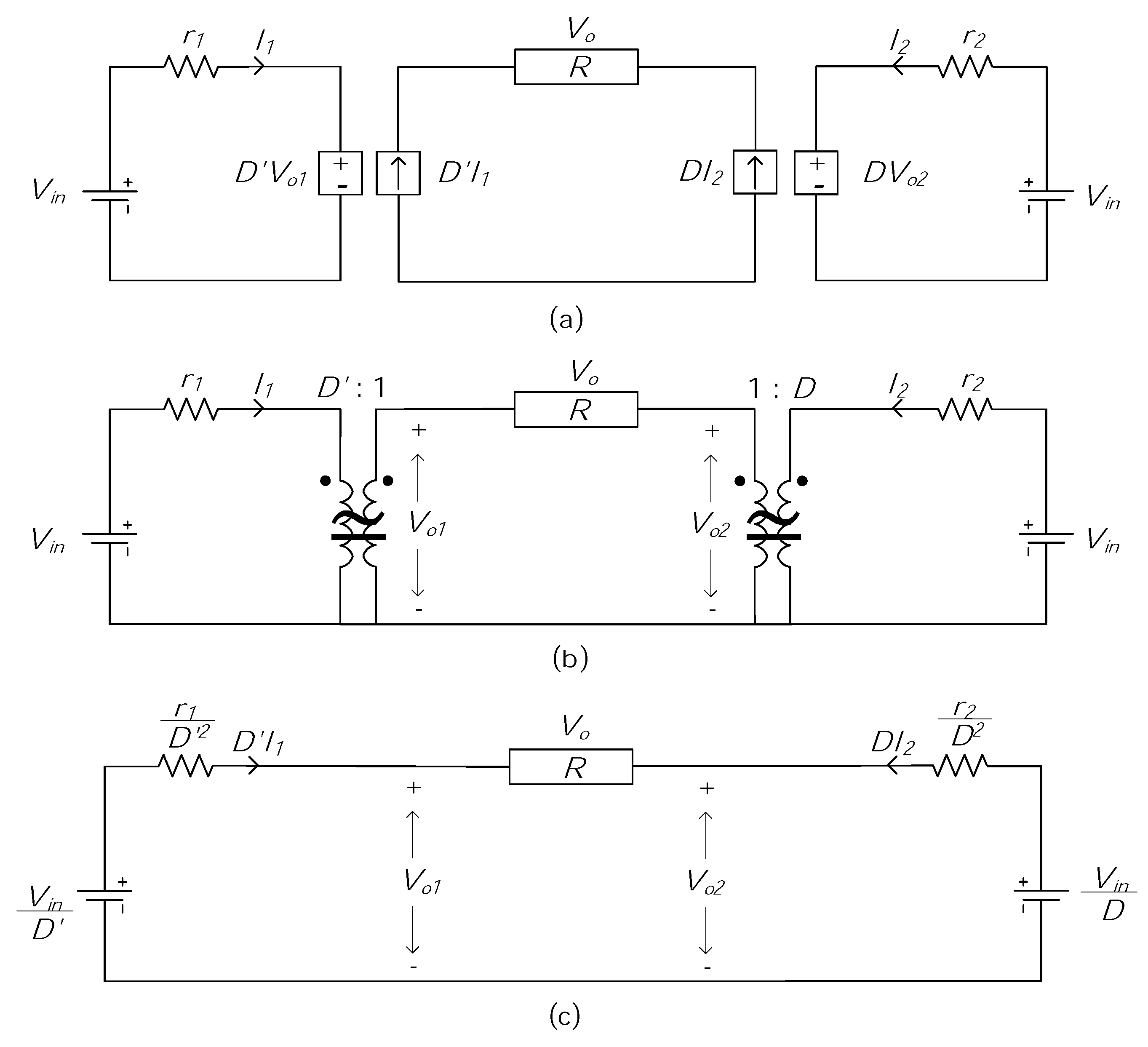

3.1. Quasi-Steady-State Equivalent Circuit Modeling

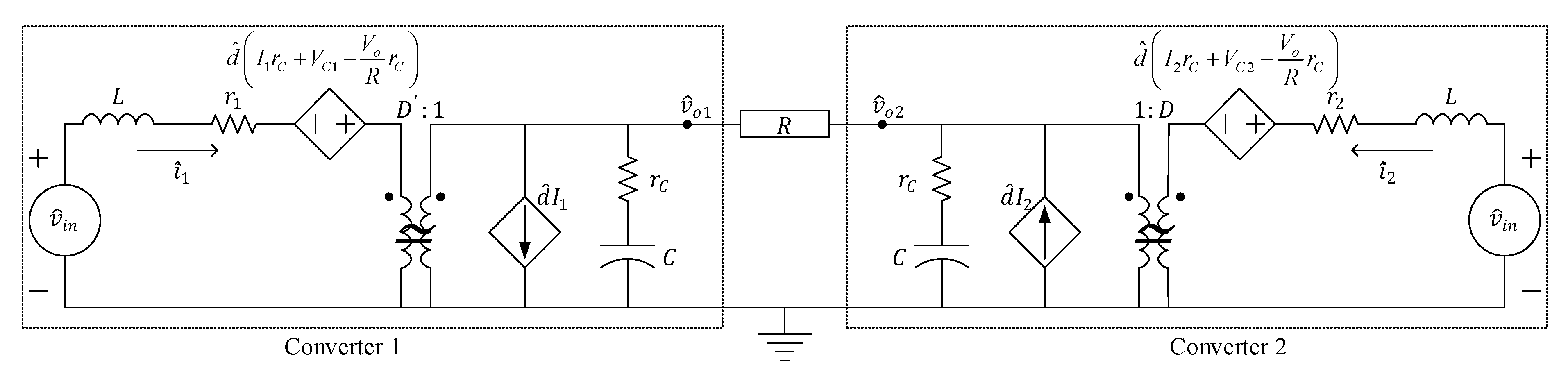

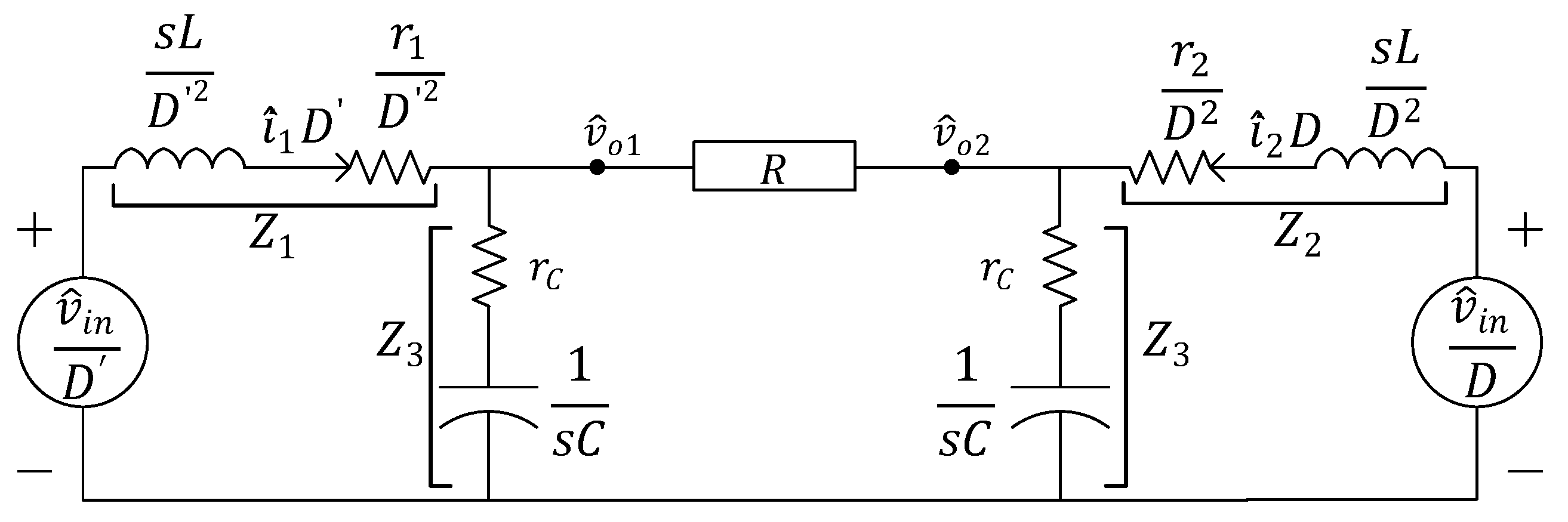

3.2. Small-Signal AC Modeling

3.3. Line to Output Transfer Function

3.4. Control-to-Output Transfer Function

3.5. Open-Loop Input Impedance

3.6. Open-Loop Output Impedance

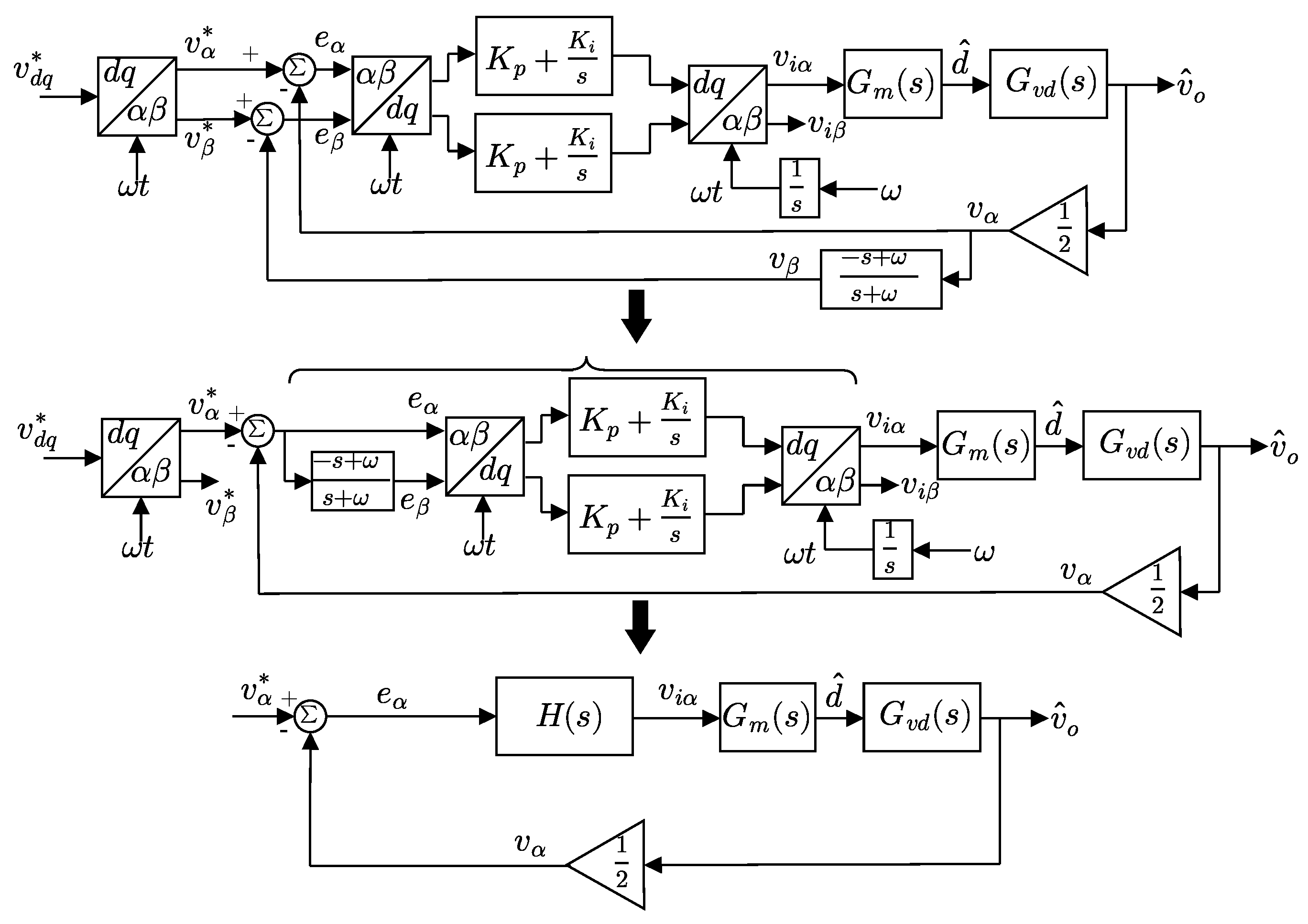

4. Voltage Mode Controller Design

5. Results and Discussions

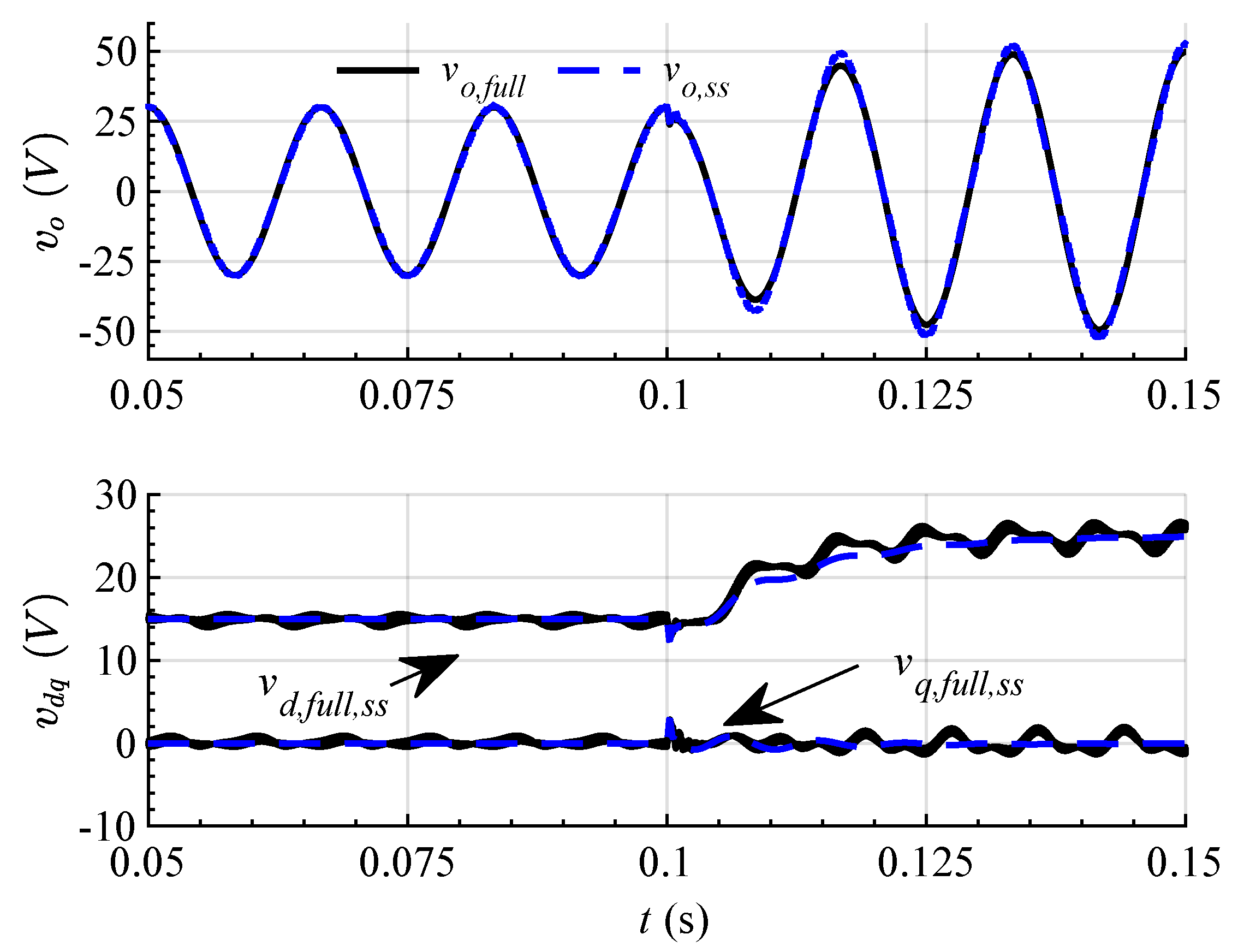

5.1. Simulation Results

5.1.1. Change in Reference

5.1.2. Change in Input

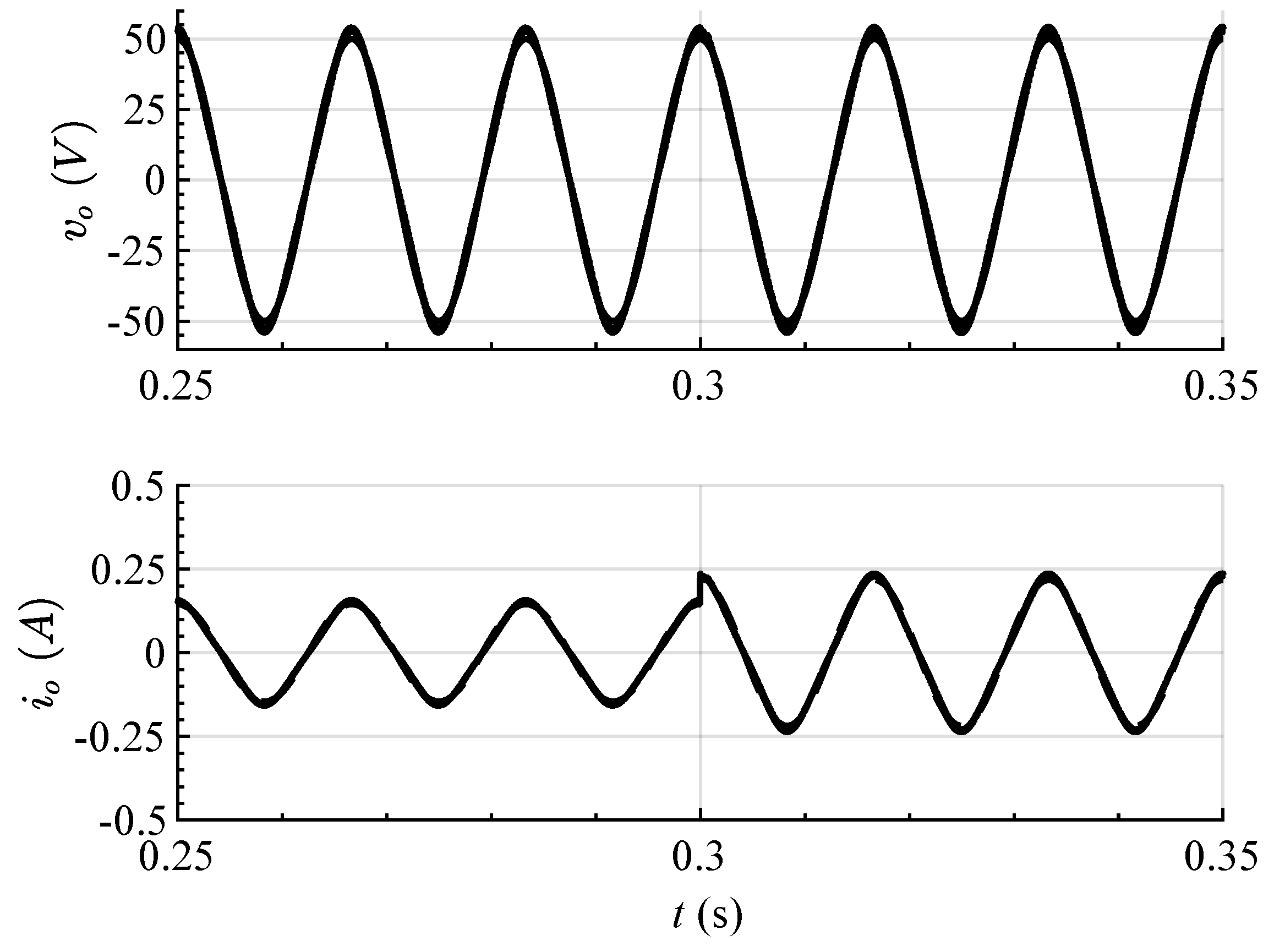

5.1.3. Change in Output Impedance

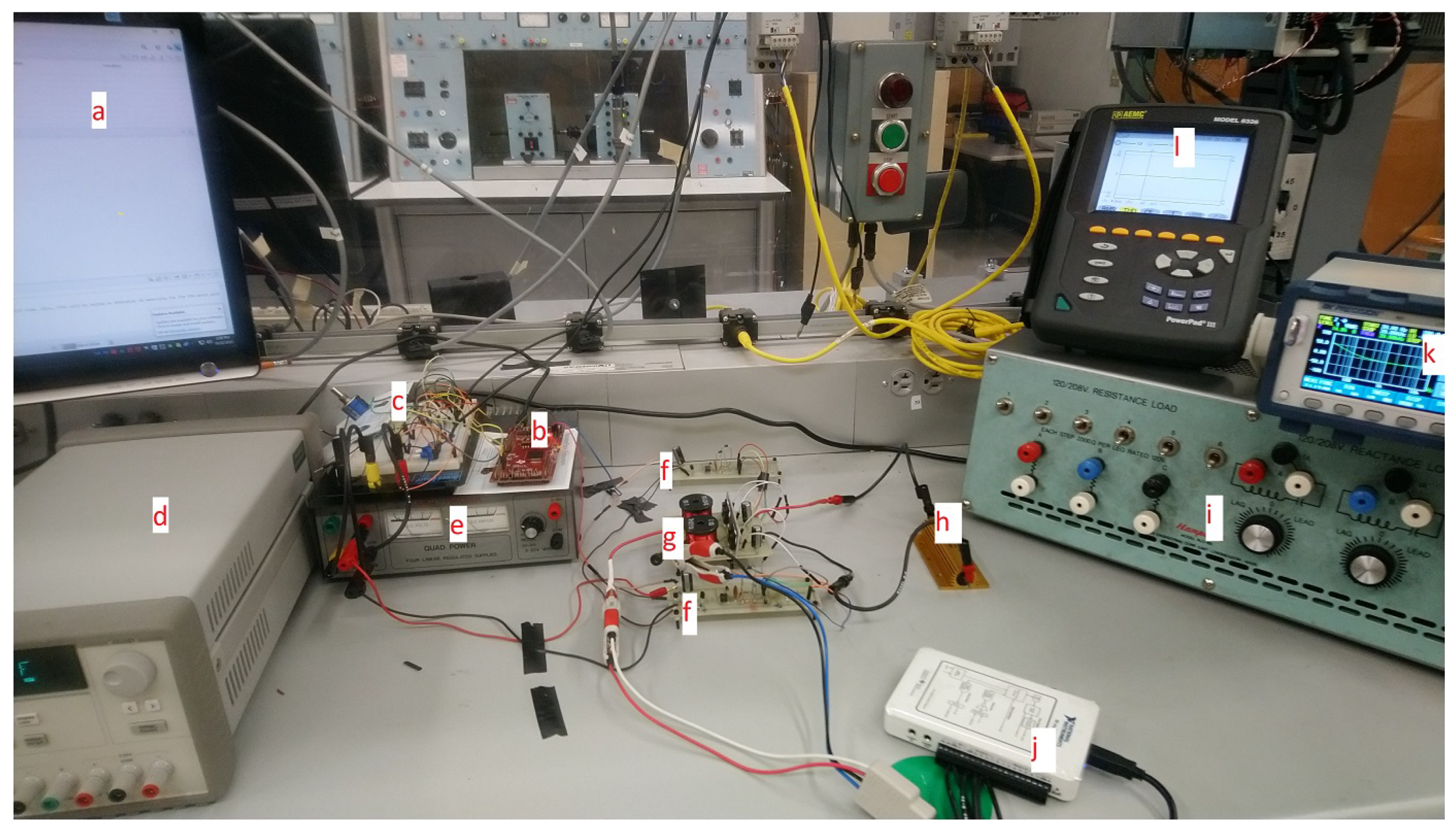

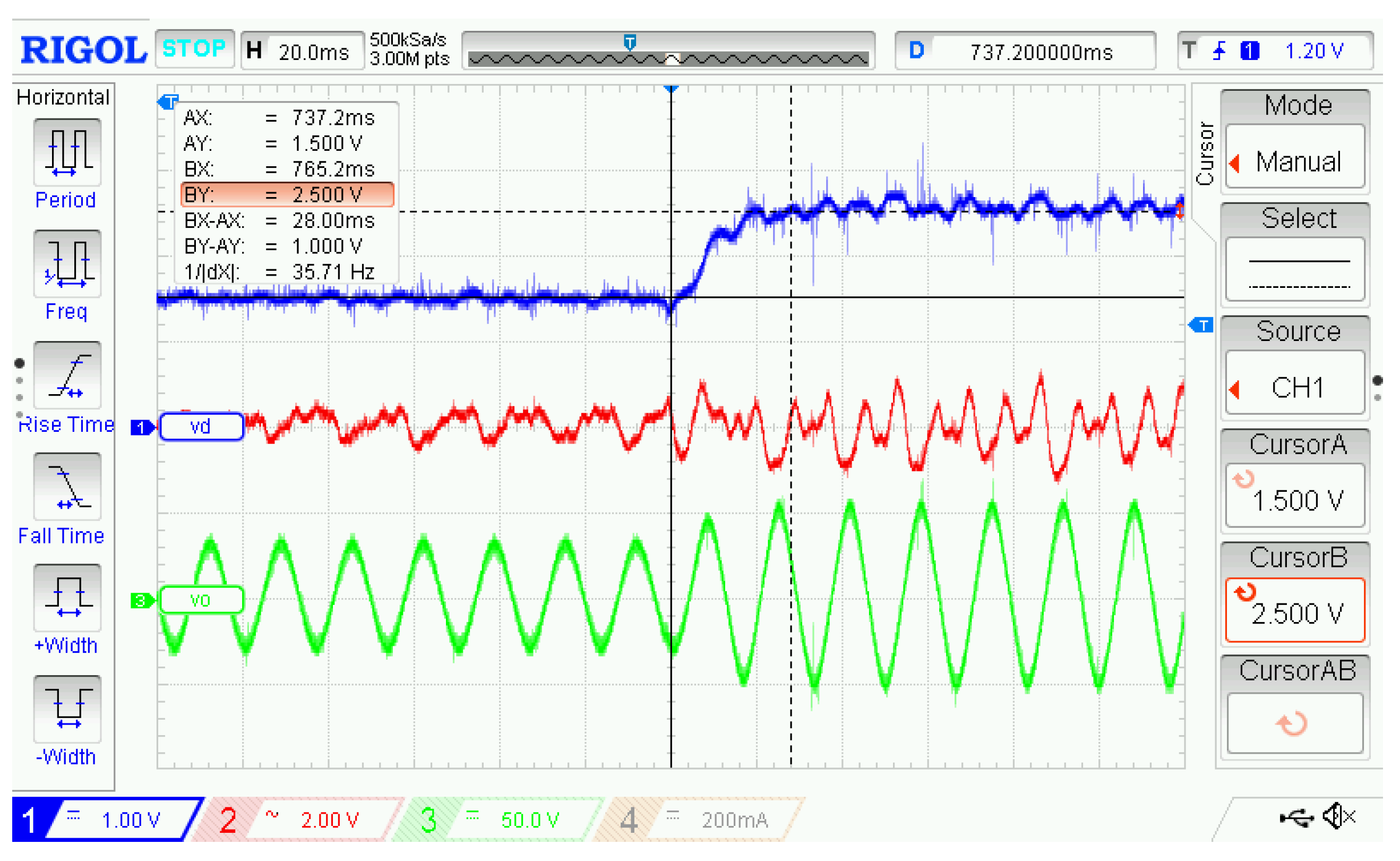

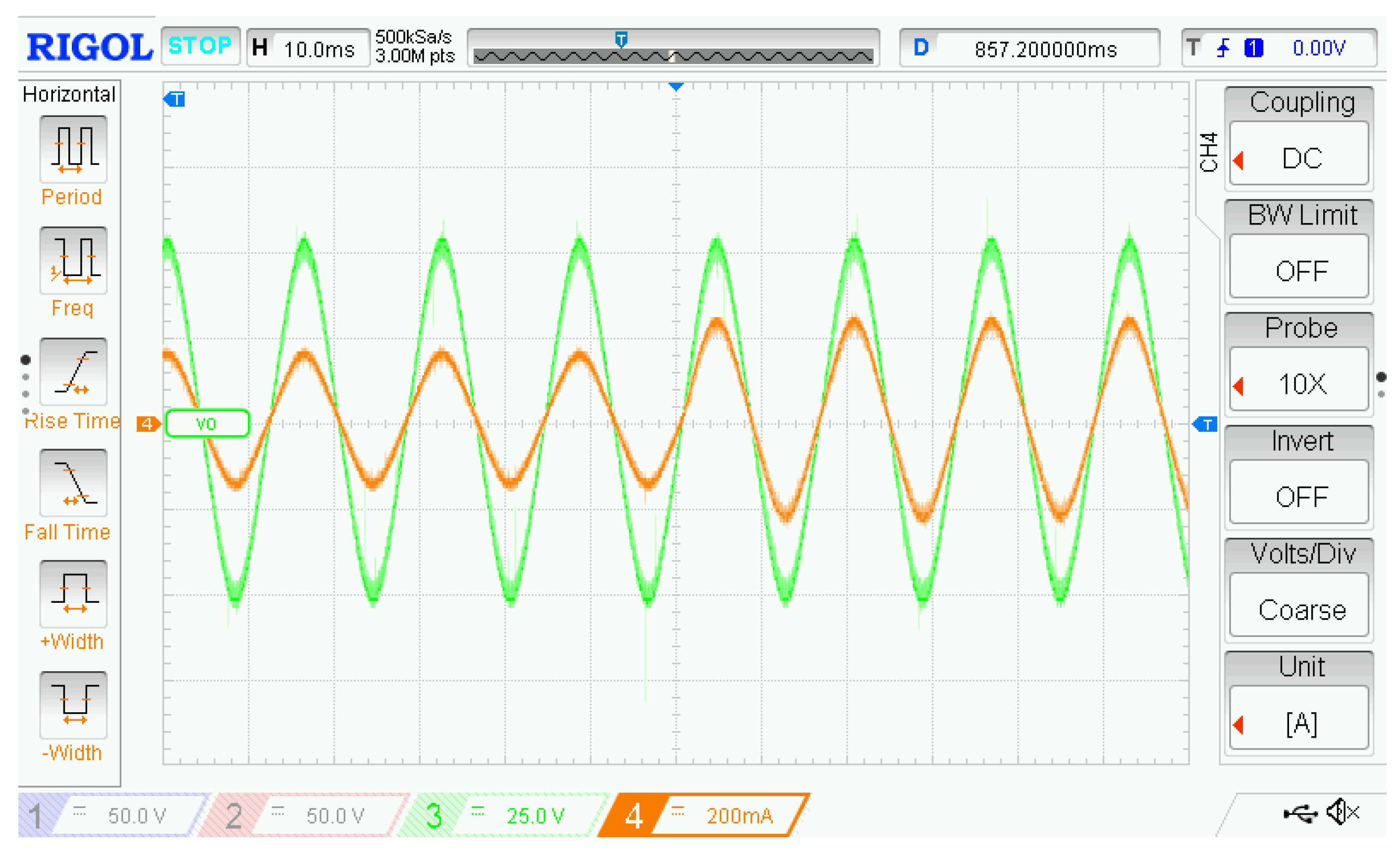

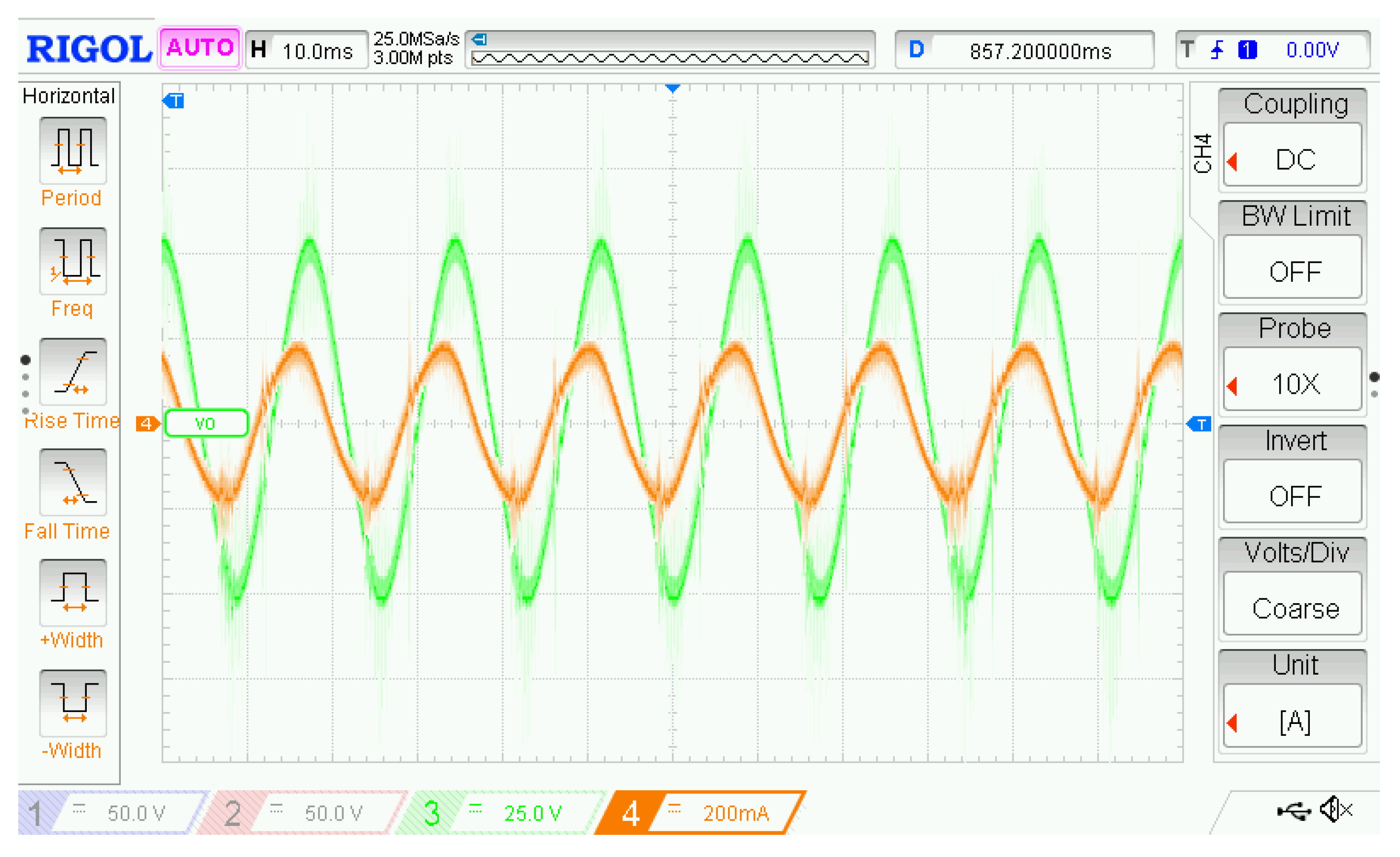

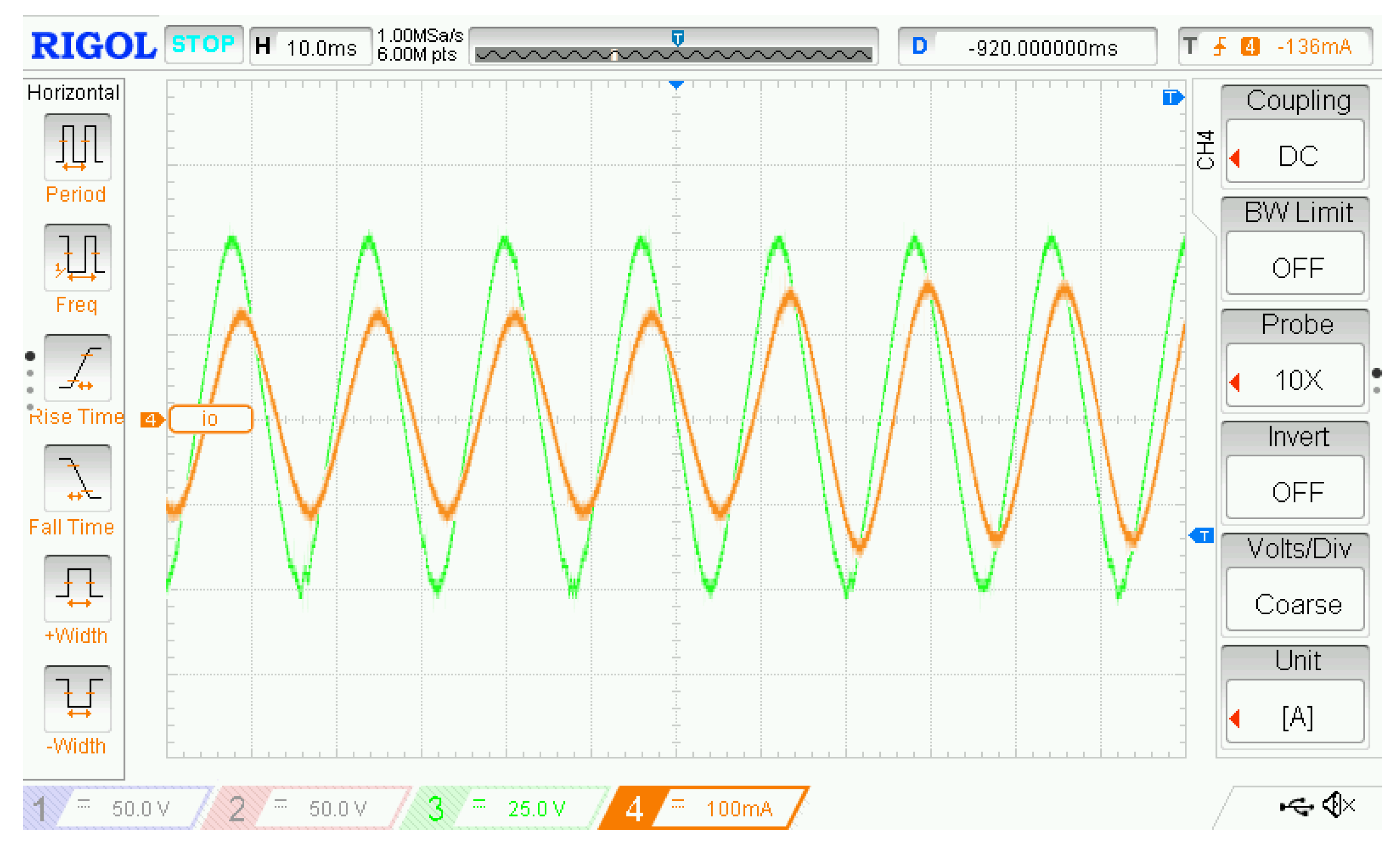

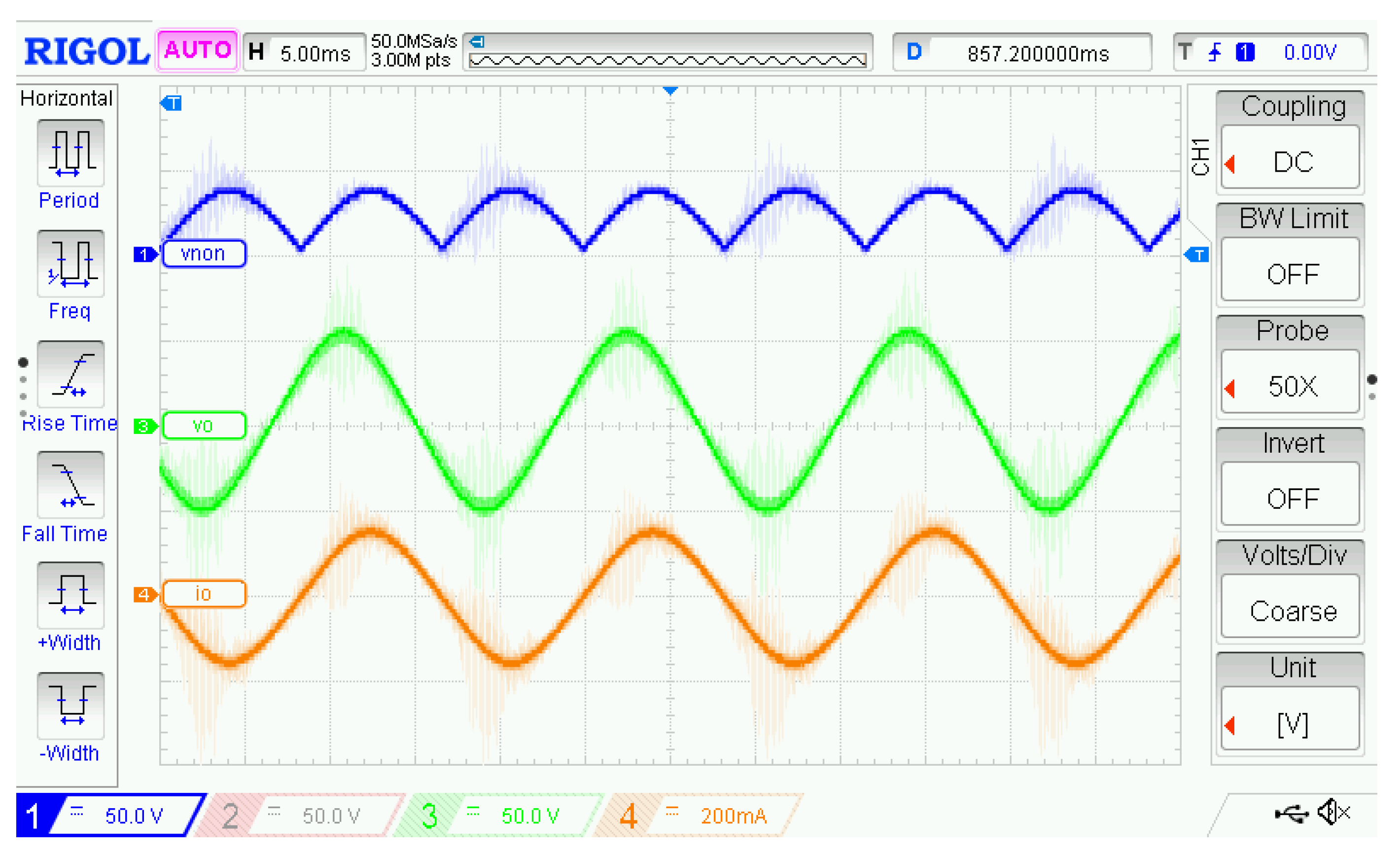

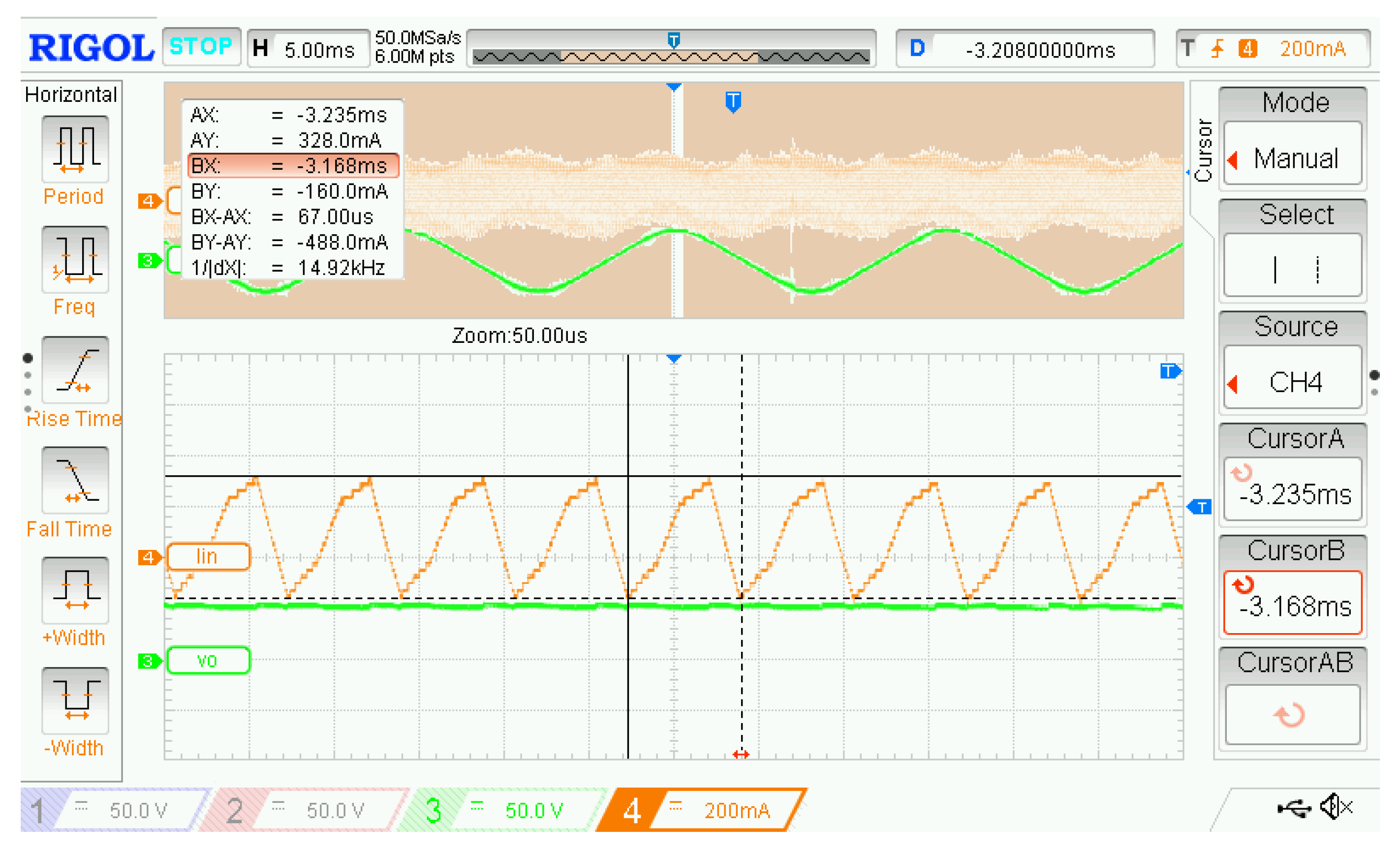

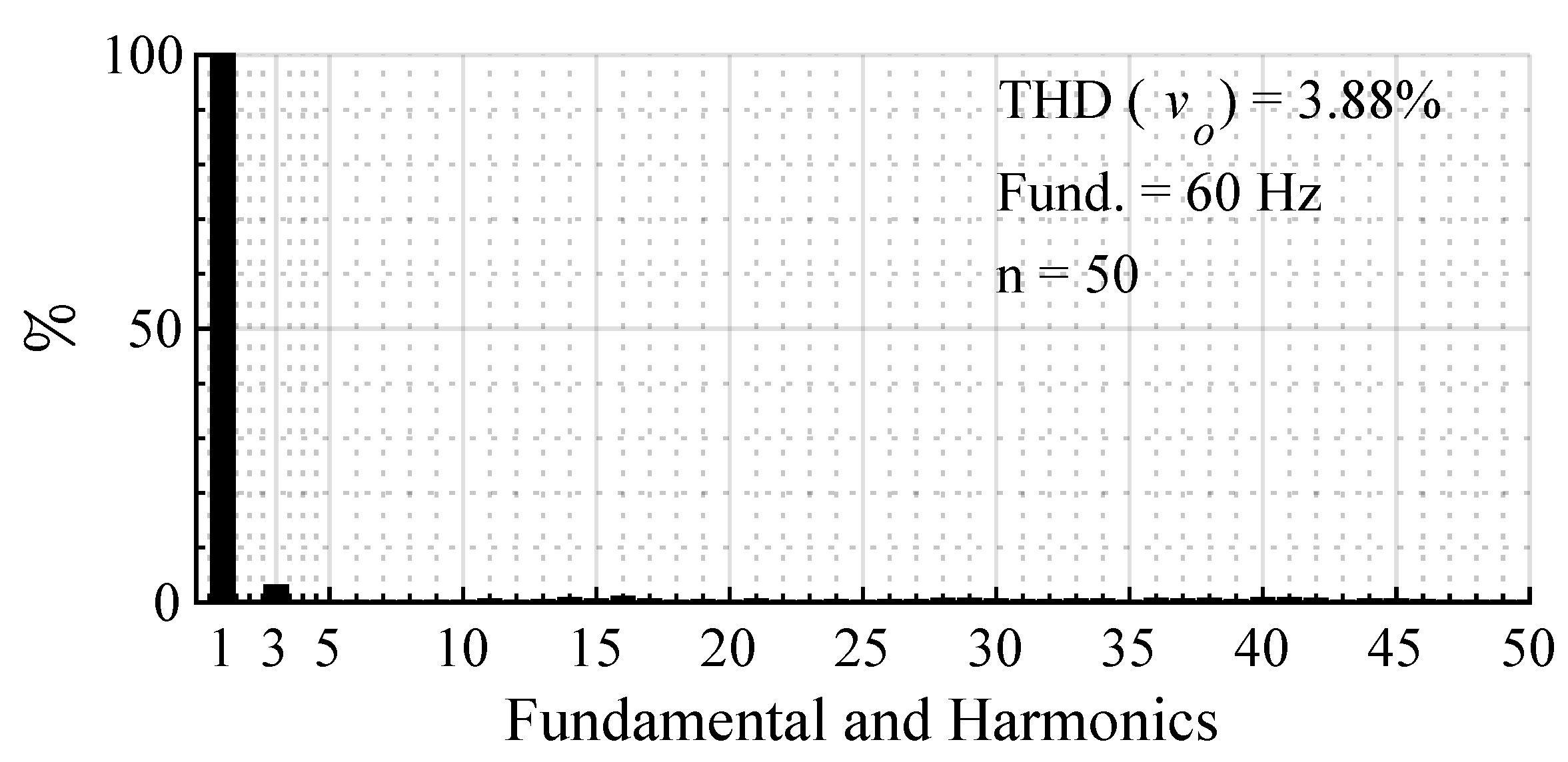

5.2. Experimental Results

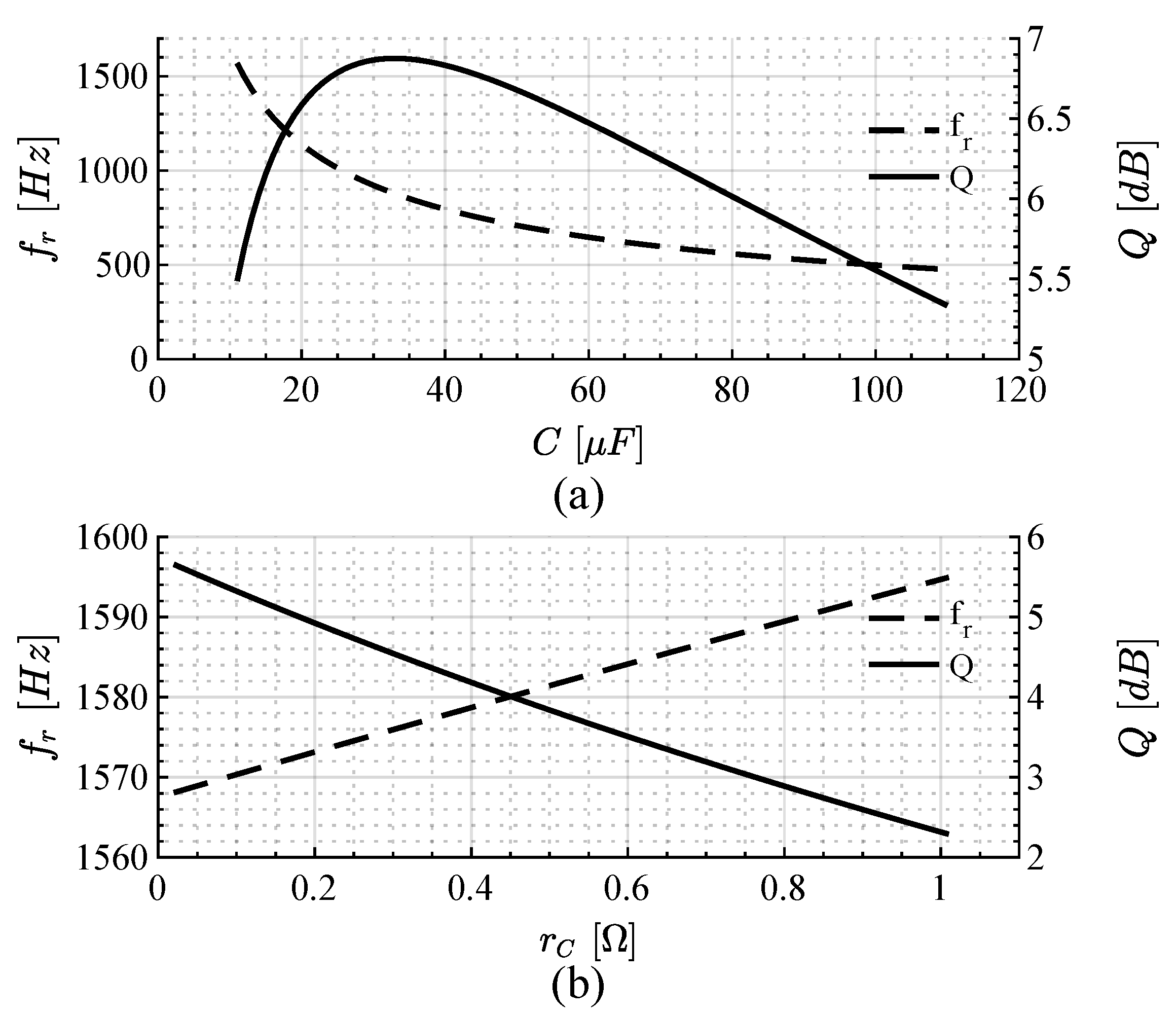

5.3. Stability Margins and Sensitivity

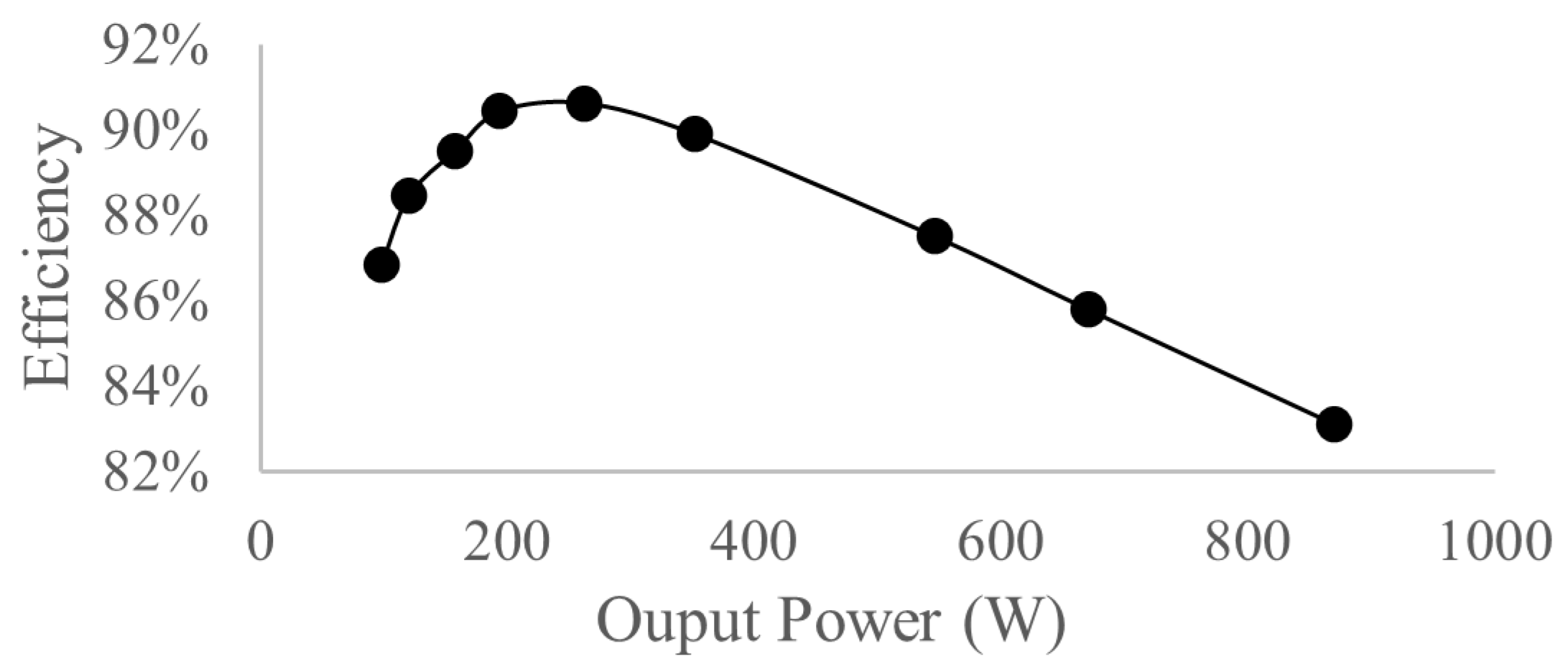

5.4. Loss Estimation and Efficiency

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Alajmi, B.N.; Ahmed, K.H.; Adam, G.P.; Williams, B.W. Single-Phase Single-Stage Transformer less Grid-Connected PV System. IEEE Trans. Power Electron. 2013, 28, 2664–2676. [Google Scholar] [CrossRef]

- Cáceres, R.; Barbi, I. A Boost DC-AC converter: Operation, analysis, control and experimentation. In Proceedings of the 1995 IEEE IECON 21st International Conference on Industrial Electronics, Control, and Instrumentation, Orlando, FL, USA, 6–10 November 1995; Volume 1, pp. 546–551. [Google Scholar]

- Xue, Y.; Chang, L.; Kjaer, S.; Bordonau, J.; Shimizu, T. Topologies of Single-Phase Inverters for Small Distributed Power Generators: An Overview. IEEE Trans. Power Electron. 2004, 19, 1305–1314. [Google Scholar] [CrossRef]

- Das, H.S.; Tan, C.W.; Yatim, A.H.M.; bin Muhamad, N.D. Analysis and control of boost inverter for fuel cell applications. In Proceedings of the IEEE International Conference on the Power and Energy (PECon), Melaka, Malaysia, 28–29 November 2016; pp. 455–460. [Google Scholar]

- Khan, A.A.; Cha, H.; Khan, U.A.; Kim, H.G. Four-switch buck-boost inverter for stand-alone and grid-connected single-phase PV systems. In Proceedings of the 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017—ECCE Asia), Kaohsiung, Taiwan, 3–7 June 2017; pp. 460–465. [Google Scholar]

- Singh, A.; Mirafzal, B. Three-phase single-stage boost inverter for direct drive wind turbines. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–7. [Google Scholar]

- Nguyen, M.K.; Tran, T.T. A Single-Phase Single-Stage Switched-Boost Inverter With Four Switches. IEEE Trans. Power Electron. 2018, 33, 6769–6781. [Google Scholar] [CrossRef]

- Silva, G.V.; Andrade, J.M.D.; Coelho, R.F.; Lazzarin, T.B. Switched-Capacitor Differential Boost Inverter: Design, Modeling, and Control. IEEE Trans. Ind. Electr. 2020, 67, 5421–5431. [Google Scholar] [CrossRef]

- Andrade, J.M.D.; Silva, G.V.; Coelho, R.F.; Lazzarin, T.B. The switched capacitor differential boost inverter applied to grid connection. Int. Trans. Electr. Energy Syst. 2020, e12752. [Google Scholar] [CrossRef]

- Chamarthi, P.; Rajeev, M.; Agarwal, V. A novel single stage zero leakage current transformer-less inverter for grid connected PV systems. In Proceedings of the 2015 IEEE 42nd Photovoltaic Specialist Conference (PVSC), New Orleans, LA, USA, 14–19 June 2015; pp. 1–5. [Google Scholar] [CrossRef]

- Jain, S.; Agarwal, V. A Single-Stage Grid Connected Inverter Topology for Solar PV Systems With Maximum Power Point Tracking. IEEE Trans. Power Electron. 2007, 22, 1928–1940. [Google Scholar] [CrossRef] [Green Version]

- Patel, H.; Agarwal, V. A Single-Stage Single-Phase Transformer-Less Doubly Grounded Grid-Connected PV Interface. IEEE Trans. Energy Convers. 2009, 24, 93–101. [Google Scholar] [CrossRef]

- Fang, Y.; Ma, X. A Novel PV Microinverter With Coupled Inductors and Double-Boost Topology. IEEE Trans. Power Electron. 2010, 25, 3139–3147. [Google Scholar] [CrossRef]

- Albea, C.; Gordillo, F. Control of the boost DC-AC converter with RL load by energy shaping. In Proceedings of the 2007 46th IEEE Conference on Decision and Control, New Orleans, LA, USA, 12–14 December 2007; pp. 2417–2422. [Google Scholar] [CrossRef] [Green Version]

- Cáceres, R.; Barbi, I. A boost DC-AC converter: Analysis, design, and experimentation. IEEE Trans. Power Electron. 1999, 14, 134–141. [Google Scholar] [CrossRef]

- Tang, Y.; Yao, W.; Blaabjerg, F. A dual mode operated boost inverter and its control strategy for ripple current reduction in single-phase uninterruptible power supplies. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, South Korea, 1–5 June 2015; pp. 2227–2234. [Google Scholar] [CrossRef]

- Vazquez, N.; Cortes, D.; Hernandez, C.; Alvarez, J.; Arau, J.; Alvarez, J. A new nonlinear control strategy for the boost inverter. In Proceedings of the IEEE 34th Annual Conference on Power Electronics Specialist, PESC’03, Acapulco, Mexico, 15–19 June 2003; Volume 3, pp. 1403–1407. [Google Scholar] [CrossRef]

- Sanchis, P.; Ursaea, A.; Gubia, E.; Marroyo, L. Boost DC-AC inverter: A new control strategy. IEEE Trans. Power Electron. 2005, 20, 343–353. [Google Scholar] [CrossRef]

- Liang, T.J.; Shyu, J.L.; Chen, J.F. A novel DC/AC boost inverter. In Proceedings of the 2002 37th Intersociety Energy Conversion Engineering Conference, IECEC’02, Washington, DC, USA, 29–31 July 2004; pp. 629–634. [Google Scholar]

- Sreekanth, T.; Lakshminarasamma, N.; Mishra, M.K. A Single-Stage Grid-Connected High Gain Buck–Boost Inverter With Maximum Power Point Tracking. IEEE Trans. Energy Convers. 2017, 32, 330–339. [Google Scholar] [CrossRef]

- Cortes, D.; Vázquez, N.; Alvarez-Gallegos, J. Dynamical sliding-mode control of the boost inverter. IEEE Trans. Ind. Electr. 2009, 56, 3467–3476. [Google Scholar] [CrossRef]

- Cáceres, R.; Barbi, I. Sliding mode controller for the boost inverter. In Proceedings of the V IEEE International Power Electronics Congress Technical Proceedings, CIEP 96, Cuernavaca, Mexico, 14–17 October 1996; pp. 247–252. [Google Scholar]

- Martínez-Salamero, L.; Valderrama-Blavi, H.; Flores-Bahamonde, F.; Bosque-Moncusi, J.M.; García, G. Using the sliding-mode control approach for analysis and design of the boost inverter. IET Power Electr. 2016, 9, 1625–1634. [Google Scholar] [CrossRef]

- Zhao, W.; Lu, D.D.C.; Agelidis, V.G. Current Control of Grid-Connected Boost Inverter With Zero Steady-State Error. IEEE Trans. Power Electron. 2011, 26, 2825–2834. [Google Scholar] [CrossRef]

- Khan, A.A.S.; Rahman, K.M. Voltage mode control of single phase boost inverter. In Proceedings of the 2008 International Conference on Electrical and Computer Engineering, Dhaka, Bangladesh, 20–22 December 2008; pp. 665–670. [Google Scholar]

- Cáceres, R.; Rojas, R.; Camacho, O. Robust PID control of a buck-boost DC-AC converter. In Proceedings of the INTELEC. Twenty-Second International Telecommunications Energy Conference (Cat. No.00CH37131), Phoenix, AZ, USA, 10–14 September 2000; pp. 180–185. [Google Scholar] [CrossRef]

- Jha, K.; Mishra, S.; Joshi, A. High-Quality Sine Wave Generation Using a Differential Boost Inverter at Higher Operating Frequency. IEEE Trans. Ind. Appl. 2015, 51, 373–384. [Google Scholar] [CrossRef]

- Twining, E.; Holmes, D. Grid current regulation of a three-phase voltage source inverter with an LCL input filter. IEEE Trans. Power Electron. 2003, 18, 888–895. [Google Scholar] [CrossRef] [Green Version]

- Tang, Y.; Bai, Y.; Kan, J.; Xu, F. Improved Dual Boost Inverter With Half Cycle Modulation. IEEE Trans. Power Electron. 2017, 32, 7543–7552. [Google Scholar] [CrossRef]

- Monfared, M.; Golestan, S.; Guerrero, J.M. Analysis, Design, and Experimental Verification of a Synchronous Reference Frame Voltage Control for Single-Phase Inverters. IEEE Trans. Ind. Electron. 2014, 61, 258–269. [Google Scholar] [CrossRef]

- Golestan, S.; Monfared, M.; Guerrero, J.M.; Joorabian, M. A D-Q synchronous frame controller for single-phase inverters. In Proceedings of the 2011 2nd Power Electronics, Drive Systems and Technologies Conference, Tehran, Iran, 16–17 February 2011; pp. 317–323. [Google Scholar] [CrossRef] [Green Version]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 3rd ed.; Springer International Publishing: Berlin, Germany, 2020. [Google Scholar] [CrossRef]

- Baier, C.R.; Torres, M.A.; Acuna, P.; Munoz, J.A.; Melin, P.E.; Restrepo, C.; Guzman, J.I. Analysis and Design of a Control Strategy for Tracking Sinusoidal References in Single-Phase Grid-Connected Current-Source Inverters. IEEE Trans. Power Electron. 2018, 33, 819–832. [Google Scholar] [CrossRef]

- Blooming, T.; Carnovale, D. Application of IEEE STD 519-1992 Harmonic Limits. In Proceedings of the Conference Record of 2006 Annual Pulp and Paper Industry Technical Conference, Appleton, WI, USA, 18–23 June 2006; pp. 1–9. [Google Scholar] [CrossRef]

- Iqbal, A.; Siddique, M.D.; Ali, J.S.M.; Mekhilef, S.; Lam, J. A New Eight Switch Seven Level Boost Active Neutral Point Clamped (8S-7L-BANPC) Inverter. IEEE Access 2020, 8, 203972–203981. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Ali, J.S.M.; Meraj, M.; Iqbal, A.; Al-Hitmi, M.A. A New Single Phase Single Switched-Capacitor Based Nine-Level Boost Inverter Topology With Reduced Switch Count and Voltage Stress. IEEE Access 2019, 7, 174178–174188. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sandeep, N.; Ali, J.S.M.; Iqbal, A.; Ahmed, M.; Ghoneim, S.S.M.; Al-Harthi, M.M.; Alamri, B.; et al. A Single DC Source Nine-Level Switched-Capacitor Boost Inverter Topology With Reduced Switch Count. IEEE Access 2020, 8, 5840–5851. [Google Scholar] [CrossRef]

| Component | Parameter | Value |

|---|---|---|

| Capacitors | 10 μF | |

| Capacitor ESR | 0.1 Ω | |

| Inductors | 270 μH | |

| Inductor ESR | 0.20 Ω | |

| MOSFET ‘on’ Resistance | 0.10 Ω | |

| Load Resistance | R | 50 Ω |

| Supply Voltage | 10 V |

| Component | Parameter | Value |

|---|---|---|

| Nominal frequency | 377 rad/s | |

| Switching frequency | 15 kHz | |

| Set point voltage | 25 V | |

| Closed loop bandwidth | 10.2 krad/s | |

| Phase margin | 45° |

| Loss Type | Component | Value | % |

|---|---|---|---|

| Conduction | Switch | 0.91 W | 3.64% |

| Switching | Switch | 0.01 W | 0.06% |

| Conduction | Switch | 0.55 W | 2.18% |

| Switching | Switch | 0.02 W | 0.04% |

| Copper loss | 9.60 W | 38% | |

| ESR loss | 1.53 W | 6.06% | |

| Per converter | 12.63 W | 50% | |

| Total | 25.26 W | 100% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rasheduzzaman, M.; Fajri, P.; Kimball, J.; Deken, B. Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter. Energies 2021, 14, 4098. https://doi.org/10.3390/en14144098

Rasheduzzaman M, Fajri P, Kimball J, Deken B. Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter. Energies. 2021; 14(14):4098. https://doi.org/10.3390/en14144098

Chicago/Turabian StyleRasheduzzaman, Md., Poria Fajri, Jonathan Kimball, and Brad Deken. 2021. "Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter" Energies 14, no. 14: 4098. https://doi.org/10.3390/en14144098

APA StyleRasheduzzaman, M., Fajri, P., Kimball, J., & Deken, B. (2021). Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter. Energies, 14(14), 4098. https://doi.org/10.3390/en14144098