Methods for the Separation of Failure Modes in Power-Cycling Tests of High-Power Transistor Modules Using Accurate Voltage Monitoring

Abstract

1. Introduction

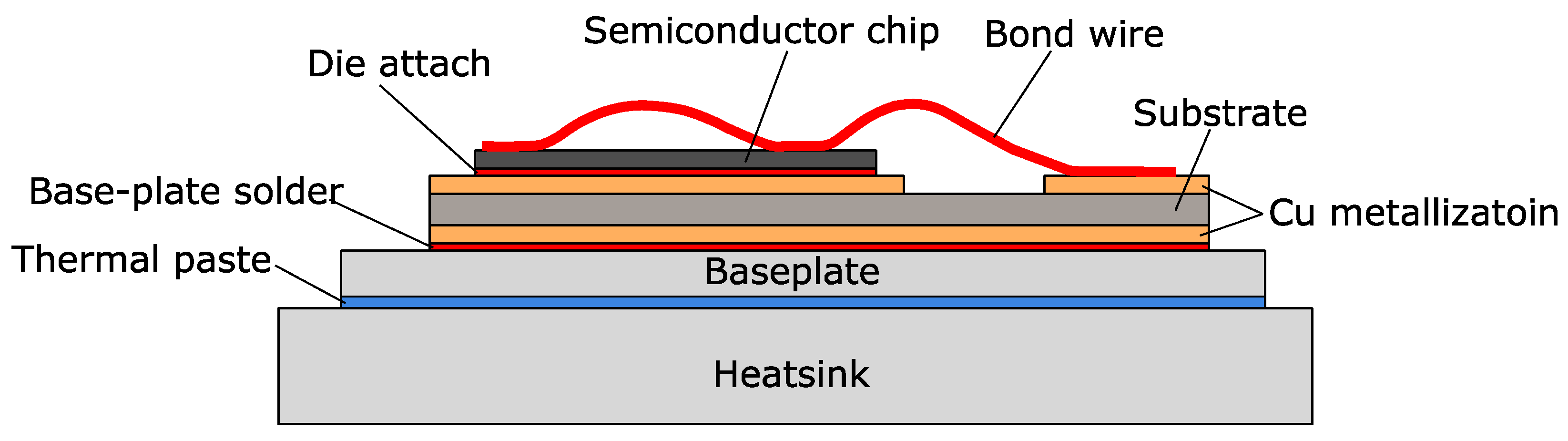

1.1. Possible Failure Mechanisms in an IGBT Module

1.2. The Most Commonly Used Reliability Test Methods

1.3. Overview Of Power-Cycling Solutions

2. Experimental Investigations

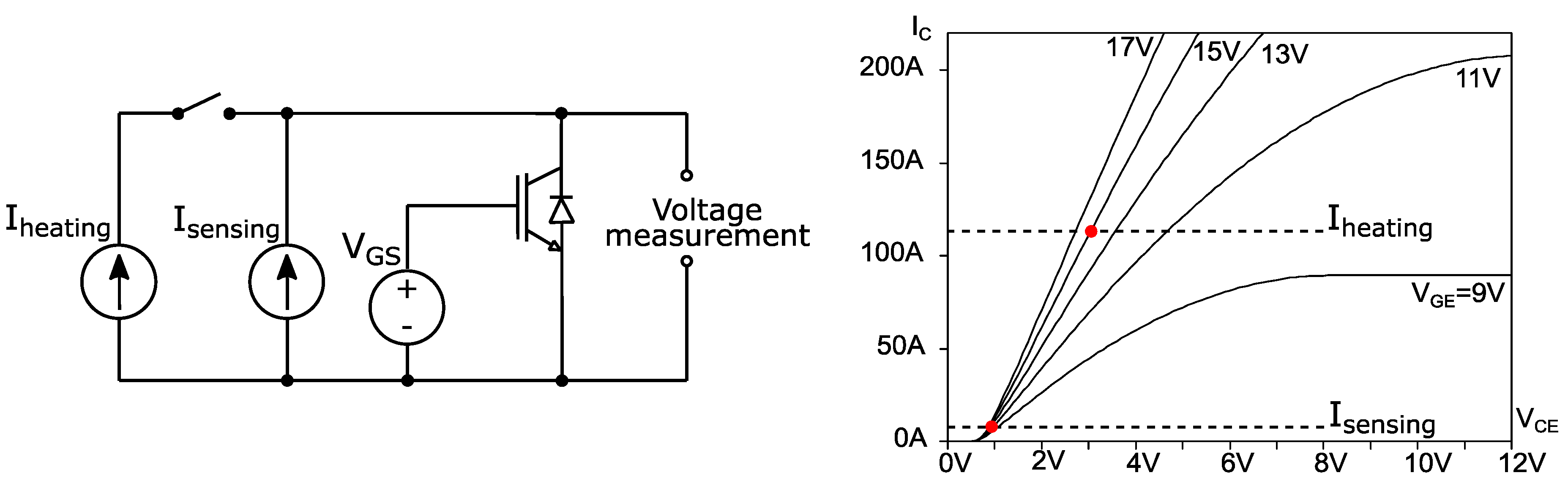

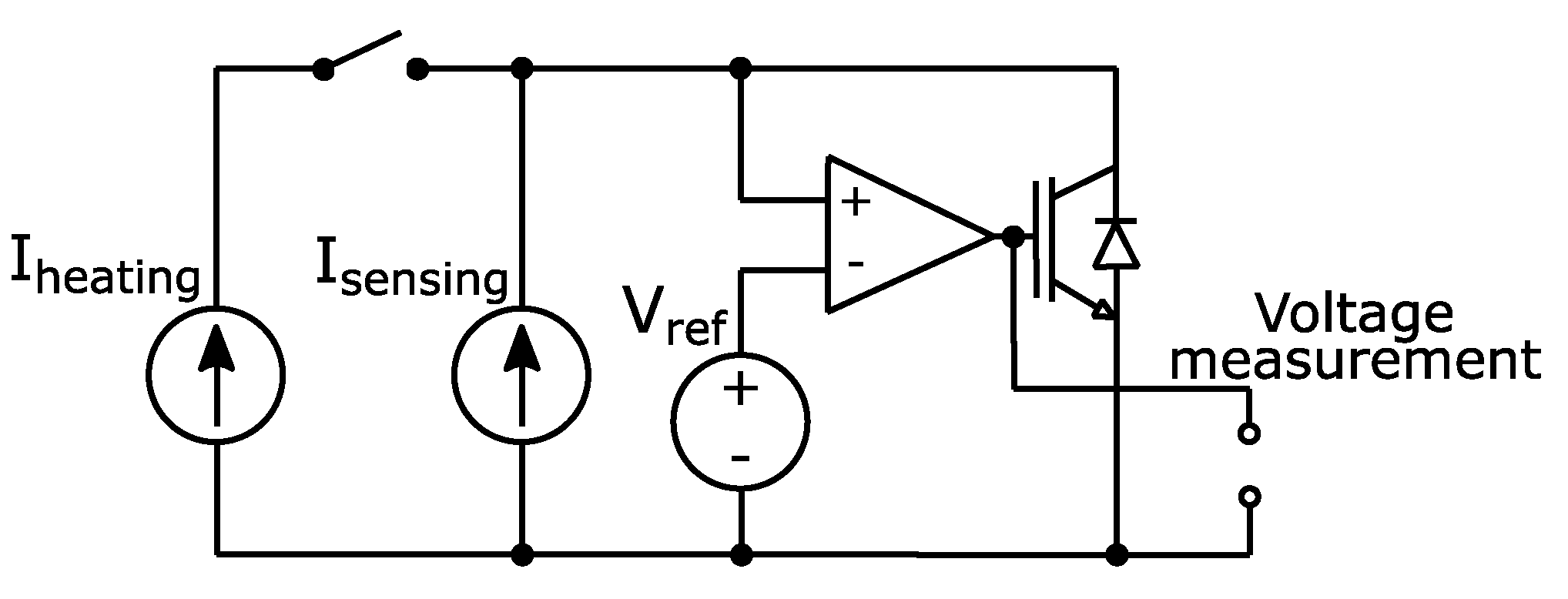

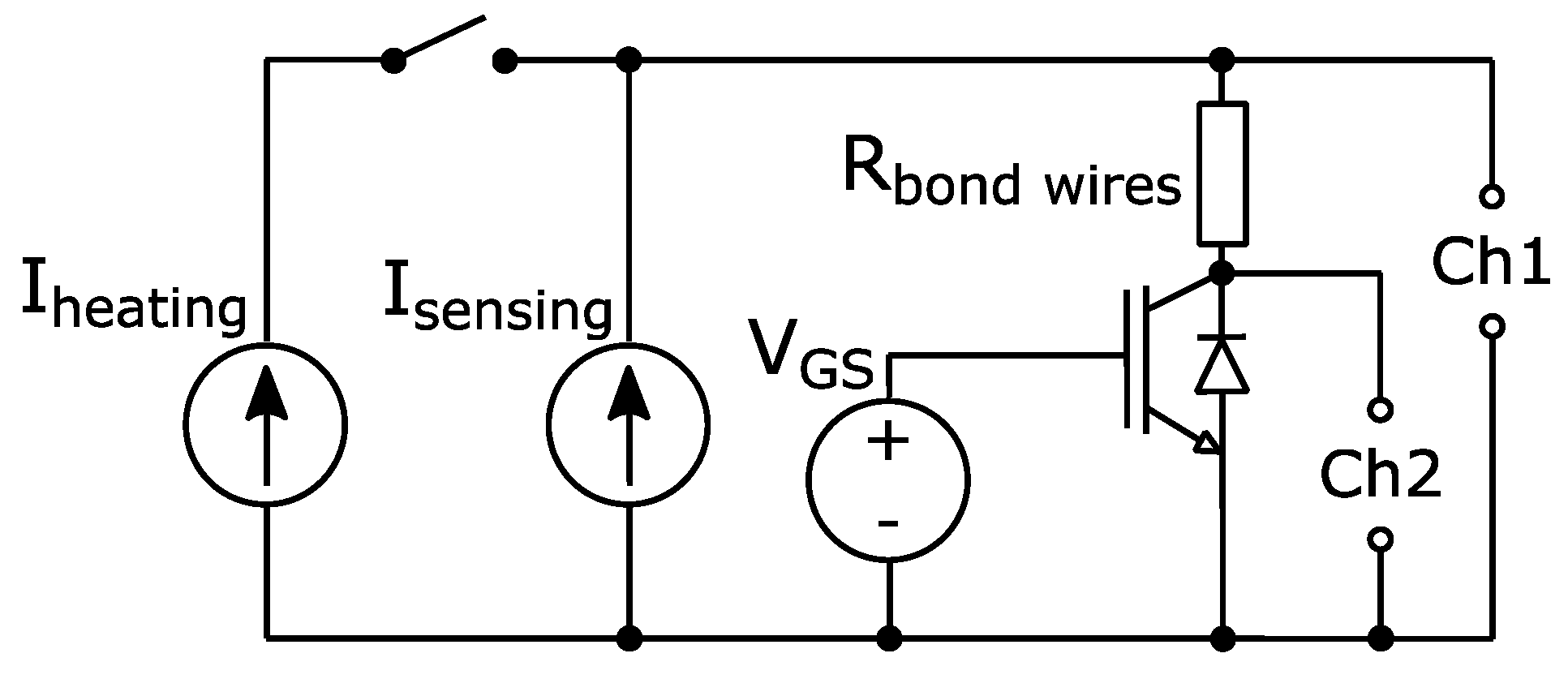

2.1. Electrical Setup

2.1.1. Current or Voltage Driving

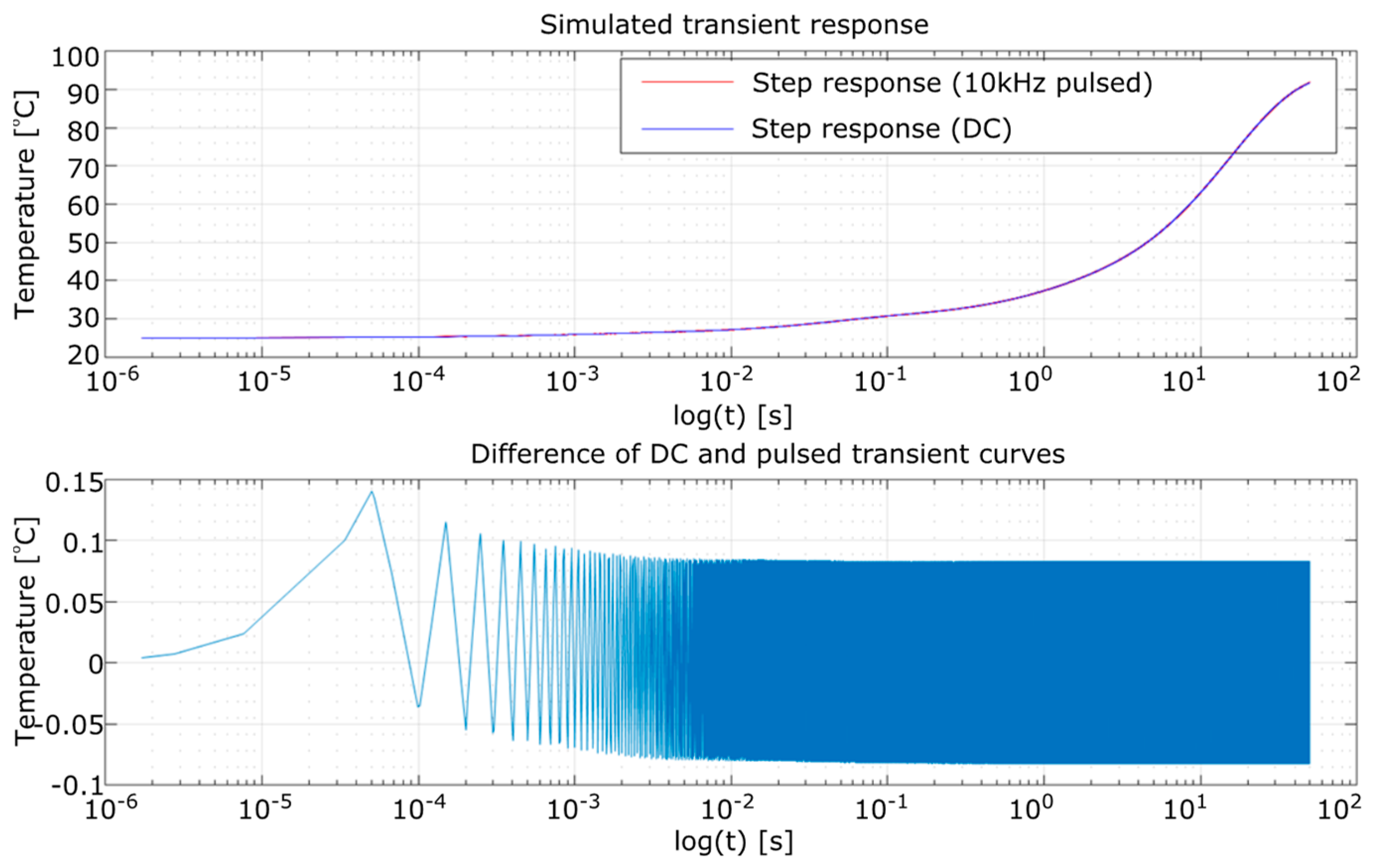

2.1.2. Pulsed or Direct Current (DC) Driving

2.2. Thermal Transient Measurement and Electrical Schemes

3. Discussion

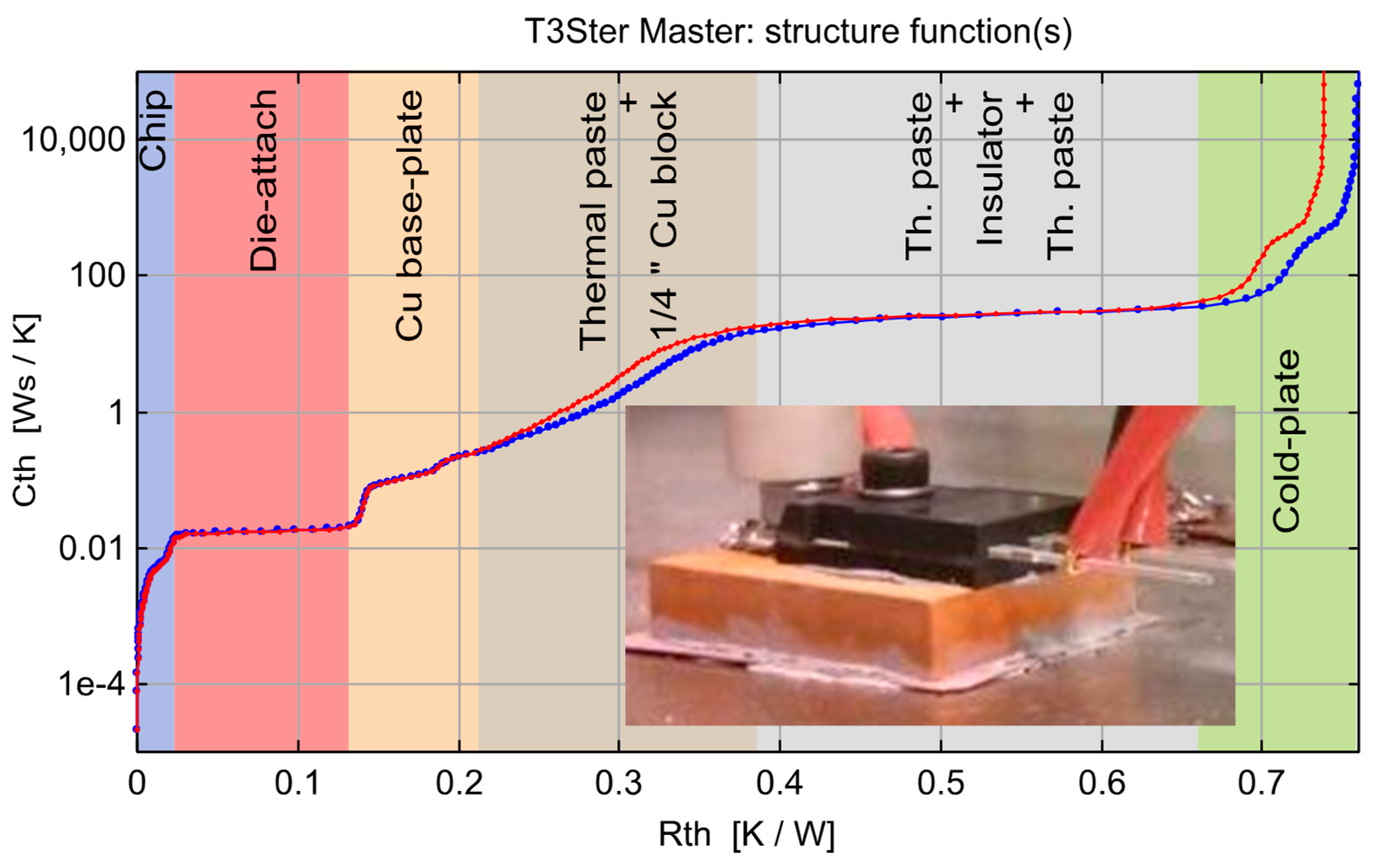

3.1. Structure Degradation in the Heat Flow Path

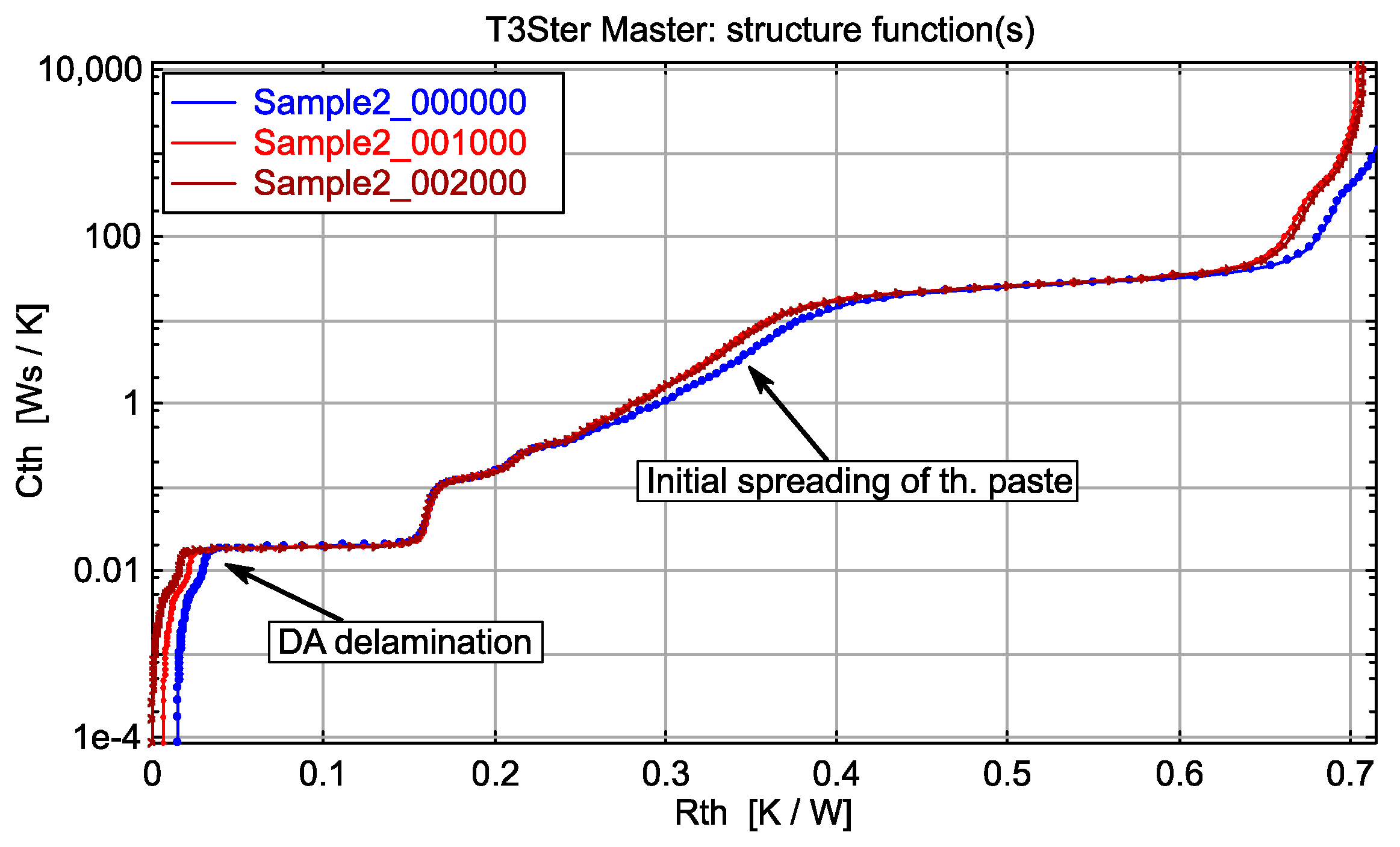

3.1.1. Die-Attach Degradation

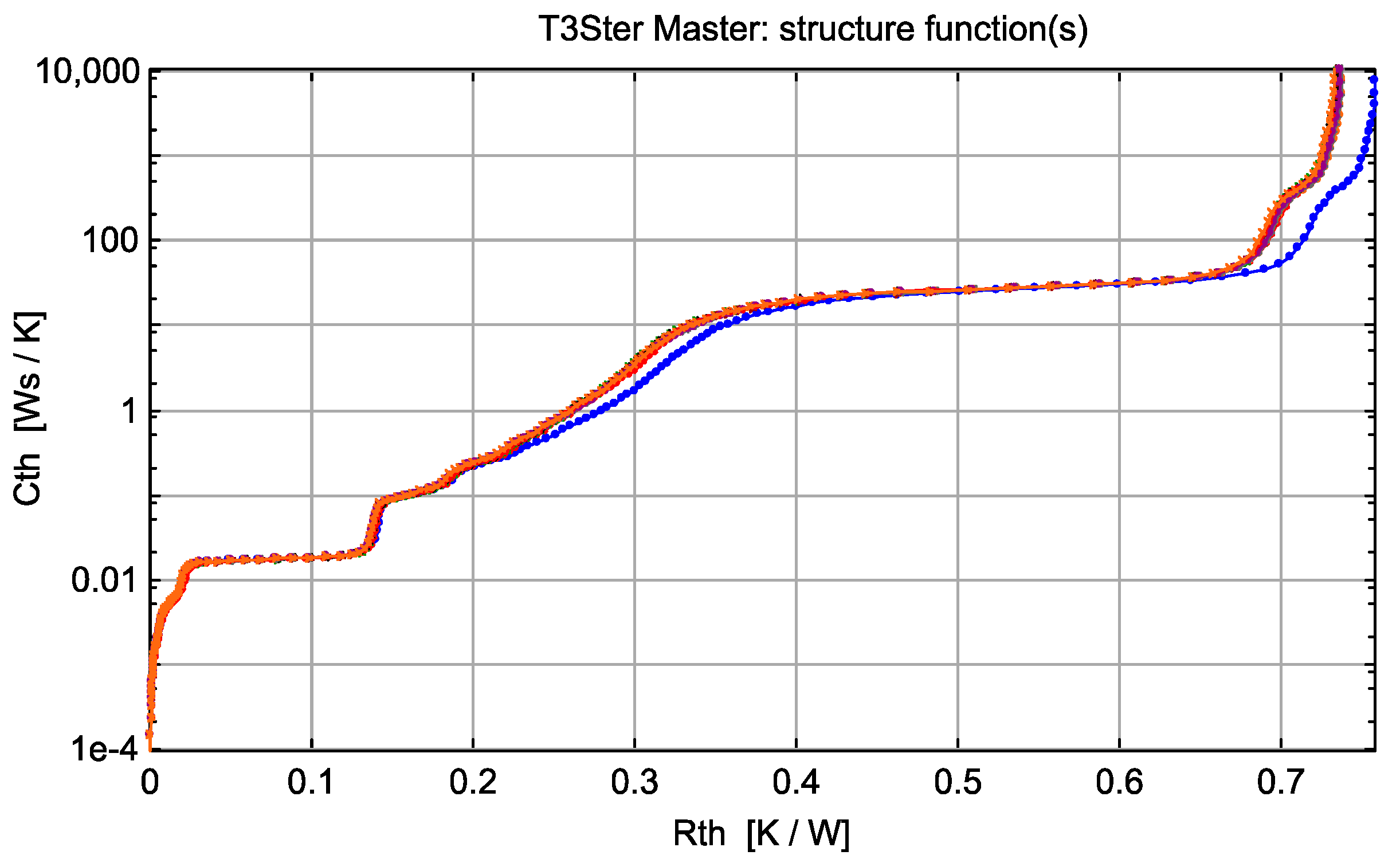

3.1.2. Baseplate Solder (TIM 2) Degradation

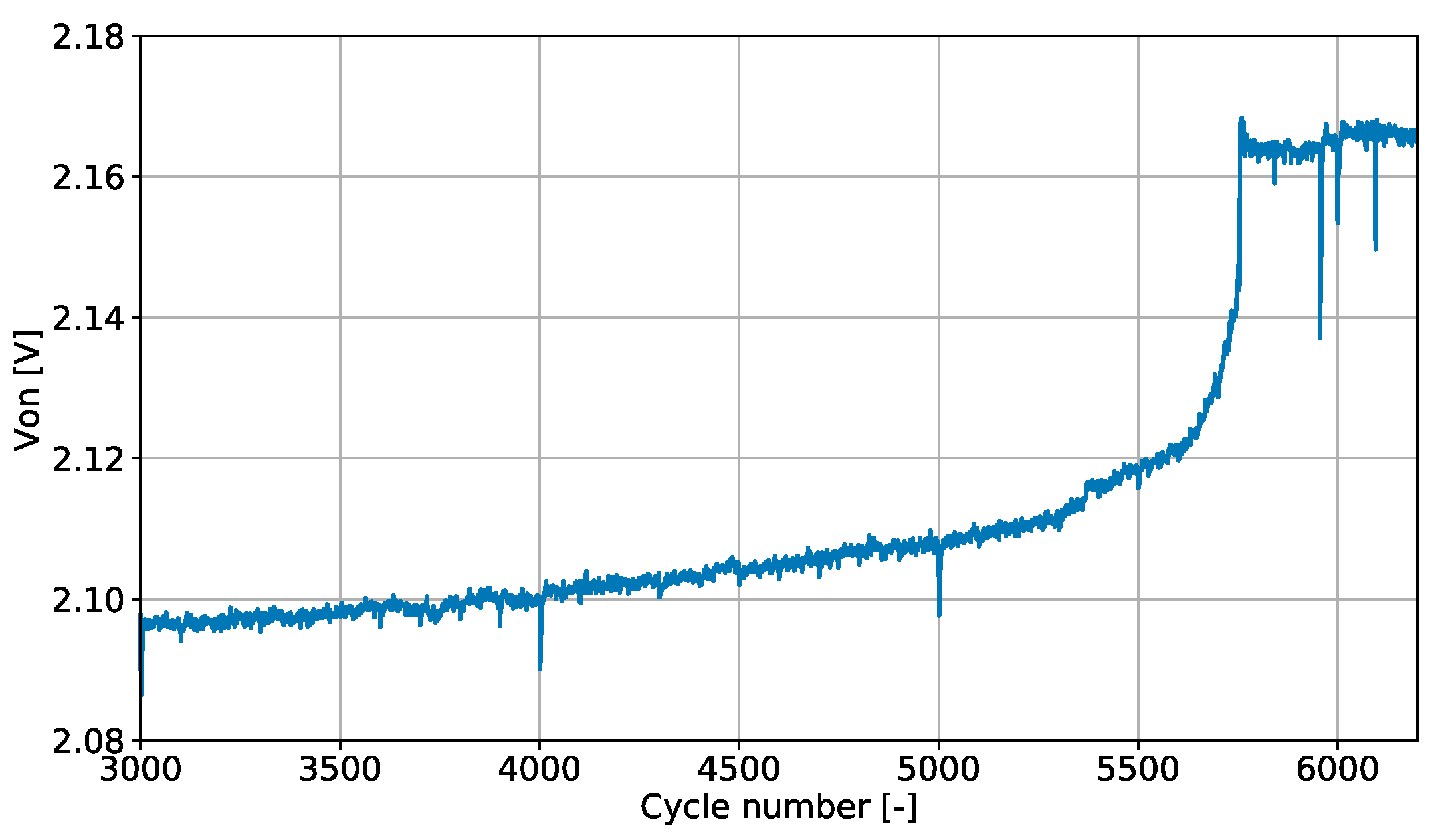

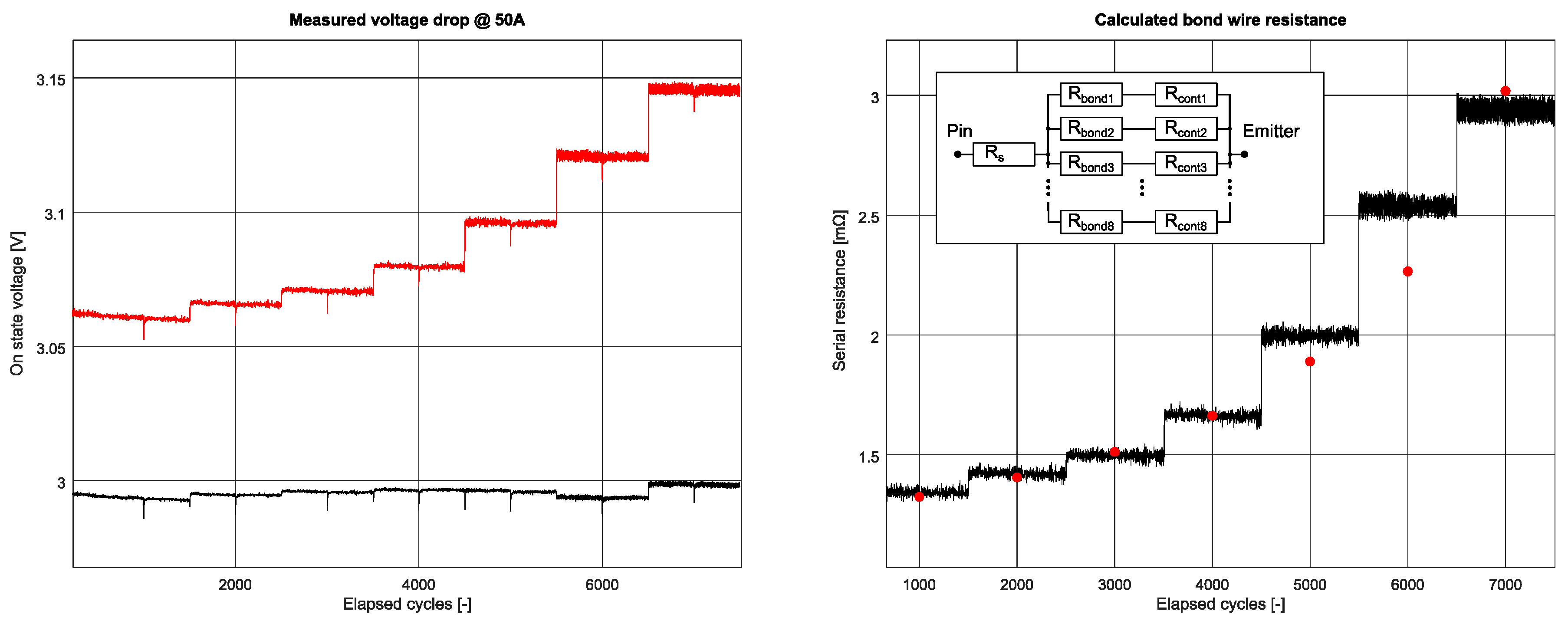

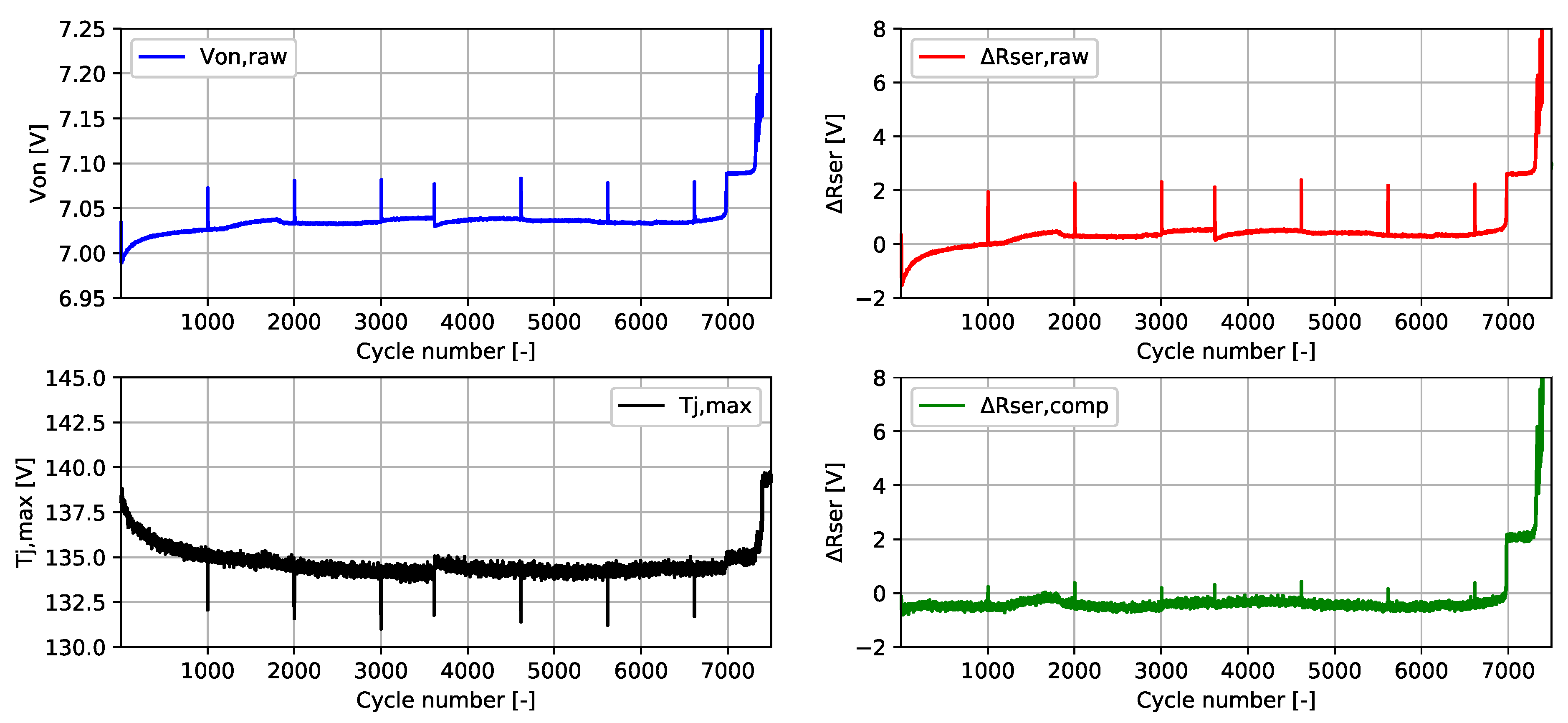

3.2. Bond-Wire Degradation and Separation of the Effects

3.2.1. Correction of the Von Voltage

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Wu, W.; Held, M.; Jacob, P.; Scacco, P.; Birolini, A. Investigation on the Long Term Reliability of Power IGBT Modules. In Proceedings of the International Symposium on Power Semiconductor Devices and IC’s: ISPSD’95, Yokohama, Japan, 23–25 May 1995; pp. 443–448. [Google Scholar] [CrossRef]

- Amro, R.; Lutz, J.; Rudzki, J.; Thoben, M.; Lindemann, A. Double-Sided Low-Temperature Joining Technique for Power Cycling Capability at High Temperature. In Proceedings of the 2005 European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005. [Google Scholar] [CrossRef]

- Schutze, T.; Berg, H.; Hierholzer, M. Further improvements in the reliability of IGBT modules. In Proceedings of the Conference Record of 1998 IEEE Industry Applications Conference, Thirty-Third IAS Annual Meeting, St. Louis, MO, USA, 12–15 October 1998; Volume 2, pp. 1022–1025. [Google Scholar] [CrossRef]

- Liu, Y.; Irving, S.; Desbiens, D.; Luk, T.; How, N.S.; Kwon, Y.; Lee, S. Impact of the die attach process on power & thermal cycling for a discrete style semiconductor package. EuroSimE 2005. In Proceedings of the 6th International Conference on Thermal, Mechanial and Multi-Physics Simulation and Experiments in Micro-Electronics and Micro-Systems, Berlin, Germany, 18–20 April 2005; pp. 221–226. [Google Scholar] [CrossRef]

- Guth, K.; Mahnke, P. Improving the thermal reliability of large area solder joints in IGBT power modules. In Proceedings of the 4th International Conference on Integrated Power Systems, Naples, Italy, 7–9 June 2006; Available online: https://ieeexplore.ieee.org/document/5758032 (accessed on 25 April 2020).

- Czerny, B.; Lederer, M.; Nagl, B.; Trnka, A.; Khatibi, G.; Thoben, M. Thermo-mechanical analysis of bonding wires in IGBT modules under operating conditions. Microelectron. Rel. 2012, 52, 2353–2357. [Google Scholar] [CrossRef]

- Davis, R.I.; Sprenger, D.I. Methodology and apparatus for rapid power cycle accumulation and in-situ incipient failure monitoring for power electronics modules. In Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 1996–2002. [Google Scholar]

- Forest, F.; Huselstein, J.J.; Faucher, S.; Elghazouani, M.; Ladoux, P.; Meynard, T.A.; Richardeau, F.; Turpin, C. Use of opposition method in the test of high-power electronic converters. IEEE Trans. Ind. Electron. 2016, 53, 530–541. [Google Scholar] [CrossRef]

- Schuler, S.; Scheuermann, U. Impact of Test Control Strategy on Power Cycling Lifetime. Proc. PCIM 2010, 57, 355–360. [Google Scholar]

- Baker, N. An Electrical Method for Junction Temperature Measurement of Power Semiconductor Switches. Ph.D. Thesis, Aalborg Universitet, Aalborg, Denmark, February 2016. [Google Scholar]

- Khatir, Z.; Carubelli, S.; Lecoq, F. Real-time computation of thermal constraints in multichip power electronic devices. IEEE Trans. Compon. Packag. Technol. 2004, 27, 337–344. [Google Scholar] [CrossRef]

- Kim, Y.S.; Sul, S.K. On-line estimation of IGBT junction temperature using on-state voltage drop. In Proceedings of the Conference Record of 1998 IEEE Industry Applications Conference, Thirty-Third IAS Annual Meeting (Cat. No.98CH36242), St. Louis, MO, USA, 12–15 October 1998; Volume 2, pp. 853–859. [Google Scholar]

- Schmidt, R.; Scheuermann, U. Using the chip as a temperature sensor—The influence of steep lateral temperature gradients on the Vce(T)-measurement. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–9. [Google Scholar]

- Ogawa, E.; Nakayama, T.; Yoshida, S.; Takenoiri, S.; Ewald, S.; Otsuki, M. Ultra-high accuracy on-chip temperature sensor in RC-IGBT module for xEV, PCIM Europe 2019. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 7–9 May 2019; pp. 1–4. [Google Scholar]

- Schmidt, R.; Scheuermann, U. Separating Failure Modes in Power Cycling Tests. In Proceedings of the 2012 7th International Conference on Integrated Power Electronics Systems (CIPS), Nuremberg, Germany, 6–8 March 2012; pp. 1–6. [Google Scholar]

- Musallam, M.; Yin, C.; Bailey, C.; Johnson, M. Mission Profile-Based Reliability Design and Real-Time Life Consumption Estimation in Power Electronics. IEEE Trans. Power Electron. 2015, 30, 2601–2613. [Google Scholar] [CrossRef]

- Ciappa, M. Lifetime prediction on the base of mission profiles. Microelectron. Reliab. 2015, 45, 1293–1298. [Google Scholar] [CrossRef]

- Standard Practices for Cycle Counting in Fatigue Analysis, ASTM E1049-85. 2017. Available online: https://www.astm.org/Standards/E1049 (accessed on 21 May 2020).

- Musallam, M.; Johnson, M. An Efficient Implementation of the Rainflow Counting Algorithm for Life Consumption Estimation. Reliability. IEEE Trans. Reliab. 2012, 61, 978–986. [Google Scholar] [CrossRef]

- Miner, M.A. Cumulative Damage in Fatigue. J. Appl. Mech. 1945, 67, A159–A164. [Google Scholar]

- Fatemi, A.; Yang, L. Cumulative fatigue damage and life prediction theories: A survey of the state of the art for homogeneous materials. Int. J. Fatigue 1998, 20, 9–34. [Google Scholar] [CrossRef]

- Feix, G.; Dieckerhoff, S.; Allmeling, J.; Schonberger, J. Simple methods to calculate IGBT and diode conduction and switching losses. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009. [Google Scholar]

- Menhart, S. Using SPICE to calculate MOSFET operating temperature PESC ’92 Record. In Proceedings of the 23rd Annual IEEE Power Electronics Specialists Conference, Toledo, Spain, 29 June–3 July 1992; pp. 901–906. [Google Scholar] [CrossRef]

- Szekely, V.; Torok, S.; Nikodemusz, E.; Farkas, G.; Rencz, M. Measurement and evaluation of thermal transients, IMTC 2001. In Proceedings of the 18th IEEE Instrumentation and Measurement Technology Conference. Rediscovering Measurement in the Age of Informatics (Cat. No.01CH 37188), Budapest, Hungary, 21–23 May 2001; Volume 1, pp. 210–215. [Google Scholar] [CrossRef]

- Herold, C.; Beier, M.; Lutz, J.; Hensler, A. Improving the accuracy of junction temperature measurement with the square-root-t method. In Proceedings of the 19th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Berlin, Germany, 25–27 September 2013; pp. 92–94. [Google Scholar]

- Rencz, M.R.; Szekely, V. Measuring partial thermal resistances in a heat-flow path. IEEE Trans. Compon. Packag. Technol. 2002, 25, 547–553. [Google Scholar] [CrossRef]

- Farkas, G.; Sarkany, Z.; Rencz, M. Structural Analysis of Power Devices and Assemblies by Thermal Transient Measurements. Energies 2019, 12, 2696. [Google Scholar] [CrossRef]

- Szekely, V. Identification of RC networks by deconvolution: Chances and limits. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1998, 45, 244–258. [Google Scholar] [CrossRef]

- Schweitzer, D.; Pape, H.; Kutscherauer, R.; Walder, M. How to evaluate transient dual interface measurements of the Rth-JC of power semiconductor packages. In Proceedings of the 2009 25th Annual IEEE Semiconductor Thermal Measurement and Management Symposium, San Jose, CA, USA, 15–19 March 2009; pp. 172–179. [Google Scholar] [CrossRef]

- Ciappa, M.; Malberti, P. Plastic-strain of aluminium interconnections during pulsed operation of IGBT multichip modules. Qual. Reliab. Eng. Int. 1996, 12, 297–303. [Google Scholar] [CrossRef]

- Schneider-Ramelow, M.; Baumann, T.; Hoene, E. Design and assembly of power semiconductors with double-sided water cooling, Integrated Power Systems (CIPS). In Proceedings of the 5th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 11–13 March 2008; pp. 1–7. Available online: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5755676&isnumber=5755665 (accessed on 25 April 2020).

| Stage | R (K/W) | C (Ws/K) |

|---|---|---|

| 1 | 1.45 × 10−3 | 8.86 × 10−2 |

| 2 | 3.3 × 10−3 | 2.79 × 10−1 |

| 3 | 1.47 × 10−2 | 2.45 |

| 4 | 3.98 × 10−2 | 28.30 |

| 5 | 0.71 × 10−1 | 5.74 × 10−1 |

| Parameter | Value |

|---|---|

| Device type | SiC MOSFET |

| Rated current | 60 A |

| Number of parallel chips | 1 |

| Number of bond wires | 3 |

| Measurement mode | On state |

| Parameter | Value |

|---|---|

| Device type | Si IGBT |

| Rated current | 80 A |

| Number of parallel chips | 1 |

| Number of bond wires | 8 |

| Measurement mode | On state |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sarkany, Z.; Rencz, M. Methods for the Separation of Failure Modes in Power-Cycling Tests of High-Power Transistor Modules Using Accurate Voltage Monitoring. Energies 2020, 13, 2718. https://doi.org/10.3390/en13112718

Sarkany Z, Rencz M. Methods for the Separation of Failure Modes in Power-Cycling Tests of High-Power Transistor Modules Using Accurate Voltage Monitoring. Energies. 2020; 13(11):2718. https://doi.org/10.3390/en13112718

Chicago/Turabian StyleSarkany, Zoltan, and Marta Rencz. 2020. "Methods for the Separation of Failure Modes in Power-Cycling Tests of High-Power Transistor Modules Using Accurate Voltage Monitoring" Energies 13, no. 11: 2718. https://doi.org/10.3390/en13112718

APA StyleSarkany, Z., & Rencz, M. (2020). Methods for the Separation of Failure Modes in Power-Cycling Tests of High-Power Transistor Modules Using Accurate Voltage Monitoring. Energies, 13(11), 2718. https://doi.org/10.3390/en13112718