Harmonic-Reduced Bias Circuit for Ultrasound Transducers

Abstract

1. Introduction

2. Materials and Methods

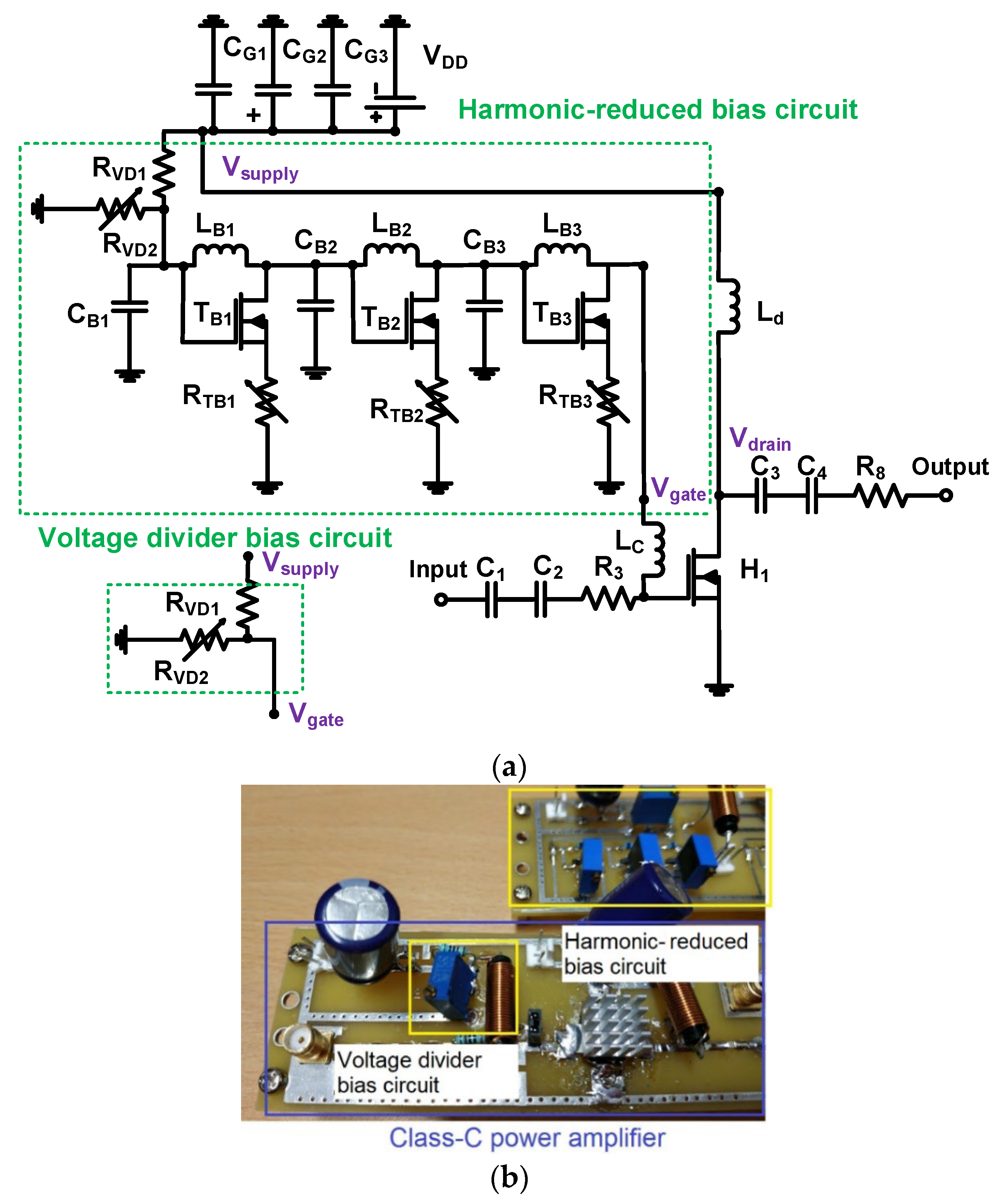

2.1. The Class-C Power Amplifier Fabrication

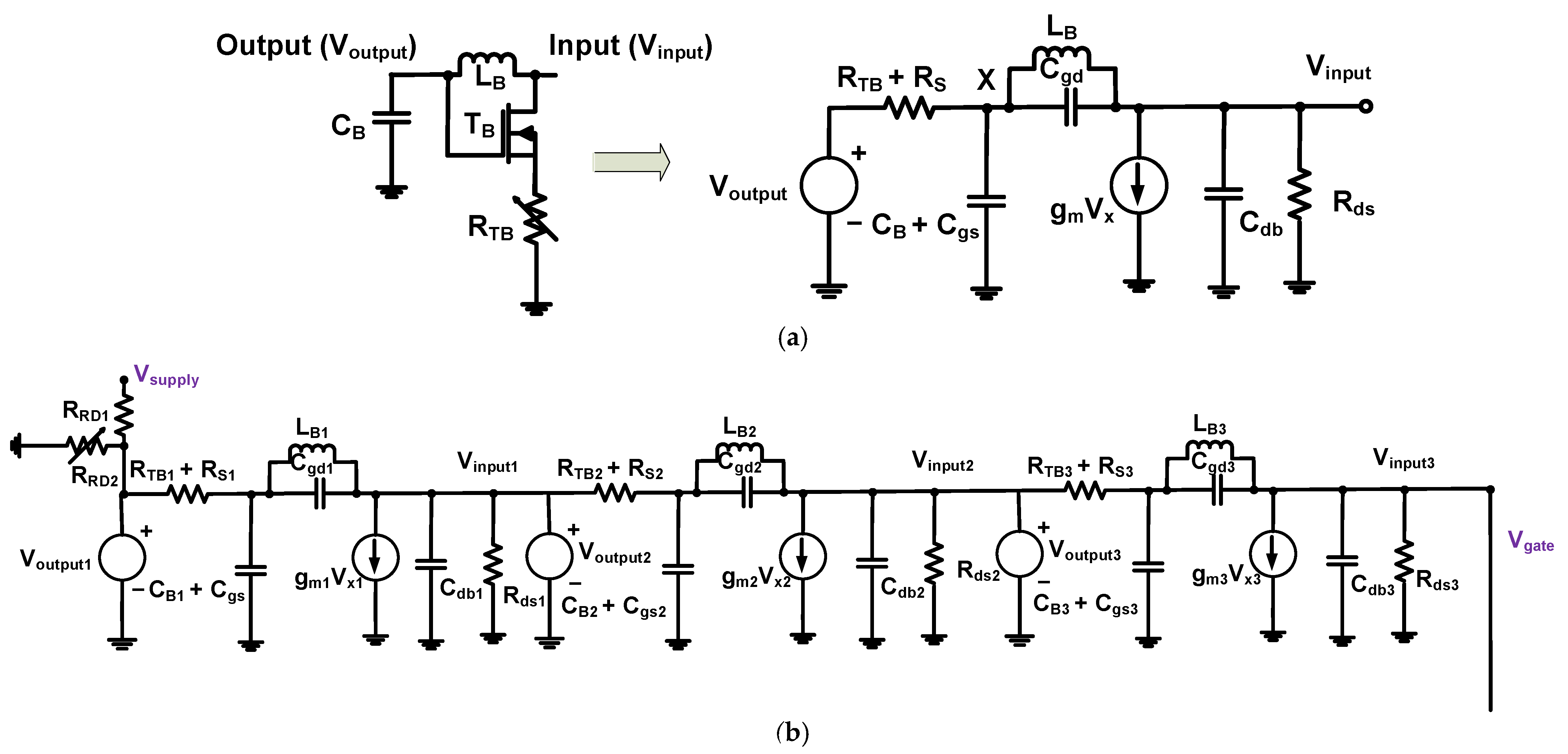

2.2. Equivalent Circuit Analysis of Bias Circuits

3. Results and Discussion

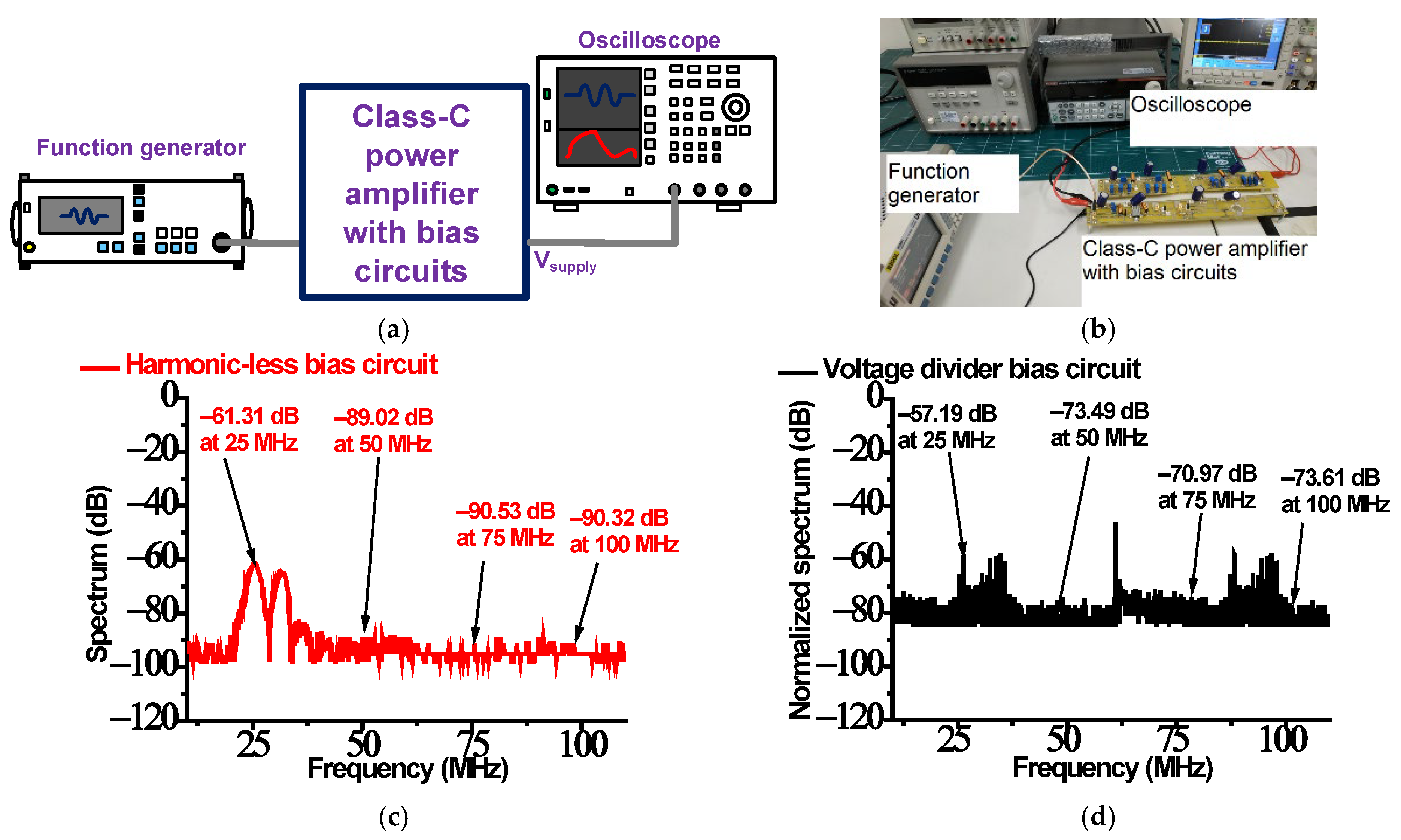

3.1. Performance Evaluation of the Bias Circuits

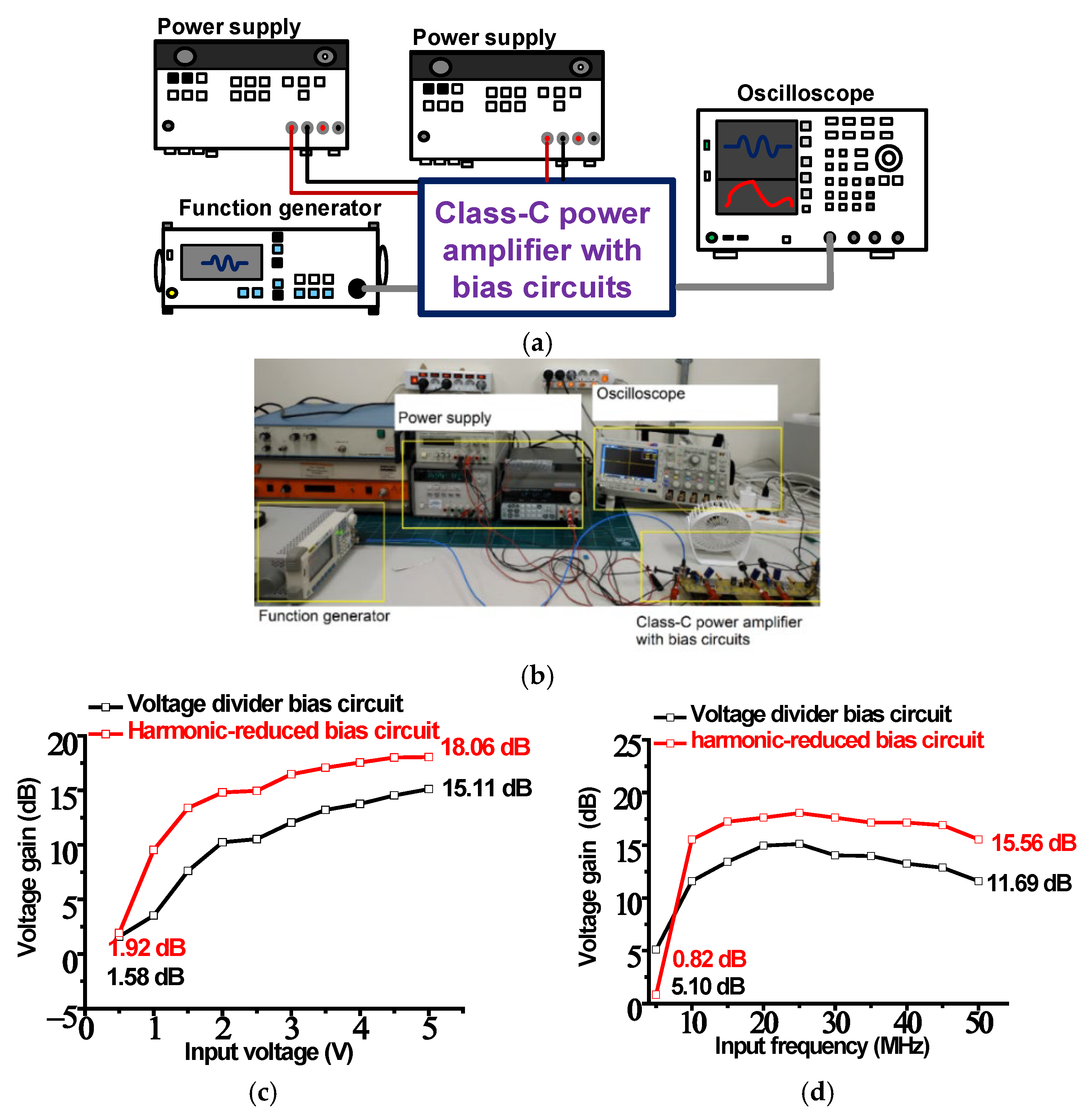

3.2. Power Amplifier Performance Evaluation

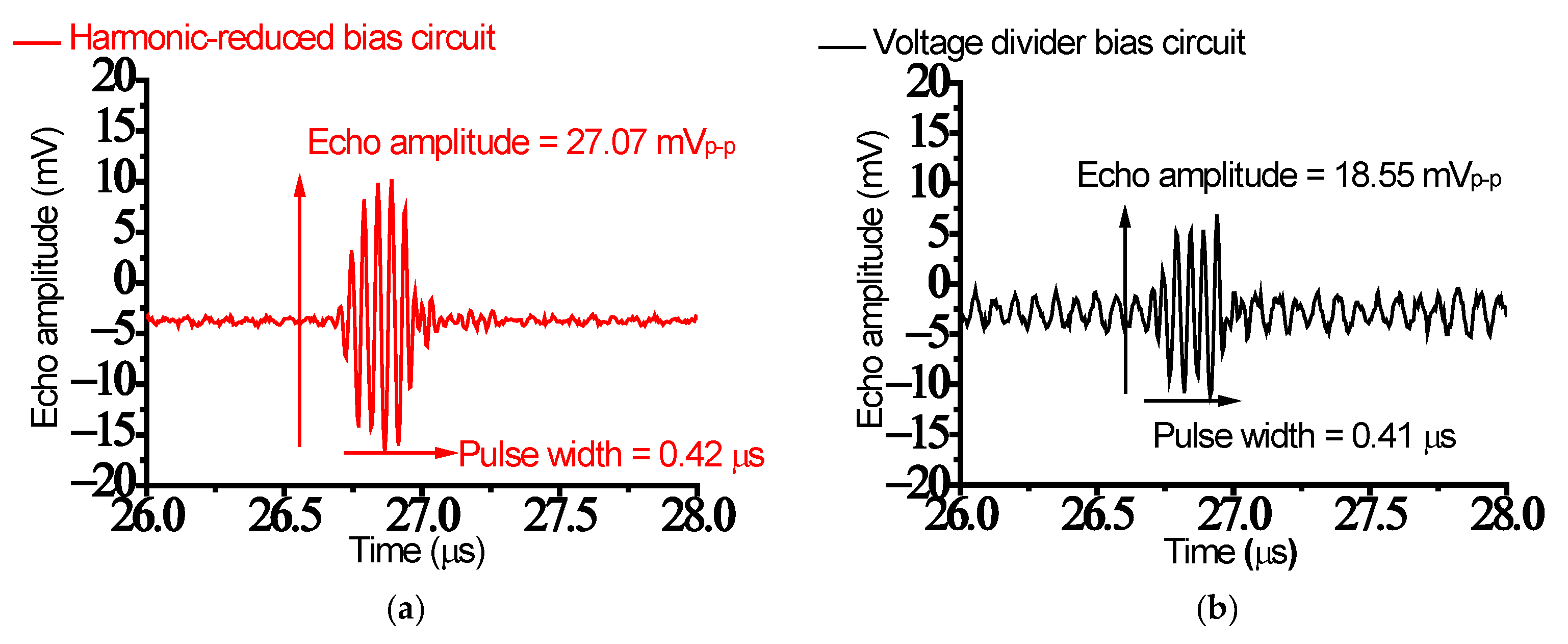

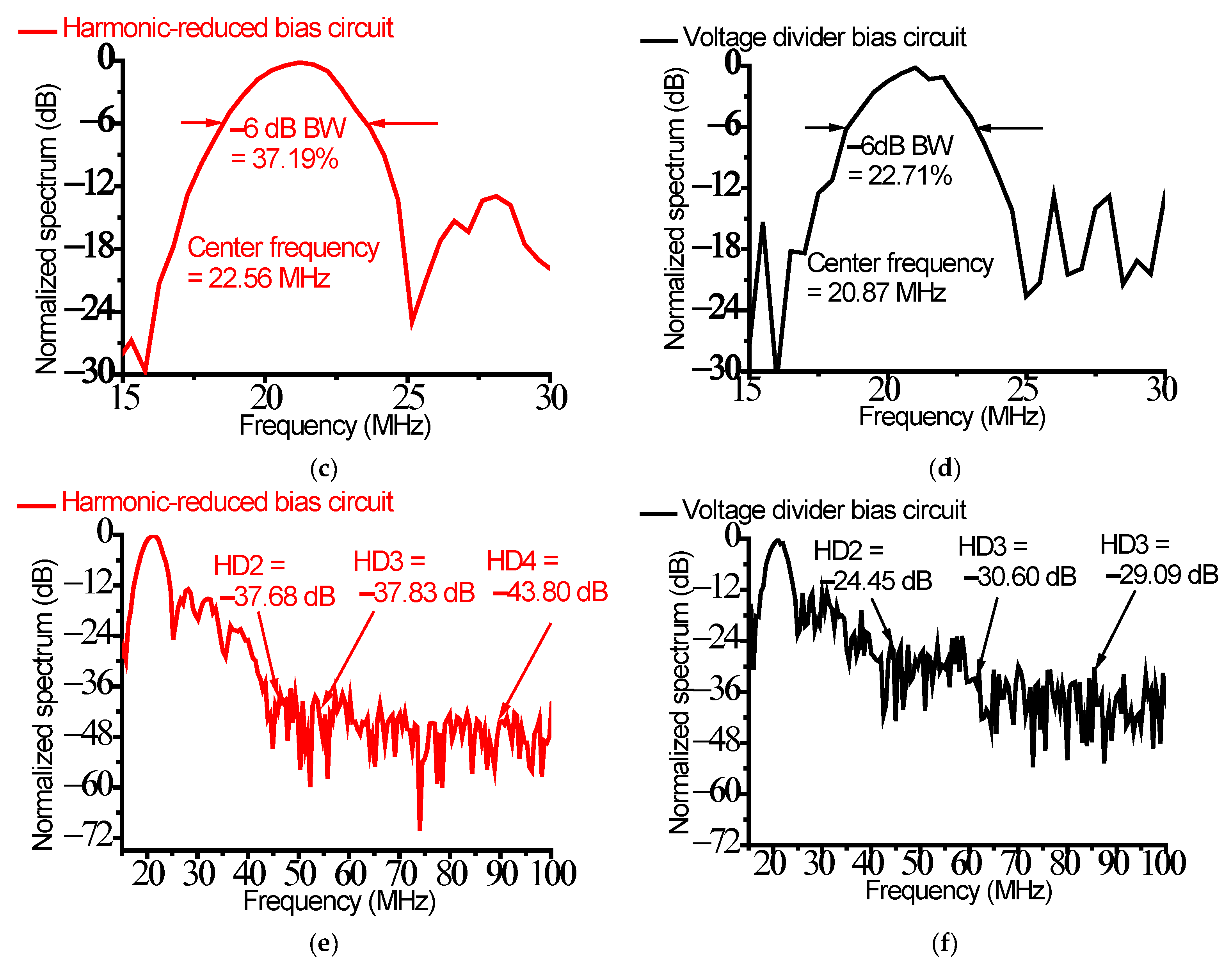

3.3. Pulse-Echo Mode Measurement

4. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Daniels, J.M.; Hoppmann, R.A. Practical Point-of-Care Medical Ultrasound; Springer: New York, NJ, USA, 2016. [Google Scholar]

- Shin, S.-H.; Yoo, W.-S.; Choi, H. Development of Public Key Cryptographic Algorithm Using Matrix Pattern for Tele-Ultrasound Applications. Mathematics 2019, 7, 752. [Google Scholar] [CrossRef]

- Moore, C.L.; Copel, J.A. Point-of-care Ultrasonography. N. Engl. J. Med. 2011, 364, 749–757. [Google Scholar] [CrossRef]

- Shin, S.-H.; Sok Yoo, W.; Choi, H. Development of modified RSA algorithm using fixed mersenne prime numbers for medical ultrasound imaging instrumentation. Comput. Assist. Surg. 2019, 24, 73–78. [Google Scholar] [CrossRef] [PubMed]

- Wagner, M.S.; Garcia, K.; Martin, D.S. Point-of-care Ultrasound in Aerospace Medicine: Known and Potential Applications. Aviat. Space Environ Med. 2014, 85, 730–739. [Google Scholar] [CrossRef] [PubMed]

- Karlen, W. Mobile Point-of-Care Monitors and Diagnostic Device Design; CRC Press: Boca Raton, FL, USA, 2014. [Google Scholar]

- Jeong, J.J.; Choi, H. An impedance measurement system for piezoelectric array element transducers. Measurement 2017, 97, 138–144. [Google Scholar] [CrossRef]

- Wagner, P.R.; Hedrick, W.R. Point-of-Care Ultrasound Fundamentals: Principles, Devices, and Patient Safety; McGraw Hill Professional: New York, NJ, USA, 2014. [Google Scholar]

- Choi, H.; Li, X.; Lau, S.-T.; Hu, C.; Zhou, Q.; Shung, K.K. Development of Integrated Preamplifier for High-Frequency Ultrasonic Transducers and Low-Power Handheld Receiver. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2011, 58, 2646–2658. [Google Scholar] [CrossRef]

- Brunner, E. How ultrasound system considerations influence front-end component choice. Analog. Dialogue 2002, 36, 1–4. [Google Scholar]

- Kripfgans, O.D.; Chan, H.-L. Ultrasonic Imaging: Physics and Mechanism; Springer International Publishing: Berlin, Germany, 2021. [Google Scholar]

- Choe, S.-W.; Choi, H. Suppression Technique of HeLa Cell Proliferation Using Ultrasonic Power Amplifiers Integrated with a Series-Diode Linearizer. Sensors 2018, 18, 4248. [Google Scholar] [CrossRef]

- Ullah, M.N.; Park, C.; Pratiwi, E.; Kim, C.; Choi, H.; Yeom, J.-Y. A new positron-gamma discriminating phoswich detector based on wavelength discrimination (WLD). Nucl. Instrum. Methods Phys. Res. Sect. A 2019, 946, 162631. [Google Scholar] [CrossRef]

- Zennaro, F.; Neri, E.; Nappi, F.; Grosso, D.; Triunfo, R.; Cabras, F.; Frexia, F.; Norbedo, S.; Guastalla, P.; Gregori, M. Real-Time Tele-Mentored Low Cost “Point-of-Care US” in the Hands of Paediatricians in the Emergency Department: Diagnostic Accuracy Compared to Expert Radiologists. PLoS ONE 2016, 11, e0164539. [Google Scholar] [CrossRef]

- Baston, C.M.; Moore, C.; Dean, A.J.; Panebianco, N. Pocket Guide to POCUS: Point-of-Care Tips for Point-of-Care Ultrasound; McGraw Hill Education, Incorporated: New York, NJ, USA, 2019. [Google Scholar]

- Choi, H.; Jung, H.; Shung, K.K. Power Amplifier Linearizer for High Frequency Medical Ultrasound Applications. J. Med. Biol. Eng. 2015, 35, 226–235. [Google Scholar] [CrossRef]

- Kim, J.; You, K.; Choi, H. Post-Voltage-Boost Circuit-Supported Single-Ended Class-B Amplifier for Piezoelectric Transducer Applications. Sensors 2020, 20, 5412. [Google Scholar] [CrossRef]

- Agbossou, K.; Dion, J.-L.; Carignan, S.; Abdelkrim, M.; Cheriti, A. Class D Amplifier for a Power Piezoelectric Load. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2000, 47, 1036–1041. [Google Scholar] [CrossRef]

- Kim, K.; Choi, H. Novel Bandwidth Expander Supported Power Amplifier for Wideband Ultrasound Transducer Devices. Sensors 2021, 21, 2356. [Google Scholar] [CrossRef]

- Nielsen, D.; Knott, A.; Andersen, M.A.E. A high-voltage class D audio amplifier for dielectric elastomer transducers. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition-APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 3278–3283. [Google Scholar]

- Christoffersen, C.; Wong, W.; Pichardo, S.; Togtema, G.; Curiel, L. Class-DE ultrasound transducer driver for HIFU therapy. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 375–382. [Google Scholar] [CrossRef]

- You, K.; Choi, H. Wide Bandwidth Class-S Power Amplifiers for Ultrasonic Devices. Sensors 2020, 20, 290. [Google Scholar] [CrossRef]

- Hendee, W.R.; Ritenour, E.R. Medical Imaging Physics; John Wiley & Sons: Hoboken, NJ, USA, 2003. [Google Scholar]

- You, K.; Kim, S.-H.; Choi, H. A Class-J Power Amplifier Implementation for Ultrasound Device Applications. Sensors 2020, 20, 2273. [Google Scholar] [CrossRef]

- Yuan, T.; Dong, X.; Shekhani, H.; Li, C.; Maida, Y.; Tou, T.; Uchino, K. Driving an inductive piezoelectric transducer with class E inverter. Sens. Actuators A 2017, 261 (Suppl. SC), 219–227. [Google Scholar] [CrossRef]

- Niyomthai, S.; Sangswang, A.; Naetiladdanon, S.; Mujjalinvimut, E. Operation region of class E resonant inverter for ultrasonic transducer. In Proceedings of the 2017 14th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), Phuket, Thailand, 27–30 June 2017; IEEE: Phuket, Thailand, 2017; pp. 435–438. [Google Scholar]

- Suri, J.S.; Kathuria, C.; Chang, R.-F.; Molinar, F.; Fenster, A. Advances in Diagnostic and Therapeutic Ultrasound Imaging; Artech House: Norwood, MA, USA, 2008. [Google Scholar]

- Adhikari, S.; Blaivas, M. The Ultimate Guide to Point-of-Care Ultrasound-Guided Procedures; Springer: Berlin, Germany, 2019. [Google Scholar]

- Kim, J.; Kim, K.; Choe, S.-H.; Choi, H. Development of an Accurate Resonant Frequency Controlled Wire Ultrasound Surgical Instrument. Sensors 2020, 20, 3059. [Google Scholar] [CrossRef]

- Jung, U.; Choi, J.H.; Choo, H.T.; Kim, G.U.; Ryu, J.; Choi, H. Fully Customized Photoacoustic System Using Doubly Q-Switched Nd: YAG Laser and Multiple Axes Stages for Laboratory Applications. Sensors 2022, 22, 2621. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics; Prentice Hall: Upper Saddel River, NJ, USA, 2011. [Google Scholar]

- Cripps, S.C. RF Power Amplifiers for Wireless Communications; Artech House: Norwood, MA, USA, 2006. [Google Scholar]

- Zhang, X.; Larson, L.E.; Asbeck, P. Design of Linear RF Outphasing Power Amplifiers; Artech House: Norwood, MA, USA, 2003. [Google Scholar]

- Grebennikov, A. RF and Microwave Power Amplifier Design; McGraw-Hill: New-York, NJ, USA, 2005. [Google Scholar]

- Reynaert, P.; Steyaert, M. RF Power Amplifiers for Mobile Communications; Springer Science & Business Media: Berlin, Germany, 2006. [Google Scholar]

- Kim, J.; You, K.; Choe, S.-H.; Choi, H. Wireless Ultrasound Surgical System with Enhanced Power and Amplitude Performances. Sensors 2020, 20, 4165. [Google Scholar] [CrossRef] [PubMed]

- Eroglu, A. Introduction to RF Power Amplifier Design and Simulation; CRC Press: Boca Raton, FL, USA, 2018. [Google Scholar]

- Eroglu, A. Linear and Switch-Mode RF Power Amplifiers: Design and Implementation Methods; CRC Press: Boca Raton, FL, USA, 2017. [Google Scholar]

- You, K.; Choi, H. Inter-Stage Output Voltage Amplitude Improvement Circuit Integrated with Class-B Transmit Voltage Amplifier for Mobile Ultrasound Machines. Sensors 2020, 20, 6244. [Google Scholar] [CrossRef] [PubMed]

- Albulet, M. RF Power Amplifiers; SciTech Publishing: London, UK, 2001. [Google Scholar]

- Kumar, N.; Grebennikov, A. Distributed Power Amplifiers for RF and Microwave Communications; Artech House: Norwood, MA, USA, 2015. [Google Scholar]

- Kazimierczuk, M.K. RF Power Amplifier; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Ullah, M.N.; Park, Y.; Kim, G.B.; Kim, C.; Park, C.; Choi, H.; Yeom, J.-Y. Simultaneous Acquisition of Ultrasound and Gamma Signals with a Single-Channel Readout. Sensors 2021, 21, 1048. [Google Scholar] [CrossRef]

- Choi, H. Prelinearized Class-B Power Amplifier for Piezoelectric Transducers and Portable Ultrasound Systems. Sensors 2019, 19, 287. [Google Scholar] [CrossRef] [PubMed]

- Kim, K.; Choi, H. High-efficiency high-voltage class F amplifier for high-frequency wireless ultrasound systems. PLoS ONE 2021, 16, e0249034. [Google Scholar] [CrossRef]

- Choi, H. Class-C Pulsed Power Amplifier with Voltage Divider Integrated with High-Voltage Transistor and Switching Diodes for Handheld Ultrasound Instruments. Energies 2022, 15, 7836. [Google Scholar] [CrossRef]

- Jung, U.; Choi, H. Active echo signals and image optimization techniques via software filter correction of ultrasound system. Appl. Acoust. 2022, 188, 108519. [Google Scholar] [CrossRef]

- Choi, H. Development of a Class-C Power Amplifier with Diode Expander Architecture for Point-of-Care Ultrasound Systems. Micromachines 2019, 10, 697. [Google Scholar] [CrossRef]

- Chen, W.-K. The Circuits and Filters Handbook; CRC Press: Boca Raton, FL, USA, 2002. [Google Scholar]

- Choi, H. Stacked Transistor Bias Circuit of Class-B Amplifier for Portable Ultrasound Systems. Sensors 2019, 19, 5252. [Google Scholar] [CrossRef]

- Szabo, T.L. Diagnostic Ultrasound Imaging: Inside Out; Elsevier Academic Press: London, UK, 2013. [Google Scholar]

- Choi, H.; Yoon, C.; Yeom, J.-Y. A Wideband High-Voltage Power Amplifier Post-Linearizer for Medical Ultrasound Transducers. Appl. Sci. 2017, 7, 354. [Google Scholar] [CrossRef]

- Khan, M.; Khan, T.M. Tunable Q matching networks for capacitive ultrasound transmitters. Analog. Integr. Circuits Signal Process. 2022, 111, 301–312. [Google Scholar] [CrossRef]

- Choi, H. Pre-Matching Circuit for High-Frequency Ultrasound Transducers. Sensors 2022, 22, 8861. [Google Scholar] [CrossRef]

- Shung, K.K.; Smith, M.; Tsui, B.M. Principles of Medical Imaging; Academic Press: Cambridge, MA, USA, 2012. [Google Scholar]

- Choi, H. A Doherty Power Amplifier for Ultrasound Instrumentation. Sensors 2023, 23, 2406. [Google Scholar] [CrossRef]

- Vuolevi, J.; Rahkonen, T. Distortion in RF Power Amplifiers; Artech House: London, UK, 2003. [Google Scholar]

- Choi, H.; Choe, S.-W. Acoustic Stimulation by Shunt-Diode Pre-Linearizer Using Very High Frequency Piezoelectric Transducer for Cancer Therapeutics. Sensors 2019, 19, 357. [Google Scholar] [CrossRef]

- Cripps, S.C. Advanced Techniques in RF Power Amplifier Design; Artech House: Norwood, MA, USA, 2002. [Google Scholar]

- Larson, L.E. RF and Microwave Circuit Design for Wireless Communications; Artech House: Norwood, MA, USA, 1996. [Google Scholar]

- Chang, K. Microwave Solid-State Circuits and Applications; Wiley: New York, NJ, USA, 1994. [Google Scholar]

- Irwin, J.D.; Wu, C.-H. Basic Engineering Circuit Analysis; Wiley: New York, NY, USA, 1999. [Google Scholar]

- Choi, H. Development of negative-group-delay circuit for high-frequency ultrasonic transducer applications. Sens. Actuators A 2019, 299, 111616. [Google Scholar] [CrossRef]

- Arnau, A. Piezoelectric Transducers and Applications; Springer: Berlin, German, 2004. [Google Scholar]

- Kim, K.; Choi, H. A New Approach to Power Efficiency Improvement of Ultrasonic Transmitters via a Dynamic Bias Technique. Sensors 2021, 21, 2795. [Google Scholar] [CrossRef]

- Choi, H.; Jeong, J.J.; Kim, J. Development of an Estimation Instrument of Acoustic Lens Properties for Medical Ultrasound Transducers. J. Healthc. Eng. 2017, 2017, 6580217. [Google Scholar] [CrossRef]

- Pasovic, M.; Danilouchkine, M.; Matte, G.; van der Steen, A.F.W.; Basset, O.; de Jong, N.; Cachard, C. Broadband Reduction of the Second Harmonic Distortion During Nonlinear Ultrasound Wave Propagation. Ultrasound Med. Biol. 2010, 36, 1568–1580. [Google Scholar] [CrossRef]

- Choi, H.; Woo, P.C.; Yeom, J.-Y.; Yoon, C. Power MOSFET Linearizer of a High-Voltage Power Amplifier for High-Frequency Pulse-Echo Instrumentation. Sensors 2017, 17, 764. [Google Scholar] [CrossRef]

- Ludwig, R. RF Circuit Design: Theory & Applications; Pearson Education: London, UK, 2000. [Google Scholar]

- Allen, P.E.; Holberg, D.R. CMOS Analog Circuit Design; Oxford University Press: Oxford, UK, 2002. [Google Scholar]

- Choi, H.; Park, C.; Kim, J.; Jung, H. Bias-Voltage Stabilizer for HVHF Amplifiers in VHF Pulse-Echo Measurement Systems. Sensors 2017, 17, 2425. [Google Scholar] [CrossRef]

- Pederson, D.O.; Mayaram, K. Analog Integrated Circuits for Communication: Principles, Simulation and Design; Springer Science & Business Media: Berlin, Germany, 2007. [Google Scholar]

- Zawawi, R.B.A.; Choi, H.; Kim, J. High-PSRR Wide-Range Supply-Independent CMOS Voltage Reference for Retinal Prosthetic Systems. Electronics 2020, 9, 2028. [Google Scholar] [CrossRef]

- Grebene, A.B. Bipolar and MOS Analog Integrated Circuit Design; John Wiley & Sons: Hoboken, NJ, USA, 2002. [Google Scholar]

- Zawawi, R.B.A.; Abbasi, W.H.; Kim, S.-H.; Choi, H.; Kim, J. Wide-Supply-Voltage-Range CMOS Bandgap Reference for In Vivo Wireless Power Telemetry. Energies 2020, 13, 2986. [Google Scholar] [CrossRef]

- Chen, W.-K. Analog Circuits and Devices; CRC Press: Boca Raton, FL, USA, 2003. [Google Scholar]

- Choi, H.; Choe, S.-W. Therapeutic Effect Enhancement by Dual-bias High-voltage Circuit of Transmit Amplifier for Immersion Ultrasound Transducer Applications. Sensors 2018, 18, 4210. [Google Scholar] [CrossRef] [PubMed]

- Johns, D.A.; Martin, K. Analog Integrated Circuit Design; John Wiley & Sons: New York, NY, USA, 2008. [Google Scholar]

- Choi, H. An Inverse Class-E Power Amplifier for Ultrasound Transducer. Sensors 2023, 23, 3466. [Google Scholar] [CrossRef]

- Grebennikov, A.; Sokal, N.O.; Franco, M.J. Switchmode RF Power Amplifiers; Newnes: Amsterdam, The Netherlands, 2011. [Google Scholar]

- Gray, P.R. Analysis and Design of Analog Integrated Circuits; John Wiley & Sons: Hoboken, NJ, USA, 2009. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill Science: New York, NJ, USA, 2016. [Google Scholar]

- Carr, J. RF Components and Circuits; Elsevier: Amsterdam, The Netherlands, 2002. [Google Scholar]

- Lee, T.H. The Design of CMOS Radio-Frequency Integrated Circuits; Cambridge University Press: Cambridge, UK, 2006. [Google Scholar]

- Hong, J.; Oh, Y.; Choi, H.; Kim, J. Low-Area Four-Channel Controlled Dielectric Breakdown System Design for Point-of-Care Applications. Sensors 2022, 22, 1895. [Google Scholar] [CrossRef]

- Abbasi, W.; Choi, H.; Kim, J. Hexagonal Stimulation Digital Controller Design and Verification for Wireless Subretinal Implant Device. Sensors 2022, 22, 2899. [Google Scholar] [CrossRef]

- Colantonio, P.; Giannini, F.; Limiti, E. High Efficiency RF and Microwave Solid State Power Amplifiers; Wiley Online Library: Hoboken, NJ, USA, 2009. [Google Scholar]

- Kang, H.; Choi, H.; Kim, J. Ambient Light Rejection Integrated Circuit for Autonomous Adaptation on a Sub-Retinal Prosthetic System. Sensors 2021, 21, 5638. [Google Scholar] [CrossRef]

- Zawawi, R.B.A.; Choi, H.; Kim, J. High PSRR Wide Supply Range Dual-Voltage Reference Circuit for Bio-Implantable Applications. Electronics 2021, 10, 2024. [Google Scholar] [CrossRef]

- Kim, J.; Kim, K.S.; Choi, H. Development of a low-cost six-axis alignment instrument for flexible 2D and 3D ultrasonic probes. Technol. Health Care 2021, 29, 77–84. [Google Scholar] [CrossRef]

- Choi, H. Novel dual-resistor-diode limiter circuit structures for high-voltage reliable ultrasound receiver systems. Technol. Health Care 2022, 30, 513–520. [Google Scholar] [CrossRef]

- Shutilov, V.A.; Alferieff, M.E. Fundamental Physics of Ultrasound; CRC Press: Boca Raton, FL, USA, 2020. [Google Scholar]

- Choi, H.; Yang, H.-C.; Shung, K.K. Bipolar-power-transistor-based limiter for high frequency ultrasound imaging systems. Ultrasonics 2014, 54, 754–758. [Google Scholar] [CrossRef]

- Shung, K.K. Diagnostic Ultrasound: Imaging and Blood Flow Measurements; Taylor & Francis: Boca Raton, FL, USA, 2015. [Google Scholar]

- Choi, H.; Ryu, J.-M.; Choe, S.-W. A novel therapeutic instrument using an ultrasound-light-emitting diode with an adjustable telephoto lens for suppression of tumor cell proliferation. Measurement 2019, 147, 106865. [Google Scholar] [CrossRef]

- Self, D. Audio Power Amplifier Design; Focal Press: Waltham, MA, USA, 2013. [Google Scholar]

- Safari, A.; Akdogan, E.K. Piezoelectric and Acoustic Materials for Transducer Applications; Springer Science & Business Media: Berlin, Germany, 2008. [Google Scholar]

| 25 MHz | 50 MHz | 75 MHz | 100 MHz | |

|---|---|---|---|---|

| Harmonic-reduced Bias Circuit | −61.31 dB | −89.02 dB | −90.53 dB | −90.32 dB |

| Voltage Divider Bias Circuit | −57.19 dB | −73.49 dB | −70.97 dB | −73.61 dB |

| Voltage Divider Bias Circuit | Harmonic-Reduced Bias Circuit | Voltage Divider Bias Circuit | Harmonic-Reduced Bias Circuit | ||

| Input Voltage | Gain | Input Frequency | Gain | ||

| 0.5 V | 1.58 dB | 1.92 dB | 5 MHz | 5.10 dB | 0.82 dB |

| 1.0 V | 3.52 dB | 9.54 dB | 10 MHz | 11.59 dB | 15.56 dB |

| 1.5 V | 7.60 dB | 13.38 dB | 15 MHz | 13.44 dB | 17.24 dB |

| 2.0 V | 10.23 dB | 14.80 dB | 20 MHz | 14.96 dB | 17.61 dB |

| 2.5 V | 10.52 dB | 14.96 dB | 25 MHz | 15.11 dB | 18.06 dB |

| 3.0 V | 12.04 dB | 16.47 dB | 30 MHz | 14.04 dB | 17.61 dB |

| 3.5 V | 13.20 dB | 17.07 dB | 35 MHz | 13.97 dB | 17.14 dB |

| 4.0 V | 13.76 dB | 17.55 dB | 40 MHz | 13.25 dB | 17.14 dB |

| 4.5 V | 14.53 dB | 18.01 dB | 45 MHz | 12.86 dB | 16.90 dB |

| 5.0 V | 15.11 dB | 18.06 dB | 50 MHz | 11.59 dB | 15.56 dB |

| Voltage Divider Bias Circuit | Harmonic-reduced Bias Circuit | Voltage Divider Bias Circuit | Harmonic-reduced Bias Circuit | ||

| Input Voltage | Power Consumption | Input Voltage | Power Consumption | ||

| 0.5 V | 8.75 W | 7.50 W | 5 MHz | 2.50 W | 1.250 W |

| 1.0 V | 8.75 W | 8.00 W | 10 MHz | 12.50 W | 13.75 W |

| 1.5 V | 10.00 W | 8.75 W | 15 MHz | 18.75 W | 17.50 W |

| 2.0 V | 10.00 W | 8.75 W | 20 MHz | 22.25 W | 20.50 W |

| 2.5 V | 11.25 W | 9.25 W | 25 MHz | 23.25 W | 21.25 W |

| 3.0 V | 12.50 W | 10.00 W | 30 MHz | 22.50 W | 20.25 W |

| 3.5 V | 15.75 W | 12.75 W | 35 MHz | 22.00 W | 19.50 W |

| 4.0 V | 18.25 W | 15.50 W | 40 MHz | 20.50 W | 18.75 W |

| 4.5 V | 20.50 W | 18.25 W | 45 MHz | 20.00 W | 18.00 W |

| 5.0 V | 23.25 W | 21.25 W | 50 MHz | 18.75 W | 17.75 W |

| Gain vs. Input Voltage | Gain vs. Input Frequency | Power Consumption vs. Input Voltage | Power Consumption vs. Input Voltage | |

|---|---|---|---|---|

| Harmonic-reduced Bias Circuit | 18.06 dB at 5 V | 15.56 dB at 50 MHz | 21.25 W at 5 V | 17.75 W at 50 MHz |

| Voltage Divider Bias Circuit | 15.11 dB at 5 V | 11.59 dB at 50 MHz | 23.25 W at 5 V | 18.75 W at 50 MHz |

| Amplitude | Pulse Width | −6 dB BW | HD2 | HD3 | HD4 | THD | |

|---|---|---|---|---|---|---|---|

| Harmonic-reduced bias circuit | 27.07 mV | 0.42 μs | 37.19% | −37.68 dB | −37.83 dB | −43.80 dB | −34.82 dB |

| Voltage divider bias circuit | 18.55 mV | 0.41 μs | 22.71% | −24.45 dB | −30.60 dB | −29.09 dB | −22.50 dB |

| This Work | [18] | [20] | [21] | [25] | [26] | |

|---|---|---|---|---|---|---|

| Topology | Class-C | Class-D | Class-D | Class-DE | Class-E | Class-E |

| Gain | 18.06 dB | -------- | -------- | -------- | -------- | -------- |

| Output Voltage | 40.0 V | -------- | 125 Vrms | -------- | -------- | 112 Vrms |

| Output Power | -------- | 2 kW | -------- | 800 mW | 133.3 mW | -------- |

| Power Consumption | 21.25 W | -------- | -------- | -------- | -------- | -------- |

| Operating Frequency | 25 MHz | 10 kHz~100 kHz | -------- | 1010 kHz | 41.27 kHz | 28.11 kHz |

| HD2 | −37.68 dB | -------- | -------- | -------- | -------- | -------- |

| HD3 | −37.83 dB | -------- | -------- | −16.40 dB | -------- | -------- |

| HD4 | −43.80 dB | -------- | -------- | -------- | -------- | -------- |

| THD | −34.82 dB | -------- | -------- | -------- | -------- | -------- |

| Applications | Piezoelectric Transducer | Piezoelectric Transducer | Dielectric Elastomer Transducer | Piezoelectric Load | Langevin Transducer | Piezoelectric Ceramic Transducer |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, H. Harmonic-Reduced Bias Circuit for Ultrasound Transducers. Sensors 2023, 23, 4438. https://doi.org/10.3390/s23094438

Choi H. Harmonic-Reduced Bias Circuit for Ultrasound Transducers. Sensors. 2023; 23(9):4438. https://doi.org/10.3390/s23094438

Chicago/Turabian StyleChoi, Hojong. 2023. "Harmonic-Reduced Bias Circuit for Ultrasound Transducers" Sensors 23, no. 9: 4438. https://doi.org/10.3390/s23094438

APA StyleChoi, H. (2023). Harmonic-Reduced Bias Circuit for Ultrasound Transducers. Sensors, 23(9), 4438. https://doi.org/10.3390/s23094438