Dual-Gate Organic Thin-Film Transistor and Multiplexer Chips for the Next Generation of Flexible EG-ISFET Sensor Chips

Abstract

1. Introduction

2. EG-ISFET Sensors

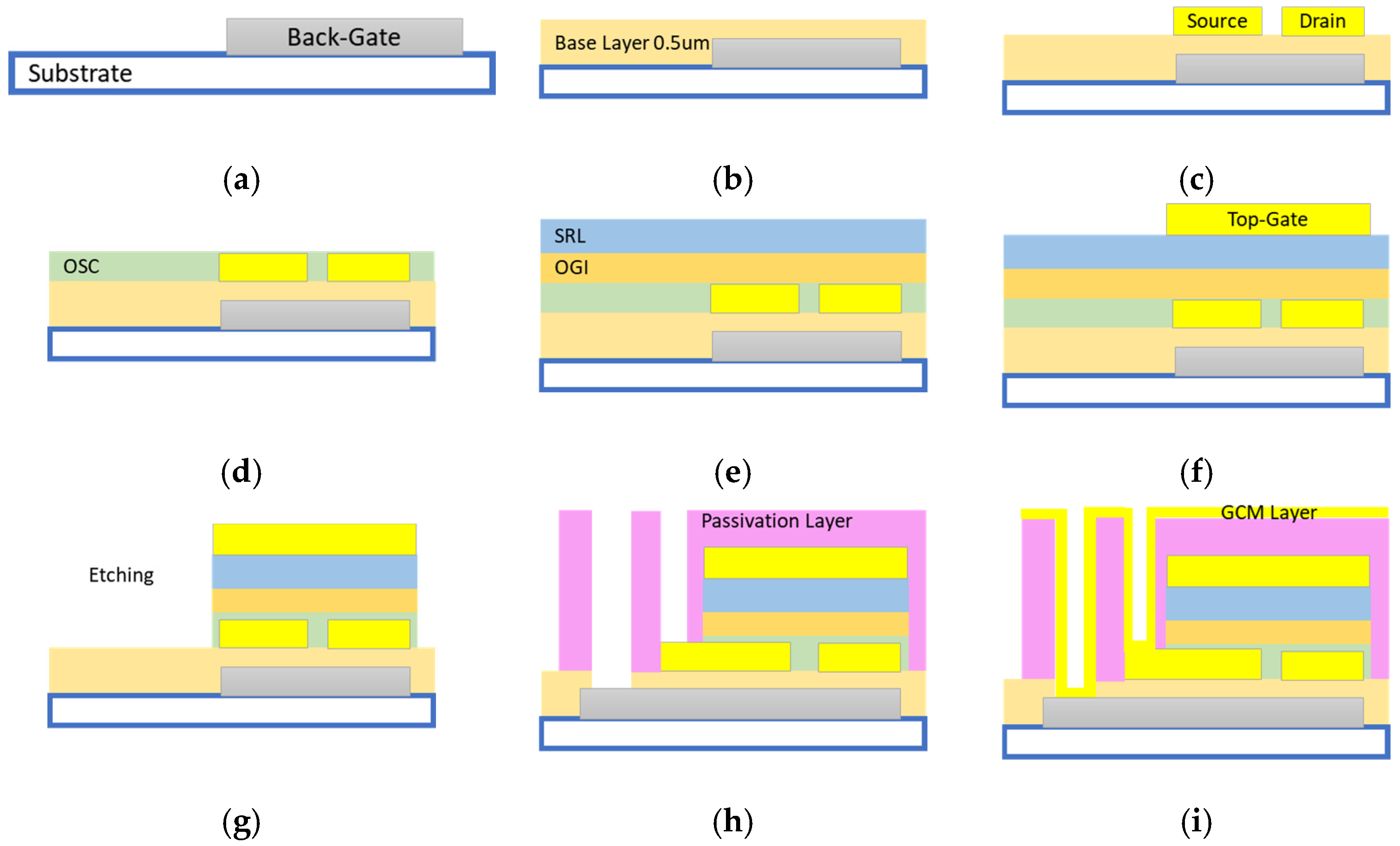

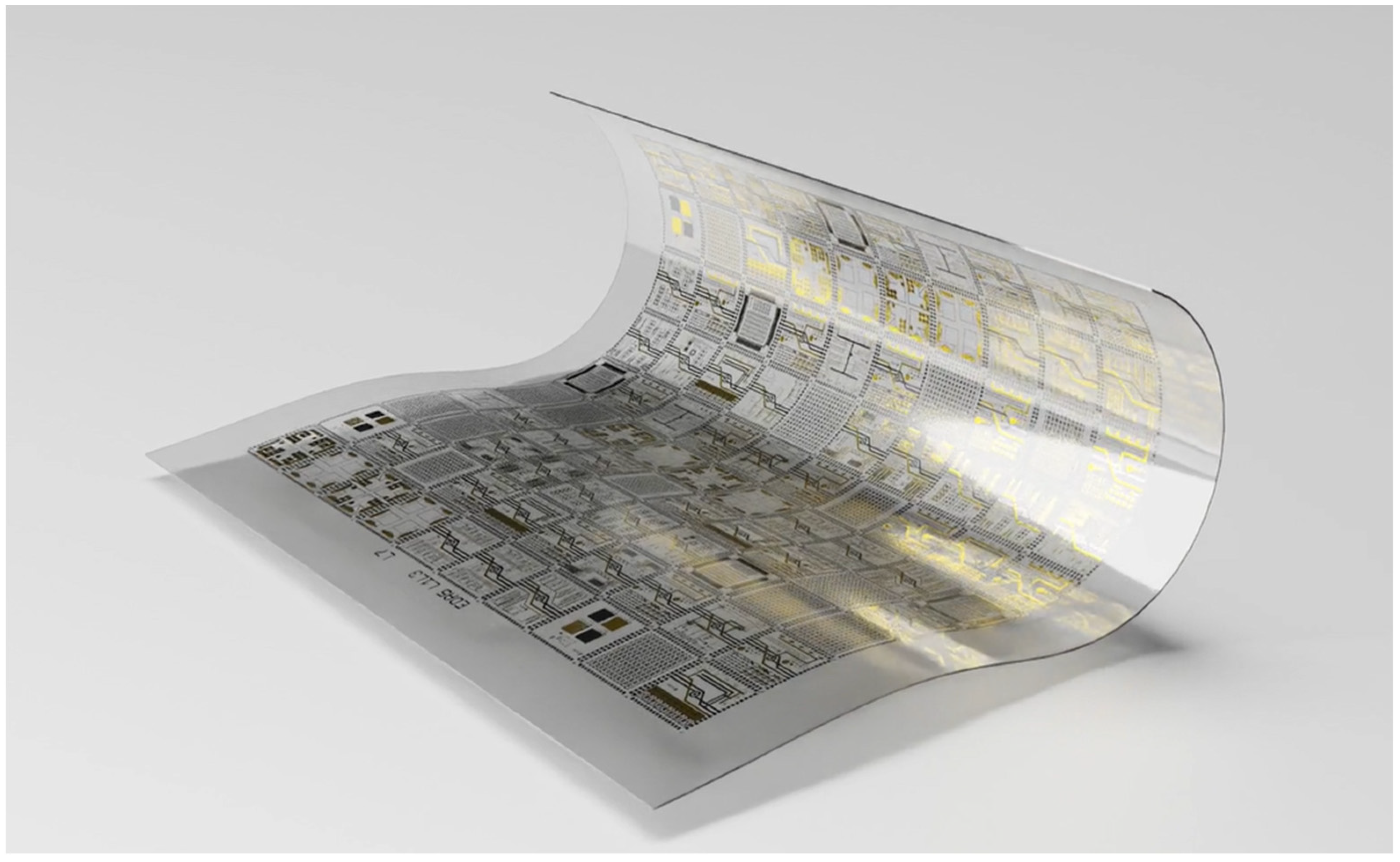

3. Dual-Gate OTFT Technology

3.1. Corbino-Shape Transistors

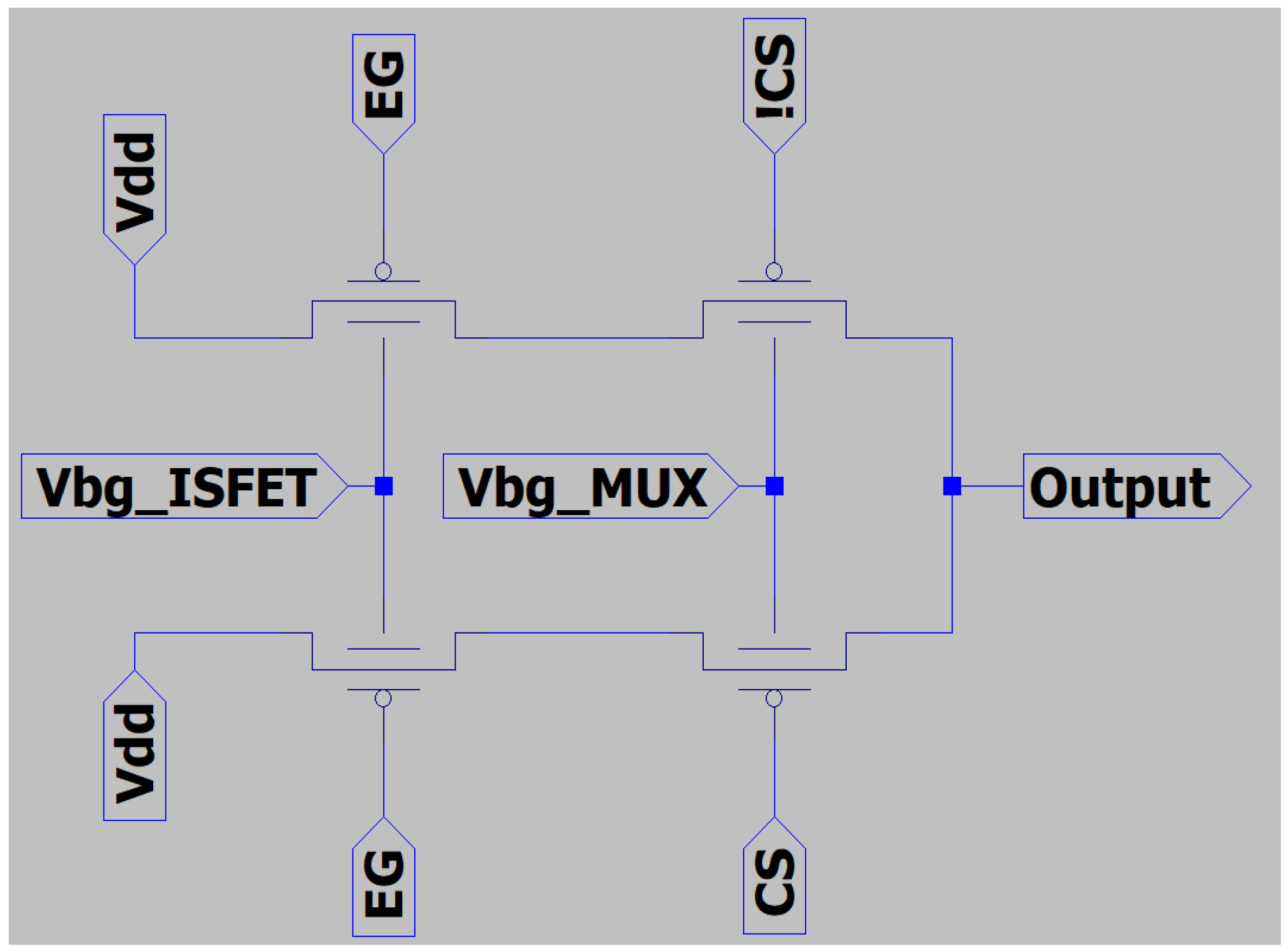

3.2. Interdigitated Transistors

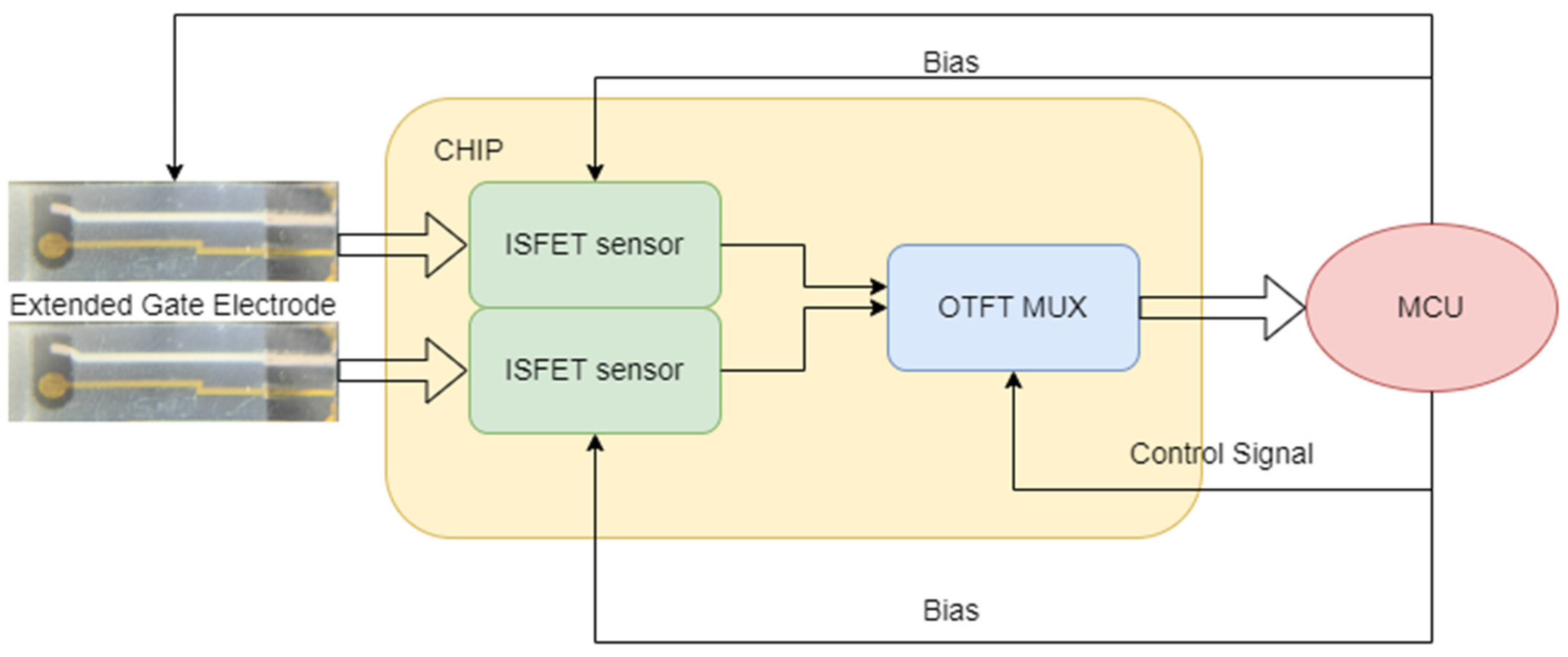

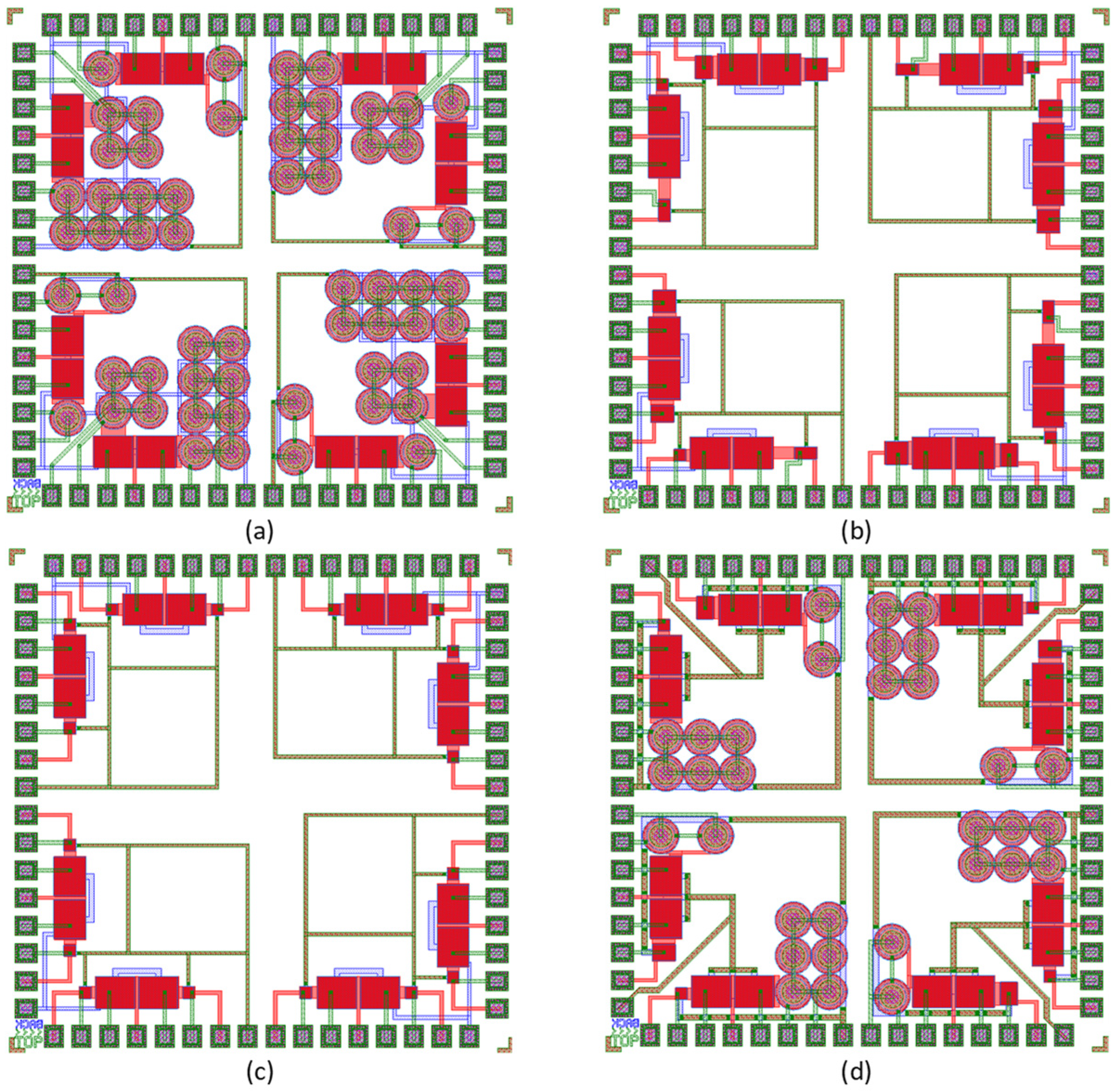

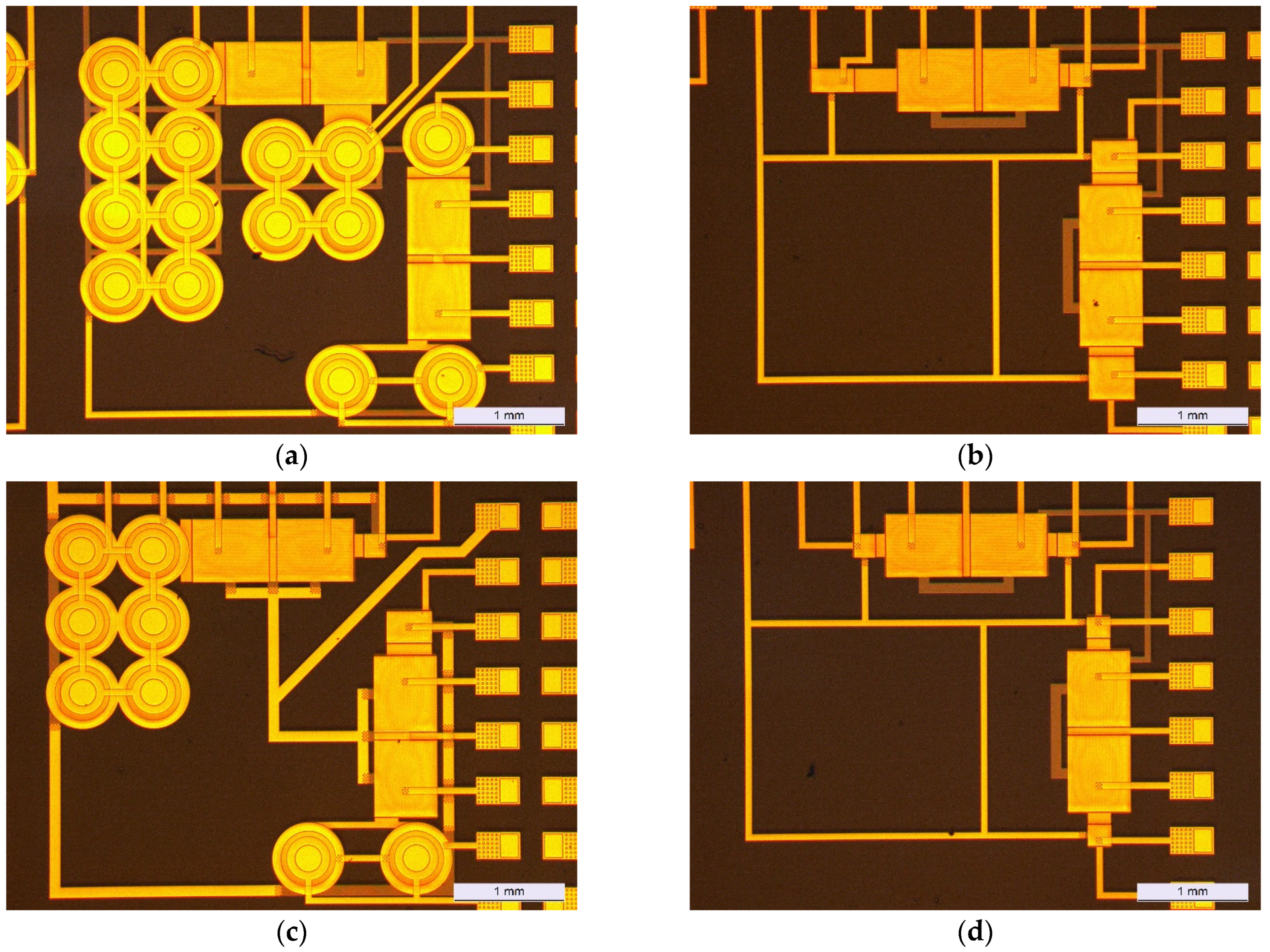

4. Microsystems Chip Architecture

5. Multiplexing Sensor Signal

6. Circuit Design

| Type | No. of Transistors | W/L | Area (µm2) | Chip |

|---|---|---|---|---|

| Corbino | 1 | 1960/4 = 490 | 445,628 | (a) |

| Corbino | 2 parallel | 3920/4 = 980 | 1,108,114 | (a), (d) |

| Corbino | 4 parallel | 7840/4 = 1960 | 1,729,239 | (a) |

| Corbino | 6 parallel | 11,760/4 = 2940 | 2,596,160 | (d) |

| Corbino | 8 parallel | 15,680/4 = 3920 | 3,432,244 | (a) |

| Interdigitated | 1 | 3920/4 = 980 | 49,728 | (b), (c) |

| Interdigitated | 1 | 7840/4 = 1960 | 93,240 | (b) |

| Interdigitated | 1 | 11,760/4 = 2940 | 135,884 | (b), (d) |

| Interdigitated | 1 | 15,680/4 = 3920 | 177,240 | (b) |

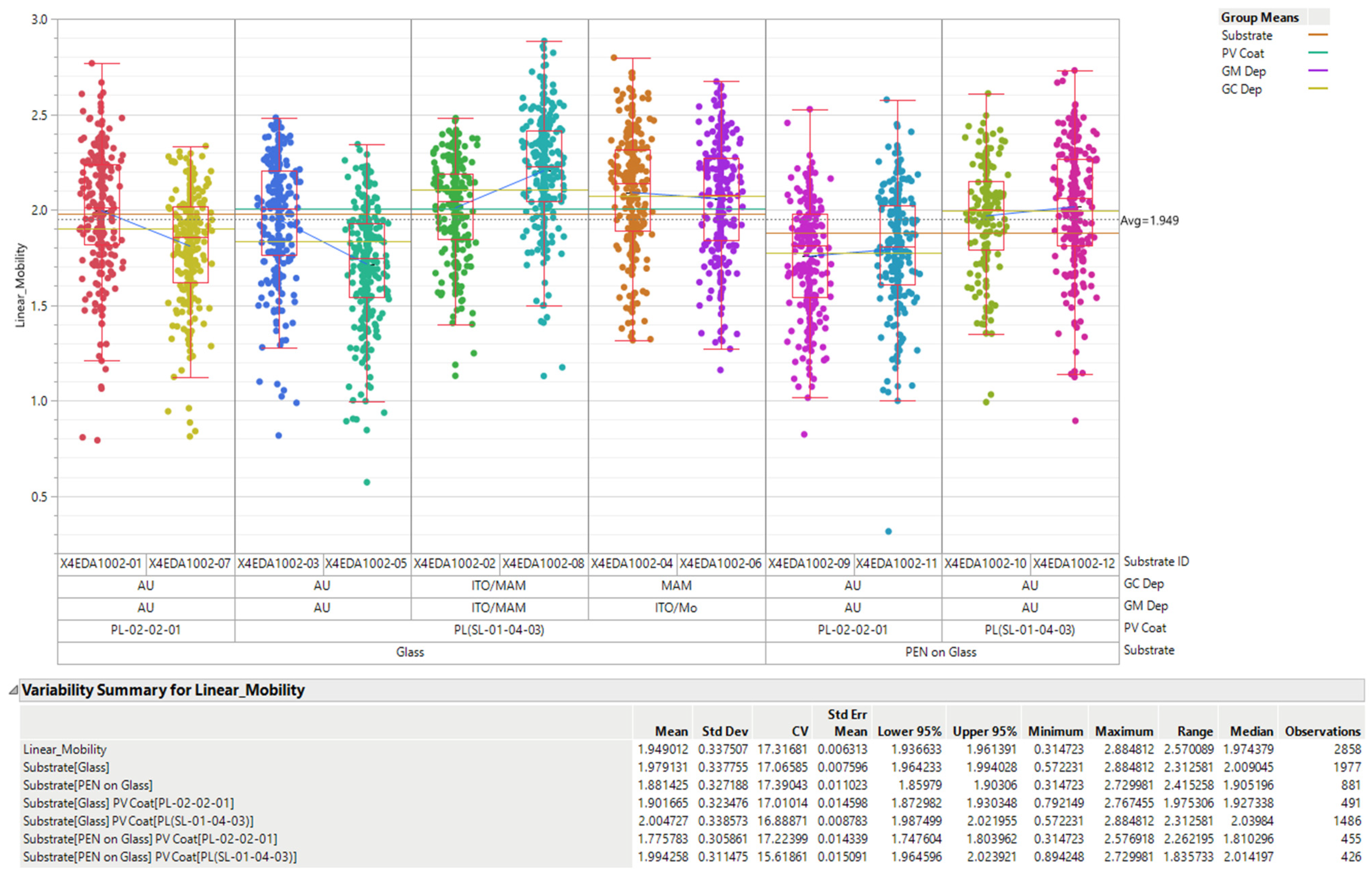

7. OTFT Characterization

| Type | W/L | Vth,mean (V) |

|---|---|---|

| Corbino | 490 | 12.8 ± 6% |

| Interdigitated | 980 | 9.5 ± 5% |

| Interdigitated | 1960 | 9.6 ± 5% |

| Interdigitated | 2940 | 9.7 ± 5% |

| Interdigitated | 3920 | 9.8 ± 5% |

| Interdigitated (MUX) | 9800 | 9.9 ± 5% |

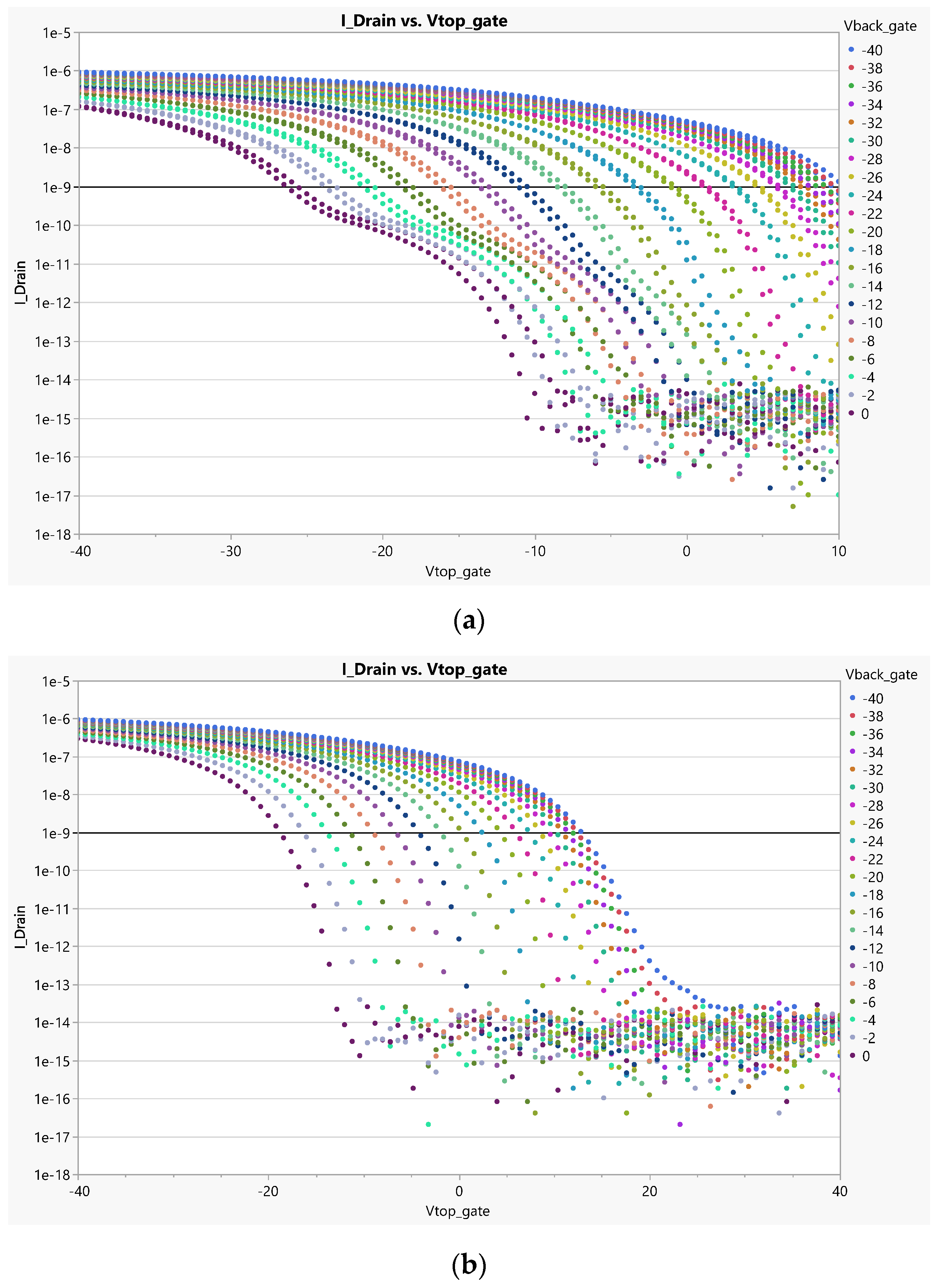

8. Circuit Tests

8.1. Testing Set-Up

8.2. Test Results

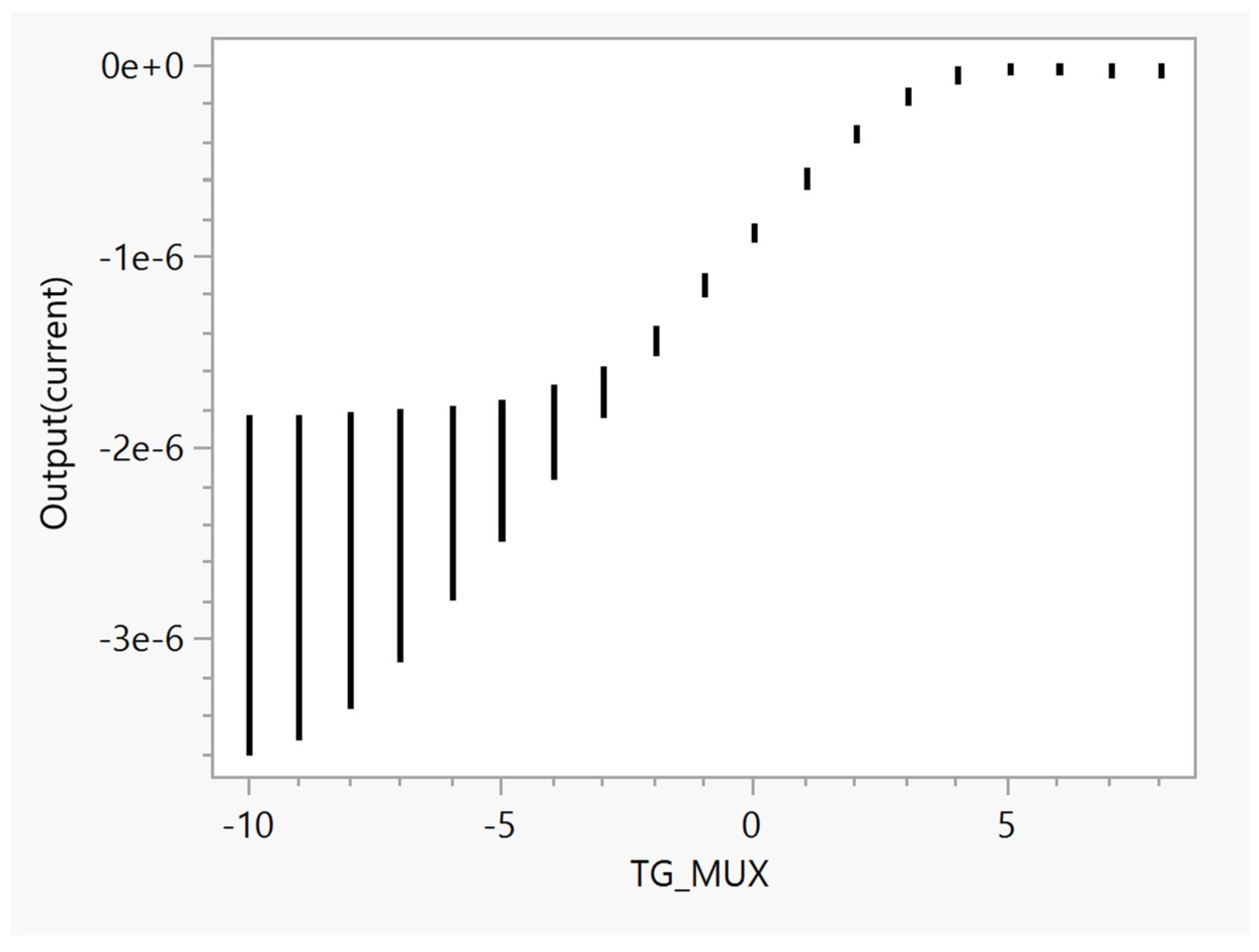

8.2.1. Multiplexing Function

8.2.2. Global Sensing Function

8.2.3. Transconductance Results

9. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Tixier-Mita, A.; Ihida, S.; Ségard, B.-D.; Cathcart, G.; Takahashi, T.; Fujita, H.; Toshiyoshi, H. Review on thin-film transistor technology, its applications, and possible new applications to biological cells. Jpn. J. Appl. Phys. 2016, 55, 04EA08. [Google Scholar] [CrossRef]

- Kumar, A.; Goyal, A.K.; Gupta, N. Review—Thin-Film Transistors (TFTs) for Highly Sensitive Biosensing Applications: A Review. ECS J. Solid State Sci. Technol. 2020, 9, 115022. [Google Scholar] [CrossRef]

- Weimer, P.K. The TFT A New Thin-Film Transistor. Proc. IRE 1962, 50, 1462–1469. [Google Scholar] [CrossRef]

- Lechner, B.; Marlowe, F.; Nester, E.; Tults, J. Liquid crystal matrix displays. In Proceedings of the 1969 IEEE International Solid-State Circuits Conference, Philadelphia, PA, USA, 19–21 February 1969. [Google Scholar] [CrossRef]

- Le Comber, P.; Spear, W.; Ghaith, A. Amorphous-silicon field-effect device and possible application. Electron. Lett. 1979, 15, 179–181. [Google Scholar] [CrossRef]

- Tiedje, T.; Abeles, B.; Morel, D.L.; Moustakas, T.D.; Wronski, C.R. Electron drift mobility in hydrogenated a-Si. Appl. Phys. Lett. 1980, 36, 695–697. [Google Scholar] [CrossRef]

- Depp, S.; Juliana, A.; Huth, B. Polysilicon FET devices for large area input/output applications. In Proceedings of the 1980 International Electron Devices Meeting, Washington, DC, USA, 8–10 December 1980. [Google Scholar] [CrossRef]

- Gao, X.; Lin, L.; Liu, Y.; Huang, X. LTPS TFT Process on Polyimide Substrate for Flexible AMOLED. J. Disp. Technol. 2015, 11, 666–669. [Google Scholar] [CrossRef]

- Serikawa, T.; Shirai, S.; Okamoto, A.; Suyama, S. Low temperature fabrication of high mobility poly-Si TFTs for large area LCDs. IEEE Trans. Electron Devices 1989, 36, 1929–1933. [Google Scholar] [CrossRef]

- Miyata, Y.; Furuta, M.; Yoshioka, T.Y.T.; Kawamura, T.K.T. Low-Temperature Polycrystalline Silicon Thin-Film Transistors for Large-Area Liquid Crystal Display. Jpn. J. Appl. Phys. 1992, 31, 4559. [Google Scholar] [CrossRef]

- Biggs, J.; Myers, J.; Kufel, J.; Ozer, E.; Craske, S.; Sou, A.; Ramsdale, C.; Williamson, K.; Price, R.; White, S. A natively flexible 32-bit Arm microprocessor. Nature 2021, 595, 532–536. [Google Scholar] [CrossRef]

- Ebisawa, F.; Kurokawa, T.; Nara, S. Electrical properties of polyacetylene/polysiloxane interface. J. Appl. Phys. 1983, 54, 3255–3259. [Google Scholar] [CrossRef]

- Drury, C.J.; Mutsaers, C.M.J.; Hart, C.M.; Matters, M.; de Leeuw, D.M. Low-cost all-polymer integrated circuits. Appl. Phys. Lett. 1998, 73, 108–110. [Google Scholar] [CrossRef]

- Guo, X.; Xu, Y.; Ogier, S.; Ng, T.N.; Caironi, M.; Perinot, A.; Li, L.; Zhao, J.; Tang, W.; Sporea, R.A.; et al. Current Status and Opportunities of Organic Thin-Film Transistor Technologies. IEEE Trans. Electron Devices 2017, 64, 1906–1921. [Google Scholar] [CrossRef]

- Jenkins, E. High-performance apparel for outdoor pursuits. In High-Performance Apparel: Materials, Development, and Applications; Elsevier: Amsterdam, The Netherlands, 2017; pp. 421–449. [Google Scholar]

- Koezuka, H.; Tsumura, A.; Ando, T. Field-effect transistor with polythiophene thin film. Synth. Met. 1987, 18, 699–704. [Google Scholar] [CrossRef]

- Park, C.B.; Kim, K.M.; Lee, J.E.; Na, H.; Yoo, S.S.; Yang, M.S. Flexible electrophoretic display driven by solution-processed organic TFT with highly stable bending feature. Org. Electron. 2014, 15, 3538–3545. [Google Scholar] [CrossRef]

- Chen, C.-M.; Anastasova, S.; Zhang, K.; Gil Rosa, B.; Lo, B.P.L.; Assender, H.E.; Yang, G.-Z. Towards Wearable and Flexible Sensors and Circuits Integration for Stress Monitoring. IEEE J. Biomed. Heal. Inform. 2019, 24, 2208–2215. [Google Scholar] [CrossRef] [PubMed]

- Myny, K.; Steudel, S.; Smout, S.; Vicca, P.; Furthner, F.; van der Putten, B.; Tripathi, A.; Gelinck, G.; Genoe, J.; Dehaene, W.; et al. Organic RFID transponder chip with data rate compatible with electronic product coding. Org. Electron. 2010, 11, 1176–1179. [Google Scholar] [CrossRef]

- Fiore, V.; Battiato, P.; Abdinia, S.; Jacobs, S.; Chartier, I.; Coppard, R.; Klink, G.; Cantatore, E.; Ragonese, E.; Palmisano, G. An Integrated 13.56-MHz RFID Tag in a Printed Organic Complementary TFT Technology on Flexible Substrate. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1668–1677. [Google Scholar] [CrossRef]

- Shiwaku, R.; Matsui, H.; Nagamine, K.; Uematsu, M.; Mano, T.; Maruyama, Y.; Nomura, A.; Tsuchiya, K.; Hayasaka, K.; Takeda, Y.; et al. A Printed Organic Amplification System for Wearable Potentiometric Electrochemical Sensors. Sci. Rep. 2018, 8, 3922. [Google Scholar] [CrossRef]

- Minemawari, H.; Yamada, T.; Matsui, H.; Tsutsumi, J.; Haas, S.; Chiba, R.; Kumai, R.; Hasegawa, T. Inkjet printing of single-crystal films. Nature 2011, 475, 364–367. [Google Scholar] [CrossRef]

- Venkateshvaran, D.; Nikolka, M.; Sadhanala, A.; Lemaur, V.; Zelazny, M.; Kepa, M.; Hurhangee, M.; Kronemeijer, A.J.; Pecunia, V.; Nasrallah, I.; et al. Approaching disorder-free transport in high-mobility conjugated polymers. Nature 2014, 515, 384–388. [Google Scholar] [CrossRef]

- Sirringhaus, H. 25th Anniversary Article: Organic Field-Effect Transistors: The Path Beyond Amorphous Silicon. Adv. Mater. 2014, 26, 1319–1335. [Google Scholar] [CrossRef]

- Shao, Y.; Xiao, Z.; Bi, C.; Yuan, Y.; Huang, J. Origin and elimination of photocurrent hysteresis by fullerene passivation in CH3NH3PbI3 planar heterojunction solar cells. Nat. Commun. 2014, 5, 5784. [Google Scholar] [CrossRef]

- Fan, H.; Zou, S.; Gao, J.; Chen, R.; Ma, Q.; Ma, W.; Zhang, H.; Chen, G.; Huo, X.; Liu, Z.; et al. High-mobility organic single-crystalline transistors with anisotropic transport based on high symmetrical “H”-shaped heteroarene derivatives. J. Mater. Chem. C 2020, 8, 11477–11484. [Google Scholar] [CrossRef]

- Paterson, A.F.; Singh, S.; Fallon, K.J.; Hodsden, T.; Han, Y.; Schroeder, B.C.; Bronstein, H.; Heeney, M.; McCulloch, I.; Anthopoulos, T.D. Recent Progress in High-Mobility Organic Transistors: A Reality Check. Adv. Mater. 2018, 30, e1801079. [Google Scholar] [CrossRef]

- Kim, N.S.; Austin, T.; Blaauw, D.; Mudge, T.; Flautner, K.; Hu, J.S.; Irwin, M.; Kandemir, M.; Narayanan, V. Leakage current: Moore’s law meets static power. Computer 2003, 36, 68–75. [Google Scholar] [CrossRef]

- Steudel, S.; Myny, K.; De Vusser, S.; Genoe, J.; Heremans, P. Patterning of organic thin film transistors by oxygen plasma etch. Appl. Phys. Lett. 2006, 89, 183503. [Google Scholar] [CrossRef]

- Tang, W.; Zhao, J.; Feng, L.; Yu, P.; Zhang, W.; Guo, X. Top-Gate Dry-Etching Patterned Polymer Thin-Film Transistors With a Protective Layer on Top of the Channel. IEEE Electron Device Lett. 2014, 36, 59–61. [Google Scholar] [CrossRef]

- Borchert, J.W.; Zschieschang, U.; Letzkus, F.; Giorgio, M.; Weitz, R.T.; Caironi, M.; Burghartz, J.N.; Ludwigs, S.; Klauk, H. Flexible low-voltage high-frequency organic thin-film transistors. Sci. Adv. 2020, 6, eaaz5156. [Google Scholar] [CrossRef] [PubMed]

- Chang, T.K.; Lin, C.W.; Chang, S. LTPO TFT technology for amoleds. Dig. Tech. Pap. 2019, 50, 545–548. [Google Scholar] [CrossRef]

- Sameshima, T.; Sekiya, M.; Usui, S. XeCl Excimer Laser Annealing used in the Fabrication of Poly-Si TFTs. IEEE Electron Device Lett. 1986, 7, 276–278. [Google Scholar] [CrossRef]

- Klauk, H.; Halik, M.; Zschieschang, U.; Schmid, G.; Radlik, W.; Weber, W. High-mobility polymer gate dielectric pentacene thin film transistors. J. Appl. Phys. 2002, 92, 5259–5263. [Google Scholar] [CrossRef]

- Forrest, S.R. The path to ubiquitous and low-cost organic electronic appliances on plastic. Nature 2004, 428, 911–918. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Y.; Li, D.; Jiang, C. Influence of grain size at first monolayer on bias-stress effect in pentacene-based thin film transistors. Appl. Phys. Lett. 2013, 103, 213304. [Google Scholar] [CrossRef]

- Huang, S.-P.; Chen, H.-C.; Chen, P.-H.; Zheng, Y.-Z.; Chu, A.-K.; Shih, Y.-S.; Wang, Y.-X.; Wu, C.-C.; Chen, Y.-A.; Sun, P.-J.; et al. Effect of ELA Energy Density on Self-Heating Stress in Low-Temperature Polycrystalline Silicon Thin-Film Transistors. IEEE Trans. Electron Devices 2020, 67, 3163–3166. [Google Scholar] [CrossRef]

- Zheng, Y.-Z.; Huang, S.-P.; Chen, P.-H.; Chang, T.-C.; Tsai, T.-M.; Chu, A.-K.; Hung, Y.-H.; Shih, Y.-S.; Wang, Y.-X.; Wu, C.-C.; et al. Enhancement of Mechanical Bending Stress Endurance Using an Organic Trench Structure in Foldable Polycrystalline Silicon TFTs. IEEE Electron Device Lett. 2020, 41, 721–724. [Google Scholar] [CrossRef]

- Lee, J.-H.; Kim, D.-H.; Yang, D.-J.; Hong, S.-Y.; Yoon, K.-S.; Hong, P.-S.; Jeong, C.-O.; Park, H.-S.; Kim, S.Y.; Lim, S.K.; et al. 42.2: World’s Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT. Dig. Tech. Pap. 2008, 39, 625–628. [Google Scholar] [CrossRef]

- Kim, M.; Ryu, S.U.; Park, S.A.; Choi, K.; Kim, T.; Chung, D.; Park, T. Donor–Acceptor-Conjugated Polymer for High-Performance Organic Field-Effect Transistors: A Progress Report. Adv. Funct. Mater. 2020, 30, 1904545. [Google Scholar] [CrossRef]

- Fratini, S.; Nikolka, M.; Salleo, A.; Schweicher, G.; Sirringhaus, H. Charge transport in high-mobility conjugated polymers and molecular semiconductors. Nat. Mater. 2020, 19, 491–502. [Google Scholar] [CrossRef]

- Phan, H.; Wang, M.; Bazan, G.C.; Nguyen, T.-Q. Electrical Instability Induced by Electron Trapping in Low-Bandgap Donor-Acceptor Polymer Field-Effect Transistors. Adv. Mater. 2015, 27, 7004–7009. [Google Scholar] [CrossRef]

- Wu, X.; Jia, R.; Jie, J.; Zhang, M.; Pan, J.; Zhang, X.; Zhang, X. Air Effect on the Ideality of p-Type Organic Field-Effect Transistors: A Double-Edged Sword. Adv. Funct. Mater. 2019, 29, 1906653. [Google Scholar] [CrossRef]

- Yang, Z.; Guo, C.; Shi, C.; Wang, D.K.; Zhang, T.; Zhu, Q.; Lu, Z.H. Improving Bias-Stress Stability of p-Type Organic Field-Effect Tran-sistors by Constructing an Electron Injection Barrier at the Drain Electrode/Semiconductor Interfaces. ACS Appl. Mater. Interfaces 2020, 12, 41886–41895. [Google Scholar] [CrossRef]

- Nikolka, M.; Nasrallah, I.; Rose, B.; Ravva, M.K.; Broch, K.; Sadhanala, A.; Harkin, D.; Charmet, J.; Hurhangee, M.; Brown, A.; et al. High operational and environmental stability of high-mobility conjugated polymer field-effect transistors through the use of molecular additives. Nat. Mater. 2017, 16, 356–362. [Google Scholar] [CrossRef] [PubMed]

- Phan, H.; Ford, M.J.; Lill, A.T.; Wang, M.; Bazan, G.C.; Nguyen, T.-Q. Improving Electrical Stability and Ideality in Organic Field-Effect Transistors by the Addition of Fullerenes: Understanding the Working Mechanism. Adv. Funct. Mater. 2017, 27, 1701358. [Google Scholar] [CrossRef]

- Xu, Y.; Sun, H.; Shin, E.-Y.; Lin, Y.-F.; Li, W.; Noh, Y.-Y. Planar-Processed Polymer Transistors. Adv. Mater. 2016, 28, 8531–8537. [Google Scholar] [CrossRef]

- Wu, X.; Jia, R.; Pan, J.; Wang, J.; Deng, W.; Xiao, P.; Zhang, X.; Jie, J. Improving Ideality of P-Type Organic Field-Effect Transistors via Preventing Undesired Minority Carrier Injection. Adv. Funct. Mater. 2021, 31, 2100202. [Google Scholar] [CrossRef]

- Wang, C.; Dong, H.; Jiang, L.; Hu, W. Organic semiconductor crystals. Chem. Soc. Rev. 2018, 47, 422–500. [Google Scholar] [CrossRef]

- Liu, C.; Jang, J.; Xu, Y.; Kim, H.-J.; Khim, D.; Park, W.-T.; Noh, Y.-Y.; Kim, J.-J. Effect of Doping Concentration on Microstructure of Conjugated Polymers and Characteristics in N-Type Polymer Field-Effect Transistors. Adv. Funct. Mater. 2014, 25, 758–767. [Google Scholar] [CrossRef]

- Lüssem, B.; Keum, C.M.; Kasemann, D.; Naab, B.; Bao, Z.; Leo, K. Doped Organic Transistors. Chem. Reviews. Am. Chem. Soc. 2016, 116, 13714–13751. [Google Scholar] [CrossRef]

- Bausells, J.; Carrabina, J.; Errachid, A.; Merlos, A. Ion-sensitive field-effect transistors fabricated in a commercial CMOS technology. Sens. Actuators B Chem. 1999, 57, 56–62. [Google Scholar] [CrossRef]

- Hansen, C.L.; Skordalakest, E.; Berger, J.M.; Quake, S.R. A robust and scalable microfluidic metering method that allows protein crystal growth by free interface diffusion. Proc. Natl. Acad. Sci. USA 2002, 99, 16531–16536. [Google Scholar] [CrossRef]

- Takayama, S.; Ostuni, E.; LeDuc, P.; Naruse, K.; Ingber, D.E.; Whitesides, G.M. Subcellular positioning of small molecules. Nature 2001, 411, 1016. [Google Scholar] [CrossRef]

- Son, J.; Samuel, R.; Gale, B.K.; Carrell, D.T.; Hotaling, J.M. Separation of sperm cells from samples containing high concentrations of white blood cells using a spiral channel. Biomicrofluidics 2017, 11, 054106. [Google Scholar] [CrossRef]

- Jafek, A.R.; Harbertson, S.; Brady, H.; Samuel, R.; Gale, B.K. Instrumentation for xPCR Incorporating qPCR and HRMA. Anal. Chem. 2018, 90, 7190–7196. [Google Scholar] [CrossRef]

- Bange, A.; Halsall, H.B.; Heineman, W.R. Microfluidic immunosensor systems. Biosens. Bioelectron. 2005, 20, 2488–2503. [Google Scholar] [CrossRef]

- Guo, M.T.; Rotem, A.; Heyman, J.A.; Weitz, D.A. Droplet microfluidics for high-throughput biological assays. Lab Chip 2012, 12, 2146–2155. [Google Scholar] [CrossRef]

- Safdar, M.; Jänis, J.; Sánchez, S. Microfluidic fuel cells for energy generation. Lab Chip 2016, 16, 2754–2758. [Google Scholar] [CrossRef] [PubMed]

- Xia, Y.; Whitesides, G.M. Soft lithography. Annu. Rev. Mater. Sci. 1998, 28, 153–184. [Google Scholar] [CrossRef]

- McDonald, J.C.; Duffy, D.C.; Anderson, J.R.; Chiu, D.T.; Wu, H.; Schueller, O.J.; Whitesides, G.M. Fabrication of microfluidic systems in poly(dimethylsiloxane). Electrophoresis 2000, 21, 27–40. [Google Scholar] [CrossRef]

- Qin, D.; Xia, Y.; Whitesides, G.M. Soft lithography for micro- and nanoscale patterning. Nat. Protoc. 2010, 5, 491–502. [Google Scholar] [CrossRef]

- Faustino, V.; Catarino, S.O.; Lima, R.; Minas, G. Biomedical microfluidic devices by using low-cost fabrication techniques: A review. J. Biomech. 2016, 49, 2280–2292. [Google Scholar] [CrossRef] [PubMed]

- Telting-Diaz, M.; Bakker, E. Mass-Produced Ionophore-Based Fluorescent Microspheres for Trace Level Determination of Lead Ions. Anal. Chem. 2002, 74, 5251–5256. [Google Scholar] [CrossRef] [PubMed]

- Wang, X.; Zhang, X. Electrochemical co-reduction synthesis of graphene/nano-gold composites and its application to electro-chemical glucose biosensor. Electrochim Acta. 2013, 112, 774–782. [Google Scholar] [CrossRef]

- Privett, B.J.; Shin, J.H.; Schoenfisch, M.H. Electrochemical sensors. Anal Chem. 2010, 82, 4723–4741. [Google Scholar] [CrossRef] [PubMed]

- Chen, C.; Kotyk, J.F.K.; Sheehan, S.W. Progress toward Commercial Application of Electrochemical Carbon Dioxide Reduction. Chem 2018, 4, 2571–2586. [Google Scholar] [CrossRef]

- Wang, Y.; Xu, H.; Zhang, J.; Li, G. Electrochemical Sensors for Clinic Analysis. Sensors 2008, 8, 2043–2081. [Google Scholar] [CrossRef] [PubMed]

- Nurul Islam, M.; Mazhari, B. Organic thin film transistors with asymmetrically placed source and drain contact. Org. Electron. 2013, 14, 862–867. [Google Scholar] [CrossRef]

- Jeon, J.H.; Cho, W.J. High-performance extended-gate ion-sensitive field-effect transistors with multi-gate structure for trans-parent, flexible, and wearable biosensors. Sci. Technol. Adv. Mater. 2020, 21, 371–378. [Google Scholar] [CrossRef]

- Zeng, R.; Zhang, J.; Sun, C.; Xu, M.; Zhang, S.-L.; Wu, D. A reference-less semiconductor ion sensor. Sens. Actuators B Chem. 2018, 254, 102–109. [Google Scholar] [CrossRef]

- Vonau, W.; Gerlach, F.; Herrmann, S. Conception of a new technique in cell cultivation using a lab-on-chip aided miniaturised device with calibratable electrochemical sensors. Microchim. Acta 2010, 171, 451–456. [Google Scholar] [CrossRef]

- Parizi, K.B.; Xu, X.; Pal, A.; Hu, X.; Wong, H.S.P. ISFET pH Sensitivity: Counter-Ions Play a Key Role. Sci. Rep. 2017, 7, 41305. [Google Scholar] [CrossRef]

- Bouftas, M. A Systematic Review on the Feasibility of Salivary Biomarkers for Alzheimer’s Disease. J. Prev. Alzheimer’s Dis. 2021, 8, 84–91. [Google Scholar] [CrossRef]

- Lau, H.-C.; Lee, I.-K.; Ko, P.-W.; Lee, H.-W.; Huh, J.-S.; Cho, W.-J.; Lim, J.-O. Non-Invasive Screening for Alzheimer’s Disease by Sensing Salivary Sugar Using Drosophila Cells Expressing Gustatory Receptor (Gr5a) Immobilized on an Extended Gate Ion-Sensitive Field-Effect Transistor (EG-ISFET) Biosensor. PLoS ONE 2015, 10, e0117810. [Google Scholar] [CrossRef]

- McKinley, B.A. ISFET and Fiber Optic Sensor Technologies: In Vivo Experience for Critical Care Monitoring. Chem. Rev. 2008, 108, 826–844. [Google Scholar] [CrossRef]

- Baghini, M.S.; Vilouras, A.; Douthwaite, M.; Georgiou, P.; Dahiya, R. Ultra-thin ISFET-based sensing systems. Electrochem. Sci. Adv. 2022, 2, e2100202. [Google Scholar]

- Pirson, T.; Delhaye, T.; Pip, A.; Le Brun, G.; Raskin, J.-P.; Bol, D. The Environmental Footprint of IC Production: Meta-Analysis and Historical Trends. In Proceedings of the ESSDERC 2022-IEEE 52nd European Solid-State Device Research Conference (ESSDERC), Milan, Italy, 19–22 September 2022; pp. 352–355. [Google Scholar] [CrossRef]

- Ogier, S.; Sharkey, D.; Carreras, A.; Tsai, S. 69-3: Opportunities for High-Performance Display Manufacturing Enabled by OTFTs Using an 80*C Maximum Process Temperature. SID Symp. Dig. Tech. Pap. 2022, 53, 929–932. [Google Scholar] [CrossRef]

- Zheng, Y.-Z.; Chen, Y.-A.; Chen, P.-H.; Chang, T.-C.; Hung, Y.-H.; Zhou, K.-J.; Tu, Y.-F.; Wang, Y.-X.; Chen, J.-J.; Wu, C.-C.; et al. Physical Mechanism of the Mechanical Bending of High-Performance Organic TFTs and the Effect of Atmospheric Factors. ACS Appl. Electron. Mater. 2022, 4, 3000–3009. [Google Scholar] [CrossRef]

- Zschieschang, U.; Klauk, H.; Borchert, J.W. High-Resolution Lithography for High-Frequency Organic Thin-Film Transistors. Adv. Mater. Technol. 2023, 8, 2201888. [Google Scholar] [CrossRef]

- Cavallari, M.R.; Pastrana, L.M.; Sosa, C.D.F.; Marquina, A.M.R.; Izquierdo, J.E.E.; Fonseca, F.J.; de Amorim, C.A.; Paterno, L.G.; Kymissis, I. Organic Thin-Film Transistors as Gas Sensors: A Review. Materials 2020, 14, 3. [Google Scholar] [CrossRef] [PubMed]

- Bilgaiyan, A.; Cho, S.-I.; Abiko, M.; Watanabe, K.; Mizukami, M. Flexible, high mobility short-channel organic thin film transistors and logic circuits based on 4H–21DNTT. Sci. Rep. 2021, 11, 11710. [Google Scholar] [CrossRef] [PubMed]

- Gupta, S.; Singh, M.K. Key aspects affecting the performances of high-K dielectrics based single-gate and dual-gate OTFTs. Mater. Today Proc. 2021, 50, 231–237. [Google Scholar] [CrossRef]

- Kumar, B.; Kaushik, B.K.; Negi, Y.S.; Goswami, V. Single and dual gate OTFT based robust organic digital design. Microelectron. Reliab. 2014, 54, 100–109. [Google Scholar] [CrossRef]

- Ha, T.-J.; Kiriya, D.; Chen, K.; Javey, A. Highly Stable Hysteresis-Free Carbon Nanotube Thin-Film Transistors by Fluorocarbon Polymer Encapsulation. ACS Appl. Mater. Interfaces 2014, 6, 8441–8446. [Google Scholar] [CrossRef]

- Dou, W.; Tan, Y. Dual-gate low-voltage transparent electric-double-layer thin-film transistors with a top gate for threshold voltage modulation. RSC Adv. 2020, 10, 8093–8096. [Google Scholar] [CrossRef] [PubMed]

- Duvvury, C.; Amerasekera, A. ESD: A pervasive reliability concern for IC technologies. Proc. IEEE 1993, 81, 690–702. [Google Scholar] [CrossRef]

- Kleinman, D.A.; Schawlow, A.L. Corbino disk. J. Appl. Phys. 1960, 31, 2176–2187. [Google Scholar] [CrossRef]

- Guzenko, V.A.; Akabori, M.; Schäpers, T.; Cabañas, S.; Sato, T.; Suzuki, T.; Yamada, S. Weak antilocalization measurements on a 2-dimensional electron gas in an InGaSb/InAlSb heterostructure. Phys. Status Solidi 2006, 3, 4227–4230. [Google Scholar] [CrossRef]

- Klauk, H.; Gundlach, D.; Nichols, J.; Jackson, T. Pentacene organic thin-film transistors for circuit and display applications. IEEE Trans. Electron. Devices 1999, 46, 1258–1263. [Google Scholar] [CrossRef]

- Arnal, A.; Martínez-Domingo, C.; Ogier, S.; Terés, L.; Ramon, E. Monotype Organic Dual Threshold Voltage Using Different OTFT Geometries. Crystals 2019, 9, 333. [Google Scholar] [CrossRef]

- Byun, Y.H.; Den Boer, W.; Yang, M.; Gu, T. An amorphous silicon TFT with annu-lar-shaped channel and reduced gate-source capacitance. IEEE Trans. Electron. Devices 1996, 43, 839–841. [Google Scholar] [CrossRef]

- Munteanu, D.; Cristoloveanu, S.; Hovel, H. Circular pseudo-metal oxide semiconductor field effect transistor in sili-con-on-insulator analytical model, simulation, and measurements. Electrochem. Solid-State Lett. 1999, 2, 242–243. [Google Scholar] [CrossRef]

- Zhao, C.; Fung, T.C.; Kanicki, J. Half-Corbino short-channel amorphous In–Ga–Zn–O thin-film transistors with a-SiOx or a-SiOx/a-SiNx passivation layers. Solid State Electron. 2016, 120, 25–31. [Google Scholar] [CrossRef]

- Kong, J.; Liu, C.; Li, X.; Ou, H.; She, J.; Deng, S.; Chen, J. Characteristics of Offset Corbino Thin Film Transistor: A Physical Model. Electronics 2023, 12, 2195. [Google Scholar] [CrossRef]

- Mativenga, M.; Geng, D.; Um, J.K.; Mruthyunjaya, R.K.; Heiler, G.N.; Tredwell, T.J.; Jang, J. 49.2: Corbino TFTs for Large-Area AMOLED Displays. SID Symp. Dig. Tech. Pap. 2014, 45, 705–708. [Google Scholar] [CrossRef]

- Das, M.B.; Josephy, R.D. High Frequency, High Power Igfet with Interdigital Electrodes and Plural Looped Gate. U.S. Patent 3,586,930, 10 March 1971. [Google Scholar]

- Tisserant, J.-N.; Wicht, G.; Göbel, O.F.; Bocek, E.; Bona, G.-L.; Geiger, T.; Hany, R.; Mezzenga, R.; Partel, S.; Schmid, P.; et al. Growth and Alignment of Thin Film Organic Single Crystals from Dewetting Patterns. ACS Nano 2013, 7, 5506–5513. [Google Scholar] [CrossRef] [PubMed]

- Bi, S.; He, Z.; Chen, J.; Li, D. Solution-grown small-molecule organic semiconductor with enhanced crystal alignment and areal coverage for organic thin film transistors. AIP Adv. 2015, 5, 077170. [Google Scholar] [CrossRef]

- Fujisaki, Y.; Takahashi, D.; Nakajima, Y.; Nakata, M.; Tsuji, H.; Yamamoto, T. Alignment Control of Patterned Organic Semicon-ductor Crystals in Short-Channel Transistor Using Unidirectional Solvent Evaporation Process. IEEE Trans. Electron. Devices 2015, 62, 2306–2312. [Google Scholar] [CrossRef]

- Genco, E.; Fattori, M.; Harpe, P.J.A.; Modena, F.; Viola, F.A.; Caironi, M.; Cantatore, E. A 4 × 4 Biosensor Array With a 42- μ W/Channel Mul-tiplexed Current Sensitive Front-End Featuring 137-dB DR and Zeptomolar Sensitivity. IEEE Open J. Solid-State Circuits Soc. 2022, 2, 193–207. [Google Scholar] [CrossRef]

- Zeng, J.; Kuang, L.; Miscourides, N.; Georgiou, P. A 128 × 128 Current-Mode Ultra-High Frame Rate ISFET Array with In-Pixel Calibration for Real-Time Ion Imaging. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 359–372. [Google Scholar] [CrossRef]

- Zeng, J.; Miscourides, N.; Georgiou, P. A 128 × 128 Current-Mode Ultra-High Frame Rate ISFET Array for Ion Imaging. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 359–372. [Google Scholar] [CrossRef]

- Cong, Y.; Xu, M.; Zhao, D.; Wu, D. A 3600 × 3600 large-scale ISFET sensor array for high-throughput pH sensing. In Proceedings of the 2017 IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017; pp. 957–960. [Google Scholar] [CrossRef]

- Chan, W.P.; Premanode, B.; Toumazou, C. 64 pH-ISFET averaging array employing global negative current feedback. Electron. Lett. 2009, 45, 536–537. [Google Scholar] [CrossRef]

- Eversmann, B.; Jenkner, M.; Hofmann, F.; Paulus, C.; Brederlow, R.; Holzapfl, B. A 128 128 CMOS Biosensor Array for Extra-cellular Recording of Neural Activity. IEEE J. Solid-State Circuits 2003, 38, 2306–2317. [Google Scholar] [CrossRef]

- Bao, B.; Karnaushenko, D.D.; Schmidt, O.G.; Song, Y.; Karnaushenko, D. Active Matrix Flexible Sensory Systems: Materials, Design, Fabrication, and Integration. Adv. Intell. Syst. 2022, 4, 2100253. [Google Scholar] [CrossRef]

- Fattori, M.; Cardarelli, S.; Fijn, J.; Harpe, P.; Charbonneau, M.; Locatelli, D.; Lombard, S.; Laugier, C.; Tournon, L.; Jacob, S.; et al. A printed proximity-sensing surface based on organic pyroelectric sensors and organic thin-film transistor electronics. Nat. Electron. 2022, 5, 289–299. [Google Scholar] [CrossRef]

- Luo, Z.; Peng, B.; Zeng, J.; Yu, Z.; Zhao, Y.; Xie, J.; Lan, R.; Ma, Z.; Pan, L.; Cao, K.; et al. Sub-thermionic, ultra-high-gain organic transistors and circuits. Nat. Commun. 2021, 12, 1928. [Google Scholar] [CrossRef] [PubMed]

- Lafaye, C.; Rovira, M.; Demuru, S.; Wang, S.; Kim, J.; Kunnel, B.P.; Besson, C.; Fernandez-Sanchez, C.; Serra-Graells, F.; Margarit-Taulé, J.M.; et al. Real-time smart multisensing wearable platform for monitoring sweat biomarkers during exercise. In Proceedings of the BioCAS 2022—IEEE Biomedical Circuits and Systems Conference: Intelligent Biomedical Systems for a Better Future, Taipei, Taiwan, 13–15 October 2022; pp. 173–177. [Google Scholar]

- Cisneros-Fernandez, J.; Guimera-Brunet, A.; Garcia-Cortadella, R.; Schafer, N.; Garrido, J.A.; Teres, L.; Serra-Graells, F. A 1024-Channel GFET 10-bit 5-kHz 36-µW Read-Out Integrated Circuit for Brain JLECoG. In Proceedings of the ICECS 2020—27th IEEE International Conference on Electronics, Circuits and Systems, Glasgow, UK, 23–25 November 2020; pp. 1–4. [Google Scholar]

- Saini, D.; Saini, S.; Negi, S. Modelling and comparison of single gate and dual gate organic thin film transistor. In Proceedings of the 2016 International Conference on Emerging Trends in Communication Technologies, ETCT, Dehradun, India, 18–19 November 2017; pp. 1–5. [Google Scholar]

- Brotherton, S.D. Introduction to thin film transistors: Physics and technology of TFTs. In Introduction to Thin Film Transistors: Physics and Technology of TFTs; Springer International Publishing: New York, NY, USA, 2013; Volume 9783319000, pp. 1–488. [Google Scholar]

- Digilent. Digilent. Analog Discovery 2—Digilent Reference Manual. Available online: https://digilent.com/reference/test-and-measurement/analog-discovery-2/reference-manual (accessed on 14 June 2023).

- Claramunt, S.; Palau, G.; Arnal, A.; Crespo-Yepes, A.; Porti, M.; Ogier, S. Exploitation of OTFTs variability for PUFs imple-mentation and impact of aging. Solid State Electron. 2023, 207, 108698. [Google Scholar] [CrossRef]

- Wu, S.-J.; Wu, Y.-C.; Tsai, H.-H.; Liao, H.-H.; Juang, Y.-Z.; Lin, C.-H.; Shang-Jing, W.; Yung-Chen, W.; Hann-Huei, T.; Hsin-Hao, L.; et al. ISFET-based pH sensor composed of a high transconductance CMOS chip and a disposable touch panel film as the sensing layer. In Proceedings of the 2015 IEEE SENSORS, Busan, Republic of Korea, 1–4 November 2015; pp. 1–4. [Google Scholar] [CrossRef]

| I/O | Dir. | Unit | Value |

|---|---|---|---|

| VDD | Input | Voltage | −5 |

| VBG,mux | Input | Voltage | −38 |

| VBG,sensor | Input | Voltage | −38 |

| VTG,mux | Input | Voltage | −10~+8 |

| VTG,sensor | Input | Voltage | −5~+5 |

| Source | Output | Current | Measure |

| No. | Design Topology | gm |

|---|---|---|

| 1 | 1 Corbino (W/L = 1960/4) | 1.18 × 10−7 ± 5% |

| 2 | 2 Corbinos (W/L = 3920/4) | 1.21 × 10−7 ± 5% |

| 3 | 4 Corbinos (W/L = 7840/4) | 1.44 × 10−7 ± 5% |

| 4 | 6 Corbinos (W/L = 11,760/4) | 1.35 × 10−7 ± 5% |

| 6 | Interdigitated (W/L = 3920/4) | 1.49 × 10−7 ± 5% |

| 7 | Interdigitated (W/L = 7840/4) | 1.47 × 10−7 ± 5% |

| 8 | Interdigitated (W/L = 11,760/4) | 1.09 × 10−7 ± 5% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rezaee, A.; Carrabina, J. Dual-Gate Organic Thin-Film Transistor and Multiplexer Chips for the Next Generation of Flexible EG-ISFET Sensor Chips. Sensors 2023, 23, 6577. https://doi.org/10.3390/s23146577

Rezaee A, Carrabina J. Dual-Gate Organic Thin-Film Transistor and Multiplexer Chips for the Next Generation of Flexible EG-ISFET Sensor Chips. Sensors. 2023; 23(14):6577. https://doi.org/10.3390/s23146577

Chicago/Turabian StyleRezaee, Ashkan, and Jordi Carrabina. 2023. "Dual-Gate Organic Thin-Film Transistor and Multiplexer Chips for the Next Generation of Flexible EG-ISFET Sensor Chips" Sensors 23, no. 14: 6577. https://doi.org/10.3390/s23146577

APA StyleRezaee, A., & Carrabina, J. (2023). Dual-Gate Organic Thin-Film Transistor and Multiplexer Chips for the Next Generation of Flexible EG-ISFET Sensor Chips. Sensors, 23(14), 6577. https://doi.org/10.3390/s23146577