A Temperature-to-Frequency Converter-Based On-Chip Temperature Sensor with an Inaccuracy of +0.65 °C/−0.49 °C

Abstract

1. Introduction

2. Circuit Design of Temperature Sensor

2.1. Top-Level Architecture

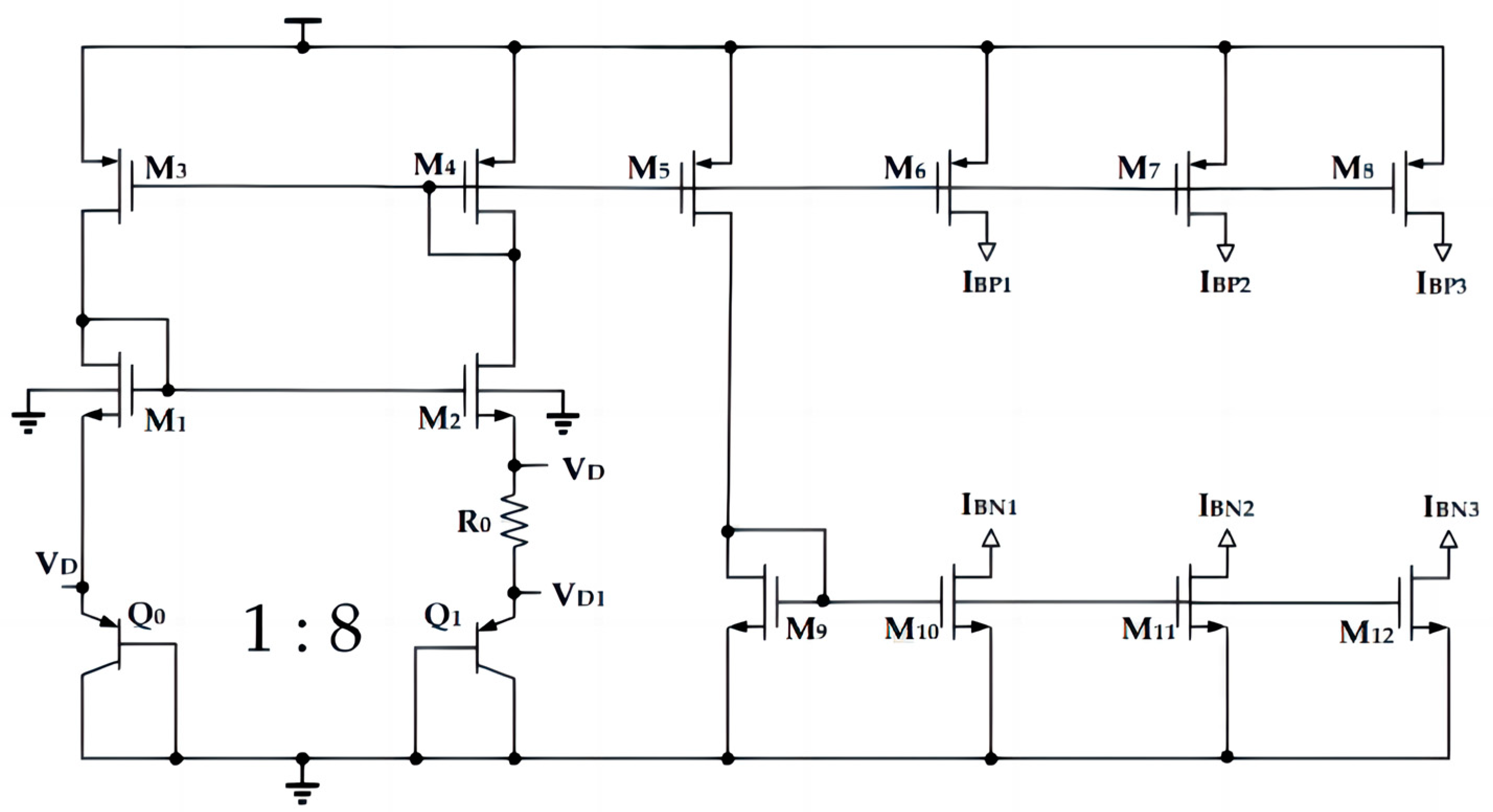

2.2. PTAT Current Circuit

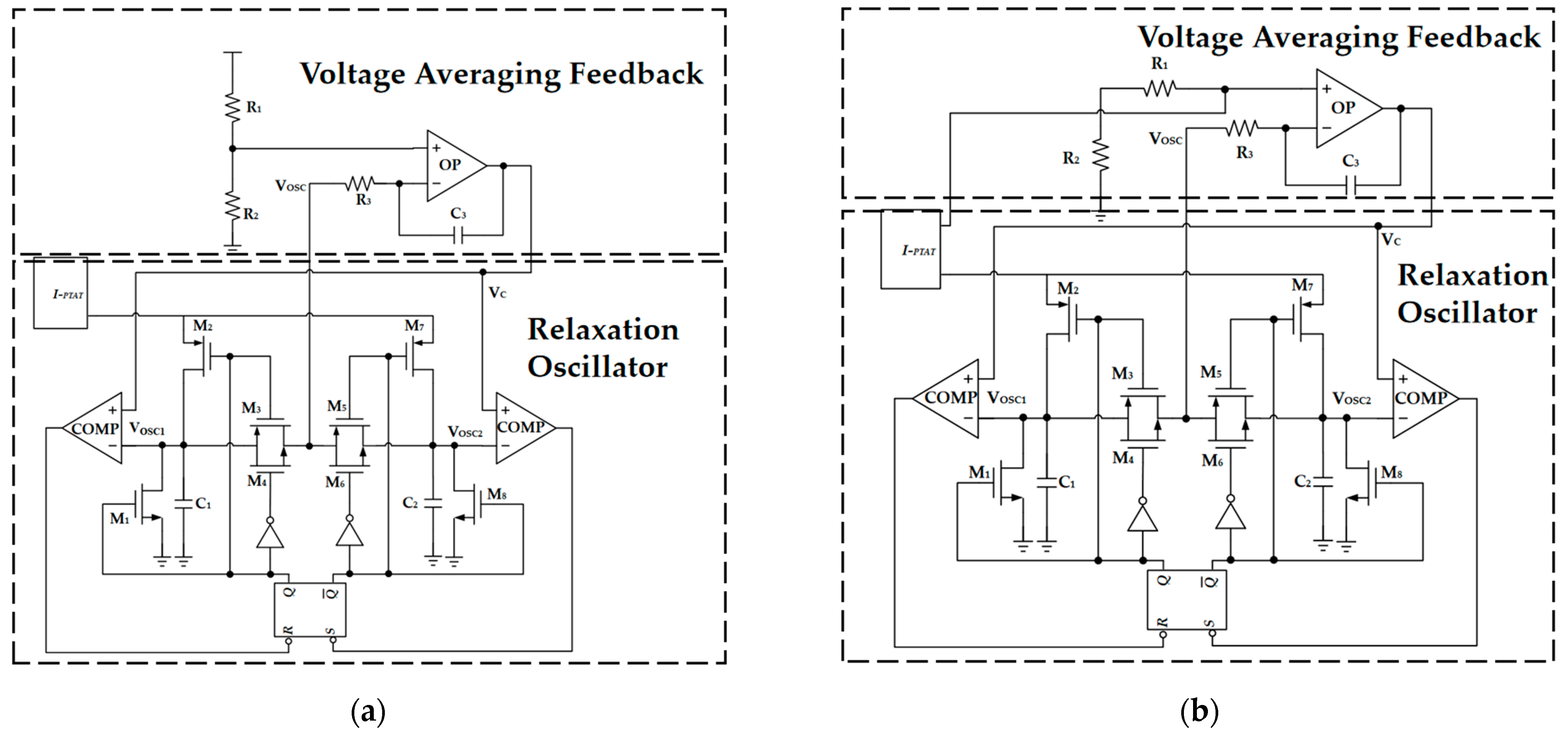

2.3. Principles of OSC Circuit Design

2.4. Frequency-to-Digital Converter

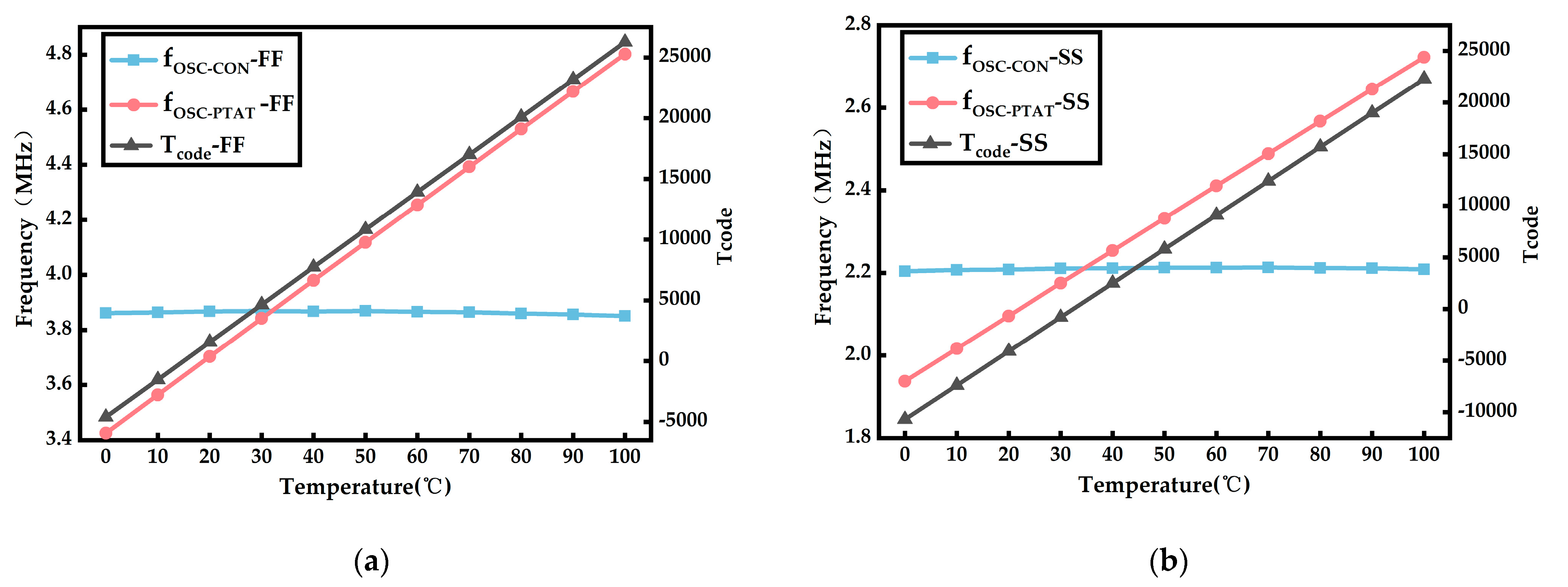

3. Simulation Results

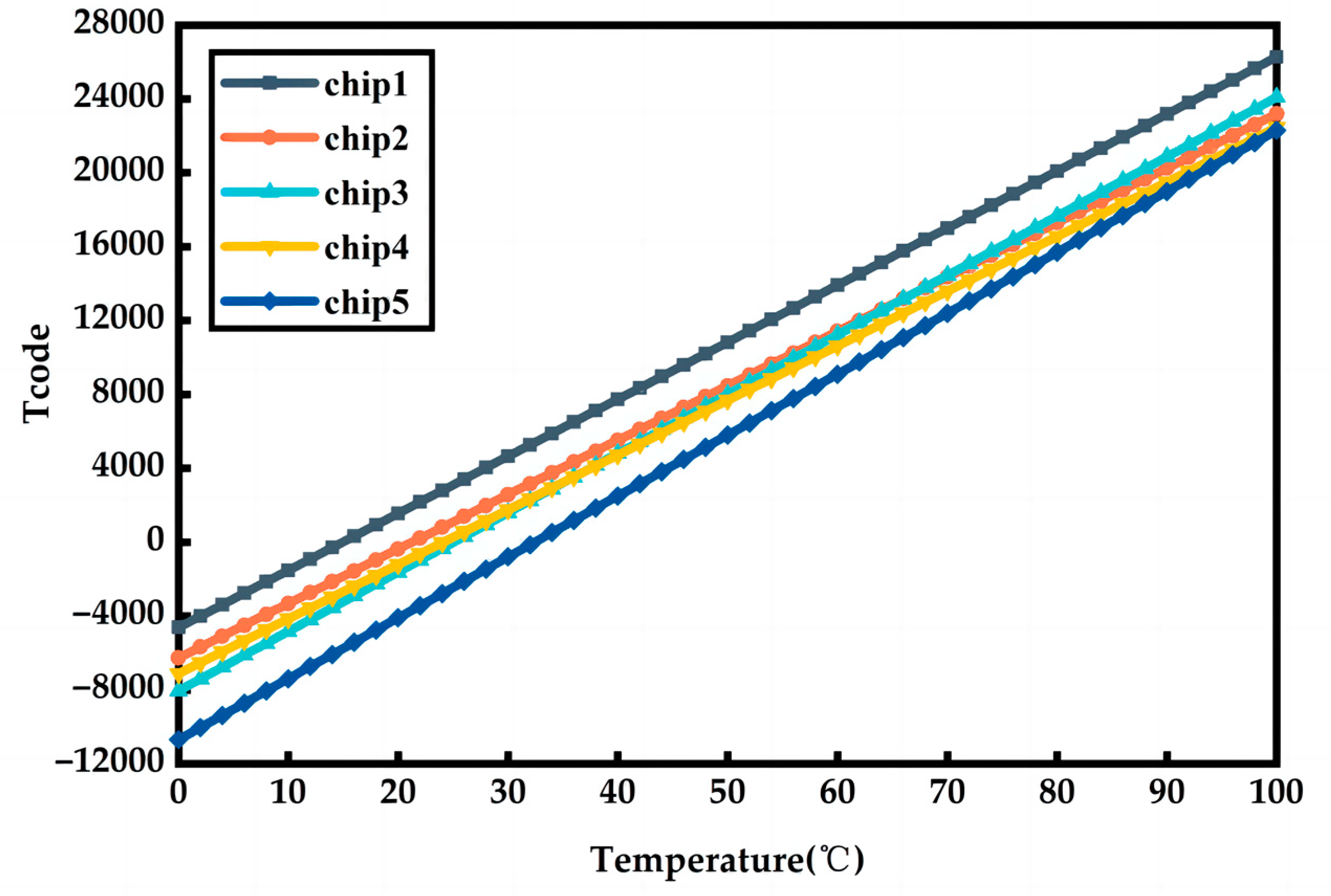

4. Test Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Xiu, L. Time Moore: Exploiting Moore’s Law from The Perspective of Time. IEEE Solid-State Circuits Mag. 2019, 11, 39–55. [Google Scholar] [CrossRef]

- Samake, A.; Kocanda, P.; Kos, A. A New Idea of Effective Cooling of Integrated Circuits. In Proceedings of the 2016 International Conference on Signals and Electronic Systems (ICSES), Krakow, Poland, 5–7 September 2016; IEEE: Krakow, Poland, 2016; pp. 179–182. [Google Scholar]

- Matsuda, T.; Yamada, K.; Demachi, H.; Iwata, H.; Hatakeyama, T.; Ishizuka, M.; Ohzone, T. Analysis of Temperature Distribution in Stacked IC With On-Chip Sensing Device Arrays. IEEE Trans. Semicond. Manufact. 2015, 28, 213–220. [Google Scholar] [CrossRef]

- Souri, K.; Chae, Y.; Makinwa, K.A.A. A CMOS Temperature Sensor with a Voltage-Calibrated Inaccuracy of ±0.15 °C (3σ) from −55 °C to 125 °C. IEEE J. Solid-State Circuits 2013, 48, 292–301. [Google Scholar] [CrossRef]

- Ikegami, A.; Arima, H.; Tosaki, H.; Matsuoka, Y.; Mitsuro, A.; Minorikawa, H.; Asahino, Y. Thick-Film Thermistor and Its Applications. IEEE Trans. Comp. Hybrids Manufact. Technol. 1980, 3, 541–550. [Google Scholar] [CrossRef]

- Xie, S.; Theuwissen, A. All-MOS Self-referenced Temperature Sensor. Electron. Lett. 2019, 55, 1045–1047. [Google Scholar] [CrossRef]

- Sonmez, U.; Sebastiano, F.; Makinwa, K.A.A. Compact Thermal-Diffusivity-Based Temperature Sensors in 40-Nm CMOS for SoC Thermal Monitoring. IEEE J. Solid-State Circuits 2017, 52, 834–843. [Google Scholar] [CrossRef]

- Souri, K.; Chae, Y.; Thus, F.; Makinwa, K. 12.7 A 0.85V 600nW All-CMOS Temperature Sensor with an Inaccuracy of ±0.4 °C (3σ) from −40 to 125 °C. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; IEEE: San Francisco, CA, USA, 2014; pp. 222–223. [Google Scholar]

- Tan, Y.; Liu, Z.; Hao, X.; Shen, Z.; Jiang, H.; Tian, F.; Liu, J. A 1.3-ΜW −0.3/+0.27 °C Inaccuracy Fully-Integrated Temperature Sensor Based on a Pre-Charge Relaxation Oscillator for IoT Applications. In Proceedings of the 2019 IEEE Asia-Pacific Microwave Conference (APMC), Singapore, 10–13 December 2019; IEEE: Singapore, 2019. [Google Scholar]

- Yang, W.; Jiang, H.; Wang, Z.; Jia, W. An Ultra-Low Power Temperature Sensor Based on Relaxation Oscillator in Standard CMOS. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018; IEEE: Shenzhen, China, 2018; pp. 1–2. [Google Scholar]

- Someya, T.; Islam, A.K.M.M.; Sakurai, T.; Takamiya, M. An 11-NW CMOS Temperature-to-Digital Converter Utilizing Sub-Threshold Current at Sub-Thermal Drain Voltage. IEEE J. Solid-State Circuits 2019, 54, 613–622. [Google Scholar] [CrossRef]

- Szajda, K.S.; Sodini, C.G.; Bowman, H.F. A Low Noise, High Resolution Silicon Temperature Sensor. IEEE J. Solid-State Circuits 1996, 31, 1308–1313. [Google Scholar] [CrossRef]

- O’Shaughnessy, T. A CMOS, Self Calibrating, 100 MHz RC-Oscillator for ASIC Applications. In Proceedings of the Eighth International Application Specific Integrated Circuits Conference, Austin, TX, USA, 18–22 September 1995; IEEE: Austin, TX, USA, 1995; pp. 279–282. [Google Scholar]

- Aita, A.L.; De la Cruz, J.V.; Bashirullah, R. A 0.45V CMOS Relaxation Oscillator with ±2.5% Frequency Stability from −55 °C to 125 °C. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; IEEE: Lisbon, Portugal, 2015; pp. 493–496. [Google Scholar]

- Sundaresan, K.; Allen, P.E.; Ayazi, F. Process and Temperature Compensation in a 7-MHz CMOS Clock Oscillator. IEEE J. Solid-State Circuits 2006, 41, 433–442. [Google Scholar] [CrossRef]

- Vilas Boas, A.; Olmos, A. A Temperature Compensated Digitally Trimmable On-Chip IC Oscillator with Low Voltage Inhibit Capability. In Proceedings of the 2004 IEEE International Symposium on Circuits and Systems (IEEE Cat. No.04CH37512), Vancouver, BC, Canada, 23–26 May 2004; IEEE: Vancouver, BC, Canada, 2004; pp. 501–504. [Google Scholar]

- Lasanen, K.; Raisanen-Ruotsalainen, E.; Kostamovaara, J. A 1-V, Self Adjusting, 5-MHz CMOS RC-Oscillator. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 7 August 2002; IEEE: Phoenix-Scottsdale, AZ, USA, 2002; Volume 4, pp. 377–380. [Google Scholar]

- Tokunaga, Y.; Sakiyama, S.; Matsumoto, A.; Dosho, S. An On-Chip CMOS Relaxation Oscillator with Voltage Averaging Feedback. IEEE J. Solid-State Circuits 2010, 45, 1150–1158. [Google Scholar] [CrossRef]

- Yousefzadeh, B.; Makinwa, K.A.A. A BJT-Based Temperature-to-Digital Converter With a ±0.25 °C 3σ -Inaccuracy from −40 °C to +180 °C Using Heater-Assisted Voltage Calibration. IEEE J. Solid-State Circuits 2019, 55, 369–377. [Google Scholar] [CrossRef]

- Qin, C.; Huang, Z.; Liu, Y.; Li, J.; Lin, L.; Tan, N.; Yu, X. An Energy-Efficient BJT-Based Temperature Sensor with ±0.8 °C (3σ) Inaccuracy from −50 to 150 °C. Sensors 2022, 22, 9381. [Google Scholar] [CrossRef] [PubMed]

- Wang, X.; Wang, P.-H.P.; Cao, Y.; Mercier, P.P. A 0.6 V 75 nW All-CMOS Temperature Sensor with 1.67 m°C/MV Supply Sensitivity. IEEE Trans. Circuits Syst. I 2017, 64, 2274–2283. [Google Scholar] [CrossRef]

- Jeong, S.; Foo, Z.; Lee, Y.; Sim, J.-Y.; Blaauw, D.; Sylvester, D. A Fully-Integrated 71 NW CMOS Temperature Sensor for Low Power Wireless Sensor Nodes. IEEE J. Solid-State Circuits 2014, 49, 1682–1693. [Google Scholar] [CrossRef]

- Li, J.; Lin, Y.; Ning, N.; Yu, Q. A +0.44 °C/−0.4 °C Inaccuracy Temperature Sensor with Multi-Threshold MOSFET-Based Sensing Element and CMOS Thyristor-Based VCO. IEEE Trans. Circuits Syst. 2020, 68, 1102–1113. [Google Scholar] [CrossRef]

- Yang, W.; Jiang, H.; Wang, Z. A 0.0014 Mm2 150 NW CMOS Temperature Sensor with Nonlinearity Characterization and Calibration for the −60 to +40 °C Measurement Range. Sensors 2019, 19, 1777. [Google Scholar] [CrossRef] [PubMed]

- Tang, Z.; Fang, Y.; Yu, X.-P.; Shi, Z.; Tan, N. A CMOS Temperature Sensor with Versatile Readout Scheme and High Accuracy for Multi-Sensor Systems. IEEE Trans. Circuits Syst. 2018, 65, 3821–3829. [Google Scholar] [CrossRef]

- Chuang, M.-C.; Tai, C.-L.; Hsu, Y.-C.; Roth, A.; Soenen, E. A Temperature Sensor with a 3 Sigma Inaccuracy of ±2 °C without Trimming from −50 °C to 150 °C in a 16 nm FinFET Process. In Proceedings of the ESSCIRC Conference 2015—41st European Solid-State Circuits Conference (ESSCIRC), Graz, Austria, 14–18 September 2015; IEEE: Graz, Austria, 2015; pp. 271–274. [Google Scholar]

| CMOS Parameters | |||

|---|---|---|---|

| Instance Name | W (μm)/ L (μm) | Finger | Multiplier |

| M1, M2 | 1/4 | 1 | 2 |

| M3, M4, M5, M6, M9, M10 | 2/4 | 1 | 2 |

| M7, M8, M11, M12 | 2/4 | 1 | 8 |

| CMOS Parameters | |||

|---|---|---|---|

| Instance Name | W (μm)/ L (μm) | Finger | Multiplier |

| M1, M2 | 1/0.5 | 1 | 2 |

| M3, M4, M5, M6 | 1/1 | 1 | 2 |

| M7, M9 | 2/1 | 1 | 2 |

| M8 | 2/1 | 1 | 4 |

| M10 | 2/1 | 1 | 2 |

| Circuit Performance Parameters | |||

| Gain (G) | 42 dB | ||

| 3 dB Bandwidth (BW) | 615 kHz | ||

| Phase margin (PM) | 56 deg | ||

| CMOS Parameters | |||

|---|---|---|---|

| Instance Name | W (μm)/ L (μm) | Finger | Multiplier |

| M1, M2, M3, M4, M5 | 2/4 | 1 | 2 |

| M6 | 4/4 | 1 | 2 |

| M7 | 4/4 | 1 | 4 |

| M8 | 4/4 | 1 | 1 |

| Circuit Performance Parameters | |||

| Gain (G) | 81.4 dB | ||

| 3 dB Bandwidth (BW) | 43.1 kHz | ||

| Parameters | [19] | [20] | [21] | [22] | [23] | [24] | [25] | [26] | This Work |

|---|---|---|---|---|---|---|---|---|---|

| Technology | 160 nm | 180 nm | 180 nm | 180 nm | 130 nm | 130 nm | 130 nm | 16 nm | 180 nm |

| type | CMOS | CMOS | CMOS | CMOS | CMOS | CMOS | CMOS | FinFET | CMOS |

| Area (mm2) | 0.15 | 0.13 | 0.45 | 0.09 | 0.07 | 0.0014 | 0.29 | 0.0126 | 0.059 |

| Supply (V) | 1.8 | 1.8/3.3 | 0.6 | 1.2 | 0.95 | 0.85 | 2–3.6 | 1.8 | 1.8 |

| Temp. range (°C) | −40–180 | −50–150 | 0–100 | 0–100 | 0–80 | −60–40 | −40–125 | −50–150 | 0–100 |

| Inaccuracy (°C) | ±0.2 | ±0.8 | +0.62/−1.33 | +1.5/−1.4 | +0.44/−0.4 | ±2 | ±0.47 | ±2 | +0.65/−0.49 |

| Calibration | 1-point | 1-point | 2-point | 2-point | 2-point | 2-point | 1-point | 0-point | 2-point |

| Resolution (°C) | 0.023 | 0.04 | 0.1 | 0.3 | 0.1 | 0.5 | 0.016 | 0.38 | 0.003 |

| Power (μW) | 9.7 | 45.7 | 0.075 | 0.071 | 0.196 | 0.15 | 313.5 | 1210 | 32.9 |

| Conversion rate (ms) | 20 | 10.24 | 254 | 30 | 59 | 1000 | 5.12 | 0.27 | 22.75 |

| Resolution *FOM (pJ/K2) | 103 | 748 | 190 | 190 | 120 | 37500 | 411 | 47175 | 6.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, Z.; Zhang, X.; Chen, S.; Cheong, J.; Yao, L. A Temperature-to-Frequency Converter-Based On-Chip Temperature Sensor with an Inaccuracy of +0.65 °C/−0.49 °C. Sensors 2023, 23, 5169. https://doi.org/10.3390/s23115169

Xu Z, Zhang X, Chen S, Cheong J, Yao L. A Temperature-to-Frequency Converter-Based On-Chip Temperature Sensor with an Inaccuracy of +0.65 °C/−0.49 °C. Sensors. 2023; 23(11):5169. https://doi.org/10.3390/s23115169

Chicago/Turabian StyleXu, Zicong, Xuan Zhang, Sili Chen, Jiahao Cheong, and Lei Yao. 2023. "A Temperature-to-Frequency Converter-Based On-Chip Temperature Sensor with an Inaccuracy of +0.65 °C/−0.49 °C" Sensors 23, no. 11: 5169. https://doi.org/10.3390/s23115169

APA StyleXu, Z., Zhang, X., Chen, S., Cheong, J., & Yao, L. (2023). A Temperature-to-Frequency Converter-Based On-Chip Temperature Sensor with an Inaccuracy of +0.65 °C/−0.49 °C. Sensors, 23(11), 5169. https://doi.org/10.3390/s23115169