VirtLAB: A Low-Cost Platform for Electronics Lab Experiments †

Abstract

:1. Introduction

- (a)

- Design space exploration;

- (b)

- Simulation of the designed system;

- (c)

- Verification of compliance to a previously defined high-level reference model through every refinement step;

- (d)

- Hardware verification, with limited debugging capabilities;

- (e)

- Characterization of the hardware system.

- (a)

- Universities buy and send to students a ‘lab kit’ built up by a set of boards suitable for lab needs. As an example, one MCU board, one FPGA board, a digital oscilloscope, a power supply, etc. This approach has a problem from the point of view of the cost, as the number of kits must be greater than the number of students that are following courses using the kits itself. In fact, in contrast to what happened with ’in presence’ labs, no sharing is possible for lab appliances, as they are physically at the home of the student. Moreover, there are logistics problems too due to the complexity involved in the delivery of kits to students before the course starts and the collection of them after the course ends. Furthermore, this problem worsens if students are located in different cities or countries (at Politecnico di Torino, one half of the students come from different regions, and one tenth from different countries).

- (b)

- Universities suggest the above kit to students (like what happens for a course text book). Of course, this solution is affordable only if the total kit is low and acceptable for the student’s balance. This is the problem. In fact, it is quite easy to find low-cost experimental boards that can be used to implement the experiment: typically, they are MCU-based (Arduino, Nucleo), with prices in the range of USD 10–20. However, there are very few low-cost boards suitable for programmable logic development (at around USD 100 each), and, worst of all, it is nearly impossible to obtain a set of low-cost measurement instruments that are suitable for reasonably sophisticated experiments (the minimum is around USD 200).

- (c)

- Universities install on-premise measurement instruments, and boards host experiments, giving access to them via the Internet. The cost is similar to approach (a), but the drawback is that students do not have physical access to the components.

- Politecnico di Milano-choice b-STM32 Nucleo with custom developed I/O piggyback [12];

- Politecnico di Torino-choice a-Electronics Engineering master course-Breadboard with off-the-shelf passive and active components, and Analog Discovery acquisition system [13];

- Mobile Studio-choice b-Custom board with emulated instruments to be integrated with other boards to host experiments [14];

- Universite de Pau et des Pays de l’Adour-choice c-High cost per seat [15];

- Universitat Oberta de Catalunya-chioice b-No user circuits, only simple prototype board [16].

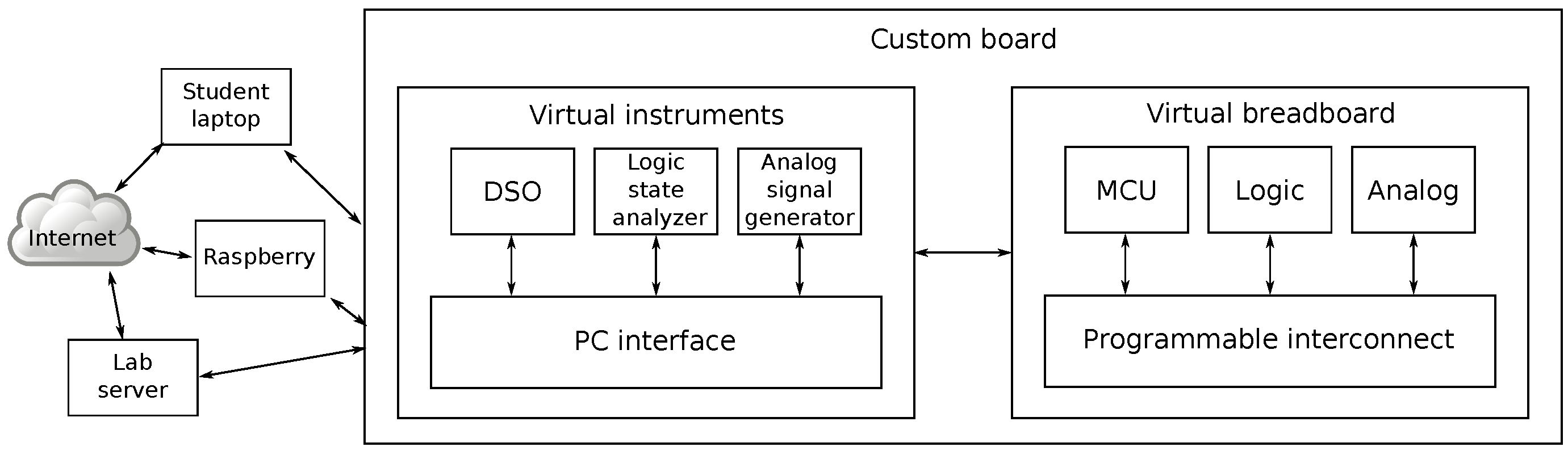

- The students use it at home. No additional hardware must be required, except for the experiment platform itself and a personal computer (laptop or desktop).

- The students use it in the campus labs. This can be a duplication of existing lab equipment, but this choice allows for the use of the same course material in different situations, i.e., remote labs or ’in presence’ ones, and to avoid biases between on-site and off-site students.

- The student is at home, but can have Internet access to the experiment deployed inside university labs. A critical point is to mimic, as far as possible, the same user interface as in preceding use case in order to maintain a uniform usage experience.

- Co-existence inside the same board of both measurement instruments (oscilloscopes, waveform generators, logic state analyzers, etc.) and experimental circuits (microcontrollers, programmable logic, analog and digital I/O).

- Cost minimization through strict performance tailoring to teaching activities.

- Size and robustness optimization, as needed for a teaching platform used by inexperienced users too.

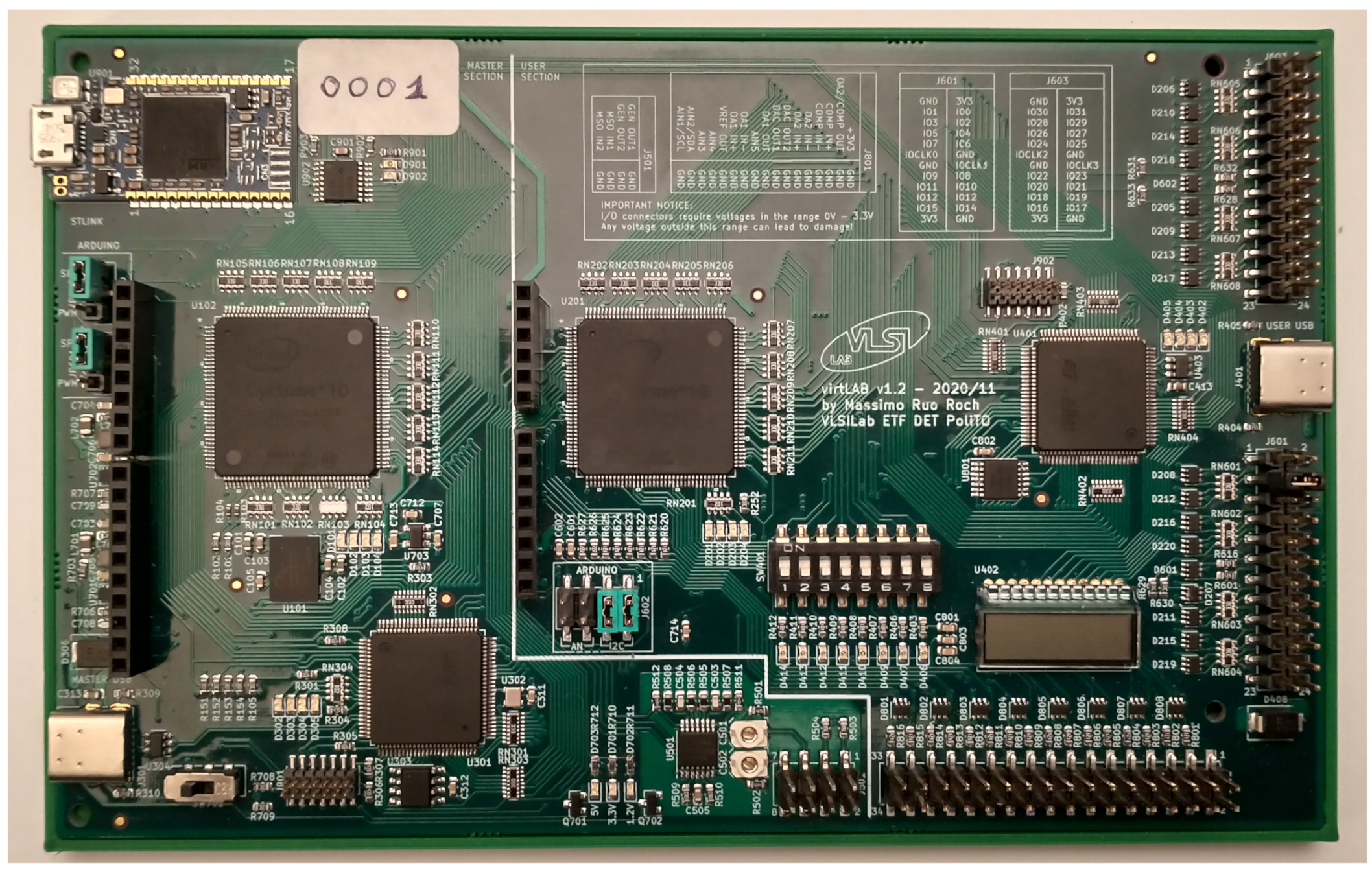

2. System Architecture

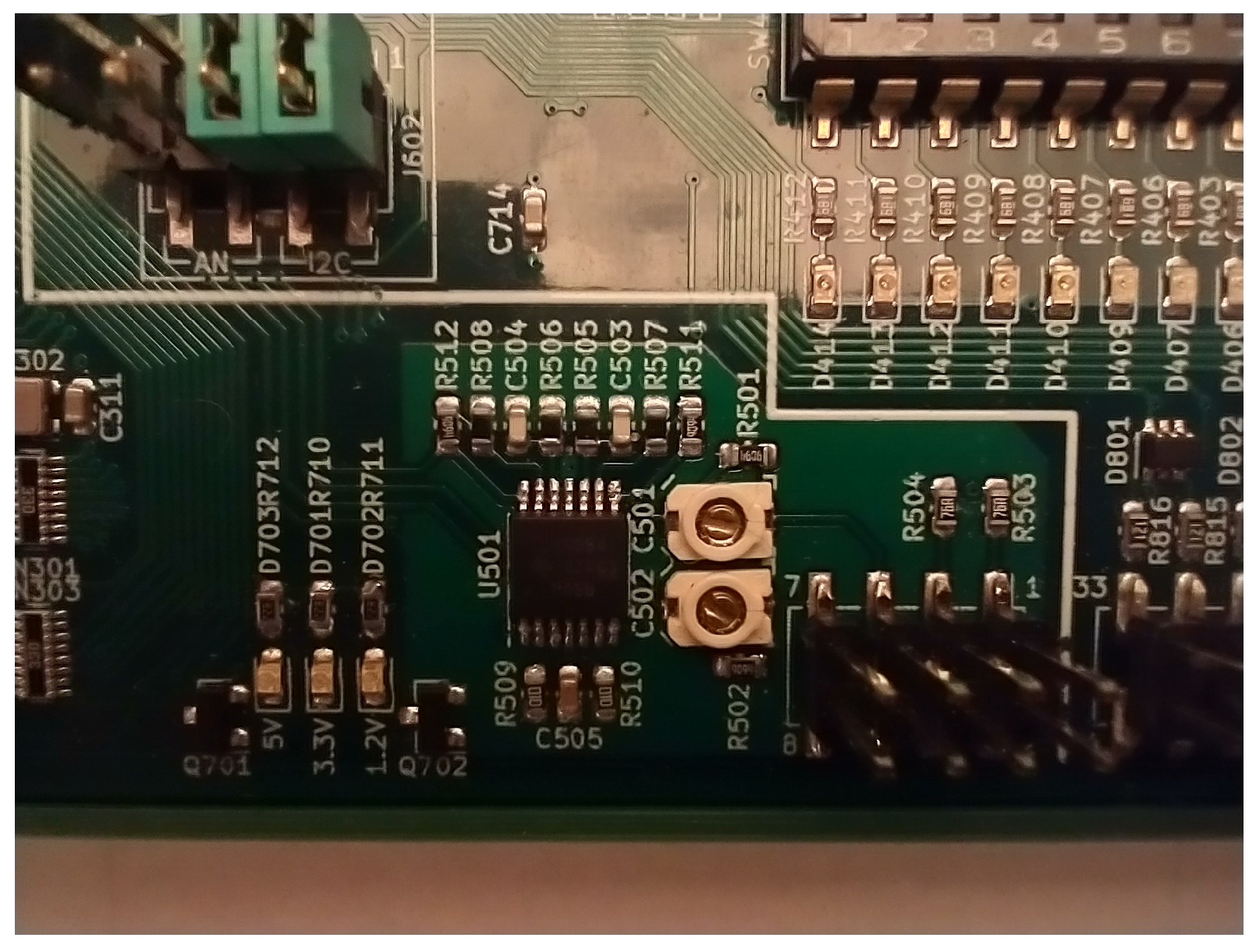

3. Design of a First System

- Generation of digital waveforms with I/O ports of a microcontroller. Timing comparisons for polling, interruption, and hardware timer-assisted generation.

- Audio signal acquisition from digital microphones. Signal reconstruction with MCU and FPGA. Sound event detection. Sound source direction detection through stereo microphones.

- Acquisition of real time data from three-axis accelerometers. Position calculation via MCU and FPGA. Graphics representation in an FPGA-based frame buffer.

- Implementation of serial communication peripherals IP and testing on FPGA (I2C, RS232).

- Implementation of parallel bus handshake protocols master and slave (synchronous, semi-synchronous, asynchronous).

- Implementation of hardware computing accelerators (FIR, IIR, FFT, AI). Power consumption optimization techniques.

3.1. Master Section Specifications

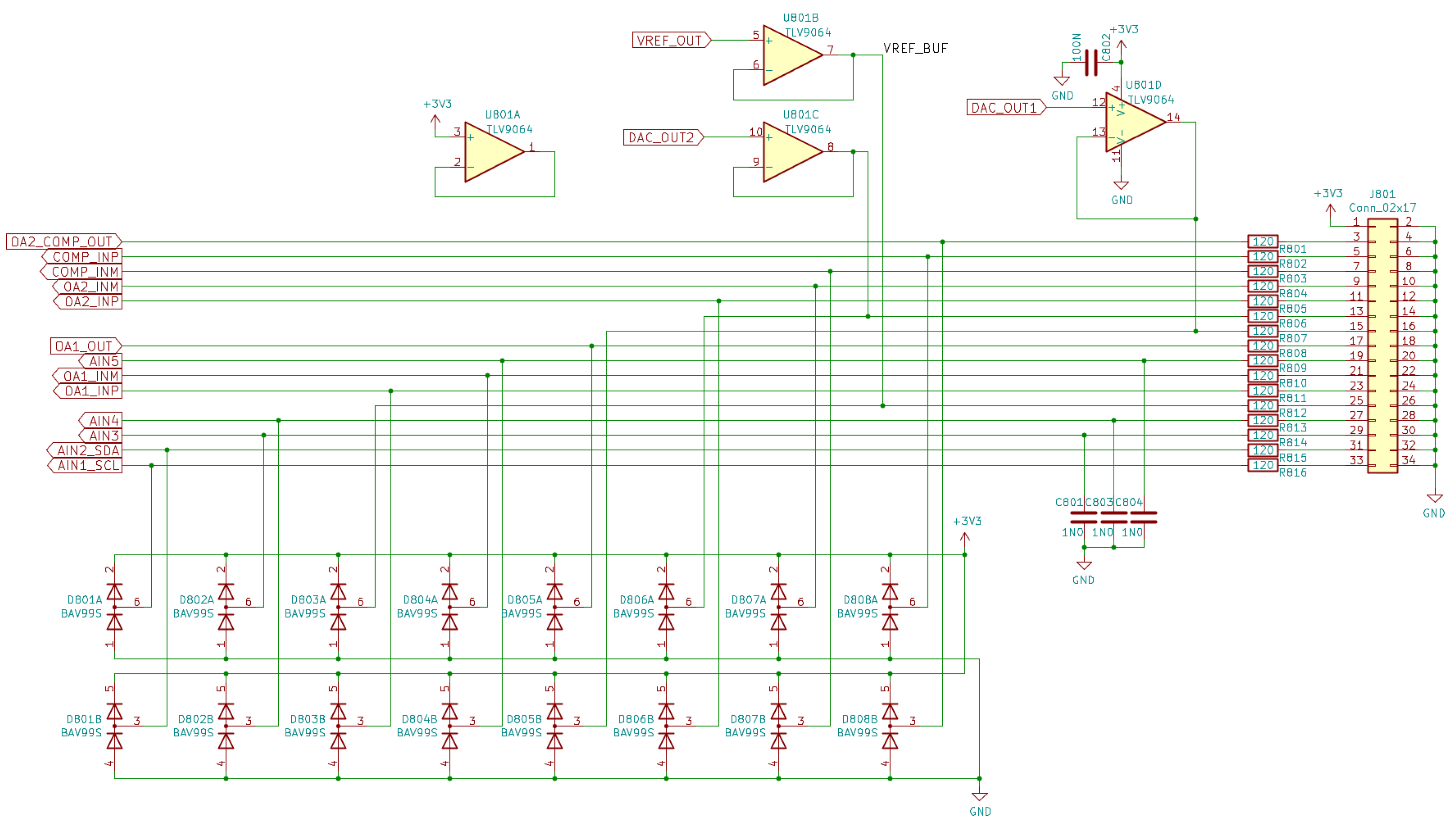

3.1.1. Digital Storage Oscilloscope

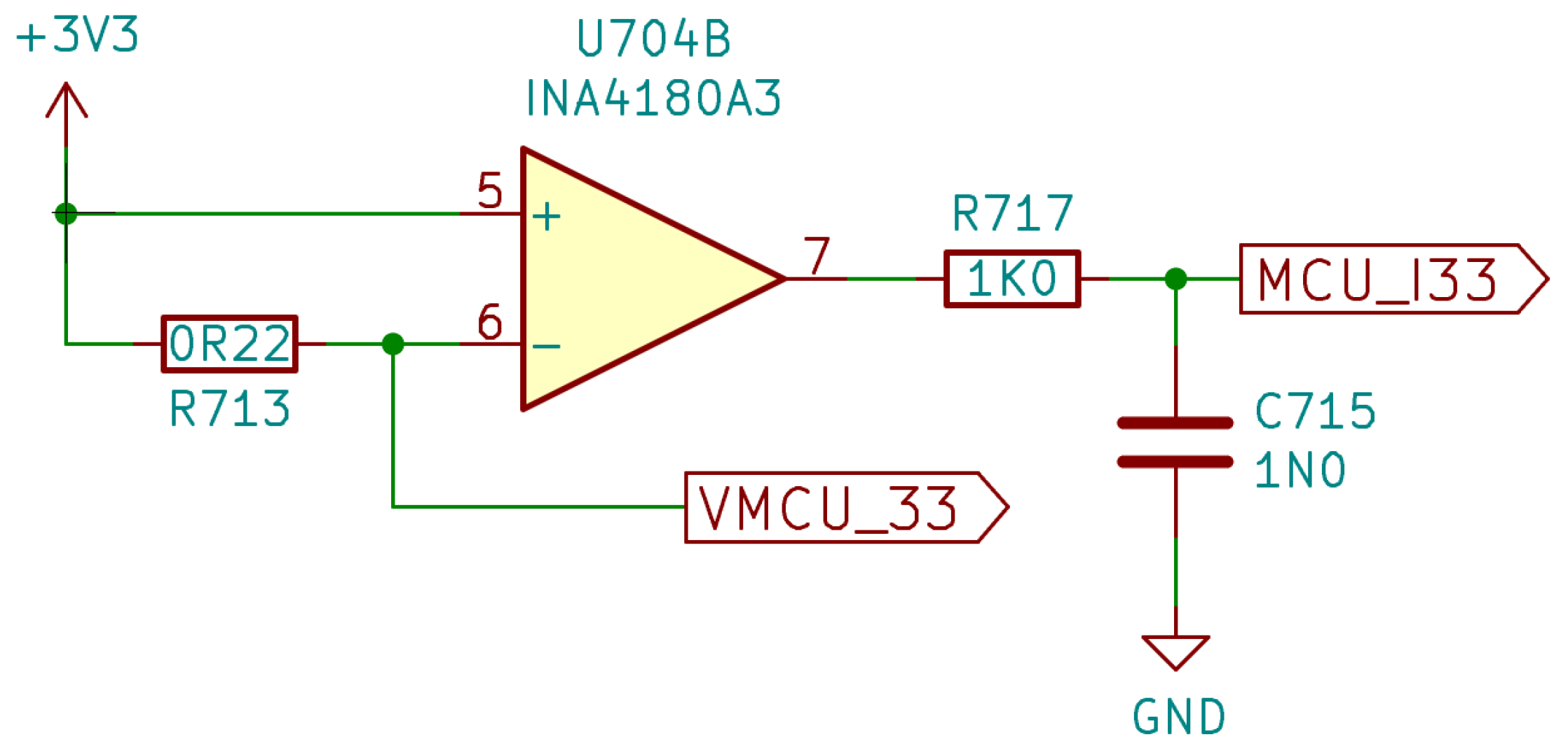

3.1.2. Multimeter

3.1.3. Analog Signal Generator

3.1.4. Logic State Analyzer

3.1.5. Digital Pattern Generator

3.2. Master Section Implementation

- Master MCU.

- Master FPGA.

- Master QSPI flash.

- Master HyperBUS RAM.

3.2.1. Master MCU

- -

- Core clock frequency: 80 MHz;

- -

- Flash memory: 512 kBytes (two equally sized independent banks);

- -

- RAM memory: 320 kBytes;

- -

- QUADSPI high-speed interface;

- -

- Multiple communication interfaces (SPI/UART/I2C/CAN);

- -

- One USB-OTG interface;

- -

- Five Msps, 12 bit, triple ADCs, with hardware oversampling;

- -

- Two channels, 12 bit DAC;

- -

- Two operational amplifiers;

- -

- Two comparators;

- -

- Fourteen-channel DMA controller;

- -

- A 1.7 V to 3.6 V power supply.

- -

- Voltage input channel 1 (compensated probe);

- -

- Voltage input channel 2 (compensated probe);

- -

- Supply current of user FPGA I/O (3.3 V);

- -

- Supply current of user FPGA PLL (2.5 V);

- -

- Supply current of user FPGA core (1.2 V);

- -

- Supply current of user MCU (3.3 V).

3.2.2. Master FPGA

3.2.3. External Storage

3.3. User Section Specifications

3.4. User Section Implementation

- Four low-power green LEDs attached to dedicated pins of the user FPGA.

- Four low-power green LEDs attached to dedicated pins of the user microcontroller.

- One four-digit, seven-segment LCD display. It is directly attached to the user MCU, as this one contains an LCD driver, easily managed through register mapped bits (one bit per segment).

- Eight small switches, attached both to the MCU and the FPGA. To have immediate feedback on the effective switch position, every switch is connected to a yellow LED, which is turned on if the switch is in the “on” position, corresponding to a logic ‘1’ on the corresponding input.

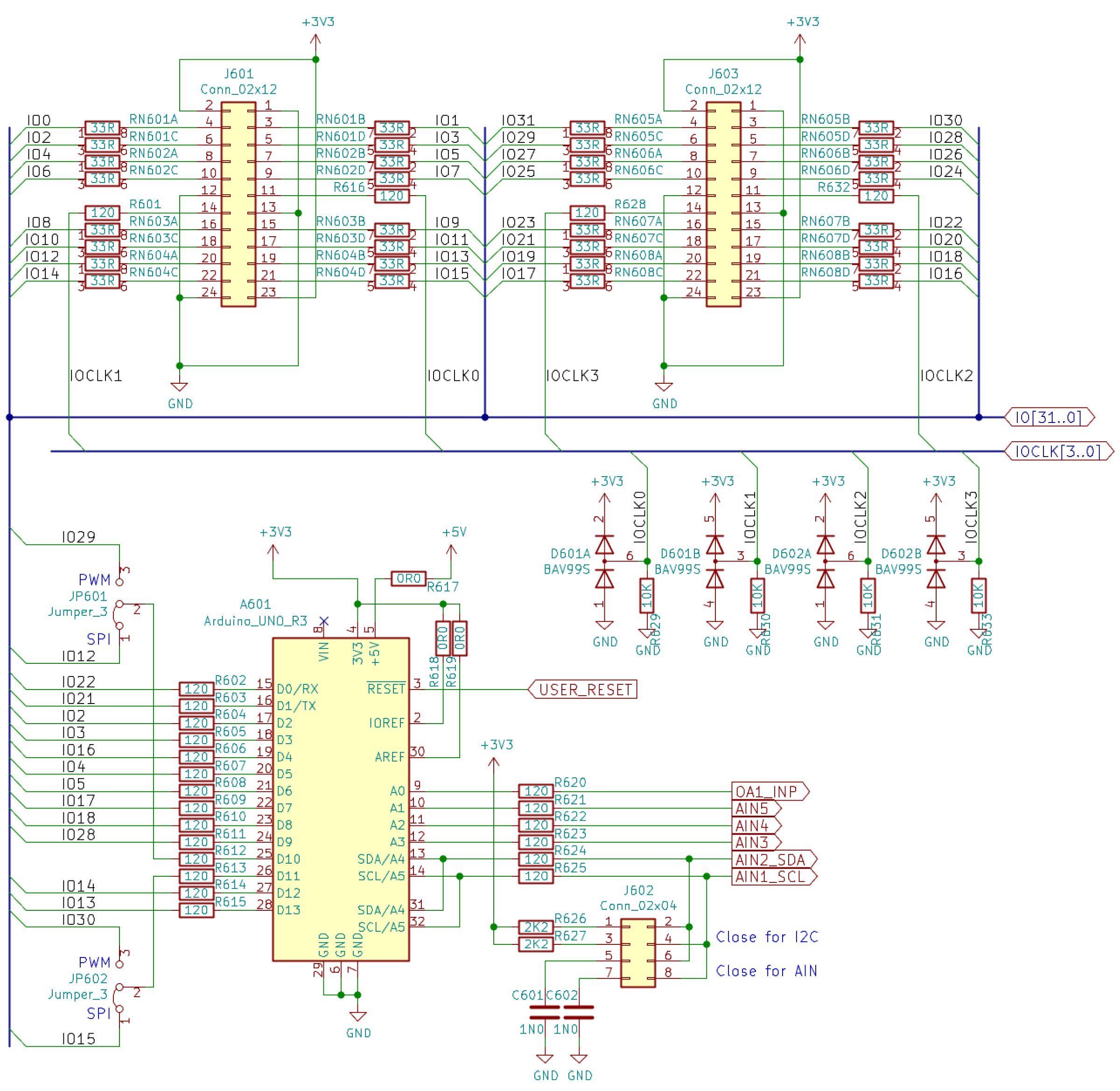

3.5. Connectivity

3.5.1. External Connections

3.5.2. Internal Connections

- General purpose 32 bit digital I/O bus. It connects external signals to the user FPGA, the user MCU, and the master MCU. The last connection is present only for bits 0–9.

- Double serial channel, from master MCU to user FPGA. Protocols supported are UART, I2C, and CAN.

- QSPI connection, from master MCU to master FPGA.

3.6. Power Supply

- A 3.3 V @ 2 A: MCU, FPGA I/O, and external connectors;

- A 2.5 V @ 100 mA: FPGA PLL low noise analog supply;

- A 1.2 V @ 2 A: FPGA core.

3.7. MCU Programming Interface

- ARM MCU programmer;

- High-speed (15Mb/s) serial interface;

- SPI, I2C, UART, GPIO expansion.

4. Conclusions and Future Work

- Flexibility. Everything is fully programmable, both on the student and on the teacher side. This means that new experiments and new virtual instruments can be freely implemented by just changing the firmware of the MCUs and FPGA configuration.

- Scalability. Devices were chosen to allow for ‘family migration’. As an example, the same footprint can host FPGAs ranging from 6 k to 25 k LEs, and the same applies to MCUs, in which, the same device can be used with different internal memory sizes. This also applies to the HyperRAM, too. This means that a ‘university edition’ of the board, used in campus laboratories, can be built maximizing available hardware resources (and costs), and a ‘student edition’ directly bought by students will be realized with minimum cost hardware.

- Low cost. As the board is specifically designed for teaching, its cost is in the order of USD 70. This is remarkable, as it substitutes an entire set of boards and measurement instruments.

- Digital integrated systems: Master’s degree in Electronic Engineering, 90 students.

- System level low power techniques for IoT: PhD course in Electrical, Electronics, and Telecommunications engineering, 26 students.

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Tropea, M.; Rango, F.D. COVID-19 in Italy: Current state, impact and ICT-based solutions. IET Smart Cities 2020, 2, 4–81. [Google Scholar] [CrossRef]

- Kiss, G. Comparison of traditional and web-based education-case study “BigBlueButton”. In Proceedings of the 2012 International Symposium on Information Technologies in Medicine and Education, Hokodate, Hokkaido, Japan, 3–5 August 2012; pp. 224–227. [Google Scholar] [CrossRef]

- Vasconcelos, P.R.M.; Freitas, G.A.d.; Marques, T.G. Virtualization technologies in web conferencing systems: A performance overview. In Proceedings of the 2016 11th International Conference for Internet Technology and Secured Transactions (ICITST), Barcelona, Spain, 5–7 December 2016; pp. 376–383. [Google Scholar] [CrossRef]

- Roch, M.R.; Graziano, M. Teaching in the Cloud-Microelectronics Ubiquitous LAB (MULAB). In Proceedings of the 9th European Workshop on Microelectronics Education (EWME)”, Grenoble, France, 9–11 May 2012; pp. 131–135. [Google Scholar]

- Roch, M.R.; Demarchi, D.; Klossek, M.; Tzanova, S. MECA, the microelectronics cloud alliance. In Proceedings of the 2018 IEEE Global Engineering Education Conference (EDUCON), Tenerife, Spain, 17–20 April 2018; pp. 1419–1423. [Google Scholar] [CrossRef]

- Available online: http://www.moodle.org (accessed on 25 March 2022).

- Magdin, M.; Cápay, M.; Halmeš, M. Implementation of LogicSim in LMS Moodle. In Proceedings of the 2012 IEEE 10th International Conference on Emerging eLearning Technologies and Applications (ICETA), Stara Lesna, Slovakia, 8–9 November 2012; pp. 57–59. [Google Scholar] [CrossRef]

- Alajbeg, T.; Sokele, M. Implementation of Electronic Design Automation software tool in the learning process. In Proceedings of the 2019 42nd International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), Opatija, Croatia, 20–24 May 2019; pp. 532–536. [Google Scholar] [CrossRef]

- Available online: https://moodlearchive.epfl.ch/2018-2019/mod/resource/view.php?id=992416 (accessed on 15 June 2022).

- Available online: https://moodlearchive.epfl.ch/2018-2019/mod/resource/view.php?id=930697 (accessed on 15 June 2022).

- Available online: https://moodlearchive.epfl.ch/2018-2019/mod/resource/view.php?id=934591 (accessed on 15 June 2022).

- Zappa, F. Microcontrollers. Hardware and Firmware for 8-bit and 32-bit Devices; Società Editrice Esculapio: Bologna, Italy, 2020; ISBN 9788835817512. [Google Scholar]

- Available online: https://digilent.com/shop/analog-discovery-2-100ms-s-usb-oscilloscope-logic-analyzer-and-variable-power-supply/ (accessed on 10 May 2022).

- Mobile Studio Project. Available online: http://www.mobilestudioproject.com (accessed on 10 May 2022).

- Letowski, B.; Lavayssière, C.; Larroque, B.; Schröder, M.; Luthon, F. A Fully Open Source Remote Laboratory for Practical Learning. Electronics 2020, 9, 1832. [Google Scholar] [CrossRef]

- Monzo, C.; Cobo, G.; Morán, J.A.; Santamaría, E.; García-Solórzano, D. Lab@Home: The Open University of Catalonia Hands-on Electronics Laboratory for Online Engineering Education. Electronics 2020, 9, 222. [Google Scholar] [CrossRef] [Green Version]

- Roch, M.R.; Martina, M. vrLab: A Virtual and Remote Low Cost Electronics Lab Platform. In Proceedings of the Conference on Applications in Electronics Pervading Industry, Environment and Society, Genova, Italy, 26–27 September 2021; Volume 738, pp. 213–220. [Google Scholar] [CrossRef]

- IEEE Std 1876–2019; IEEE Standard for Networked Smart Learning Objects for Online Laboratories. IEEE SA: Piscataway, NJ, USA, 2019; pp. 1–57. [CrossRef]

| Input | Bits | Resolution | Gain | Range | Bandwidth |

|---|---|---|---|---|---|

| Channel 1 | 12 | 0.5 mV | 1 V/V | 0–2.048 V | 1 MHz |

| Channel 2 | 12 | 0.5 mV | 1 V/V | 0–2.048 V | 1 MHz |

| FPGA 3.3 V current | 12 | 0.022 mA | 22 V/A | 0–93 mA | 150 kHz |

| FPGA 2.5 V current | 12 | 0.125 mA | 4 V/A | 0–512 mA | 150 kHz |

| FPGA 1.2 V current | 12 | 0.125 mA | 4 V/A | 0–512 mA | 150 kHz |

| MCU 3.3 V current | 12 | 0.022 mA | 22 V/A | 0–93 mA | 150 kHz |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ruo Roch, M.; Martina, M. VirtLAB: A Low-Cost Platform for Electronics Lab Experiments. Sensors 2022, 22, 4840. https://doi.org/10.3390/s22134840

Ruo Roch M, Martina M. VirtLAB: A Low-Cost Platform for Electronics Lab Experiments. Sensors. 2022; 22(13):4840. https://doi.org/10.3390/s22134840

Chicago/Turabian StyleRuo Roch, Massimo, and Maurizio Martina. 2022. "VirtLAB: A Low-Cost Platform for Electronics Lab Experiments" Sensors 22, no. 13: 4840. https://doi.org/10.3390/s22134840

APA StyleRuo Roch, M., & Martina, M. (2022). VirtLAB: A Low-Cost Platform for Electronics Lab Experiments. Sensors, 22(13), 4840. https://doi.org/10.3390/s22134840