NaviSoC: High-Accuracy Low-Power GNSS SoC with an Integrated Application Processor

Abstract

1. Introduction

2. SoC Overview and RF Architecture

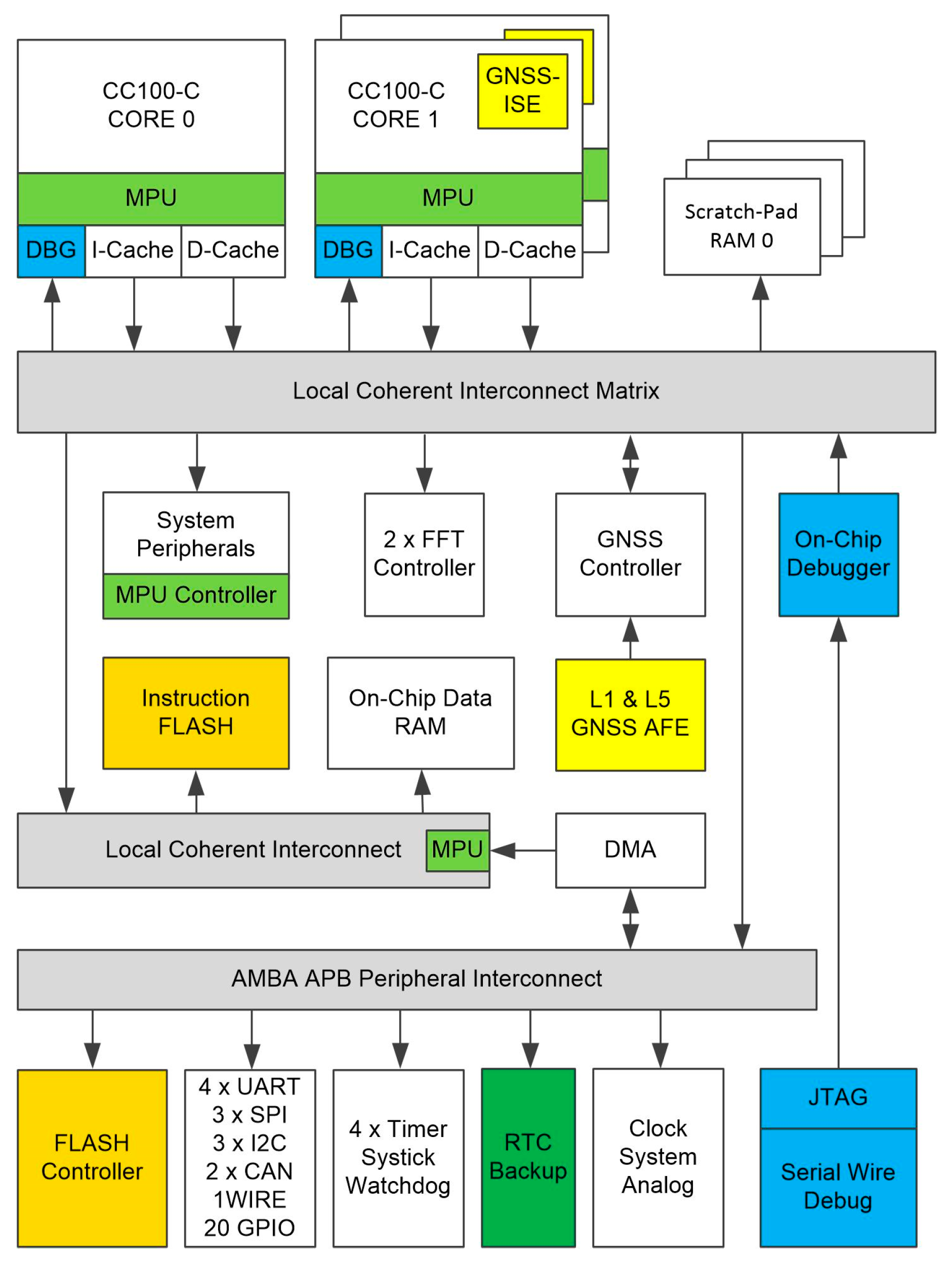

2.1. SoC Overview

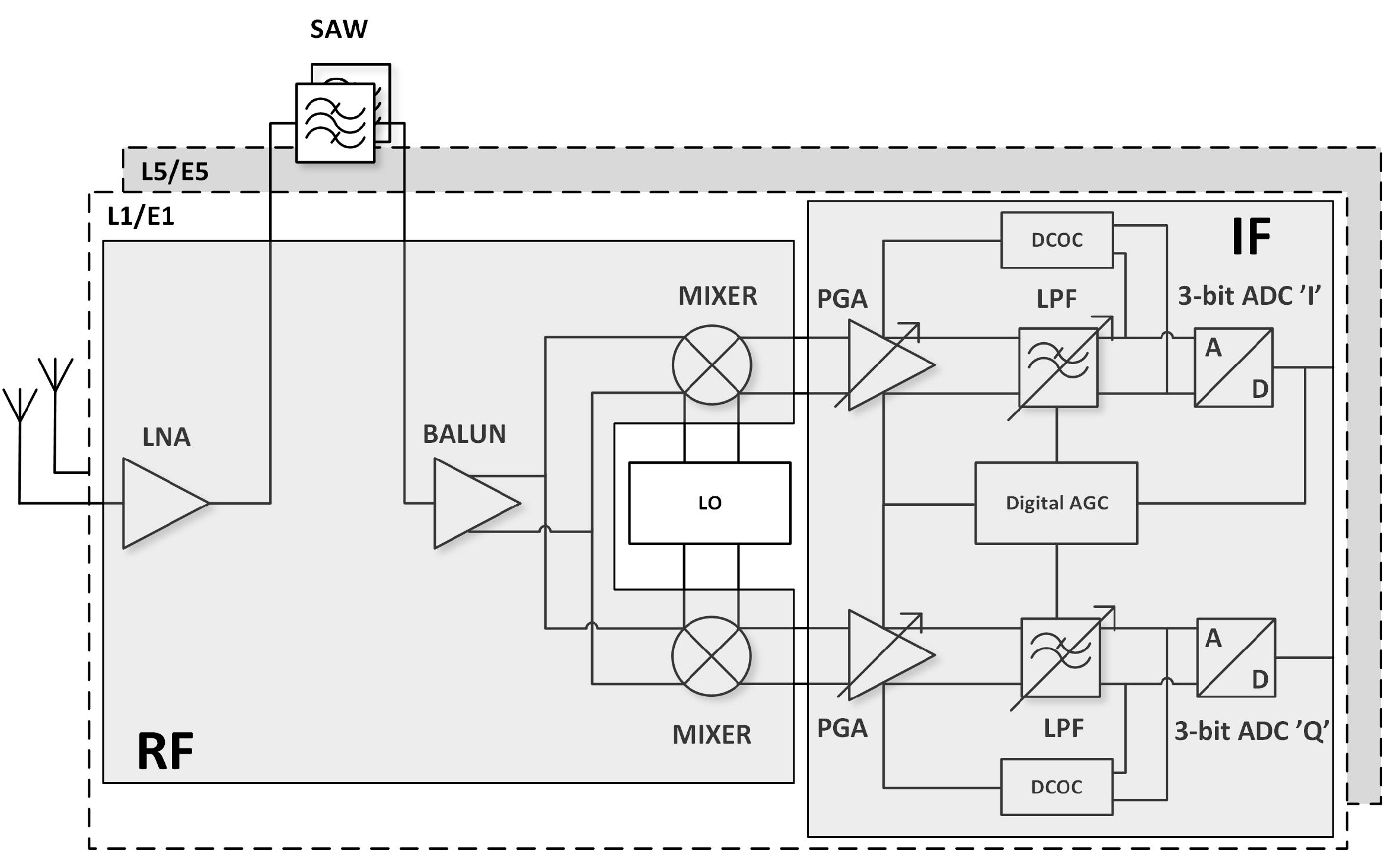

2.2. Radio Architecture for GNSS Signals

- RF circuits that amplify and filter the GNSS signals received from an external passive antenna and pass them to the mixers,

- An LO (local oscillator) generation module implemented as an ADPLL (all-digital phase-locked loop),

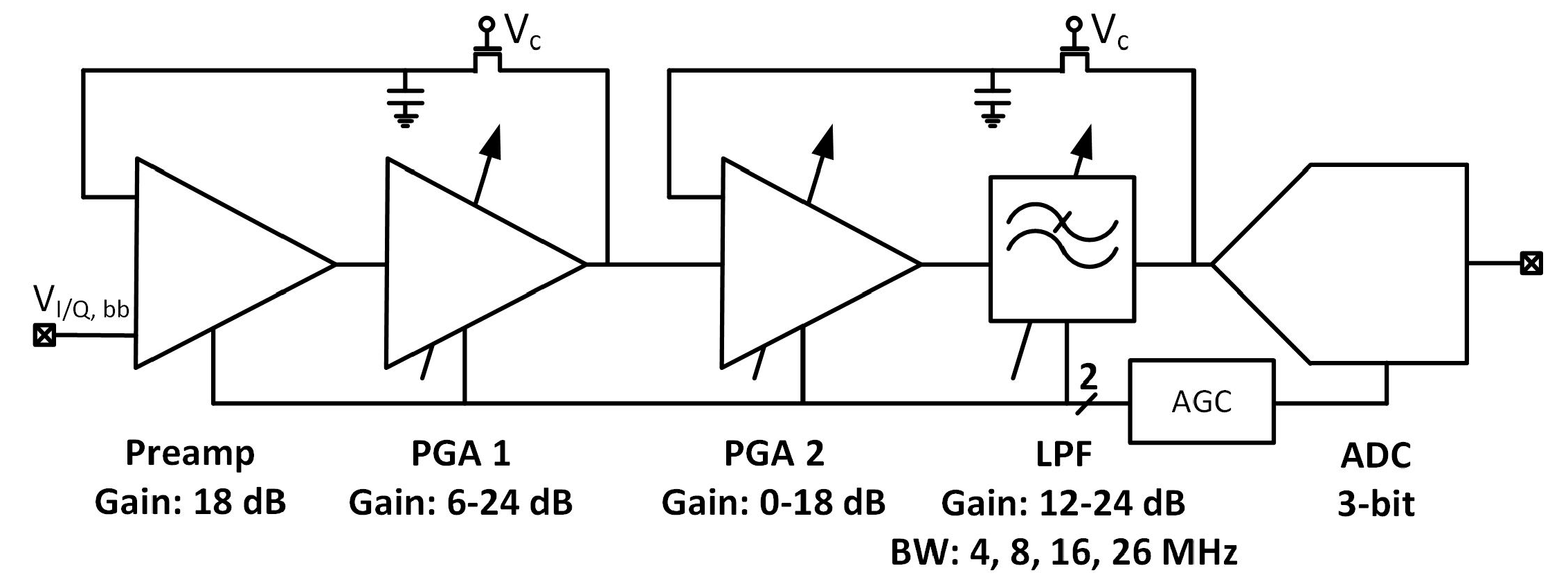

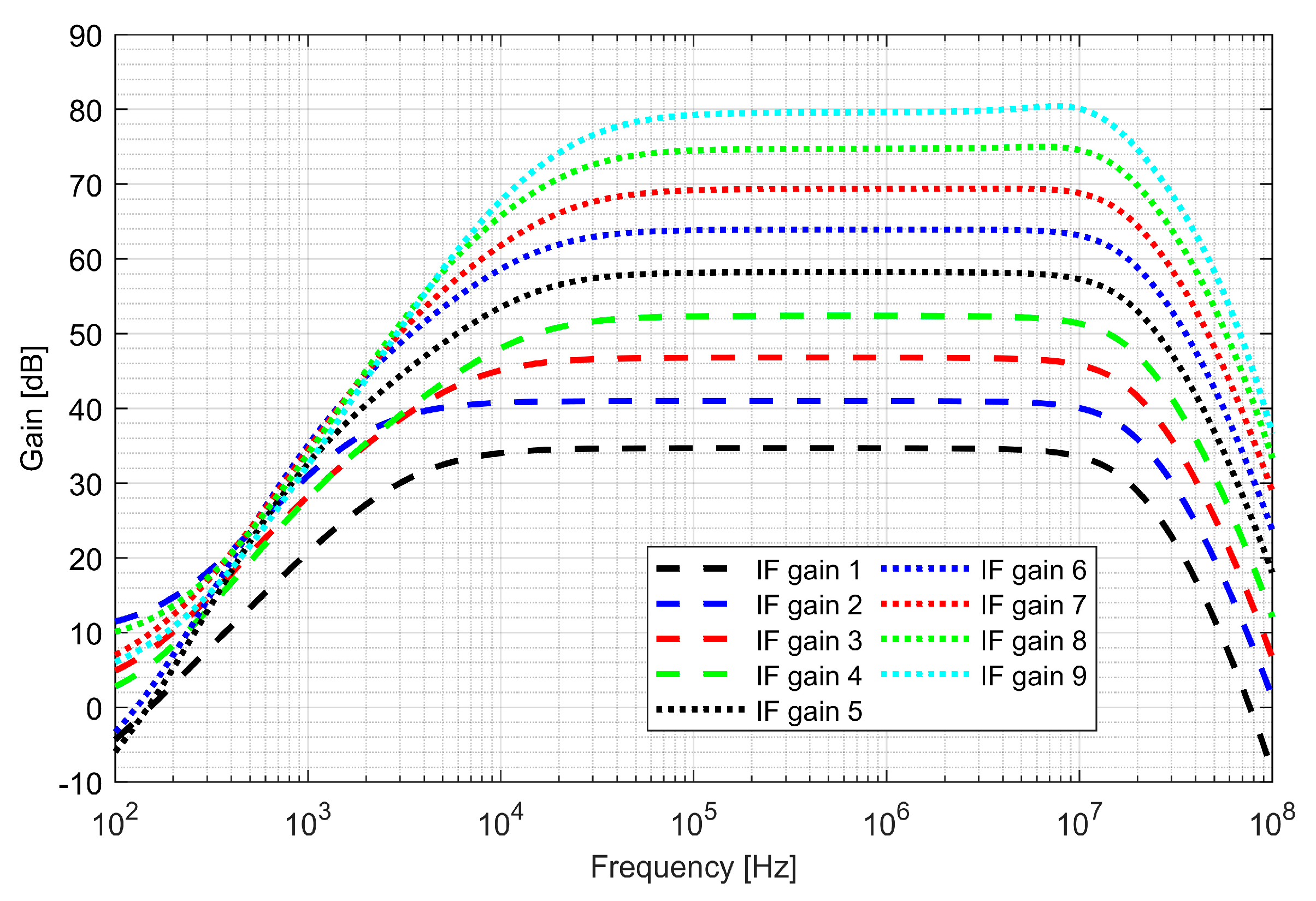

- IF (intermediate frequency) blocks (programmable gain amplifier (PGA), low pass filter (LPF), automatic gain control (AGC)) that process low-frequency I/Q (in-phase and quadrature) signals for 3-bit complex analog-to-digital converters (ADC).

2.3. Frequency Planning for Dual-Frequency Receiver

3. Circuit Implementation

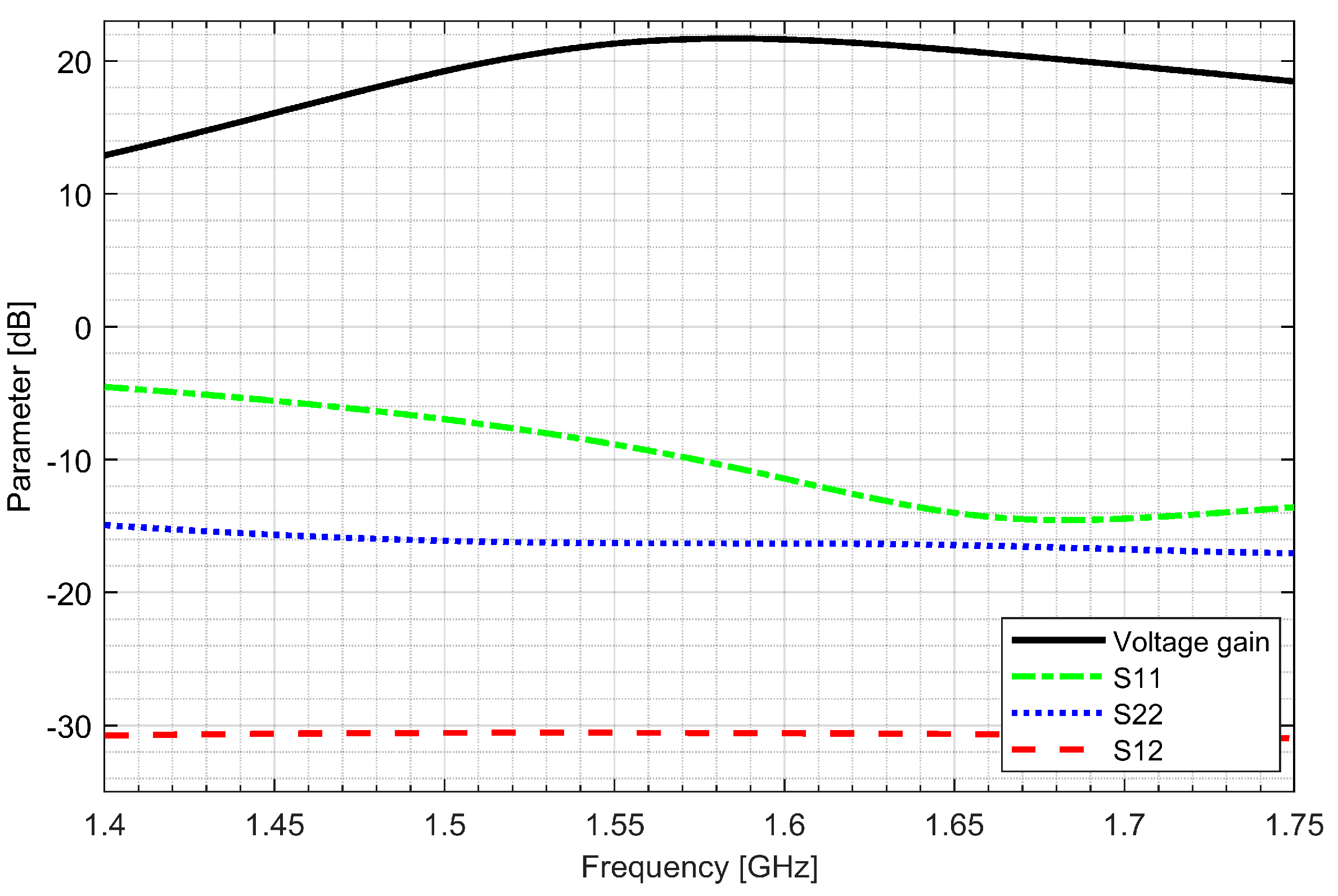

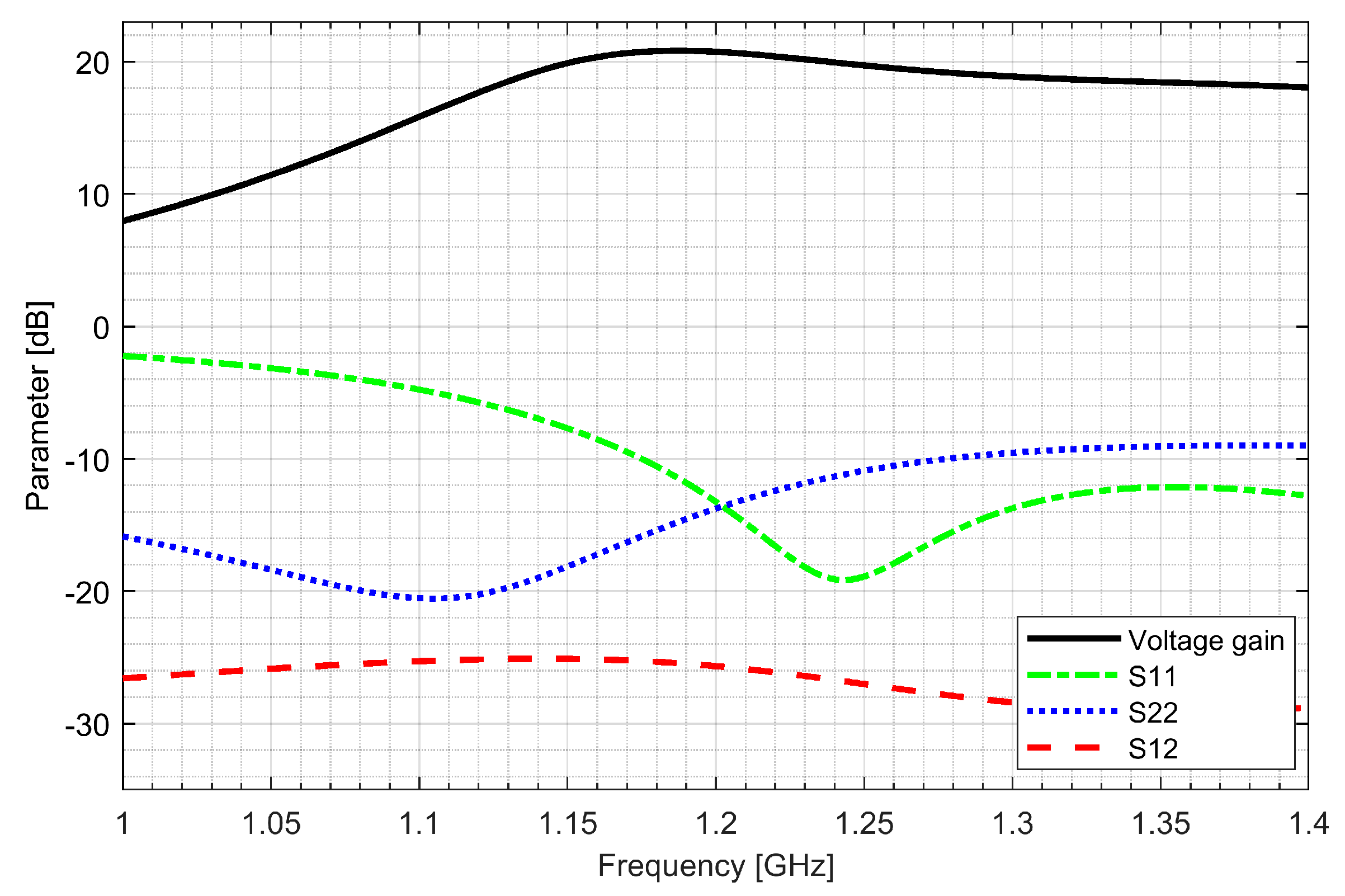

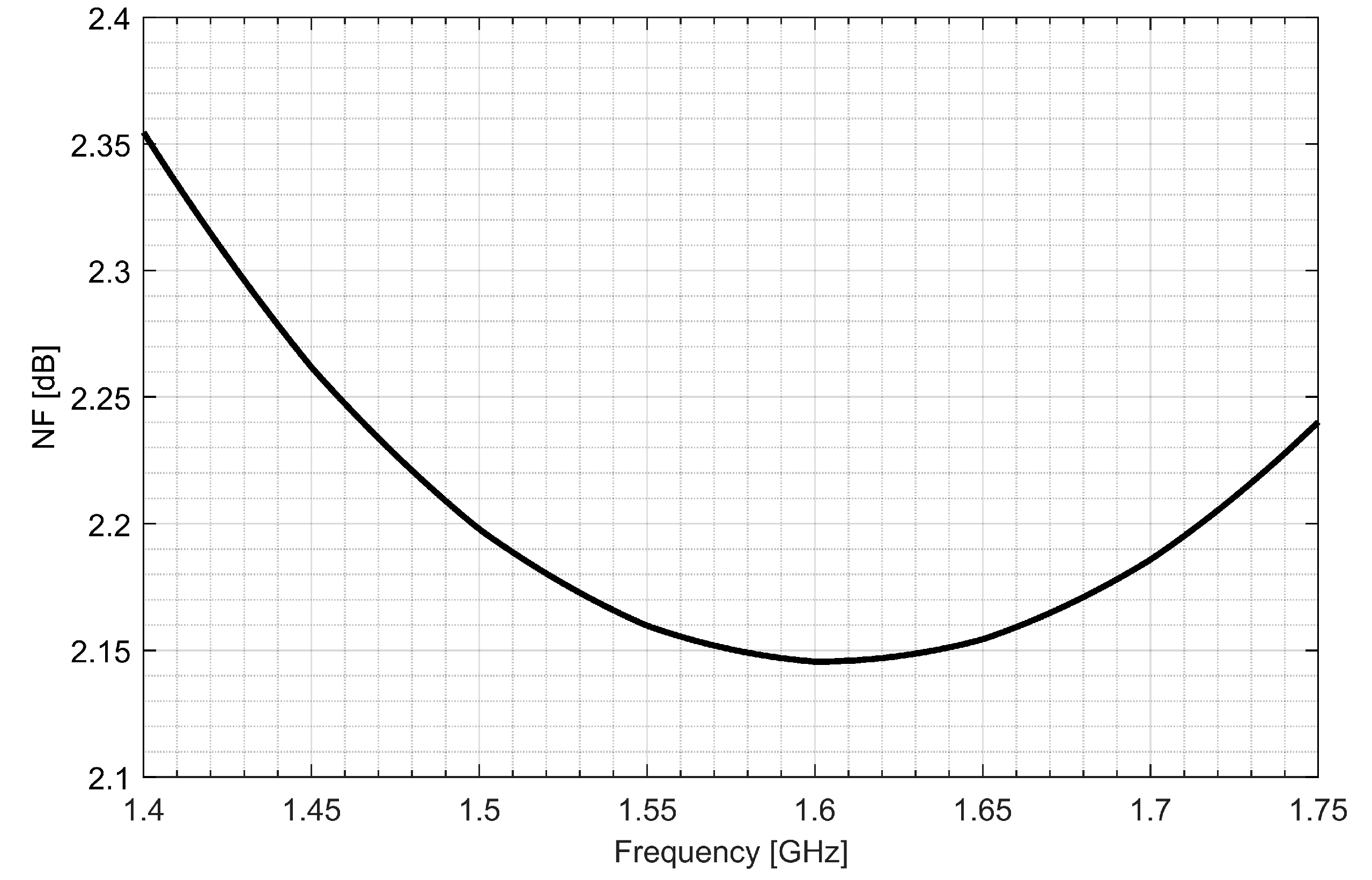

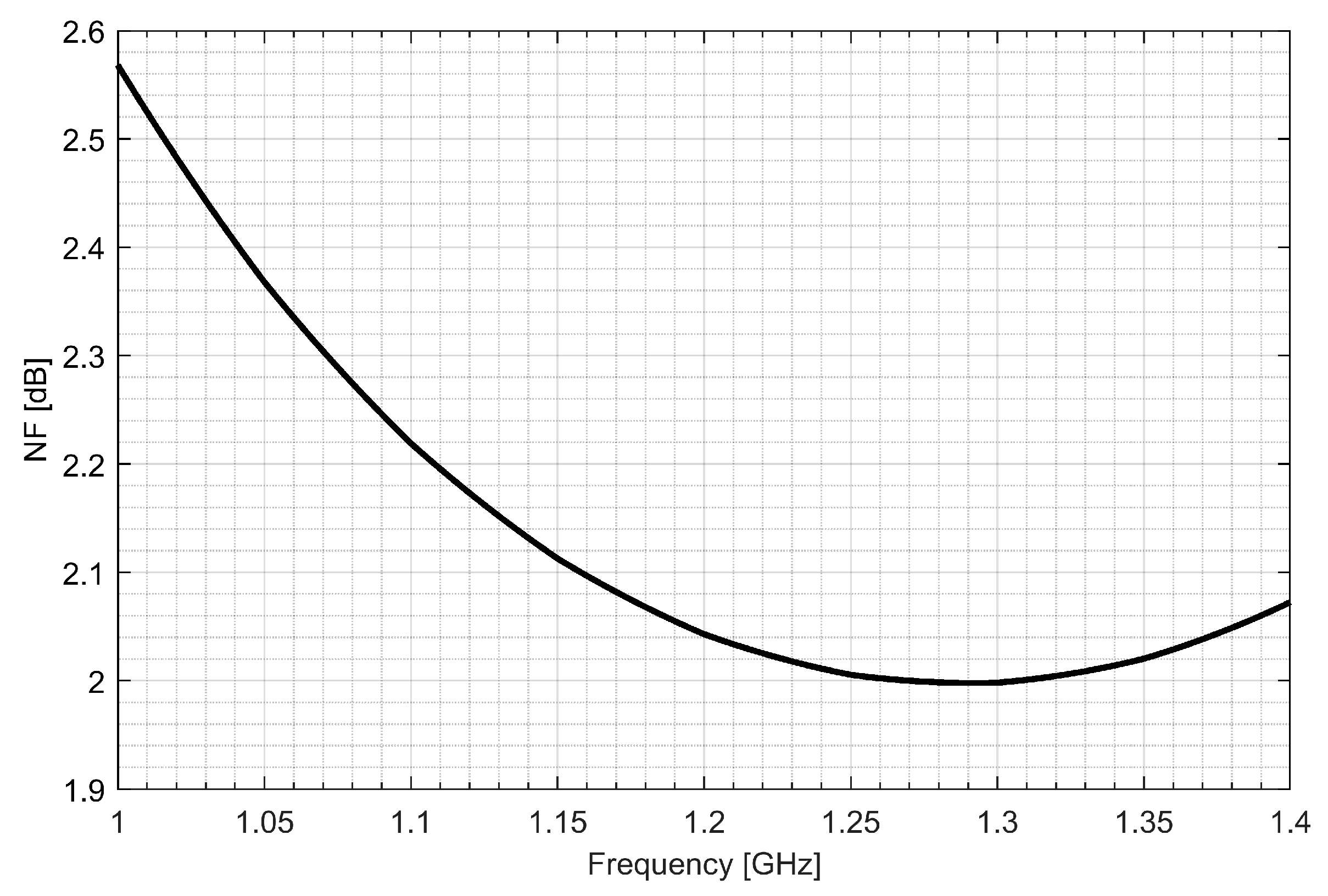

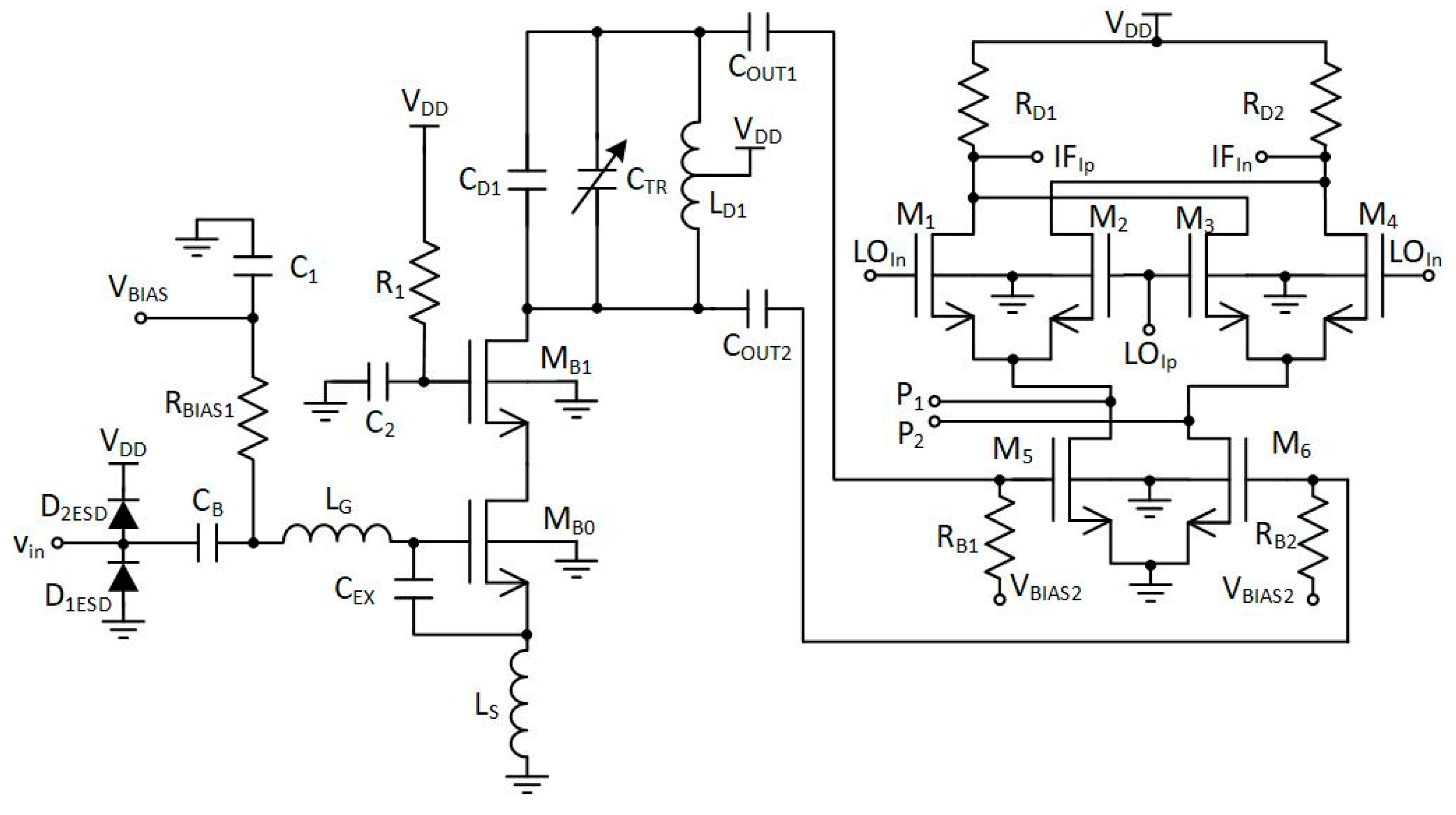

3.1. Low-Noise Amplifier

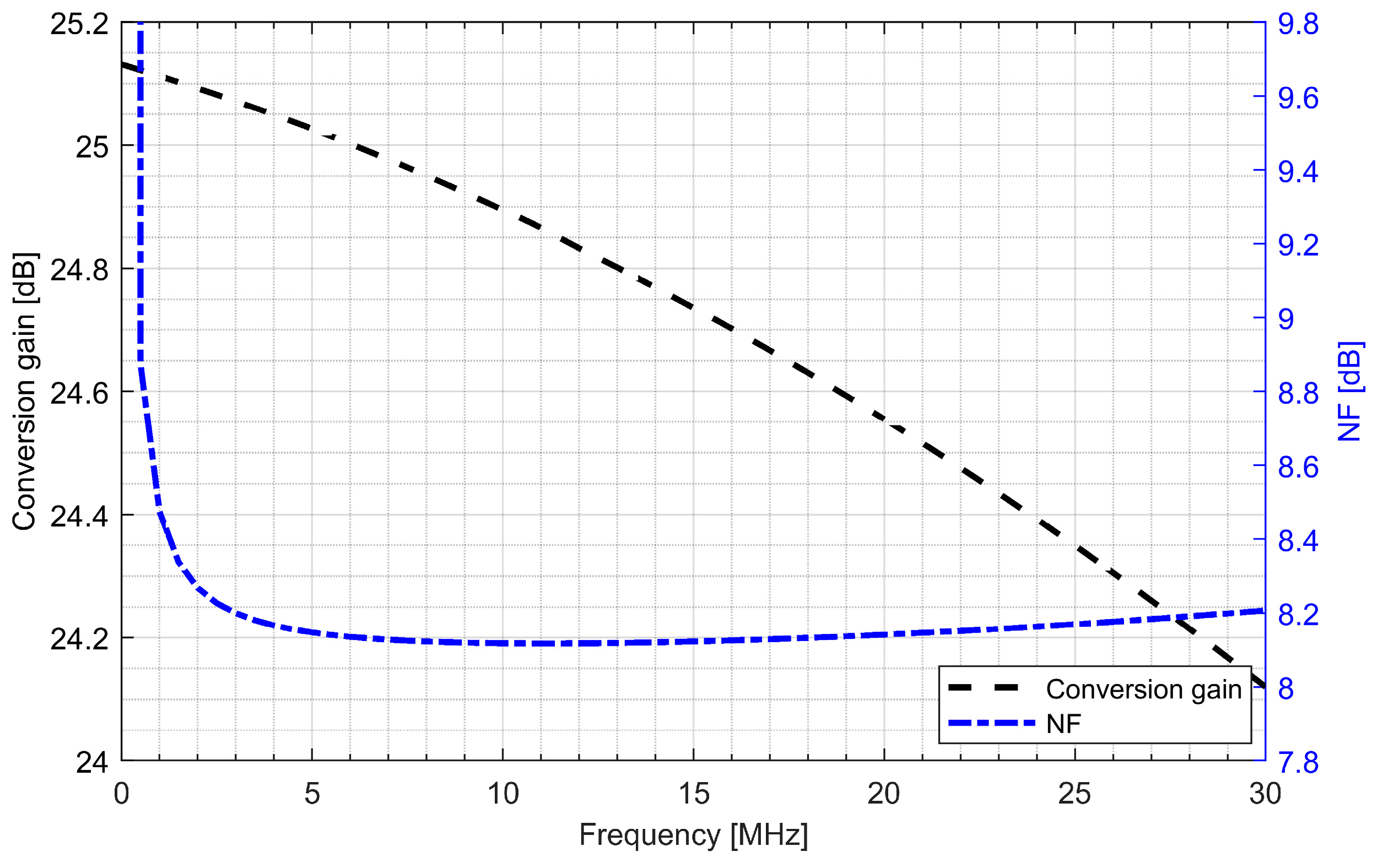

3.2. Active Balun and Down-Conversion Mixer

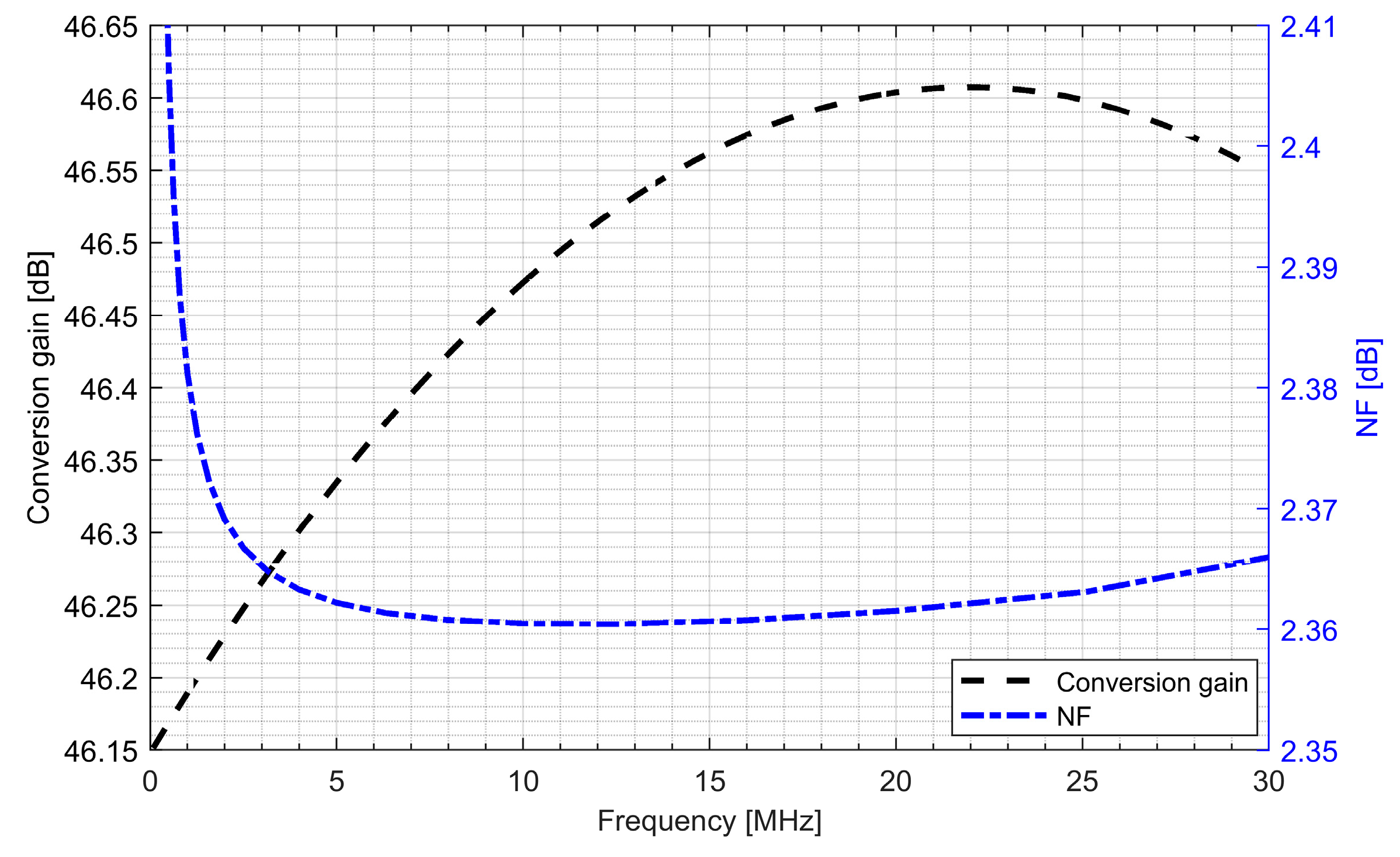

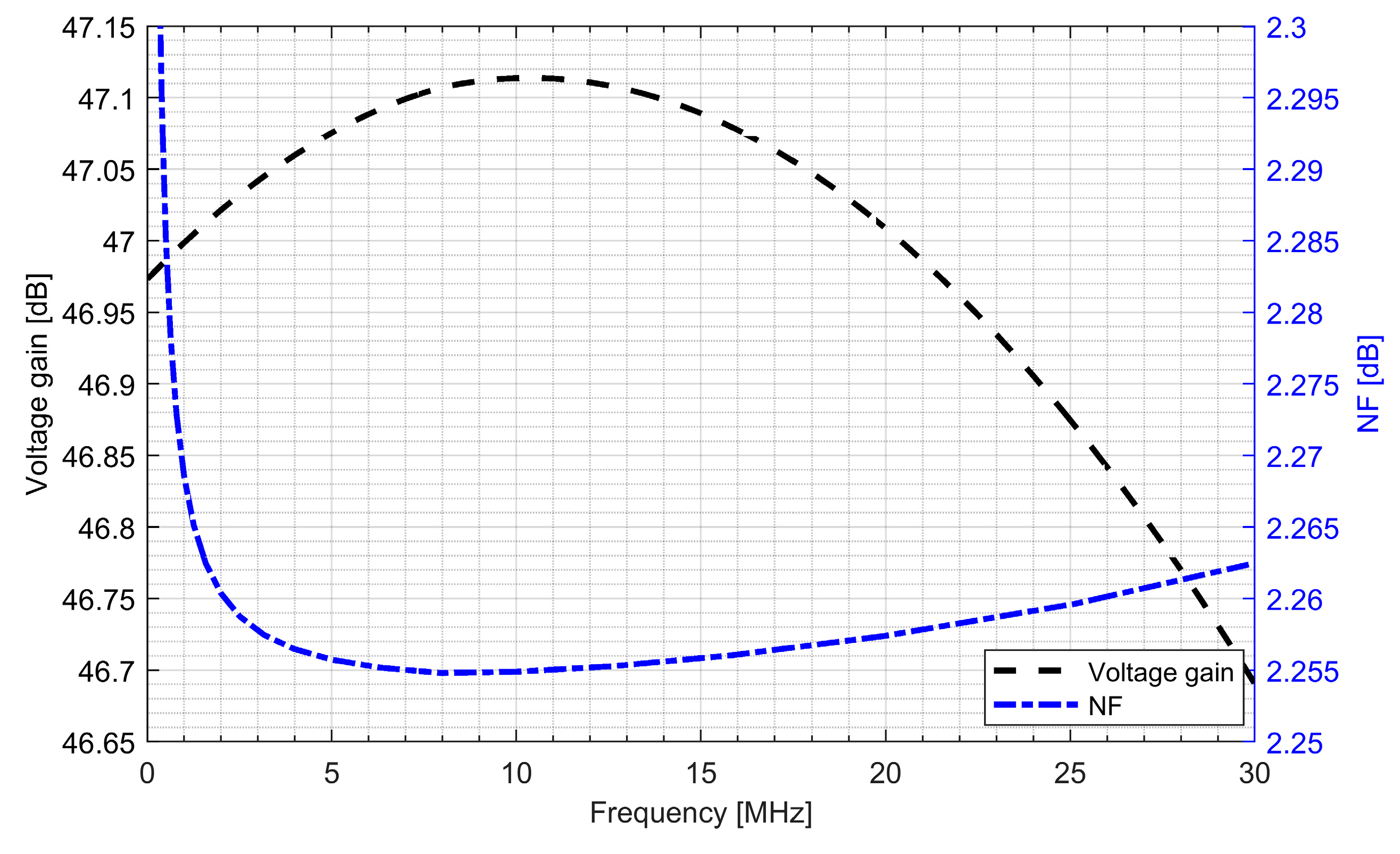

3.3. Radio-Frequency Front-End

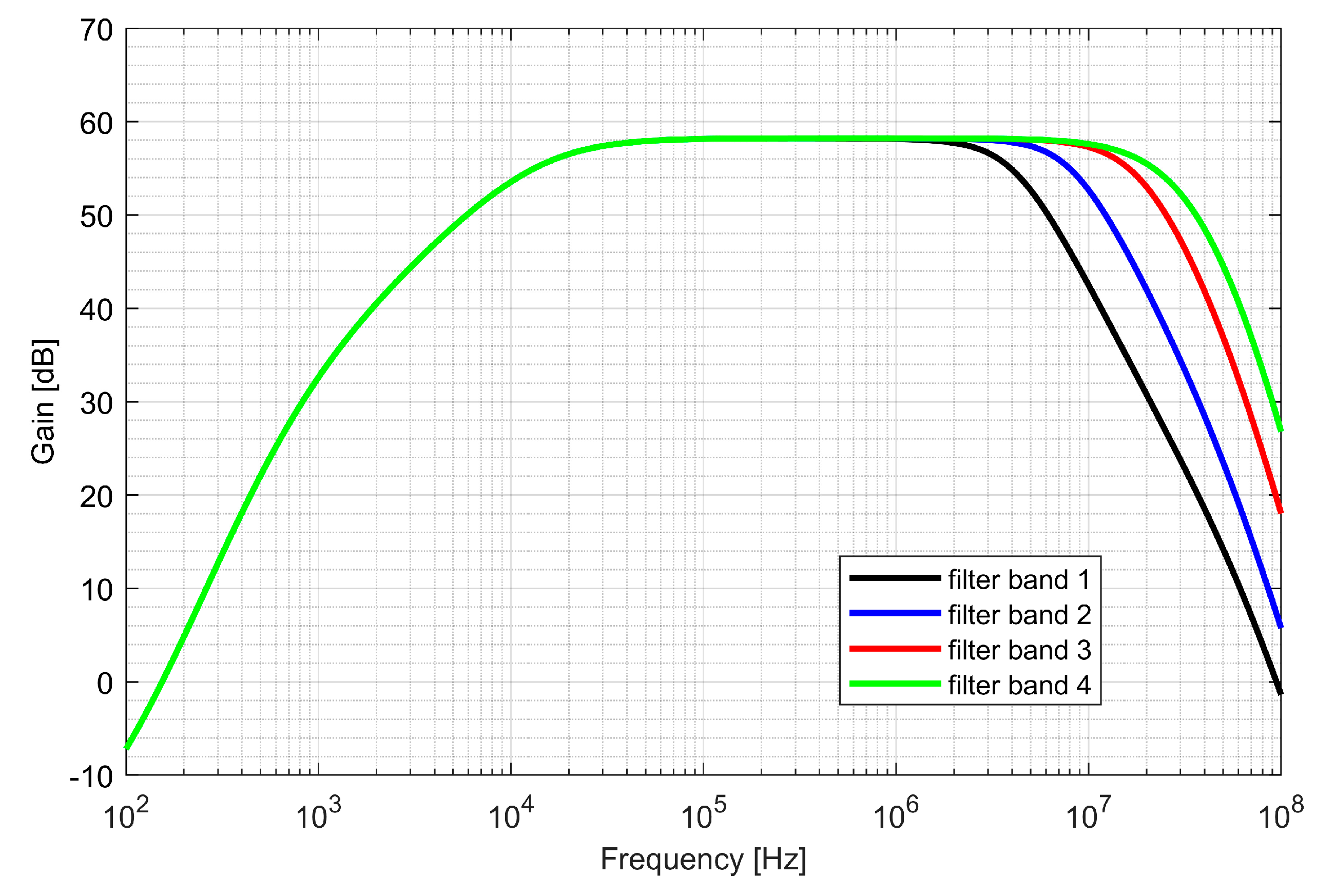

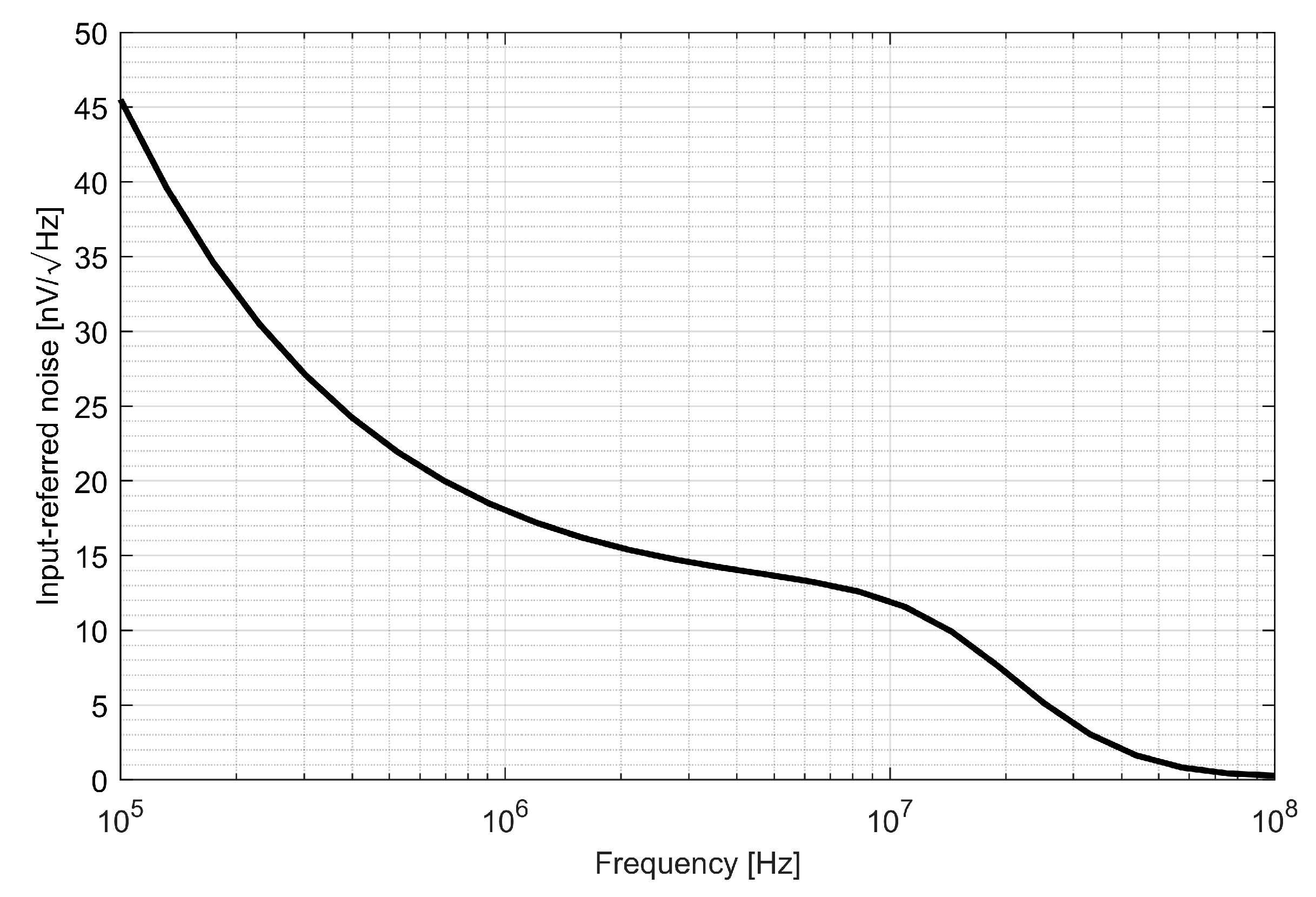

3.4. Intermediate Frequency Block and ADC

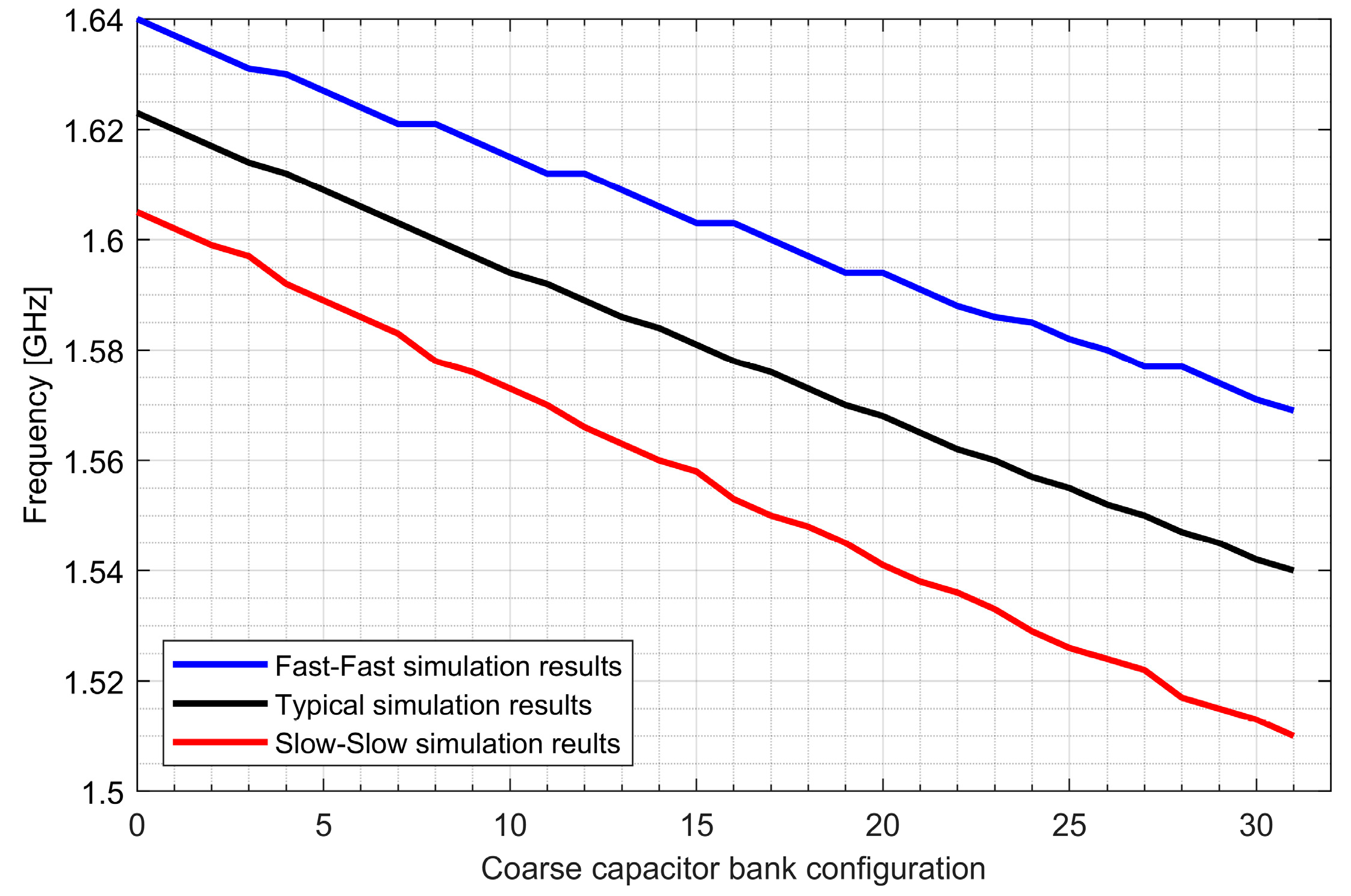

3.5. Frequency Synthesizer and I/Q LO Signal Generation

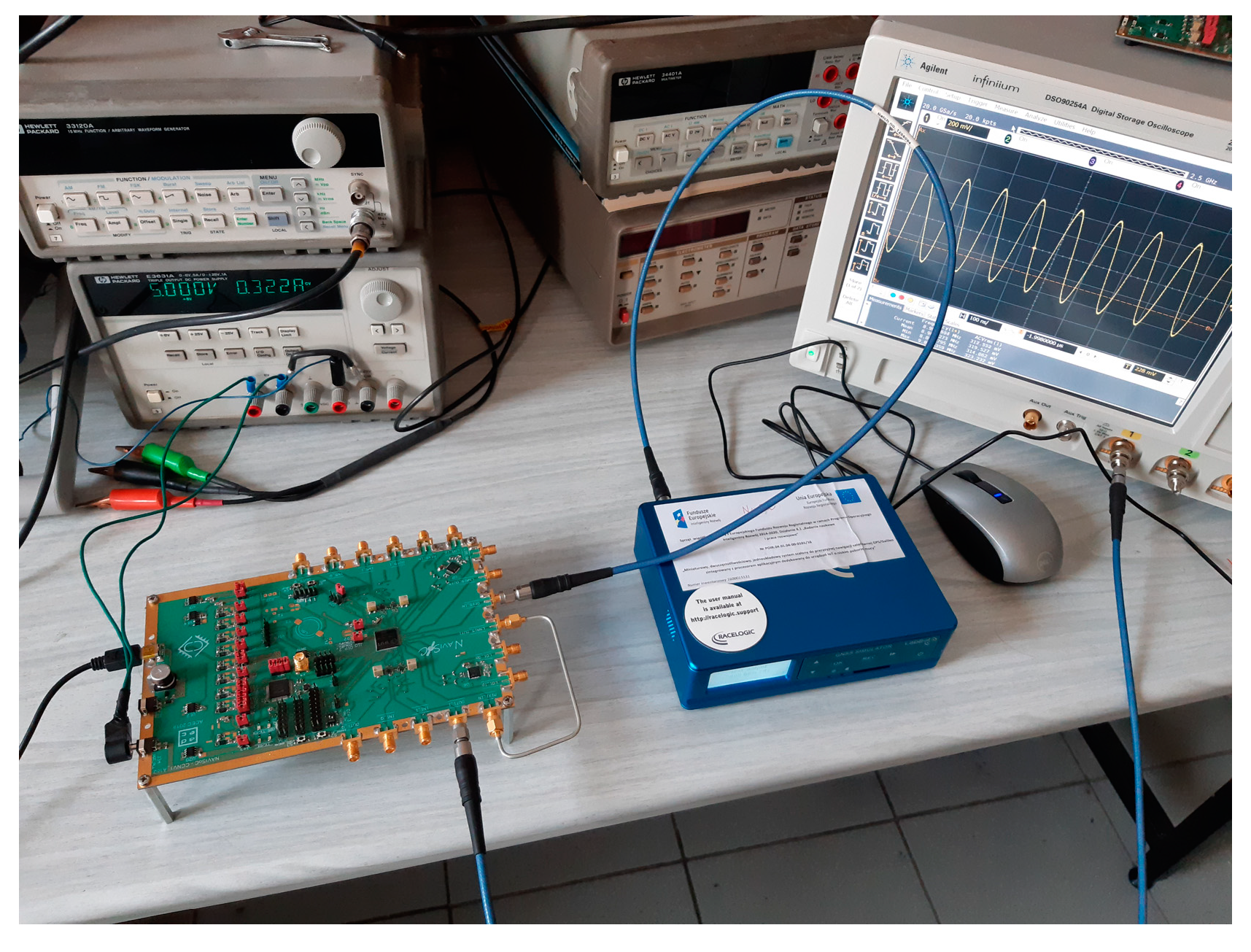

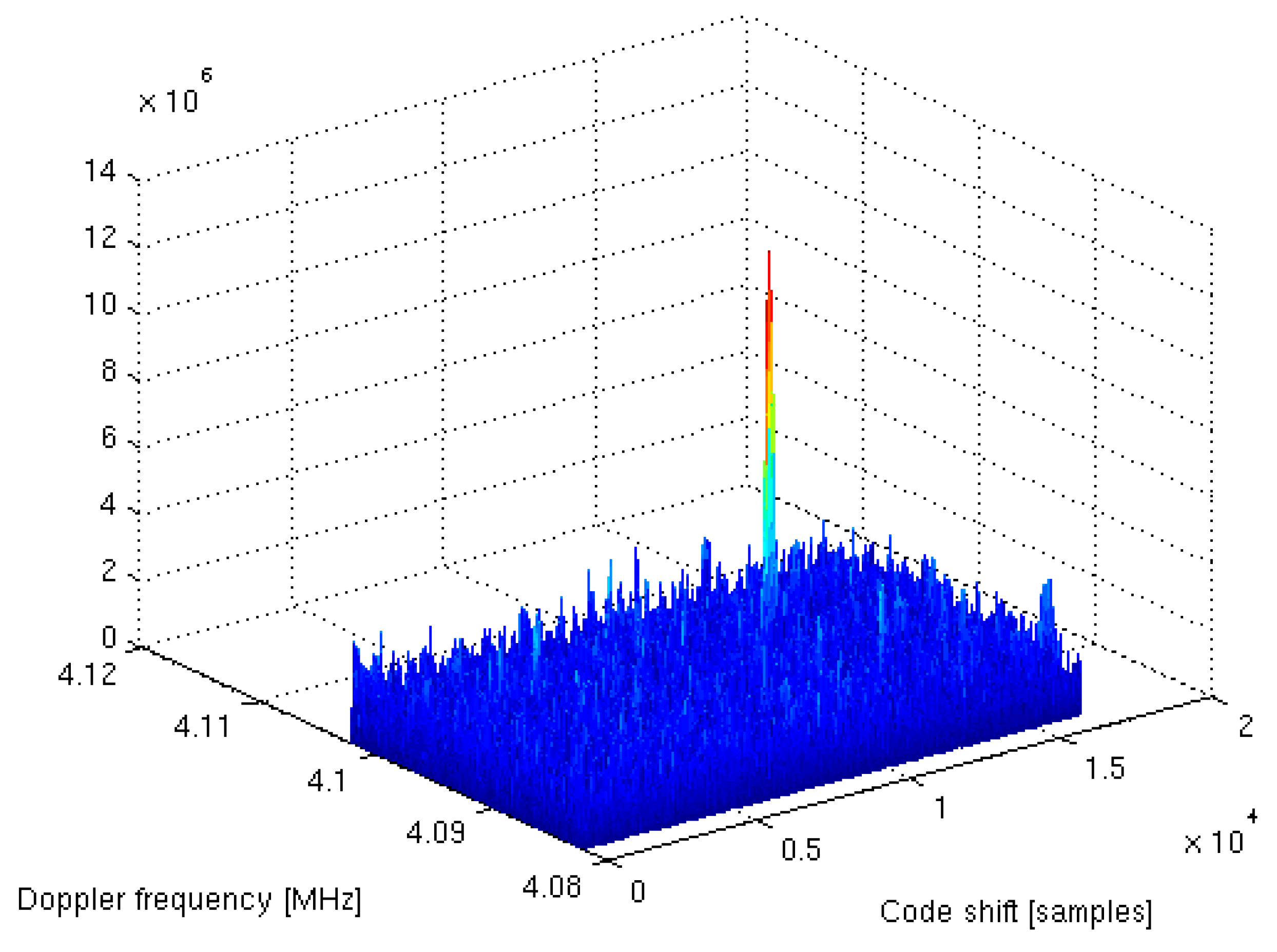

4. System-on-Chip Verification

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Fernandez-Prades, C.; Lo Presti, L.; Falletti, E. Satellite Radiolocalization From GPS to GNSS and Beyond: Novel Technologies and Applications for Civil Mass Market. Proc. IEEE 2011, 99, 1882–1904. [Google Scholar] [CrossRef]

- GNSS Market Report, Issue 5, Publications Office of the European Union, Copyright© European GNSS Agency. 2017. Available online: https://www.gsa.europa.eu/system/files/reports/gnss_mr_2017.pdf (accessed on 16 November 2019).

- Kadoyama, T.; Suzuki, N.; Sasho, N.; Iizuka, I.; Nagase, I.; Usukubo, H.; Katakura, M. A complete single-chip GPS receiver with 1.6-V 24-mW radio in 0.18-µm CMOS. IEEE J. Solid-State Circuits 2004, 39, 562–568. [Google Scholar] [CrossRef]

- Sahu, D.; Das, Q.; Darwhekar, Y.; Ganesan, S.; Rajendran, G.; Kumar, R.; Chandrashekar, B.G.; Gosh, A.; Gaurav, A.; Krishnaswamy, T.; et al. A 90 nm CMOS single-chip GPS receiver with 5 dBm out-of-band IIP3 and 2.0 dB NF. In Proceedings of the IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 2005; pp. 308–309. [Google Scholar] [CrossRef]

- Gramegna, G.; Mattos, P.G.; Losi, M.; Das, S.; Franciotta, M.; Bellantone, N.G.; Vaiana, M.; Mandara, V.; Paparo, M. A 56-mVienna, AustriaW 23-mm2 single-chip 180-nm CMOS GPS receiver with 27.2-mW 4.1-mm2 radio. IEEE J. Solid State Circuits 2006, 41, 540–551. [Google Scholar] [CrossRef]

- Wei, J.-M.; Chen, C.-N.; Chen, K.-T.; Kuo, C.-F.; Ong, B.-H.; Lu, C.-H.; Liu, C.-C.; Chiou, H.-C.; Yeh, H.-C.; Shieh, J.-H.; et al. A 110 nm RFCMOS GPS SOC with 34 mW -165dBm tracking sensitivity. In Proceedings of the IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 8–12 February 2009; pp. 254–255. [Google Scholar] [CrossRef]

- Moon, H.; Lee, S.; Heo, S.-C.; Yu, H.; Yu, J.; Chang, J.-S.; Choi, S.-I.; Park, B.-H. A 23 mW fully integrated GPS receiver with robust interferer rejection in 65 nm CMOS. In Proceedings of the IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 7–11 February 2010; pp. 68–69. [Google Scholar] [CrossRef]

- Wu, C.-H.; Tsai, W.-C.; Tan, C.-G.; Chen, C.-N.; Li, K.-I.; Hsu, J.-L.; Lo, C.-L.; Chen, H.-H.; Su, S.-Y.; Chen, K.-T.; et al. A GPS/Galileo SoC with adaptive in-band blocker cancellation in 65 nm CMOS. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 462–464. [Google Scholar]

- Tan, C.G.; Song, F.; Choke, T.Y.; Kong, M.; Song, D.-C.; Yong, C.-H.; Shu, W.; You, Z.H.; Lin, Y.-H.; Shanaa, O. A universal GNSS (GPS/Galileo/Glonass/Beidou) SoC with a 0.25 mm2 radio in 40 nm CMOS. In Proceedings of the IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2013; pp. 334–335. [Google Scholar] [CrossRef]

- Skournetou, D.; Lohan, E.-S. Ionospheric delay corrections in multi-frequency receivers: Are three frequencies better than two? In Proceedings of the 2011 International Conference on Localization and GNSS (ICL-GNSS), Tampere, Finland, 29–30 June 2011; pp. 181–186. [Google Scholar] [CrossRef]

- Kaplan, E.D.; Hegarty, C. Understanding GPS/GNSS: Principles and Applications, 3rd ed.; Artech House: Boston, MA, USA, 2017. [Google Scholar]

- Jiang, Z.; Groves, P.D.; Ochieng, W.Y.; Feng, S.; Milner, C.D.; Mattos, P.G. Multi-Constellation GNSS Multipath Mitigation Using Consistency Checking. In Proceedings of the 24th International Technical Meeting of The Satellite Division of the Institute of Navigation (ION GNSS 2011), Portland, OR, USA, 20–23 September 2011; pp. 3889–3902. [Google Scholar]

- Detratti, M.; Lopez, E.; Perez, E.; Palacio, R.; Lobeira, M. Dual-band RF receiver chip-set for Galileo/GPS applications. In Proceedings of the IEEE/ION Position, Location and Navigation Symposium, Monterey, CA, USA, 5–8 May 2008; pp. 851–859. [Google Scholar] [CrossRef]

- Moon, Y.; Cha, S.; Kim, G.; Park, K.; Ko, S.; Park, H.; Park, J.; Lee, J. A 26mW dual-mode RF receiver for GPS/Galileo with L1/L1F and L5/E5a bands. In Proceedings of the IEEE International SoC Design Conference, Busan, Korea, 24–25 November 2008; p. I-421. [Google Scholar] [CrossRef]

- Qi, N.; Xu, Z.; Chi, B.; Xu, Z.; Yu, X.; Zhang, X.; Xu, N.; Chiang, P.; Rhee, W.; Wang, Y. A Dual-Channel Compass/GPS/GLONASS/Galileo Reconfigurable GNSS Receiver in 65 nm CMOS With On-Chip I/Q Calibration. IEEE Trans. Circuits Syst. I 2012, 59, 1720–1732. [Google Scholar] [CrossRef]

- Chen, D.; Pan, W.; Jiang, P.; Jin, J.; Mo, T.; Zhou, J. Reconfigurable Dual-Channel Multiband RF Receiver for GPS/Galileo/BD-2 Systems. IEEE Trans. Microw. Theory Tech. 2012, 60, 3491–3501. [Google Scholar] [CrossRef]

- Garzia, F.; Kohler, S.; Urquijo, S.; Neumaier, P.; Driesen, J.; Haas, S.; Leineweber, T.; Zhang, T.; Krause, S.; Henkel, F.; et al. NAPA: A fully integrated multi-constellation two-frequency single-chip GNSS receiver. In Proceedings of the 2014 IEEE/ION Position, Location and Navigation Symposium (PLANS 2014), Monterey, CA, USA, 5–8 May 2014; pp. 1075–1083. [Google Scholar] [CrossRef]

- Jo, I.; Bae, J.; Matsuoka, T.; Ebinuma, T. RF front-end architecture for a triple-band CMOS GPS receiver. Microelectron. J. 2015, 46, 27–35. [Google Scholar] [CrossRef]

- Li, S.; Li, J.; Gu, X.; Wang, H.; Li, C.; Wu, J.; Tang, M. Reconfigurable All-Band RF CMOS Transceiver for GPS/GLONASS/Galileo/Beidou With Digitally Assisted Calibration. IEEE Trans. Very Large Scale Integr. Syst. 2015, 23, 1814–1827. [Google Scholar] [CrossRef]

- NaviSoC Project. Available online: http://navisoc.com/ (accessed on 22 December 2019).

- Marcinek, K.; Pleskacz, W.A. GNSS-ISE: Instruction Set Extension for GNSS Baseband Processing. Sensors 2020, 20, 465. [Google Scholar] [CrossRef] [PubMed]

- Navipedia, European Space Agency Science GNSS Science Support Centre. Available online: https://gssc.esa.int/navipedia (accessed on 16 November 2019).

- Ji, X.; Wu, J.; Shi, L. Current reused Colpitts VCO and frequency divider for quadrature generation. In Proceedings of the International Conference on Electric Information and Control Engineering, Wuhan, China, 15–17 April 2011; pp. 256–259. [Google Scholar] [CrossRef]

| Parameter | Values | |||

|---|---|---|---|---|

| Ref [9] | Ref [19] | Ref [17] | This Work | |

| Process | 40 nm | 55 nm | 65 nm | 110 nm |

| GNSS bands (simultaneous reception) | Galileo E1, GPS L1, BeiDou B1, Glonass L1 | Galileo E1/E5ab, GPS L1/L2/L5, BeiDou B1/B2, Glonass L1/L2 | Galileo E1/E5a, GPS L1/L5, Glonass L1 | Galileo E1/E5ab, GPS L1/L1C/L5, BeiDou B1/B2, GLONASS L1/L3/L5, QZSS L1/L5, IRNSS L5 |

| IF bandwidth | 2–15 MHz | 2–20 MHz | 14/20 MHz | 2–52 MHz |

| NF | 2.1 dB | 1.92–2.5 dB | - | 2.3 dB |

| Maximum Gain | 78 dB | 116 dB | - | 131 dB |

| ADC resolution | 9 bit | 4 bit | 4 bit | I/Q 3 bit |

| ADC sampling rate | 66 MHz | - | 74 MHz | 8–64 MHz |

| Phase noise at 1 MHz | −94 dBc | −112 dBc | - | −121 dBc |

| SRAM/FLASH | -/- | - | 1 MB/- | 512 kB/768 kB |

| RF/SoC area | 0.25 mm2/6.4 mm2 | 8.4 mm2/- | 4.5 mm2/22.5 mm2 | 4.5 mm2/34 mm2 |

| RF power consumption | 16 mW | 36 mW | - | 35 mW |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Borejko, T.; Marcinek, K.; Siwiec, K.; Narczyk, P.; Borkowski, A.; Butryn, I.; Łuczyk, A.; Pietroń, D.; Plasota, M.; Reszewicz, S.; et al. NaviSoC: High-Accuracy Low-Power GNSS SoC with an Integrated Application Processor. Sensors 2020, 20, 1069. https://doi.org/10.3390/s20041069

Borejko T, Marcinek K, Siwiec K, Narczyk P, Borkowski A, Butryn I, Łuczyk A, Pietroń D, Plasota M, Reszewicz S, et al. NaviSoC: High-Accuracy Low-Power GNSS SoC with an Integrated Application Processor. Sensors. 2020; 20(4):1069. https://doi.org/10.3390/s20041069

Chicago/Turabian StyleBorejko, Tomasz, Krzysztof Marcinek, Krzysztof Siwiec, Paweł Narczyk, Adam Borkowski, Igor Butryn, Arkadiusz Łuczyk, Daniel Pietroń, Maciej Plasota, Szymon Reszewicz, and et al. 2020. "NaviSoC: High-Accuracy Low-Power GNSS SoC with an Integrated Application Processor" Sensors 20, no. 4: 1069. https://doi.org/10.3390/s20041069

APA StyleBorejko, T., Marcinek, K., Siwiec, K., Narczyk, P., Borkowski, A., Butryn, I., Łuczyk, A., Pietroń, D., Plasota, M., Reszewicz, S., Wiechowski, Ł., & Pleskacz, W. A. (2020). NaviSoC: High-Accuracy Low-Power GNSS SoC with an Integrated Application Processor. Sensors, 20(4), 1069. https://doi.org/10.3390/s20041069