3.1. Analysis of Core Technology Identification Results in the Chip Field

3.1.1. Identification of Core Technologies in Chip Design

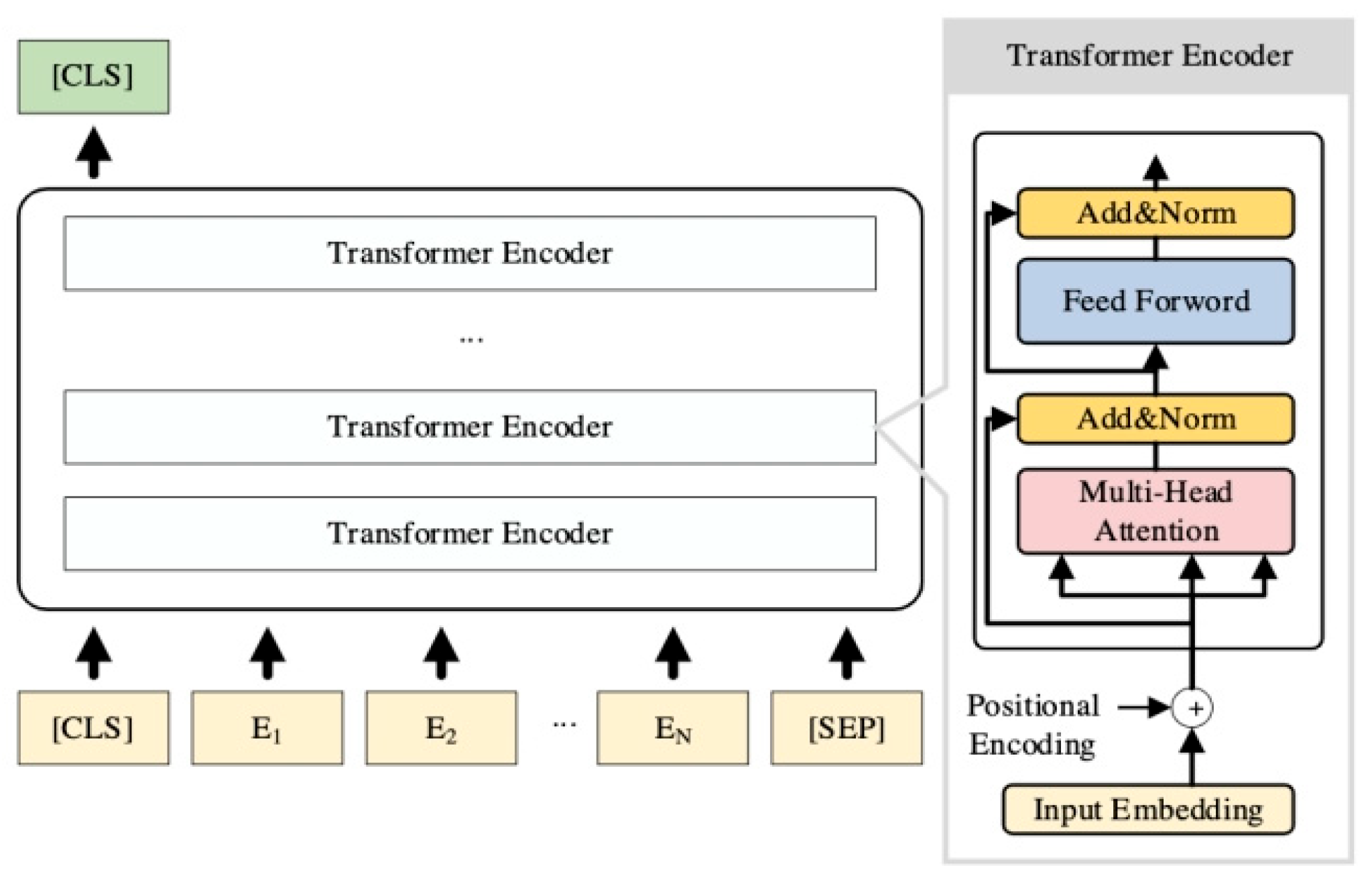

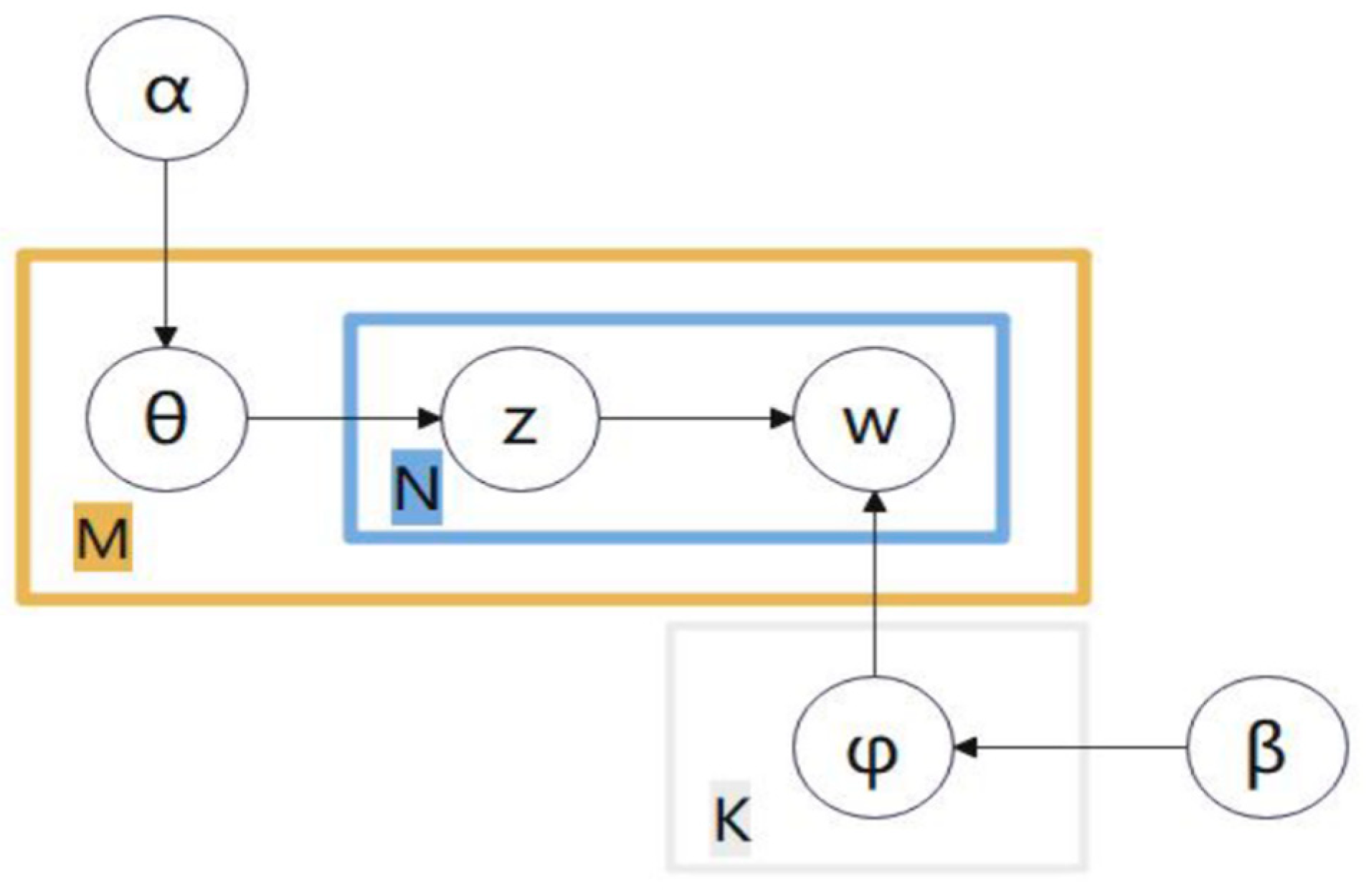

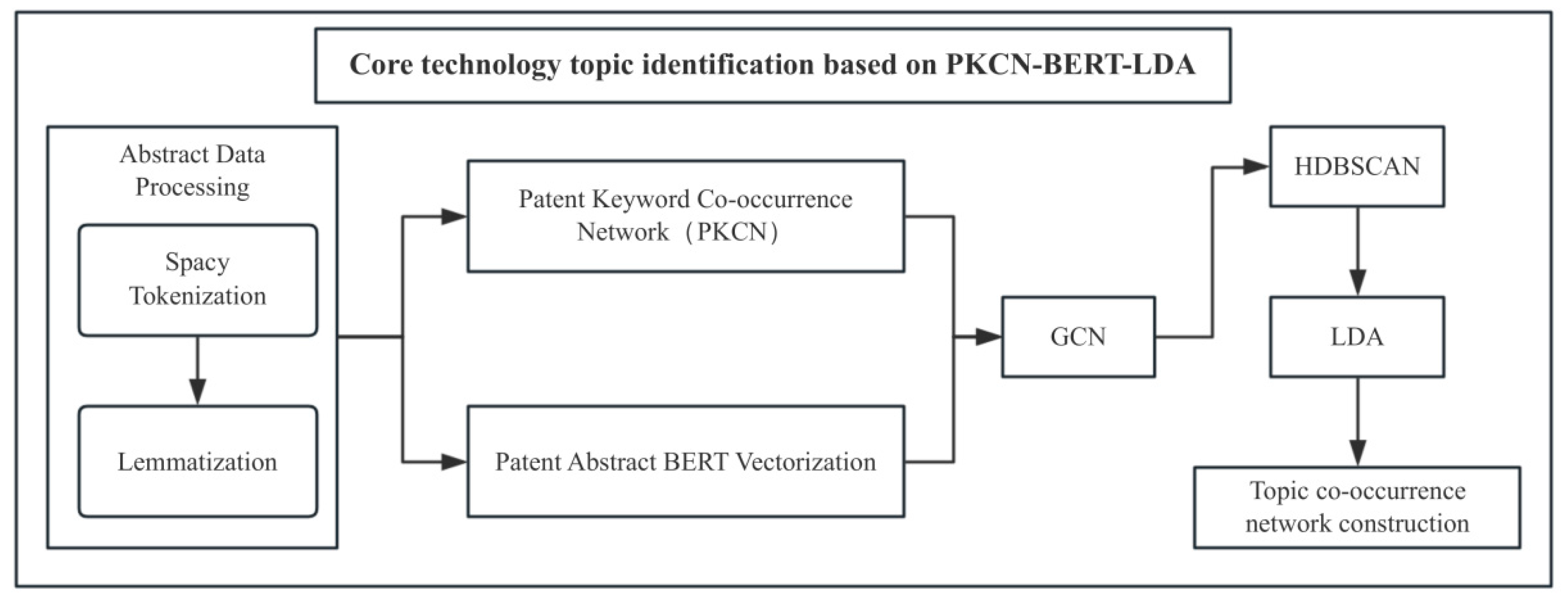

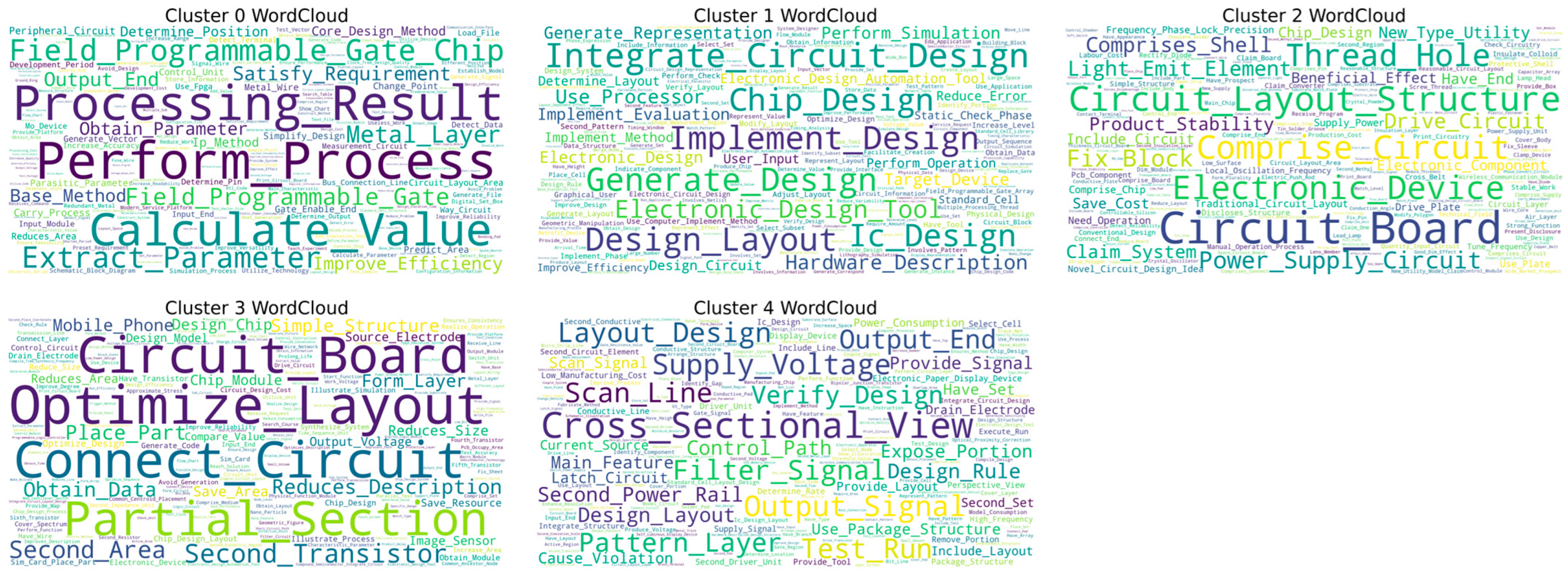

This study utilizes the HDBSCAN algorithm to cluster text data within the field of chip design, initially forming five distinct clusters (Cluster 0–4), as illustrated in

Figure 6. The word cloud visualizations show that each cluster displays a certain thematic inclination, as detailed in

Figure 7. High-frequency terms in Cluster 0, such as “Field Programmable Gate Chip” and “Optimize Design,” indicate a focus on programmable logic device design and optimization. In Cluster 1, terms like “Generate Design” suggest themes of design automation and generation. Clusters 2 and 3 prominently feature “Circuit_Layout,” accompanied by terms such as “Optimize Layout,” “Structure,” and “Power Supply Circuit,” emphasizing the physical layout of circuits and their optimization and highlighting the central importance of this theme within the dataset. Cluster 4 centers on keywords like “Circuit_Diagram” and “Semiconductor View,” focusing on the representation of circuit layers and device views.

However, a deeper analysis of the word cloud content reveals significant limitations in the current clustering results regarding the elucidation of core technical details. Firstly, the differentiation between themes is inadequate; for instance, common high-frequency terms such as “Design Rule,” “Schematic View,” and “Optimize Layout” appear redundantly across multiple clusters (e.g., Clusters 0, 2, and 3). This indicates that the algorithm may not have effectively disentangled foundational common concepts, leading to blurred boundaries between clusters and dilution of core technical features. Secondly, there is a lack of refined technical breakdowns within core themes, particularly evident in the critical area of circuit layout (Clusters 2 and 3). The word cloud only generally presents macro terms like “Circuit_Layout” and “Optimize Layout,” failing to distinguish between various types such as Analog Layout, Digital Place & Route, and RF Layout. It also lacks explicit representations of specific layout optimization techniques (e.g., timing-driven, power-driven, area optimization) or key metrics (e.g., routing congestion, signal integrity). Similarly, themes like design generation (Cluster 1) and circuit diagrams (Cluster 4) remain at a relatively general level.

Thus, while the clustering provides a preliminary outline of research hotspots, the existing results struggle to accurately map to specific, actionable core technical branches or methodological differences. To clearly define the characteristics of different technical routes and their corresponding relationships in classification, further refined analysis in conjunction with fine-grained feature engineering is essential.

Next, this study will focus on each major category from a fine-grained perspective, using LDA topic models and topic co-occurrence networks to identify the core technology topics within each major category.

Firstly, the coherence score was used to determine the number of topic divisions for each major category. The higher the coherence score, the more reasonable the topic division. The test results indicated that the number of topics in the clusters from 0 to 5 is 5, 7, 7, 7, and 6, respectively. Subsequently, the following results are obtained by analyzing the co-occurrence of topics in each major category and calculating the average degree of topic nodes, as shown in

Table 1.

Through keyword analysis of each topic, five core technological topics were identified. Given the highly specialized nature of the semiconductor field, detailed explanations of each core technology are provided to facilitate reader comprehension, as presented in

Table 2.

3.1.2. Identification of Core Technologies in Chip Manufacturing

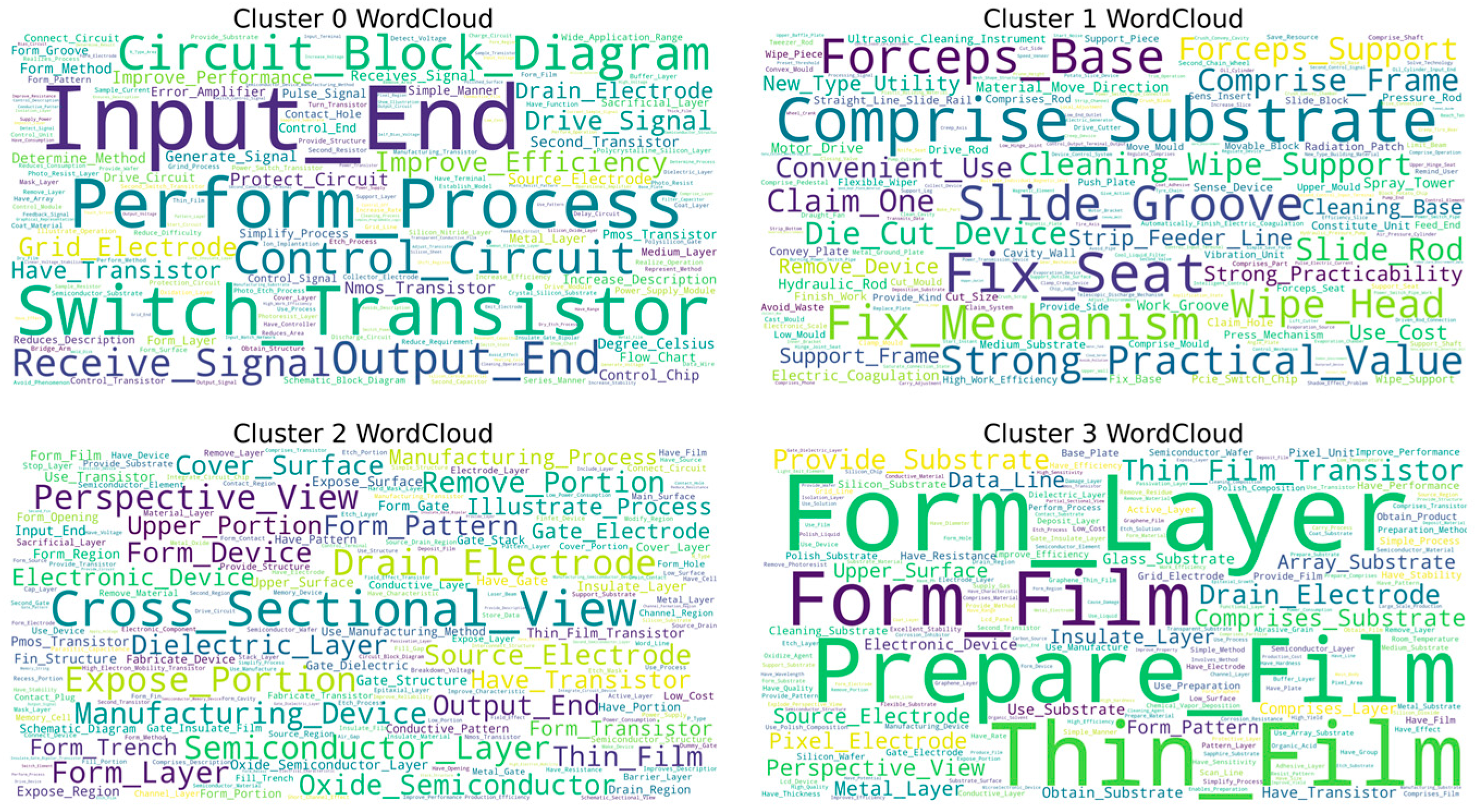

As shown in

Figure 8 and

Figure 9, the four word cloud clusters (Cluster 0–3) generated from text in the field of chip manufacturing using the HDBSCAN algorithm provide an initial insight into the differences in thematic distribution. Cluster 0 features high-frequency terms such as “Switch_Transistor,” “Circuit_Block_Diagram,” and “Protect_Circuit,” indicating a focus on transistor-level circuit design and protection mechanisms. In contrast, Cluster 1 is dominated by terms related to engineering support tools, such as “Fix_Mechanism,” “Cleaning_Wipe_Support,” and “Spray_Towel,” which significantly deviate from the core technical domain of chip manufacturing. Clusters 2 and 3 both involve view representations (“Schematic_View,” “Cross_sectional_View”) and process steps (“Form_Structure,” “Manufacturing_Method”), but they exhibit a high degree of overlap in core terms, with words like “Semiconductor_Device,” “Drain_Electrode,” and “Thin_Film” repeated across both clusters.

However, similar to the findings in the chip design sector, the current clustering results demonstrate clear deficiencies in identifying core technical features. Firstly, key technological elements are overly generalized, particularly within the core process clusters (Clusters 0, 2, and 3). For instance, high-frequency terms like “Thin_Film” and “Form_Structure” may point toward critical processes such as thin film deposition and structural formation, but they lack differentiation regarding specific technical pathways (e.g., CVD/PVD deposition methods, photolithography etching parameters) or material systems (e.g., high-k dielectrics, III-V compounds). Secondly, there is a noticeable disconnect in the core process chain; the word cloud fails to cluster significant manufacturing processes such as “Lithography,” “Etching,” and “Ion_Implantation.” Additionally, discrete device terms like “Drain_Electrode” and “Insulate_Line” appear in isolation, preventing the formation of a coherent sequence of process flows.

In summary, while the current classification exhibits surface-level thematic dispersion, it is constrained by a lack of technical granularity and missing interprocess connections, resulting in an inability to accurately map the core stages in chip manufacturing that have clear technological barriers. Therefore, it is essential to repeat the aforementioned steps to conduct a more detailed analysis.

Firstly, it is necessary to determine the number of LDA topics in each technology cluster. Based on the corresponding topic coherence scores, the number of topics is determined to be 17, 10, 16, and 12, respectively.

Subsequently, a document topic co-occurrence analysis was conducted on the topics of each technology cluster. In the analysis of technology cluster 0 and technology cluster 1, regardless of adjusting the threshold of document topic probability, the average value of all topic degrees within these two clusters remains consistent. Based on the number of patents in these two technology clusters, it could be inferred that this phenomenon is mainly due to the relatively insufficient number of patents: technology cluster 0 contains 893 patents, while technology cluster 1 only has 233 patents.

In view of this, the authors of this study believe that the topics within these two clusters are equally important, and there may be interrelationships between the topics within the same technology cluster. Therefore, it is reasonable to directly consider technology clusters 0 and 1 as two core technology topics. The analysis of technology clusters 2 and 3 is consistent with the previous method. The results are shown in

Table 3.

Through LDA keyword analysis of each topic, four core technological topics were identified, as shown in

Table 4.

3.1.3. Identification of Core Technologies for Chip Packaging and Testing

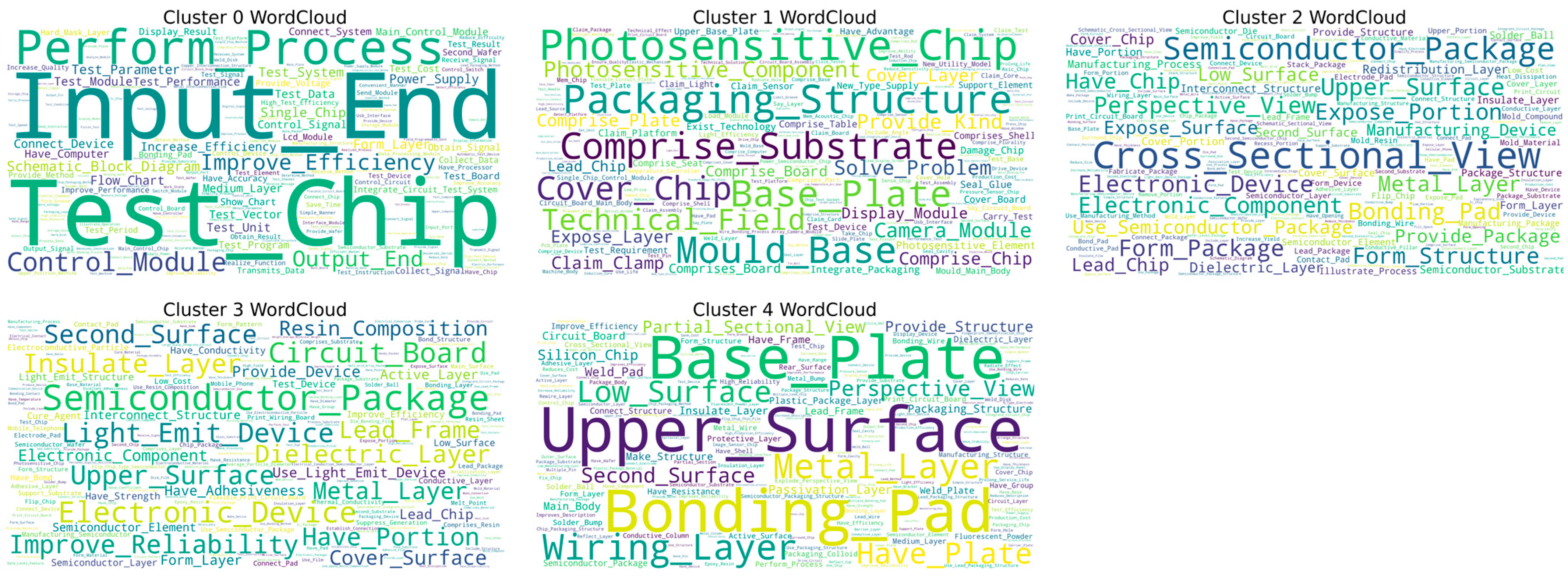

As shown in

Figure 10, the HDBSCAN algorithm has classified chip packaging and testing patent data into five clusters (Cluster 0–4). As shown in

Figure 11, the word cloud visualizations indicate an initial differentiation of themes: Cluster 0 features high-frequency terms, such as “Test_Chip,” “Control_Module,” and “Test_Parameter,” which point towards testing systems and process control. Cluster 1 centers on key terms like “Comprise_Substrate” and “Photosensitive_Chip,” linking substrate materials to optoelectronic device packaging. Cluster 2 prominently includes terms like “Perspective_View,” “Cross_Sectional_View,” and “Semiconductor_Package,” highlighting the visual representation of packaging structures. Cluster 3 focuses on terms such as “Insulate_Layers,” “Light_Emit_Device,” and “Dielectric_Layer,” which relate to the integration of insulating materials and light-emitting devices. Finally, Cluster 4 revolves around terms like “Base_Plate,” “Wiring_Layer,” and “Bonding_Pad,” emphasizing substrate design and interconnect wiring.

Nevertheless, the current classification exhibits certain shortcomings in representing the core technologies of packaging and testing. Firstly, key technological elements are obscured by surface-level terminology. For instance, terms like “Test_Chip” and “Improve_Efficiency” in Cluster 0 only reflect the objectives of testing without revealing specific testing techniques (such as CP testing, FT testing, or 3D stacking tests) or critical metrics (like yield, throughput, and fault coverage rates). Secondly, there is a disconnect between materials and processes. Although “Photosensitive_Chip” in Cluster 1 and “Resin_Composition” in Cluster 3 mention materials, they do not relate to specific processes (such as molding, underfilling, or laser debonding) and fail to distinguish between material types (such as epoxy resin, silicone, or liquid encapsulant). Thirdly, there is a homogenization of core packaging technologies, with terms like “Semiconductor_Package” and “Upper_Surface” appearing repeatedly across Clusters 2, 3, and 4 without highlighting differences in advanced packaging techniques (such as Fan-Out, SiP, or RDL routing in Chiplet integration, TSV vias, and micro-bump technology). Additionally, terms like “Wiring_Layer” and “Bonding_Pad” in Cluster 4 exist in isolation without clear correlations to specific interconnection technologies (such as wire bonding, flip-chip bonding, or hybrid bonding).

In conclusion, while the current clustering provides a framework for application scenarios, it relies overly on generalized engineering vocabulary, leading to a dilution of features related to high-density packaging processes, material systems, and reliability design.

Firstly, the number of LDA topics was determined for each technology cluster based on coherence scores. The corresponding LDA topics for each technology cluster are 8, 10, 6, 13, and 8, respectively.

Subsequently, co-occurrence analysis was conducted on the topics of each technology cluster, and it was found that the average degree of each topic was consistent when analyzing technology cluster 1. Therefore, technology cluster 1 was considered a core topic. In addition, when analyzing technology cluster 2, it was found that the average degree values of Topic 3 and Topic 6 were the same. Subsequently, through in-depth mining of these two topic keywords, it is believed that there is a certain correlation between the Topic 3 and Topic 6 keywords. Therefore, these two topics were merged. The results are shown in

Table 5.

Finally, five core technology topics in the field of chip packaging and testing could be obtained by summarizing and analyzing the LDA keywords for each topic, as specifically shown in

Table 6.

3.1.4. Identification Result Verification

To evaluate the core technology identification performance of the PKCN-BERT-LDA model, this study follows the methodology of Ruan et al. [

36] and selects the experimental results of BERT, Word2Vec, and LDA as a control group for comparative analysis. The parameters used in the processes of data dimensionality reduction and text clustering are consistent with those applied in the experiments of the proposed fusion model.

This paper utilizes topic coherence metrics to assess the quality of topics generated by different algorithms. Topic coherence is measured by evaluating the semantic similarity of high-frequency terms within each topic, providing a score that reflects meaningful connections within the topics; higher scores indicate better model performance. Specifically, this study employs two metrics: U_mass (where negative values closer to 0 are preferred) and C_V (ranging from 0 to 1, with values closer to 1 being better) to calculate topic coherence. Through experimental comparisons, the topic coherence of the four methods—PKCN-BERT-LDA, BERT, Word2Vec, and LDA—was calculated. The detailed results are presented in

Table 7.

As shown in

Table 7, in the identification of core technology themes in the field of chip technology, the PKCN-BERT-LDA model achieved the highest U_mass and C_V values in the areas of chip design, manufacturing, and packaging & testing, indicating that the proposed method exhibits the best topic coherence. A comparative analysis of the experimental data reveals that the PKCN-BERT-LDA model yields topic coherence values (C_V) greater than 0.5 in all three areas of core technology identification, demonstrating that the identified feature words within the same topic exhibit better coherence and effectively enhance the interpretability of the identification results. Furthermore, the LDA model shows the lowest topic coherence, which highlights the diversity of technical terminology in patent literature. This diversity introduces instability when identifying patent technology topics based on lexical co-occurrence relationships. The comparative results indicate that the clustering performance of core technology identification based on the PKCN-BERT-LDA model is indeed the best.

3.2. Analysis of the Evolution Results of Core Technologies in the Chip Field

In the following section, this paper will construct patent citation networks to analyze the technological evolution of the identified 14 core technologies. Before doing so, it is deemed necessary to explain how technology evolves through the patent citation network.

The patent citation network is constructed based on the formal citation relationships among patent documents, reflecting the cumulative and evolutionary characteristics of technological knowledge. According to the theory of knowledge spillover, patent citation relationships are not merely a legal requirement; they also reflect the pathways of technological knowledge transfer among inventors. In the patent citation network, each patent node carries specific technological information, while directed edges indicate the flow of technological knowledge from the cited patent to the citing patent, forming a mechanism of “knowledge source → knowledge recipient.” Technological evolution within the patent citation network follows a path dependence principle, meaning the emergence of new technologies relies on existing technological foundations. When Patent A cites Patent B, it signifies that the invention of Patent A is inspired by or built upon the technological foundation of Patent B. This citation relationship constitutes the micro-mechanism of technological evolution. Technological knowledge is transmitted across time via citation chains, forming technological trajectories. Moreover, when multiple patents cite the same foundational patent, technical branches arise, propelling the technology in different directions. Additionally, the information flow within the patent citation network exhibits notable sequential and cumulative characteristics. The sequential aspect is evidenced by the requirement that the application date of the citing patent must be later than that of the cited patent, ensuring the logical order of technological evolution. The cumulative aspect manifests in the tendency for subsequent patents to cite multiple prior patents, facilitating the integration and synthesis of technological knowledge. Key nodes in the network often exhibit high citation frequencies, becoming crucial cornerstones of technological development, while the main paths reveal the core evolutionary trajectories within the technological field.

Taking semiconductor lithography technology as an example, early contact lithography patents (such as foundational lithographic process patents from the 1960s) established the basic principles of pattern transfer. Subsequent projection lithography patents, by citing these foundational patents, developed non-contact precision processing methods based on their technological foundations. As we entered the nanotechnology era, extreme ultraviolet lithography (EUV) patents not only referenced traditional lithography patents but also cited patents from related fields, such as laser technology and precision optical systems, reflecting the characteristic of integrative technological evolution. This citation pattern has formed an evolutionary path in the network that transitions from a single technological foundation to multi-technology integration, illustrating the trajectory of lithography technology’s development from simplicity to complexity and from singularity to comprehensiveness. By tracing these citation relationships, we can clearly identify the core evolutionary context and key technological nodes in lithography technology.

3.2.1. Evolution of Core Technologies in Chip Design

- (1)

Analysis of the Technological Evolution of “Circuit Layout and Simulation Flowchart”

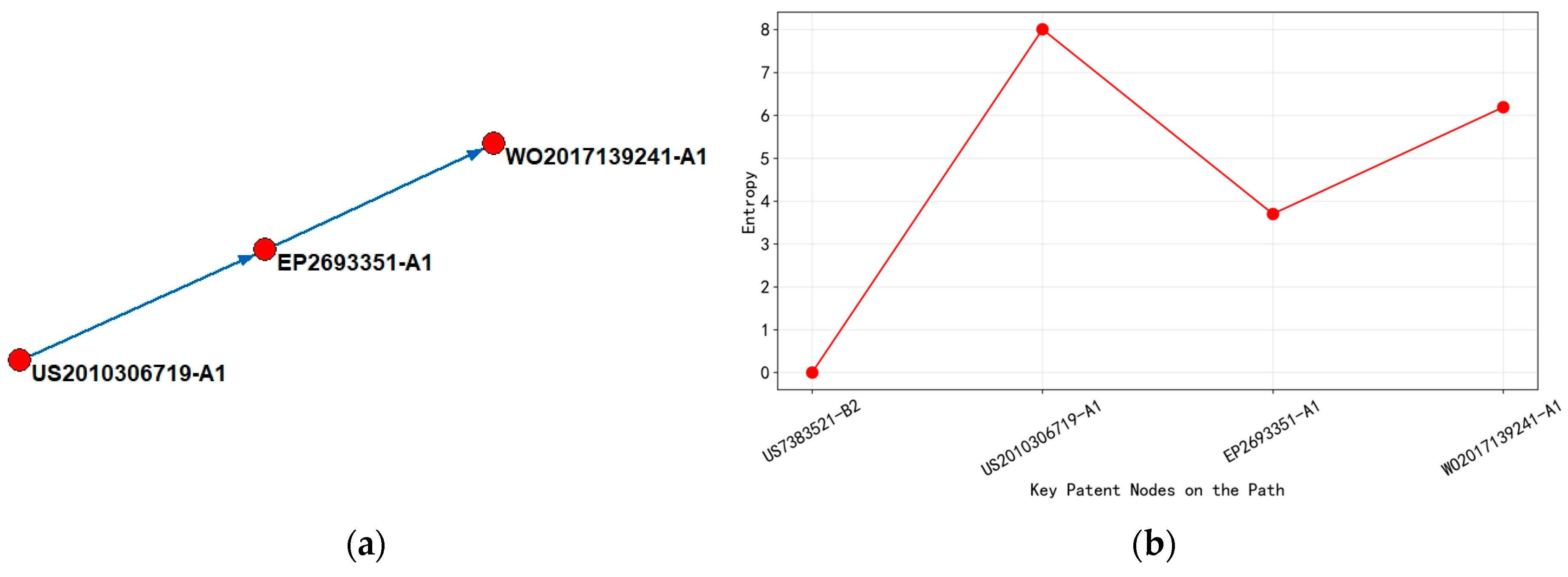

Based on the analysis of

Figure 12, it could be concluded that, from 2010 to 2014, the core of the technological evolution path focused on the field of integrated circuit physical design automation (computer-aided design processes that convert circuit descriptions into manufacturable layouts), with patent technology classification mainly concentrated in G06F-017/50 (computer-aided design technology). Starting from US2010306719-A1 (2010), this stage achieved circuit parameter optimization before layout through “unit level process compensation technology (methodology to adjust design parameters to compensate for manufacturing variations at the individual circuit element level) ”, with an entropy value of 8.0056, reflecting the high uncertainty of the technology exploration stage. The patent layout is centered around the United States, demonstrating the knowledge concentration characteristics of the technology’s origin.

During 2012–2016, it belonged to the stage of technological iteration, and the technology classification was expanded to seven categories, including H01L-021/00 (semiconductor device manufacturing process). The entropy value of EP2693351-A1 (2014) decreased to 3.7004, indicating that the technology has entered a convergence optimization period. This node innovatively introduced a “deterministic boundary interconnect feature generator (tool for creating precise interconnection patterns in dual patterning lithography) ” to solve the physical boundary alignment problem of dual patterning technology (a challenge in aligning multiple lithographic patterns with nanometer-level precision to create single features) through a system-level collaboration mechanism. The scope of patent layout has expanded to semiconductor industry clusters, such as Europe, Japan, and South Korea, where the repeated layout of KR and JP reveals the key position of East Asia in the landing of advanced process technologies. At this stage, the flow of technological knowledge presented a one-way diffusion trend from the United States to the manufacturing hub in East Asia.

From 2015 to 2019, we entered the stage of technological transition, and the main path patent classification was further expanded to 13 cross-disciplinary fields such as G05F-001/59 (circuit power control) and G06F-021/00 (data security technology). The entropy value of WO2017139241-A1 (2017) rebounded to 6.1898, indicating that the technology has entered an innovation cycle of multidimensional integration. Using “secure optimization layout and routing strategy” and “power signature analysis technology”, this node has achieved collaborative optimization of circuit design security and energy efficiency indicators. The patent layout covers major economies, such as WO, CN, EP, and US, among which the repeated appearance of CN marks China’s deep involvement in the field of integrated circuit design toolchain. At this stage, technology diffusion presented a multi-center network characteristic, and the knowledge flow path includes both the continuous output of traditional technology powers in Europe and America, as well as the active absorption of technological improvements by emerging markets.

There are two important points to note: First, the entropy value of the patent US7383521-B2 in

Figure 12b is zero because the patent search period defined in this study is limited to the years 2010–2024. Therefore, patents filed before 2010 will have an entropy value of zero, and this applies to all subsequent figures as well. Second, the patents indicated by the blue arrows on the left main path diagram are connected in the order of the x-axis of the entropy line graph on the right. Furthermore, the patents along the main path only showcase patents from the period 2010–2024.

- (2)

Analysis of the Technological Evolution of “Optical Proximity Correction Technology”

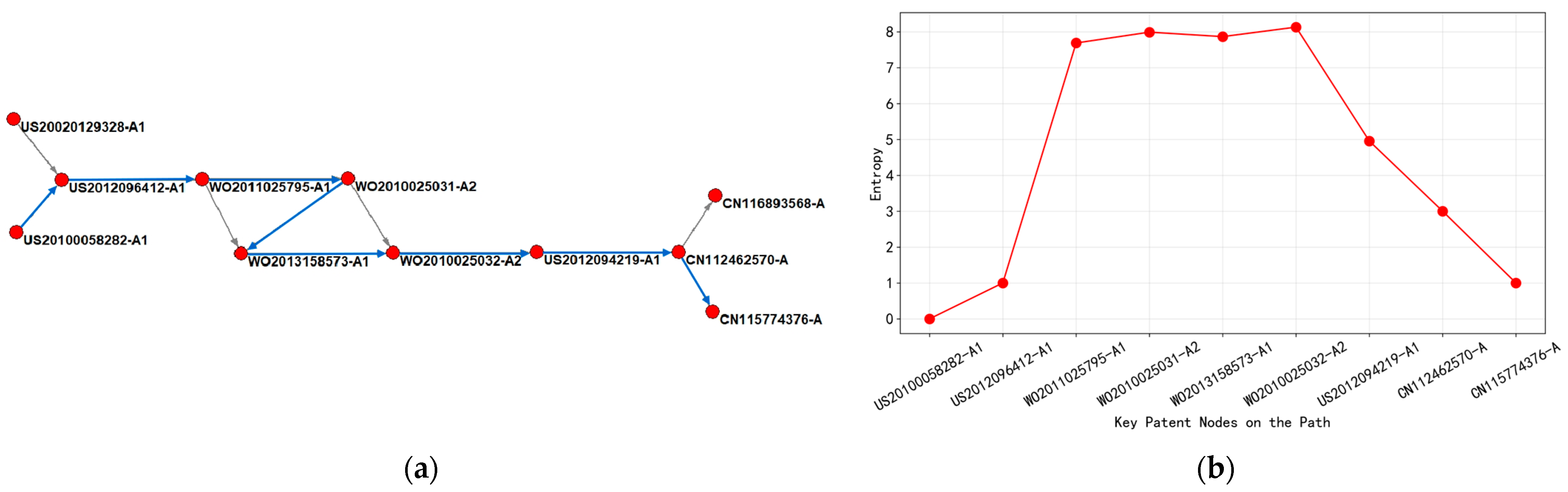

As shown in

Figure 13, early patents focused on the fundamental algorithm of Optical Proximity Correction (OPC-a photolithography enhancement technique that pre-distorts mask patterns to compensate for diffraction and process effects during semiconductor manufacturing, crucial for sub-wavelength lithography) and the collaborative optimization of computer-aided design (G06F-017/50) and optical lithography process (G03F-007/20). For example, US2012096412-A1 (2012) proposed the “OPC Simplification Method in Optical Lithography Process”, which has a low entropy value indicating a relatively single technological path and a concentrated layout in the United States. Subsequently, WO2011025795-A1 (2011) introduced a charged particle beam lithography device (advanced patterning technology using electron or ion beams instead of photons for higher resolution patterning), expanding the technology classification to semiconductor manufacturing (H01L-021/027) and photolithography mask design (G03F-001/14), with entropy values jumping to 7.6865, reflecting the intersection of knowledge from multiple fields. At this stage, the patent layout has covered 11 regions, including WO, JP, US, KR, etc., and the technology diffusion presented a cross-border flow characteristic of “US led and East Asian coordinated”.

During the period from 2013 to 2021, the technological path shifted towards mask data preparation (MDP, the process of converting design data into formats suitable for mask manufacturing) and exposure efficiency optimization. WO2013158573-A1 (2013) achieved automated processing of mask data through a charged particle beam, with the addition of mask defect correction (G03F-001/78) and a high-entropy value (7.8642), indicating the continuous accumulation of technical complexity. During the same period, CN112462570-A (2021) proposed the “angle filtering rotary OPC method”, focusing on controlling lithography process parameters (G03F-001/36). The entropy value dropped to 3, indicating that China has achieved a professional breakthrough in specific technology nodes (such as mask geometry correction (techniques to adjust mask patterns to compensate for manufacturing distortions)), and the layout is still mainly local, narrowing the scope of technology diffusion.

After 2022, the latest patent CN115774376-A (2023) integrates model-driven correction technology, continuing the G03F core code but reducing the entropy value to 1, reflecting the convergence of the technology to the refinement stage of mask manufacturing process optimization. Although China’s patent layout is still dominated by CN, KR, and US, high-entropy patents (such as WO2010025032-A2, entropy 8.1293) continue to spread through multilateral systems, such as WO and EP, reflecting the formation of the “US East Asia Europe” triangular technology flow network. At this stage, technological evolution presented a bidirectional feature: on the one hand, basic algorithms were widely disseminated through the international patent system (WO); on the other hand, regional patents such as CN and TW strengthened local technological barriers in terms of process details.

From

Figure 13b, entropy fluctuations revealed a pattern of “exploration expansion convergence” in optical proximity correction technology from 2010 to 2024. The high-entropy stage (7.6865–8.1293) corresponded to a period of intensive multi-technology fusion and international cooperation, such as the cross-domain combination of charged particle beams and OPC; the low-entropy stage (1–4.9542) marked the maturity of technology and regional specialization, such as China’s targeted innovation in model driven calibration. In terms of regional layout, the United States has always been the core technology export hub, with significantly higher bidirectional citation density with Japan and South Korea than other regions, while China has gradually integrated into the global technology chain through localization improvement, forming a progressive path of “basic technology input application innovation output”.

- (3)

Analysis of the Technological Evolution of “Silicon Via Interconnection Technology for 3D Chip Stacking”

Time can be divided into two stages by analyzing

Figure 14 and combining it with the detailed information of patents on the main path.

The period from 2010 to 2020 is the early stage (such as WO2010022163-A1, entropy value 5.129), and the technical focus is on the basic optimization of TSV (Through Silicon Via—vertical electrical connections that pass completely through a silicon wafer, enabling 3D chip integration by stacking multiple layers of active circuits) manufacturing process, including interface material selection (interface material selection—choosing appropriate barrier and adhesion layers) and low-cost copper hole filling technology (metallization process to create electrical connections in vias using electroplating or chemical vapor deposition). At this stage, the patent layout covers 11 countries and regions, and the globalization strategy aims to seize emerging markets. However, the technology classification is relatively concentrated (such as wafer thinning (process of reducing wafer thickness to enable 3D stacking, typically from 725 μm to less than 50 μm) and metallization (process of forming metal interconnections)), and the low-entropy value reflects that the technology path has not yet differentiated. By 2020 (US2020365583-A1, entropy 9.920), the complexity of technology had increased sharply, with copper bonding and ultra-thin wafer stacking (<5 μm) becoming the core, involving multi-physics field coupling (thermal stress, electrical performance) and cross-disciplinary technology integration (materials science, precision machining). The high-entropy value confirmed the diversity of its technical classification number (over 20 categories) and process complexity. At this stage, the patent layout shrank to the United States, indicating that, after the technology matures, companies turned to core market protection and consolidated technological barriers through focused strategies.

Until after 2020, patent US2023048534-A1 (entropy value 4.585) showed that the technology path extended towards high-power scenarios, optimizing heat dissipation performance through thermal interface layer design. The decrease in entropy value indicated that the focus of technology has shifted from multidimensional innovation to specific performance improvements (such as thermal management efficiency). The patent layout maintained a focus on the domestic market in the United States, reflecting the precise targeting of target markets (such as AI chips and high-performance computing) by enterprises during technology commercialization. The decrease in entropy value and the centralization of classification numbers (such as G06F30/39 involving chip thermal simulation) further revealed the shift of technical knowledge from extensive exploration to vertical application, marking the stabilization of mainstream technological paradigms.

The peak entropy value (2020) corresponded to the critical point of technological complexity, where multiple technology nodes frequently cross-reference and knowledge diffusion exhibited a “center radiation” pattern. Core patents (such as US2020365583-A1) became the hub for subsequent innovation. As entropy decreases, the technology citation network shifted from cross-border and multi-directional flow (such as the global layout in 2010) to regional closed loop (such as focusing on the United States in 2023), implying a concentration of technological dominance towards top enterprises.

This evolutionary path revealed that technological breakthroughs in the high-entropy stage rely on cross-domain knowledge integration, while technological optimization in the low-entropy stage relies on deep vertical domain iteration. The two alternately drive the evolution of the industry from laboratory innovation to large-scale applications.

- (4)

Analysis of the Technological Evolution of “Timing Manufacturability Collaborative Routing Optimization Technology”

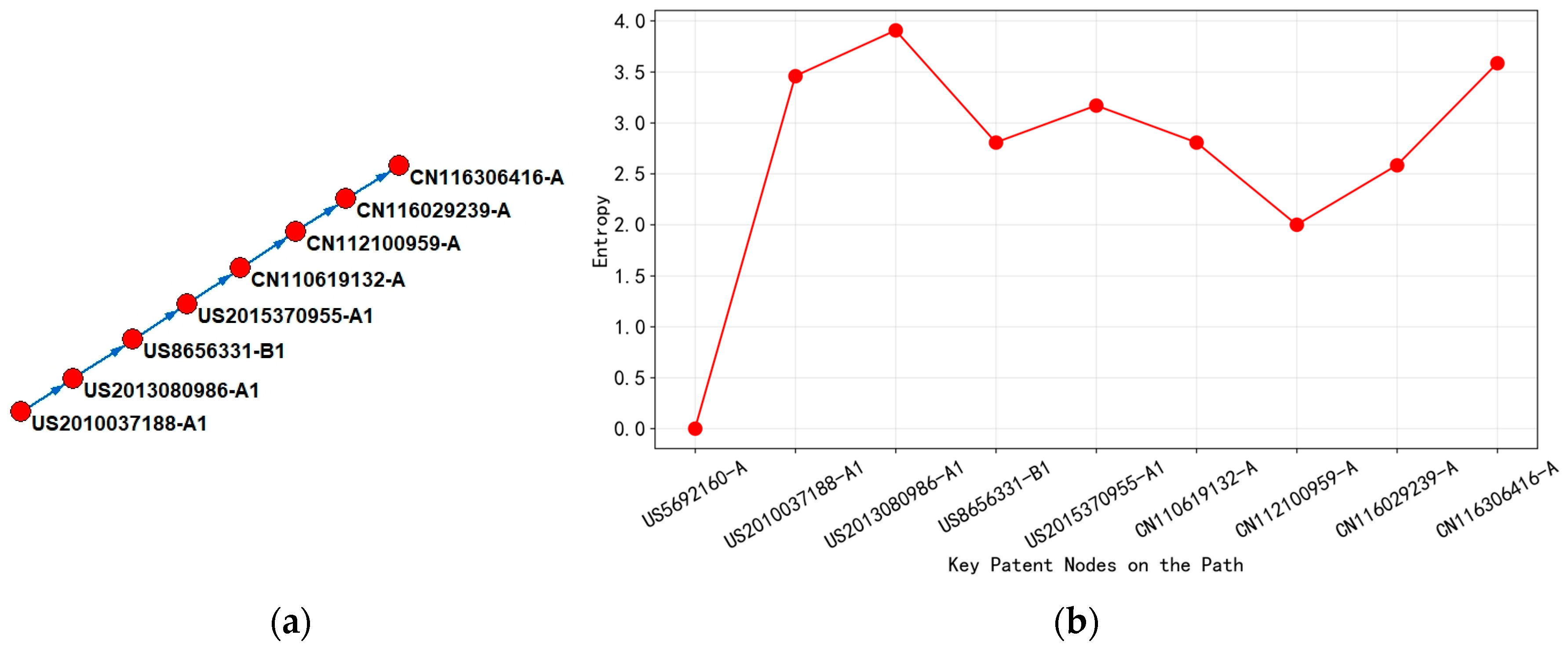

Based on the analysis of

Figure 15, it can be concluded that, from 2010 to 2013, technological evolution focused on the G06F-017/50 (integrated circuit design method) field, with core patents represented by “Voltage Scaling Optimization Performance/Power Consumption Index” (US2010037188-A1, entropy 3.46) and “Unit Level Voltage Supply Derating Technology” (US2013080986-A1, entropy 3.91). At this stage, US patents dominated, and the complexity of technology showed an upward trend. The peak entropy value (3.91) corresponded to the breakthrough of dynamic voltage dynamic voltage derating technology (adaptive voltage adjustment techniques that respond to real-time operating conditions) in static timing analysis (design verification method that checks if signals meet timing requirements without simulation), marking the initial synergy between timing optimization and power consumption control. The patent citation relationship indicated that downstream patents transform upstream voltage scaling theory into quantifiable design rules by introducing unit-level voltage supply (CVS) tools (software tools for managing voltage distribution at individual circuit components), promoting the diffusion of knowledge from abstract methods to tool chain implementation.

In 2014–2015, the technological path extended towards the intersection of G06F-017/50 and G06F-030/00 (electronic design automation), and patents such as “Time Margin Generation Method” (US8656331-B1, entropy 2.81) and “Dynamic Correction Derating Factor” (US2015370955-A1, entropy 3.17) began to focus on process variation compensation. The regional layout had been extended to South Korea, Taiwan, and China, indicating that the technology application scenario had penetrated the OEM and manufacturing end. In the main path, the downstream patent (US2015370955-A1) introduced the target unit design conditions as dynamic correction variables by referencing the upstream unit level derating framework, achieving preliminary coupling between the temporal model and manufacturing parameters.

From 2019 to 2023, the technological focus shifted to G06F-030/3315 (Electronic Design Automation Verification), with Chinese patents leading the technological iteration. Representative patents included “Voltage Drop Timing Repair” (CN112100959-A, entropy value 2.00) and “Static Timing Library Second Sequence Arc Optimization” (CN116306416-A, entropy value 3.58). Entropy values showed polarization: low-entropy patents (2.00) focus on regularized repair processes, reflecting technological modularity and tool integration; the high-entropy patent (3.58) redefined the timing manufacturing collaborative model through minimum end-to-end delay optimization, reflecting a new round of complexity leap. At this stage, the main path presented the characteristics of technology reflux. Chinese patents (such as CN116306416-A) upgraded the unit-level derating theory to a global optimization based on multi-physics field coupling by referencing early US patents (such as US2013080986-A1), while accelerating technology diffusion through localized layout.

By analyzing the dynamic changes in entropy values, it could be concluded that the fluctuations in entropy values in the main path are highly correlated with the technical lifecycle—the initial high entropy (3.91) corresponds to theoretical breakthroughs, the mid-term decrease in entropy values reflected engineering convergence, and the later rebound in entropy values (3.58) marked the reconstruction of a new paradigm. The evolution of national layout further revealed the bidirectional nature of knowledge flow: early technologies in the United States spread to Asia through patent citations, while China achieved reverse knowledge appreciation through high-entropy patents (such as CN116306416-A), forming a closed-loop path of “basic theory tool optimization manufacturing collaboration”.

- (5)

Analysis of the Technological Evolution of “Intelligent Power Optimization Technology”

Based on the analysis of

Figure 16, it could be concluded that the main path can be divided into four time periods according to the change in entropy value.

Firstly, from 2012 to 2016, patents during this period focused on the G06F-001/32 (dynamic power management method) classification, with representative patents achieving circuit board-level power control through voltage regulation modules and sensor networks. Early patents with entropy values below 10 (such as US2012054397-A1) were taken as an example; their technical solutions focus on single-parameter feedback regulation, with a clear commercialization path but limited innovation complexity. The entropy characteristics reflected that the technology was in the mature stage of application.

From 2016 to 2018, core technologies migrated towards the intersection of H04B-003/56 (power line carrier communication) and H01L-025/00 (integrated circuit packaging thermal management). The key node patent (such as US2016112263-A1) introduced a multi-mode communication switching algorithm for the first time, optimizing power consumption through dynamic spectrum allocation and thermal noise suppression, and the entropy value jumped to 11.62. The high-entropy value revealed a significant increase in technical complexity, involving multi physics field coupling modeling and real-time feedback mechanisms, becoming the underlying knowledge hub for subsequent patents. At this stage, the patent layout covered 11 markets, including North America and East Asia, and the technology diffusion showed a trend of global penetration.

From 2018 to 2020, the evolution path extended to G05F-001/66 (adaptive voltage regulator circuit) and G06F-001/28 (chip-level power gate control) classification. The cited patent (such as US2017019150-A1) inherited the multimodal framework and used deep learning to predict load fluctuations and dynamically adjust gating strategies, with entropy values maintained in the range of 11.3–11.5. The stable entropy value indicated that the technology had entered a local optimization stage, and the focus of innovation has shifted towards improving algorithm efficiency. The patent layout has shrunk to five high-value markets (such as the United States and Germany), reflecting the entry of technology commercialization into a stage of strengthened barriers.

After 2020, the latest patent (such as US2018323826-A1) integrated H03K-019/00 (low-power logic circuit design) and G06F-030/30 (physical design automation) across layers, reducing leakage current through electromagnetic interference shielding structure and process parameter optimization. The entropy value differentiation was significant (9.8–12.1), with high-entropy patents focusing on electromagnetic thermal co-simulation of 3D stacked chips, while low-entropy patents focus on standardized interface protocols, revealing a dual track evolution of the technical route towards “standardization of basic protocols + high entropy of core modules”.

3.2.2. Evolution of Core Technologies in Chip Manufacturing

- (1)

Analysis of the Technological Evolution of “Thin Film Microstructure Etching” Technology

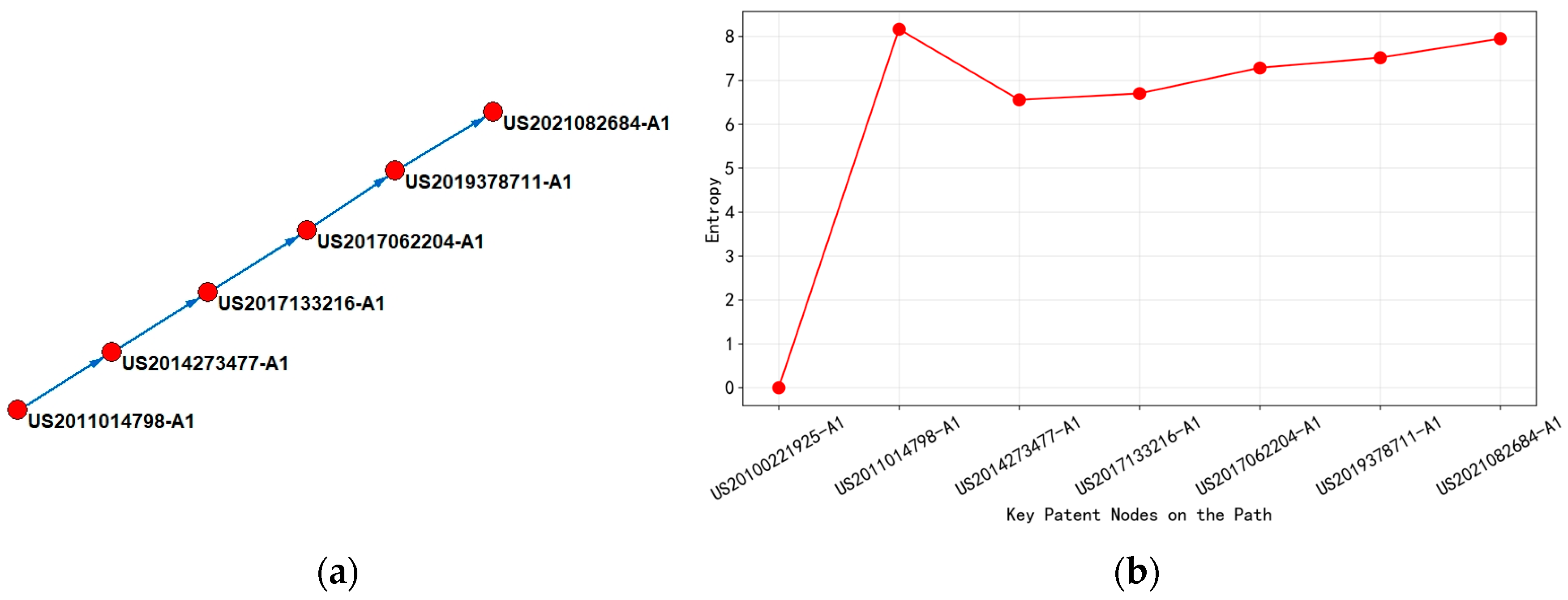

This main path is divided into three time periods based on the trend of entropy changes by analyzing

Figure 17.

During the period from 2011 to 2014, with US2011014798-A1 (2011) as the core starting point, low leakage deposition (deposition process that minimizes unwanted current paths) (entropy 8.16) of high aspect ratio silicon oxide structures (tall, narrow oxide structures with height-to-width ratios typically > 10:1) was achieved for the first time through high-temperature curing (600 °C) and dual silicon precursor design (using two different silicon-containing chemical precursors). The high-entropy value of this patent reflected the complexity of multi parameter cross regulation (temperature, precursor, free radical reaction) in the process, and the direct citation of subsequent patent US2014273477-A1 (2014) (entropy value reduced to 6.55) indicated that the technology has shifted from test exploration to standardized processes: simplifying reaction steps and improving the quality of silicon nitride films (insulating layers with high mechanical strength and chemical resistance) through low-temperature PEALD process (Plasma Enhanced Atomic Layer Deposition at reduced temperatures) and organic ligand silicon precursor (silicon-containing molecules with organic functional groups). The citation network in this stage presented a one-way flow, and the patent layout was concentrated in the United States, confirming the convergence of basic technology from complex prototypes to mass-produced processes.

Subsequently, in the three-year period from 2014 to 2017, the citing patents of US2014273477-A1 (2014), namely, US2017062204-A1 (2017) and US2017133216-A1 (2017), further promoted the technological differentiation. The former introduces high-pressure plasma (>20 Torr) and iodinated silane precursor (entropy value rises to 7.28), optimizing the etching uniformity of the 3D structure through a high-pressure environment; the latter improves the step coverage by stepwise adsorption and nitrogen plasma activation (entropy 6.70). The fluctuation of entropy value (6.55 → 7.28) reveals the further increase in process complexity under the demand of 3D devices, and the reference chain (2014 → 2017) showed the diffusion of technical knowledge towards multi-objective parameters (pressure, ligand, adsorption time). At this stage, the patent layout had been extended to South Korea, Japan, Taiwan, and China (such as US2017062204-A1 multi-country application), and the citation network had shifted from a single U.S. center to cross-regional collaboration, reflecting the penetration of technology into global manufacturing hubs.

From 2017 to 2021, US2019378711-A1 (2019) proposed the “super cycle” process (conventional deposition + high-pressure treatment sub cycle, entropy value 7.51), which balanced the growth rate and density of thin films through periodic pressure switching; US2021082684-A1 (2021) used bromine/iodosilane precursor as the core, strictly controlling the etching rate ratio (sidewall/top) to <2 (entropy 7.95), solving the anisotropy problem of non-planar structures such as FinFET. The continuous increase in entropy value (7.28 → 7.95) indicated that the complexity of technology under multiple constraints (uniformity, rate ratio, structural compatibility) is approaching the early prototype stage. The citation chain (2017 → 2021) and patent layout further revealed the directional flow of technology from process innovation to terminal applications.

- (2)

Analysis of the Technological Evolution of “High Dielectric Constant Metal Gate Integration Technology”

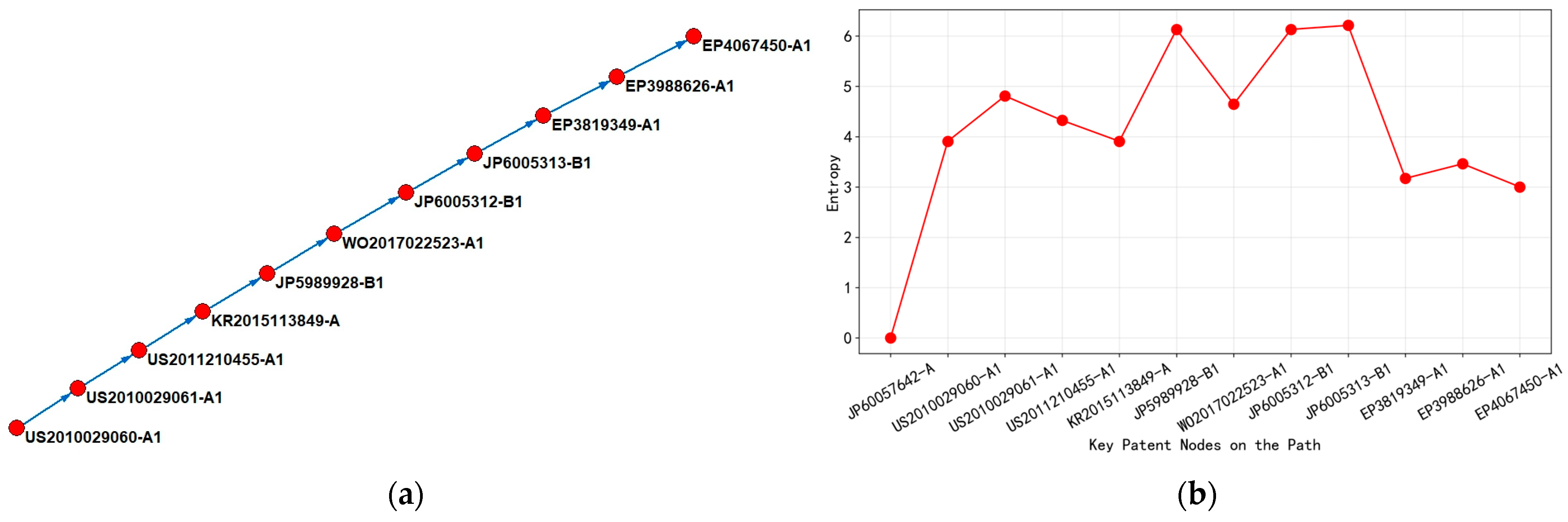

Observing

Figure 18, it is found that the main path of high dielectric constant metal gate integration technology is mostly related to ALD atomic deposition technology patents. This is because ALD is an irreplaceable enabling technology for HKMG, and its atomic-level control and 3D adaptability solve the core pain points of HKMG. Therefore, the main path of patents must be based on ALD. Below is an analysis of these two images. The patents from 2011 to 2014 mainly focused on the process basis of atomic layer deposition (ALD) and interface passivation technology, with representative patents including US2014106574-A1 and US2014027884-A1. From the perspective of entropy changes, the 2011 core patent WO2011019950-A1 (entropy 12.02) significantly improved the uniformity of metal oxide films through the ALD cycle technology of ozone and excited nitrogen oxides, becoming an important reference point for subsequent high-entropy patents (such as US2018033606-A1, entropy 11.90). It was found that the US domestic patents dominated the technology diffusion by observing the citation of patents, of which US2014103145-A1 was cited many times by patents in South Korea, Taiwan, and China, indicating that early technology output focused on equipment innovation.

With the popularity of 3D semiconductor structures, patent research between 2017 and 2019 has shifted towards high aspect ratio filling and doping control. US2018122642-A1 and US2019032211-A1 have solved the conformability problem of nitride thin films in FinFET structures by improving the spatial distribution of reactants. At this stage, the entropy value slightly decreased compared to the previous stage (average 11.30), reflecting the convergence of technical complexity from multivariate collaboration to specific process optimization. The proportion of transnational references rose to 42%, especially the Chinese Mainland patent CN116875961-A, citing the core patents of the United States and South Korea, which showed the acceleration of regional technology integration. The bidirectional citation intensity between the United States and South Korea is the highest, accounting for 58% of cross-border citations, highlighting the technological complementarity between the two countries in equipment material collaborative development.

The latest stage of patents focuses on low-temperature ALD processes and cost control, such as CN116875961-A, which reduces thermal budget through inert gas isolation design and adapts to advanced logic chip manufacturing needs. The entropy value further decreases to below 10.80, indicating that the technological path is developing towards maturity, and innovation points are focused on local parameter optimization.

- (3)

Analysis of the Technological Evolution of “Inter Electrode Isolation Technology”

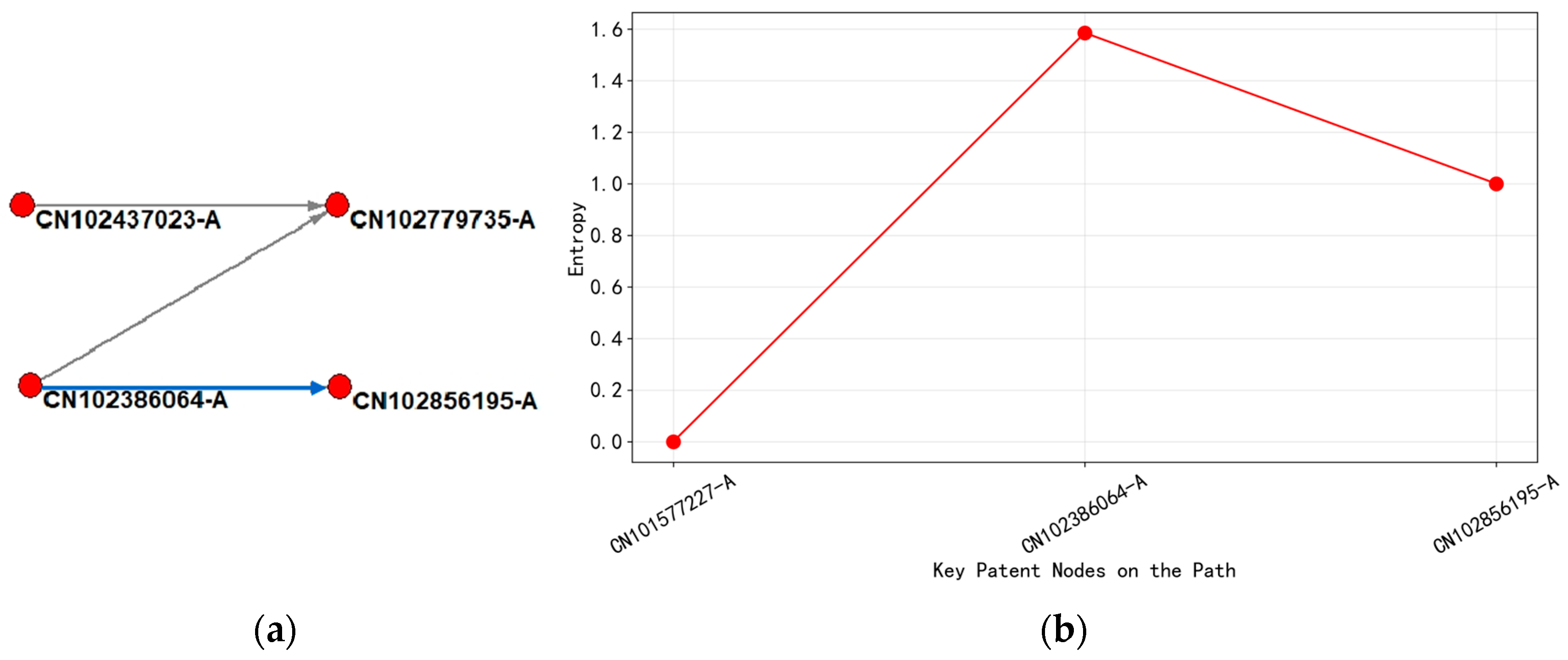

As shown in

Figure 19, from 2010 to 2013, patent classification mainly focused on H01L-021/334 (semiconductor etching process) and H01L-029/768 (multi-layer metal interconnect structure), with the technical goal of precision control and reliability improvement of capacitor structures. A typical patent such as CN102856195-A (2013) proposed a process of forming metal grooves by etching a low dielectric layer, combined with a mixed layer design to optimize the breakdown voltage, with an entropy range of 1.5–1.6, demonstrating the diffusion of technology branches. At this stage, there were cross-border citations, such as US7015110-B2 being cited by CN102386064-A (2012), indicating that the United States’ pioneering technology in semiconductor processes was flowing to China.

After entering 2013, technological evolution further focused on H01L-021/306 (processing of high aspect ratio structures) and H01L-023/522 (interconnect layer isolation technology), with patent content involving nanoscale precision control of inter-electrode isolation. For example, CN102709154-A (2012) proposed a method for preparing isolation layers based on dual lithography and selective deposition, with an entropy value of over 1.8, reflecting the complexity of the technology and cross-domain integration. The citation network presented a dense “bidirectional mutual reference” feature, such as CN102779735-A and CN102709154-A, forming a technological closed loop, indicating that China’s domestic research and development has entered the stage of independent innovation.

Through the analysis of entropy changes and citation network structure, it was found that the stepwise increase in entropy (1.1 → 1.8) revealed the transformation of technology from single-process breakthroughs to multi-dimensional innovation. The early low-entropy stage corresponded to the high convergence of technology, while the later high-entropy stage reflected the collaborative optimization of injection technology, materials, and structural design. The citation network structure indicated that the flow of technological knowledge presented a “core edge” diffusion pattern: the United States and international patents (such as the WO series) served as early sources of technology, continuously exporting basic methodologies to the Chinese patent network; after 2013, the inter citation density of domestic patents in China significantly increased, forming regional technology clusters, marking the shift of research and development focus towards localization. This evolutionary path not only reflected the upgrade of inter electrode isolation technology from basic processes to high-end manufacturing, but also reflected the typical trajectory of “introduction digestion independent innovation” in the global semiconductor technology ecosystem.

- (4)

Analysis of the Technological Evolution of “Atomic Layer Deposition Technology”

Based on the analysis of

Figure 20, it can be concluded that the upstream patent WO2020159882-A1 in 2020 focuses on the multi technology cross fusion of the ALD process. Its international patent classification covers the subdivision fields of C23C (plating technology) and H01L (semiconductor devices), involving metal film deposition process, low-temperature compatibility, and semiconductor device integration method. The technical goal of this stage is to solve the limitations of metal film resistivity and process temperature and achieve material performance breakthroughs through a two-step ALD process. By 2022, the downstream patent CN115261821-A significantly narrowed the scope of IPC classification, focusing on the improvement of thin film hydrogenation processes under C23C. The technological focus shifted towards optimizing the optoelectronic properties of thin films and regulating oxygen vacancies, reflecting the deep development of the technological path from multidimensional innovation to specific application scenarios.

Analyzing the changes in entropy values, the entropy value of the main path node decreased from 8.34 in the upstream to 3.0 in the downstream, indicating that the complexity of technical knowledge has shifted from divergence to convergence. The high-entropy value of upstream patents stems from their comprehensive improvement of ALD devices, controller programs, and multi-material systems, covering multiple technical levels, such as process design, equipment development, and semiconductor integration. The low-entropy value of downstream patents was reflected in the specialization of technical knowledge, optimizing film performance through single-point breakthroughs in hydrogenation processes, and shifting the focus of technology from basic process innovation to the improvement of specific performance parameters.

In addition, the upstream patent layout covered major global semiconductor technology markets (WO, US, JP, KR, etc.), demonstrating its technological foundation and wide applicability, and may become a core node for subsequent technology diffusion, while downstream patents are only located in China (CN), reflecting the deepening regional application of the technology path.

3.2.3. Evolution of Core Technologies in Chip Packaging and Testing

- (1)

Analysis of the Technological Evolution of “Wafer Level Packaging Technology”

As shown in

Figure 21a, based on the citation network and entropy evolution of the main path of wafer-level packaging technology patents from 2010 to 2020, the technological evolution was divided into the following three stages.

From 2010 to 2013, with WO2010121068-A2 (2010) as the core node, this patent had an entropy value of up to 6.82 and its technology classification covers 16 IPC subclasses (such as H01L-021/02, H01L-021/673), involving multi-layer process integration of wafer bonding equipment (adhesive layer, UV curing layer, laser release layer). The high-entropy value reflected the high degree of technological intersection and system complexity, which echoed the globalization strategy of its layout in 11 countries, indicating that the technology at this stage needs to adapt to the semiconductor manufacturing standards of multiple countries. Citation analysis showed that this patent, as the cited basic technology, directly drove the research and development of CN103035482-A (ring groove bonding method) and CN103441093-A (carrier framework design) in 2013. Although the entropy value of subsequent patents decreased to 2.00 (reducing the number of categories to 2), its technical topic focused on process optimization and achieved technological convergence by referencing upstream patents.

In 2015, CN104485294-A (2015) served as an intermediate node, with entropy rising to 5.88 and the number of classifications expanded to 25, covering subdivision directions such as mechanical peeling of isolation films and thermal decomposition adhesives. The fluctuation of the entropy value revealed that the technological path had shifted from equipment integration to process innovation, and the patent layout had expanded to four countries (CN/US/JP/KR), showing regional diffusion characteristics of technological knowledge. The abstract emphasized “reducing operational complexity”, but the sharp increase in the number of categories indicated that the technical solution should be compatible with different material systems (such as glass carrier plates and polymer isolation films). The citation structure simultaneously cites global patents from 2010 and domestic patents from China in 2013, forming cross-regional technology integration.

In 2020, regarding CN111524849-A (2020), at the end of the path, the entropy value drops to 2.32, with only one classification number. The technical topic focuses on the single-step bonding process of “inorganic layer adhesive coating”. Low-entropy values indicated an increase in technological maturity and a shift in process complexity from multi-module collaboration to material innovation dominance. The patent layout had shrunk to China, but the abstract showed that it cited early high-entropy patents (such as WO2010121068-A2), indicating that knowledge flow was concentrated from basic equipment patents to application layer process patents. The decrease in entropy value during this stage was closely related to the trend of miniaturization in semiconductor manufacturing (such as processes below 5 nm), and the technological evolution presented a path characteristic of “complex systems → breakthroughs in core materials”.

Entropy evolution analysis: As shown in

Figure 21b, the entropy value decreased step by step from a peak from 6.82 to 2.32, reflecting the transformation of wafer-level packaging technology from interdisciplinary integration to specialized process deepening. Early high-entropy patents established the breadth of technology diffusion through extensive layout and multi-class coverage; in the later stage, low-entropy patents improved the efficiency of technological iteration through localization and material innovation. The citation network further verified that the cross-border flow of technical knowledge (such as WO → CN/US) was strongly correlated with entropy changes, and the high complexity of global patents provided technical reserves for regional improvement, forming a closed-loop evolution path of “divergence convergence”.

- (2)

Analysis of the Technological Evolution of “Inverted Chip Packaging Technology”

As shown in

Figure 22, based on the patent main path citation network analysis, the evolution of flip chip packaging technology (a mounting method where the chip is inverted and connected face-down to the substrate) could be divided into three key stages (2005–2010, 2011–2016, 2017–2020), and its technical focus, entropy characteristics, and citation structure showed a significant correlation.

From 2005 to 2010, patents were focused on B32B-027/38 (layered structure adhesive layer) and H01L-021/58 (semiconductor packaging method), with title keywords such as “dicingdie-bonding film” and “pressure-sensitive adhesive layer” indicating that the technical focus was on the physical structure design of packaging materials. The patent layout was dominated by the United States (US) and Japan (JP), with an average entropy value of 3.91, reflecting the concentration of technical knowledge in a single field (layered materials and packaging processes). The citation network presented a linear topology with close citation relationships between nodes, manifested as the strong traction of the “core patent group” on subsequent technologies. For example, US2010029060-A1 was designed as a high-frequency cited node for subsequent patents through a multi-layer adhesive structure.

From 2011 to 2016, the technical focus expanded to C09J-133/08 (acrylic polymer adhesive) and H01L-023/00 (thermal management of packaged devices), with the titles “acrylic polymer design” and “pre-event wafer waring (predictive monitoring system for wafer-level failures)” indicating that material chemistry and device reliability have become innovative priorities. The patent layout spread to South Korea (KR), Taiwan, and China (TW), and the entropy value jumped to 4.81, revealing that the complexity of technical knowledge increased, and the cross discipline (material chemistry + mechanical engineering) led to a significant increase in information density. The citation network has evolved from linear to network, with high-entropy nodes (such as KR2010015290-A) connecting different technology subclasses through multi-path citations, forming a “technology bridging” effect and promoting collaborative innovation between packaging processes and materials science.

Finally, from 2017 to 2020, patent IPC classification focused on C09J-175/14 (polyurethane adhesive) and H01L-021/78 (thin wafer processing), with titles and abstracts emphasizing “thin wafer compatibility” and “high-tech resistance”, indicating a deepening of technology towards high-precision and weather-resistant scenarios. The patent layout presented a multipolar competitive pattern, with significant entropy differentiation (3.8–4.9), reflecting the maturity and subdivision of the technological path: low-entropy nodes focus on mature process improvement (such as CN101645425-B), while high-entropy nodes (such as JP5368502-B2) explore emerging directions such as 3D packaging by integrating photoresist materials and packaging processes. The citation network presented a “core edge” structure, with high-entropy nodes becoming technology diffusion hubs, and their citation relationships crossing geographical boundaries, confirming the transformation of technological knowledge from unipolar dominance to multipolar collaboration.

- (3)

Analysis of the Technological Evolution of “3D Stacked Packaging Technology”

As shown in

Figure 23a, in the evolution path of 3D stacked packaging technology in the field of chip packaging and testing, the main path only displays the evolution after 2020. From the analysis of the patent main path from 2020 to 2024, technological evolution could be divided into two stages: from 2020 to 2023, patent technology classification focuses on H01L-021/768 (semiconductor interconnect process) and H01L-023/00 (packaging structure design), with core innovations revolving around adhesive free bonding and multi-layer interconnect optimization; during 2023–2024, the technology classification was further expanded to H01L-025/065 (3D integrated circuit packaging), and the innovation direction shifted towards inorganic material composite packaging and thermal expansion coefficient control. This classification migration reflected the deepening of technology from a single packaging structure to high-density integration and material collaborative design.

From the analysis of

Figure 23b, the change in entropy value had a particularly critical impact on the citation network. The entropy value of the 2020 patent (US2020013754-A1) is 6.41, indicating a high complexity of its technical combination, corresponding to the multi-regional layout (US/WO/CN/TW) and cross domain technology citation (such as the combination of molding packaging and thermal management) in the citation network, forming a divergent knowledge diffusion. By 2023, the entropy value increased to 8.68 (US2023253367-A1), and technological integration was further strengthened. The dual encapsulation layer structure and high-density interconnection technology promoted the densification of citation network nodes, manifested as the concentrated citation of domestic patents in the United States, implying that the technological path converged to a specific innovation subject. It is worth noting that the entropy value of the 2024 patent (US2024243103-A1) suddenly dropped to 0, which may indicate technological singularity or data anomalies. Its citation network presented a “terminal node” feature (only cited without being cited) or reflected that inorganic material packaging technology was still in the early stage of monopoly, and knowledge mobility is limited.

- (4)

Analysis of the Technological Evolution of “Probe Testing Technology”

In the evolution of the main path of probe testing technology, as shown in

Figure 24, probe testing technology in the field of chip packaging and testing could be divided into three stages based on changes in entropy values and patents on the main path.

During 2010 and 2014, technological evolution centered around the improvement of the mechanical structure and electrical performance of probe cards, with IPC classification focusing on the intersection of G01R-031/00 (integrated circuit electrical performance testing) and G01R-001/067 (probe contact technology). High-entropy patents dominated at this stage, reflecting a dense phenomenon of technological knowledge recombination. The typical manifestation was the breakthrough patent of probe impedance matching technology, whose entropy value was significantly higher than the average level of the same period, triggering the main path to differentiate into two sub-directions: probe array topology optimization and multi-level signal transmission. The citation network exhibited significant unipolar diffusion characteristics, and the frequency of patent citations in East Asia from the United States as a technology source continued to increase, reflecting the primary unidirectionality of technology diffusion.

From 2015 to 2019, the focus of technology shifted towards improving thermal management efficiency and material durability, and the IPC classification was expanded to H01L-021/66 (semiconductor testing related technology) and the cross-disciplinary integration of thin film deposition processes. The entropy distribution showed a polarized trend: innovative patents for basic materials (such as elastomer substrate technology) exhibited extremely high-entropy characteristics, driving the main path to differentiate into two parallel paths: thermal expansion compensation and insulation structure optimization; the entropy value of process parameter improvement patents was significantly reduced, forming convergence nodes in the technology evolution tree. The cross-border citation network began to show signs of two-way interaction, with South Korean patents increasing synchronous citation frequency of US basic patents and Japanese material patents, while their domestic patents were cited more frequently than before, indicating the emergence of regional technological synergy.

After 2020, technological evolution entered a period of interdisciplinary system integration, and IPC classification further covered microelectromechanical packaging and high-frequency testing methods, marking a new level of technological complexity. At this stage, the proportion of high-entropy patents continued to increase, and typical nodes achieved systematic breakthroughs in probe durability and testing bandwidth through the integration of heterogeneous material composites and intelligent calibration technology. The significant increase in entropy value and the positive correlation with the strength of the main path bifurcation indicated that knowledge recombination had become the core mechanism driving technological transition. The citation network showed a multi-center diffusion pattern. The strength of mutual citation of patents from the United States, Japan, and South Korea had increased significantly, and the proportion of independent innovation achievements cited by Taiwan and China had increased synchronously, reflecting the maturity of the global regional dual dimension technology absorption and re-innovation mechanism.

- (5)

Analysis of the Technological Evolution of “Built-in Self Testing (BIST) Technology”

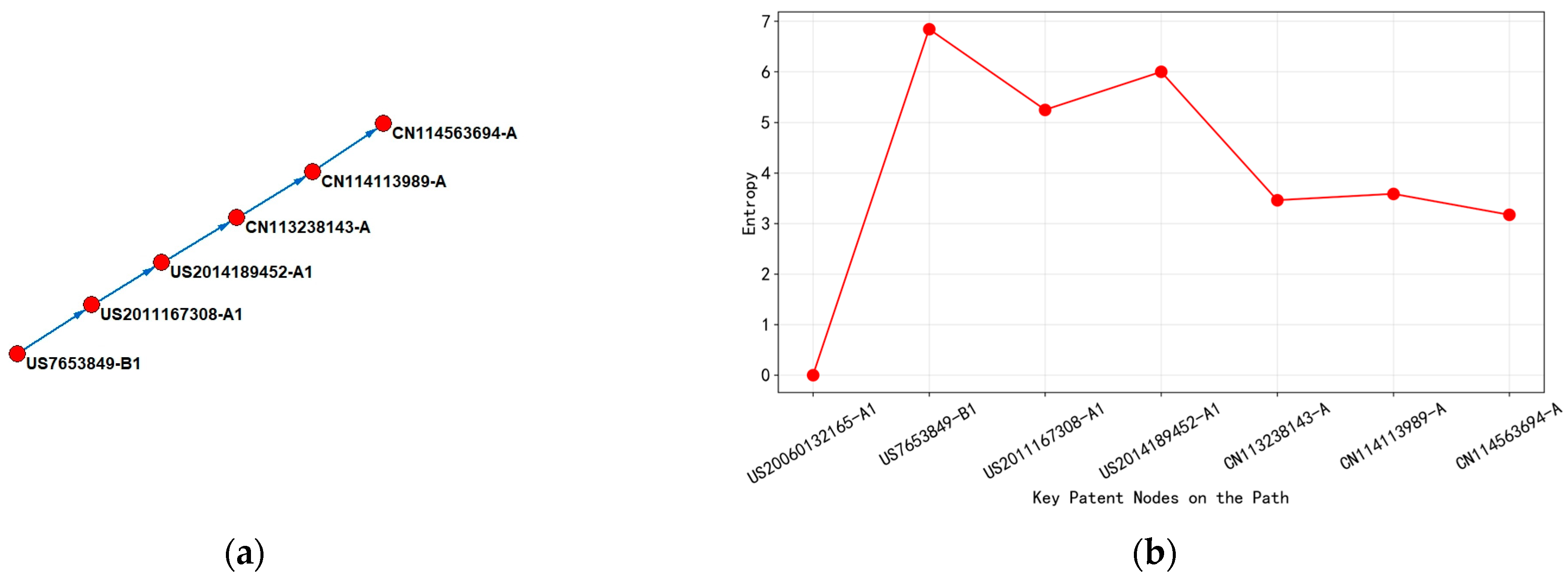

In the main path evolution of Built-in Test (BIST) technology in the field of chip packaging and testing, the entropy value changed, citation structure, and technical layout of patent nodes exhibited significant stage characteristics. The dynamic evolution of technical knowledge complexity and innovation direction can be observed through vertical analysis of the main path patents.

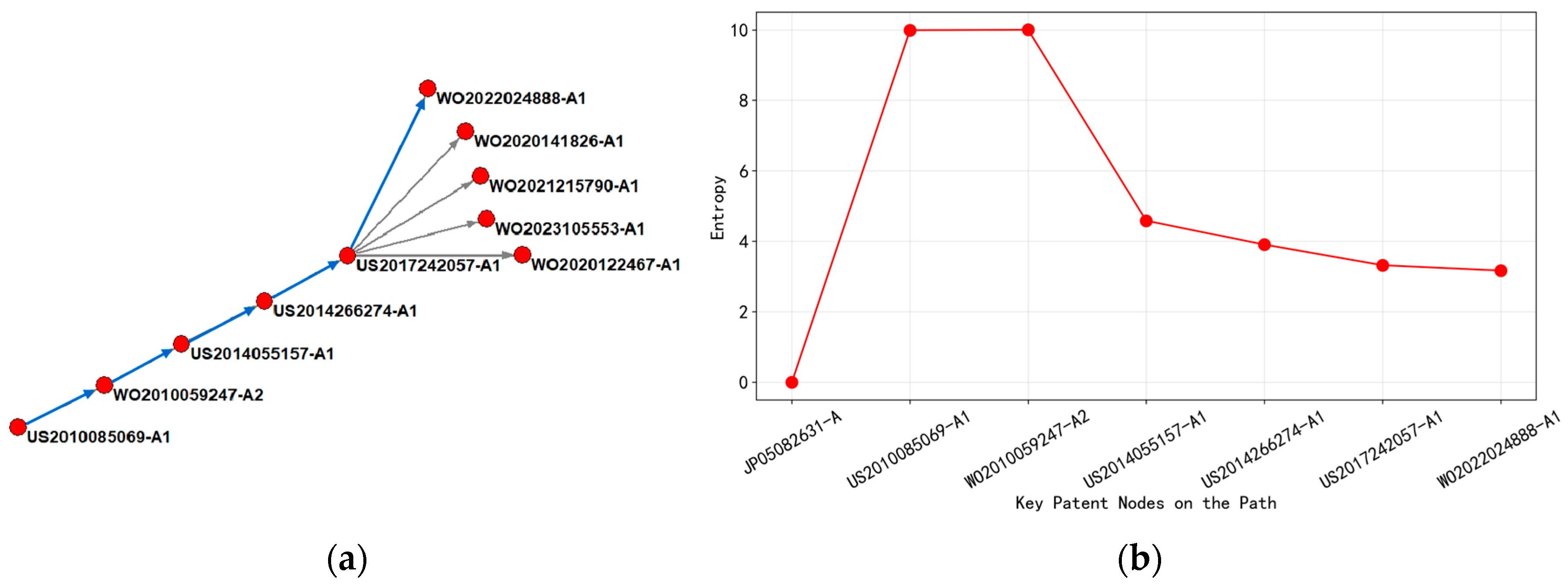

Stage 1: 2010–2014. At this stage, patents mainly focus on the classification of G01R31/3185 (scan chain testing) and G01R31/317 (digital logic testing), with the United States (US) patents as the focus, with a core emphasis on the underlying design of scan chain self-testing architecture. Representative patents such as US7653849-B1 (entropy 6.85) proposed a multi-component coupling testing method, which directly controlled the scan chain through an external tester. Its high-entropy feature reflected the high complexity of the technical solution, involving cross-module signal synchronization and dynamic power management. This type of patent is frequently cited by subsequent patents, forming the starting point of the main path.

Stage 2: 2015–2018. With the standardization of technology, the patent entropy value had significantly decreased (average 4.2), and technological improvements had shifted towards scan chain frequency division and test vector compression. For example, CN105243207-A (entropy 3.8) proposed a frequency division clock gating scheme to reduce testing time by simplifying control logic. At this stage, the proportion of patents between China (CN) and South Korea (KR) has increased to 40%, and the citation network showed the characteristics of regional technology diffusion: US basic patents were cited by Asian patents, and the mutual citation rate between CN patents had increased, indicating the initial formation of a localized technology ecosystem.

Phase III: 2019–2022. Recently, patents have shown polarization in entropy values: High-entropy nodes, such as US2022189452-A1 (entropy value 6.2), propose heterogeneous BIST architecture (self-test system combining different types of test circuits) and integrate AI driven adaptive testing algorithms (machine learning based test optimization that adapts to circuit behavior); low-entropy nodes, such as CN114563694-A (entropy 3.5), focus on modular design of clock gating circuits (standardized building blocks for power management in digital circuits). The technology classification has been expanded to G06F11/27 (self-checking fault-tolerant system), demonstrating the trend of integration between BIST technology and system-level reliability management. The patent layout was further globalized, with an increase in the number of World Intellectual Property Organization (WO) patent applications, and high-entropy patents were mostly jointly applied for by multinational enterprises, reflecting the demand for technological collaborative innovation.

By analyzing

Figure 25b, the fluctuation in entropy values revealed the exploration and convergence laws in the technology lifecycle: high-entropy nodes indicate architectural innovation (such as multi test mode coupling and dynamic reconstruction techniques), and their complexity required cross domain knowledge integration; low-entropy nodes correspond to modular improvements in technical solutions, reducing implementation costs through local optimization. The periodic increase in entropy value in the main path indicated that after breaking through the technical bottleneck, new knowledge entered the diffusion stage again.

From the analysis of

Figure 25a, US patents occupied a core hub position in the citation network, with the majority of CN and KR patents directly referencing US basic patents, while reverse citations were only a minority, indicating a one-way flow of technical knowledge from the US to Asia. It is worth noting that the density of patent applications in China has increased since 2018, indicating that the local technology system has gradually acquired the ability of derivative innovation. The entropy value of cross-border patents (such as EP and WO) was generally higher than that of single-country patents, confirming the positive impact of open innovation on technological complexity.